Page 1

!!!"#$%&'( )!*&+,+&-'+#.(

□ Tentative Specification

■ Preliminary Specification

□ Approval Specification

MODEL NO.: V420DK1

SUFFIX: LS1

!

&/0123456( (

!

"##$%&'(!)*! ! ! ! ! ! +,-."/0$'!

!

!

!"#$%&%'()*$% % % % % % % % % % % %%%%%%%%%%%%%%%%%%%%%%

!+)$%

!

!!!!!!!!!!!!!! !!!!!!!!!!!!!!!! !!!!!!!!!!!!!!!!

!"#$%#&'#()'*&+&,-./&0-'&/-)'&,-*01'2$(1-*&31(4&/-)'&%15*$()'#&$*6&

,-22#*(%7&

Approved By Checked By Prepared By

Chao-Chun Chung YP Lee Jim Ho

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 2

!!!"#$%&'( )!*&+,+&-'+#.(

CONTENTS

CONTENTS ....................................................................................................................................................................... 2

REVISION HISTORY.........................................................................................................................................................4

1. GENERAL DESCRIPTION ............................................................................................................................................ 5

1.1 OVERVIEW ......................................................................................................................................................................... 5

1.2 FEATURES ..........................................................................................................................................................................5

1.3 APPLICATION................................................................................................................................................................... 5

1.4 GENERAL SPECIFICATI0NS........................................................................................................................................... 5

1.5 MECHANICAL SPECIFICATIONS................................................................................................................................. 6

2. ABSOLUTE MAXIMUM RATINGS ................................................................................................................................7

2.1 ABSOLUTE RATINGS OF ENVIRONMENT ................................................................................................................ 7

2.2 PACKAGE STORAGE ....................................................................................................................................................... 8

2.3 ELECTRICAL ABSOLUTE RATINGS............................................................................................................................. 8

2.3.1 TFT LCD MODULE................................................................................................................................................. 8

2.3.2 BACKLIGHT CONVERTER UNIT .......................................................................................................................8

3. ELECTRICAL CHARACTERISTICS .............................................................................................................................9

3.1 TFT LCD MODULE ........................................................................................................................................................... 9

3.2 BACKLIGHT UNIT.......................................................................................................................................................... 12

3.2.1 CONVERTER CHARACTERISTICS................................................................................................................... 12

3.2.2 CONVERTER INTERFACE CHARACTERISTICS ...........................................................................................14

4. BLOCK DIAGRAM OF INTERFACE ........................................................................................................................... 16

4.1 TFT LCD MODULE ......................................................................................................................................................... 16

5 .INPUT TERMINAL PIN ASSIGNMENT ....................................................................................................................... 17

5.1 TFT LCD MODULE ......................................................................................................................................................... 17

5.2 BACKLIGHT UNIT.......................................................................................................................................................... 23

5.3 CONVERTER UNIT......................................................................................................................................................... 24

5.4 LVDS INTERFACE........................................................................................................................................................... 25

5.5 COLOR DATA INPUT ASSIGNMENT......................................................................................................................... 26

6. INTERFACE TIMING...................................................................................................................................................27

6.1 INPUT SIGNAL TIMING SPECIFICATIONS .............................................................................................................. 27

6.1.1 Input Timing Spec for FHD, Frame Rate = 50Hz .............................................................................................. 27

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 3

!!!"#$%&'( )!*&+,+&-'+#.(

6.1.2 Input Timing Spec for FHD, Frame Rate = 60Hz .............................................................................................. 28

6.1.3 Input Timing Spec for FHD, Frame Rate = 100Hz ............................................................................................ 28

6.1.4 Input Timing Spec for FHD, Frame Rate = 120Hz ............................................................................................ 29

6.1.5 Input Timing spec for QFHD, Frame Rate = 24Hz ........................................................................................... 30

6.1.6 Input Timing spec for QFHD, Frame Rate = 30Hz ........................................................................................... 30

6.2 POWER ON/OFF SEQUENCE ......................................................................................................................................33

7. OPTICAL CHARACTERISTICS ..................................................................................................................................34

7.1 TEST CONDITIONS ........................................................................................................................................................ 34

7.2 OPTICAL SPECIFICATIONS .........................................................................................................................................35

8. PRECAUTIONS...........................................................................................................................................................40

8.1 ASSEMBLY AND HANDLING PRECAUTIONS........................................................................................................ 40

8.2 SAFETY PRECAUTIONS ................................................................................................................................................ 40

8.3 SAFETY STANDARDS.................................................................................................................................................... 40

9. DEFINITION OF LABELS............................................................................................................................................ 41

9.1 INX MODULE LABEL..................................................................................................................................................... 41

9.2 CARTON LABEL.............................................................................................................................................................. 42

10. PACKAGING..............................................................................................................................................................43

10.1 PACKAGING SPECIFICATIONS ................................................................................................................................ 43

10.2 PACKAGING METHOD............................................................................................................................................... 43

10.3 UN PACKAGING METHOD ....................................................................................................................................... 45

11. M ECHANI CAL C HARACTERI STIC.... .... .... .... ..... .... .... .... ..... .... .... ..... .... .... .... ..... .... .... .... ..... .... .... .... .......................... 46

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 4

!!!"#$%&'( )!*&+,+&-'+#.(

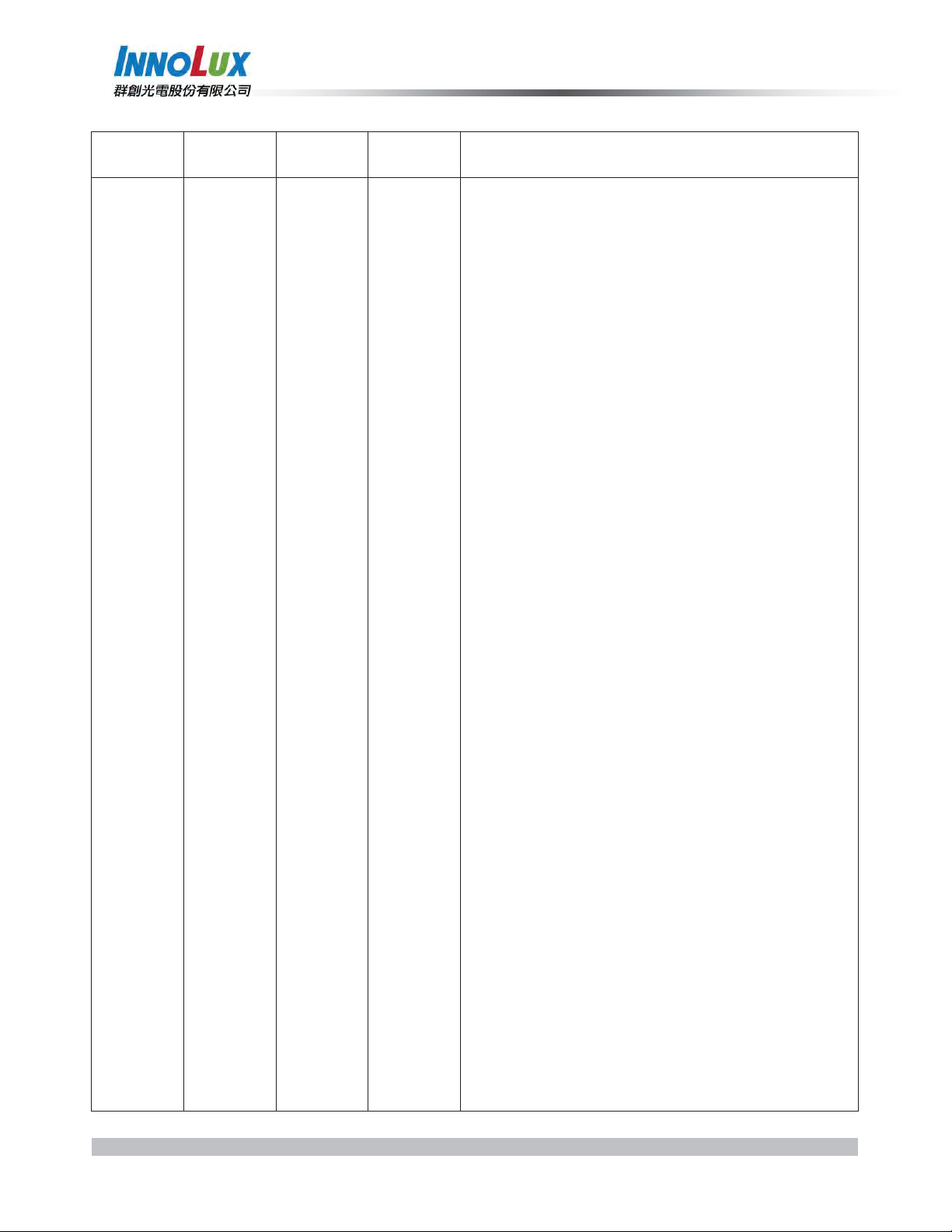

REVISION HISTORY

Version Date

Ver. 1.0 Ap r. 26, 2013 Al l Al l The pre liminary spec ifica tion was f irst issu ed.

Page

(New)

Section Description

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 6 ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 5

!!!"#$%&'( )!*&+,+&-'+#.(

1. GENERAL DESCRIPTION

1.1 OVERVIEW

8603V420DK1-LS1 is a 42” TFT Liquid Crystal Display module with LED Backlight unit and 4ch-LVDS interface.

This module supports 3840 x 2160 Quad Full HDTV format and can display true 1.07G colors (8-bit+FRC).

The driving board module for backlight is built-in.

1.2 FEATURES

! High brightness 350 nits

! High contrast ratio 5000:1

! Fast response time Gray to Gray typical : 6.5 ms

! High color saturation NTSC 72%

! Quad Full HDTV (3840 x 2160 pixels) resolution, true HDTV format

! LVD S (Lo w Volta ge Di ffer entia l Sign aling ) inter face

! Optimized response time for 100Hz/120Hz frame rate

! Viewing Angle : 176(H)/176(V) (CR>20) VA Technology

! Ultra wide viewing angle: Super MVA technology

! RoHs compliance

! T-con input frame rate : FHD 50/60Hz, FHD 100/12 0Hz or QFHD 24/30Hz

Output frame rate: QFHD 50/60Hz, QFHD 100/120Hz or QFHD 48/60Hz

1.3 APPLICATION

! Standard Living Room TVs

! Public Display Application

! Home Theater Application

! MFM Application

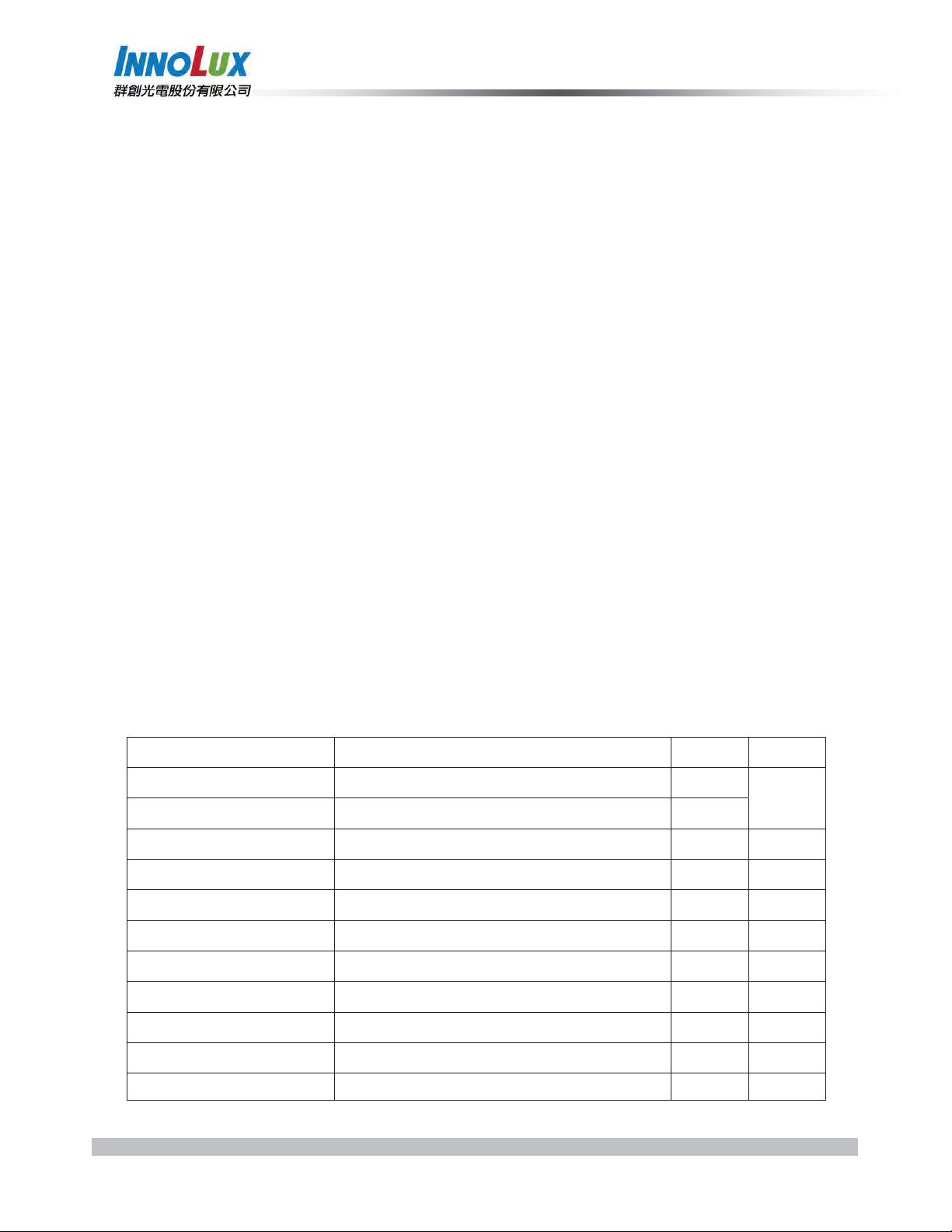

1.4 GENERAL SPECIFICATI0NS

Item Specific ati on Unit Note

Active Area

Bezel Opening Area

Driver Element

Pixel Number

Pixel Pitch(Sub Pixel)

Pixel Arrangement

Display Colors

Display Operation Mode

919.296 (H) x 517.104 (V)

924.296 (H) x 522.104 (V)

a-si TFT active matrix

3840 x R.G.B. x 2160

0.0798 (H) x 0.2394 (V)

RGB vertical stripe

1.07G colors (8-bit+FRC)

Transmissive mode / Normally black

mm

(1)

mm

--

pixel -

mm -

--

color -

--

Surface Treatment

Rotation Function

Display Orientation

Note (1) Please refer to the attached drawings in chapter 11 for more information about the front and back outlines.

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 7 ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Anti-Glare coating (Haze 1%)

Achievable (3)

Signal input with “INX” (3)

-(2)

Page 6

!!!"#$%&'( )!*&+,+&-'+#.(

Note (2) The spec of the surface treatment is temporarily for this phase. INX reserves the rights to change this feature.

Note (3)

Back Side

Front Side

INX

Tc on Bo ar d

1.5 MECHANICAL SPECIFICATIONS

Item Min. Typ. Max. Unit Note

Horizontal (H) 935.3 936.3 937.3 mm (1),(2)

Module Size

Weight 8189

Note (1) Please refer to the attached drawings for more information of front and back outline dimensions.

Note (2) Module Depth does not include connectors.

Ver t ical (V) 5 37.1 538.1 539.1 mm (1), (2)

15.2 16.2 17.2 mm To Rear

Depth (D)

24.6 25.6 26.6 mm

8620

9051 g

To co nv er te r

cover

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 3 ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 7

2. ABSOLUTE MAXIMUM RATINGS

2.1 ABSOLUTE RATINGS OF ENVIRONMENT

!!!"#$%&'( )!*&+,+&-'+#.(

Item Symbol

Unit Note

Min. Max.

Storage Temperatur e TST -20 +60 ºC (1)

Operating Ambient Temperature TOP 0 50 ºC (1), (2)

Value

Shock (Non-Operating) S

Vibration (Non-Operating) V

Note (1) Temperature and relative humidity range is shown in the figure below.

(a) 90 %RH Max. (Ta ! 40 ºC).

(b) Wet-bulb temperature should be 39 ºC Max. (Ta > 40 ºC).

(c) No condensation.

Note (2)

The maximum operating temperature is based on the test condition that the surface temperature of

- 50 G (3), (5)

NOP

- 1.0 G (4), (5)

NOP

display area is less than or equal to 65 ºC with LCD module alone in a temperature controlled chamber.

Thermal management should be considered in final product design to prevent the surface temperature

of display area from being over 65 ºC. The range of operating temperature may degrade in case of

improper thermal management in final product design.

Note (3) 11 ms, half sine wave, 1 time for ± X, ± Y, ± Z.

Note (4) 10 ~ 200 Hz, 30 min, 1 time each X, Y, Z.

Note (5) At testing Vibration and Shock, the fixture in holding the module has to be hard and rigid enough so that the module

would not be twisted or bent by the fixture.

Relative Humidity (%RH)

100

90

80

60

Operating Range

40

20

Storage Range

10

80 60 -20 40 0 20 -40

Tempe r at ure (º C)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 8 ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 8

!!!"#$%&'( )!*&+,+&-'+#.(

2.2 PACKAGE STORAGE

When storing modules as spares for a long time, the following precaution is necessary.

(a) Do not leave the module in high temperature, and high humidity for a long time, It is highly recommended to

store the module with temperature from 0 to 35 ! at normal humidity without condensation.

(b) The module shall be stored in dark place. Do not store the TFT-LCD module in direct sunlight or fluorescent

light.

2.3 ELECTRICAL ABSOLUTE RATINGS

2.3.1 TFT LCD MODULE

Item Symbol

Min. Max.

Power Supply Voltage VCC -0.3 13.5 V

Logic Input Voltage VN -0.3 3.6 V

2.3.2 BACKLIGHT CONVERTER UNIT

Item Symbol

Light Bar Voltage VW Ta = 25 ! - - 60 V

Converter Input Voltage VBL - 0 - 30 V

Control Signal Level - - -0.3 - 6 V

Note (1) Permanent damage to the device may occur if maximum values are exceeded. Function operation should be

restricted to the conditions described under Normal Operating Conditions.

Note (2) No moisture condensation or freezing.

Note (3) The control signals include On/Off Control and External PWM Control.

Value

Test

Condition

Unit Note

Min. Type Max. Unit Note

RMS

3D Mode

(1)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 9 ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 9

!!!"#$%&'( )!*&+,+&-'+#.(

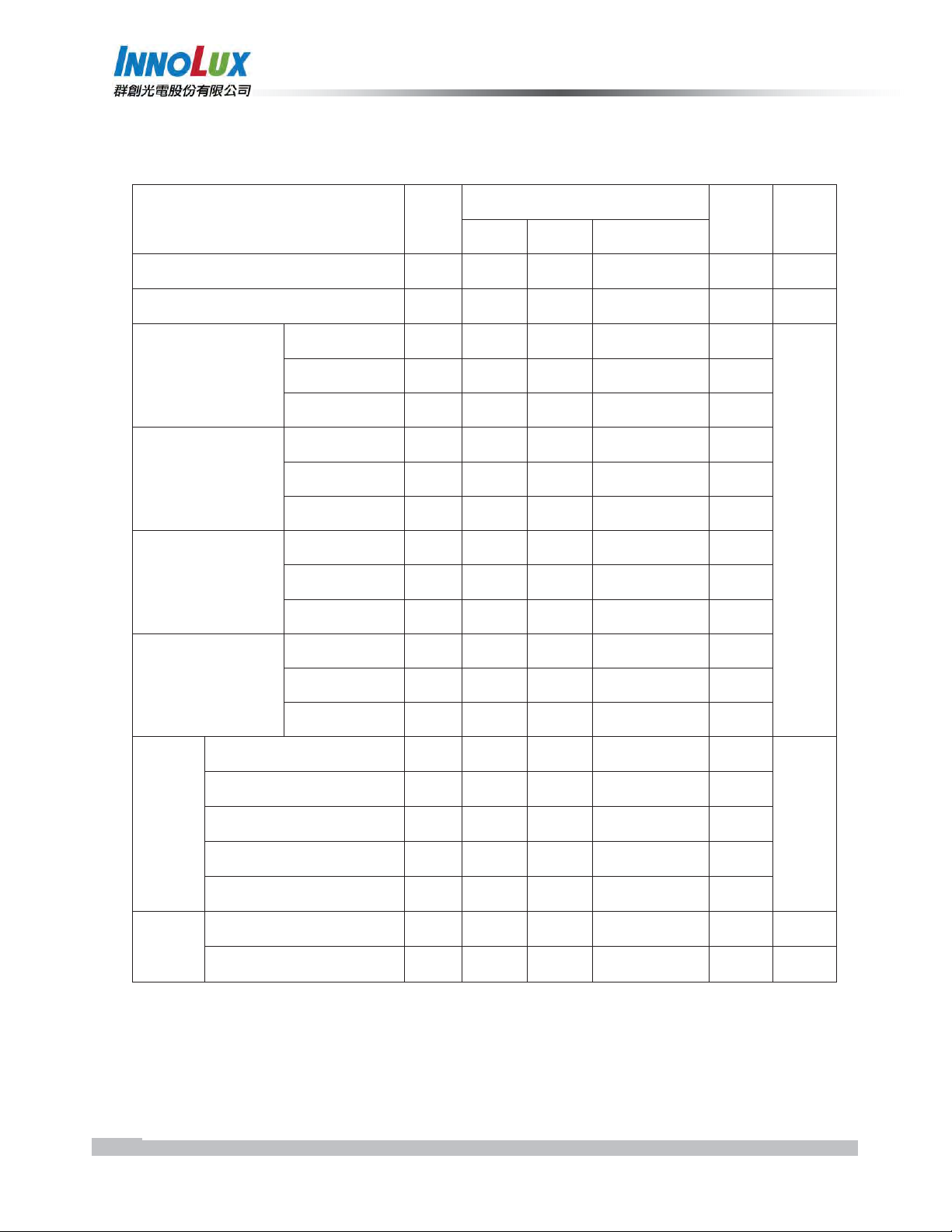

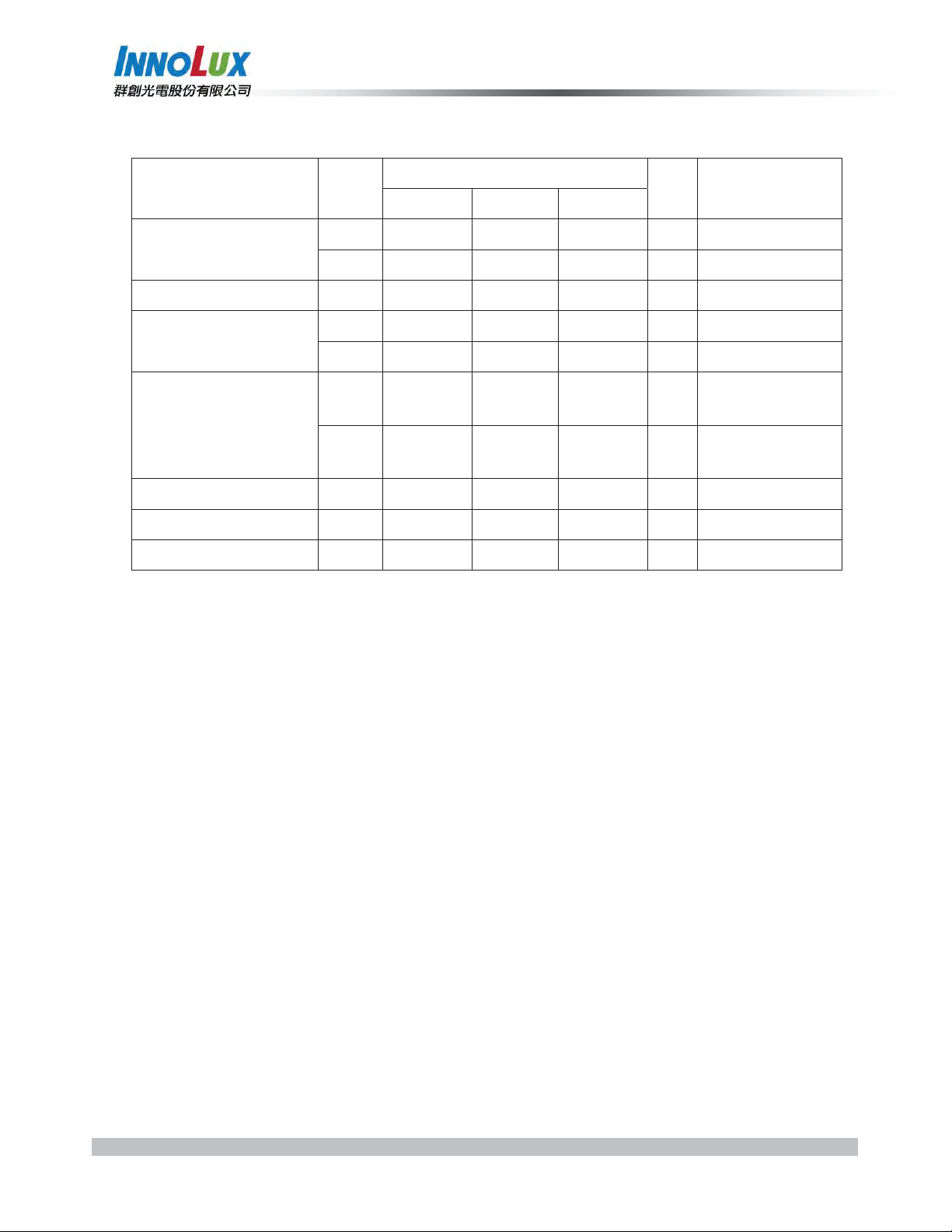

3. ELECTRICAL CHARACTERISTICS

3.1 TFT LCD MODULE

(Ta = 25 ± 2 ºC)

Valu e

Parameter Symbol

Min. Typ. Max.

Power Supply Voltage VCC 10.8 12 13.2 V (1)

Unit Note

Rush Current I

White Pattern P

QFHD 120Hz Output

Power Consumption

Horizontal Stripe P

Black Pattern P

White Pattern

QFHD 120Hz Output

Horizontal Stripe

Power Supply Current

Black Pattern

White Pattern P

QFHD 60Hz Output

Horizontal Stripe P

Power Consumption

Black Pattern P

White Pattern

QFHD 60Hz Output

Horizontal Stripe

Power Supply Current

Black Pattern

Differential Input High

Threshold Voltage

Differential Input Low

Threshold Voltage

LVD S

interface

Common Input Voltage VCM 1.0 1.2 1.4 V

Differential input voltage

(single-end)

RUSH

T

T

T

!!

!

!

!

!!

!!

!!

T

T

T

!

!

!

!!

!!

!!

+100

V

LVT H

-300

V

LVT L

|V

| 200

D

(2.8) A (2)

(9.12) (10.68) W

(20.88) (25.20) W

(9.36) (11.04) W

(0.76) (0.89) A

(1.74) (2.10) A

(0.78) (0.92) A

(9.72) (11.28) W

(20.16) (23.52) W

(8.88) (10.20) W

(0.81) (0.94) A

(1.68) (1.96) A

(0.74) (0.85) A

!

!

!

+300 mV

-100 mV

600 mV

(3)

(4)

CMOS

interface

Te r mi n a ti n g Re s is to r R

T

!

Input High Threshold Voltage VH 2.7

Input Low Threshold Voltage V

0

IL

100

!

!

!

ohm

3.3 V

0.7 V

Note (1) The module should be always operated within the above ranges. The ripple voltage should be controlled under

10% of Vcc (Typ.)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( : ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/ (0 1#*234(2+ )5( ( ( ( ( ( ( ( (

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 10

!!!"#$%&'( )!*&+,+&-'+#.(

Note (2) Measurement condition :

GND

Note (3) The specified power supply current is under the conditions at Vcc = 12 V, Ta = 25 ± 2 ºC, fv = 60/120 Hz, whereas a

power dissipation check pattern below is displayed.

a. White Pattern

Vcc rising time is 470us

Vcc

0.9Vcc

0.1Vcc

470us

b. Black Pattern

Active Area

c. Horizontal Pattern

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) +( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Active Area

Page 11

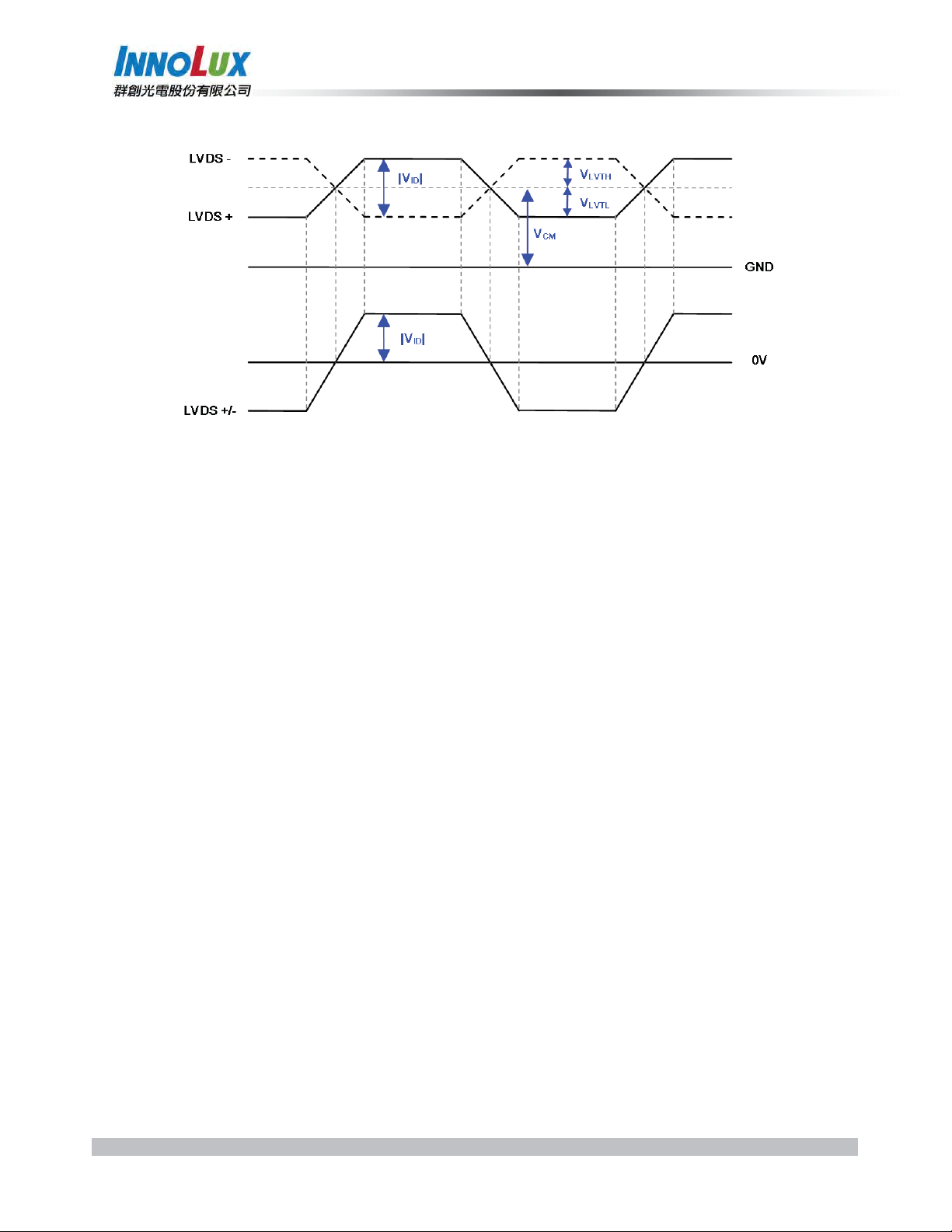

Note (4) The LVDS input characteristics is shown as below :

!!!"#$%&'( )!*&+,+&-'+#.(

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) )( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 12

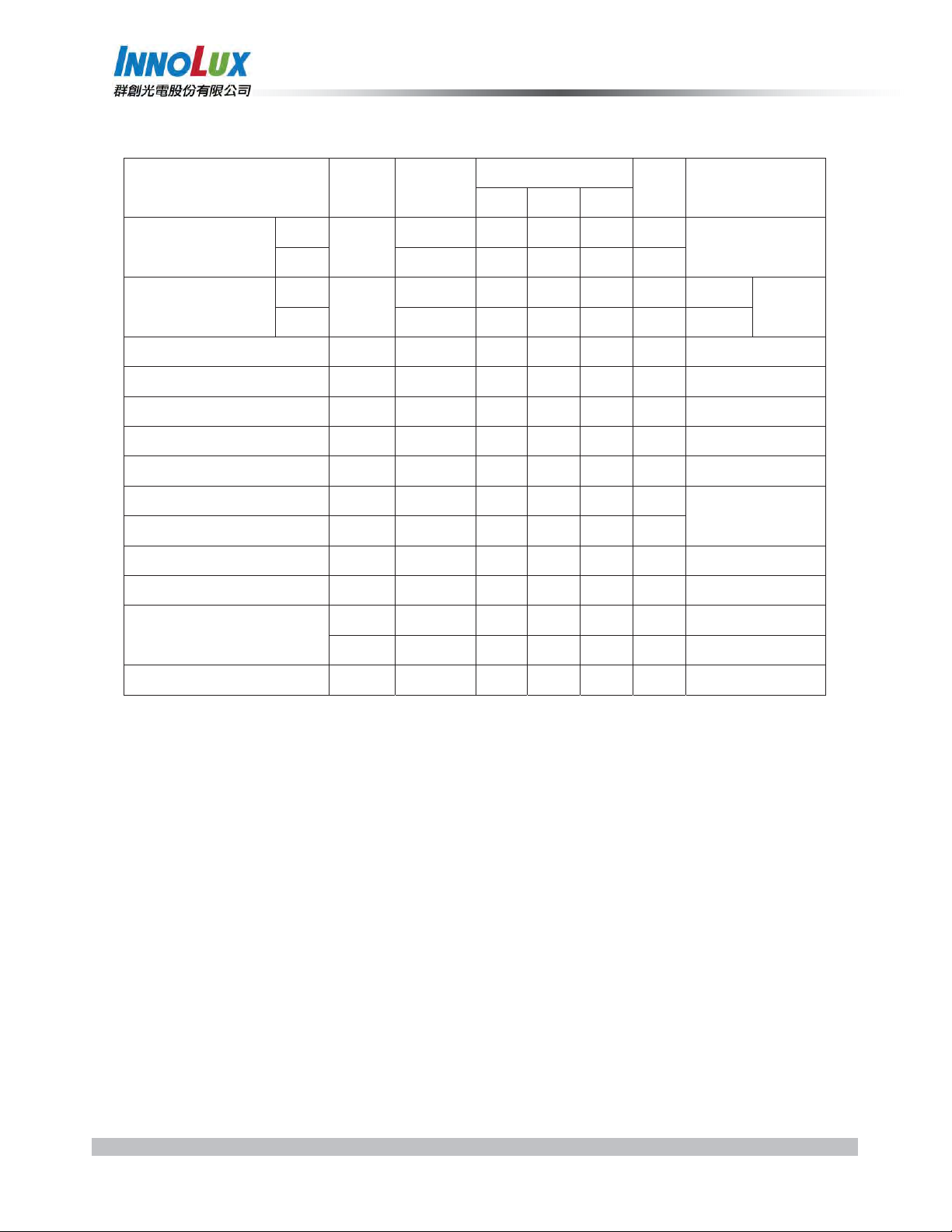

3.2 BACKLIGHT UNIT

3.2.1 CONVERTER CHARACTERISTICS

!!!"#$%&'( )!*&+,+&-'+#.(

Parameter Symbol

Unit Note

Min. Typ. Max.

Value

P

BL(2D)

"

44.9 51.7

W

(1), (2)

Power Consumption

P

BL(3D)

"

36.3 40.7 W (1), (2)

Converter Input Voltage VBL 22.8 24.0 25.2 VDC

Converter Input Current

I

BL(2D)

I

BL(3D)

I

R(2D)

"

"

""

1.87 2.2

A Non Dimming

1.63 1.73 A

3.9

Apeak

VBL=22.8V

(3), (6)

Input Inrush Current

I

R(3D)

""

5.4

Apeak

VBL=22.8V

(3), (6)

Dimming Frequency FB 170 180 190 Hz (5)

Dimming Duty Ratio DDR 5 - 100 % (4), (5)

Life Time

Note (1) The power supply capacity should be higher than the total converter power consumption PBL. Since the pulse

width modulation (PW M) mode was applied for backlight dimming, the driving current changed as PWM duty

on and off. The transient response of power supply should be considered for the changing loading when

converter dimming.

Note (2) The measurement condition of Max. value is based on 39" backlight unit under input voltage 24V, at 2D/3D

Mode and lighting 1 hour later.

Note (3) For input inrush current measure, the VBL rising time from 10% to 90% is about 20ms.

Note (4) EPWM signal have to input available duty range. Between 97% and 100% duty (DDR) have to be avoided.

(97% < DDR < 100%) But 100% duty(DDR) is possible. 5% duty (DDR) is only valid for electrical operation.

Note (5) FB and DDR are available only at 2D Mode.

Note (6) Below diagram is only for power supply design reference.

-

30,000 - - Hrs (7)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) 2( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 13

!!!"#$%&'( )!*&+,+&-'+#.(

Current : 5.4A

Current : 3.9 A

Current: 2.45A

Current : 2.2 A

Test Condition : VBL=22.8V,

Iin(A)

at 2D Mode / at 3D Mode

2D Mode

3D Mode

T1 T2 Time (m )

200 ms

Mode Change

2 D ->

3D

T2

Duty 20%

Dimming Freq .

200 ms

Note (7) The lifetime is defined as the time which luminance of the LED decays to 50% compared to the initial value,

Operating condition: Continuous operating at Ta = 25±2!

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) 5( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 14

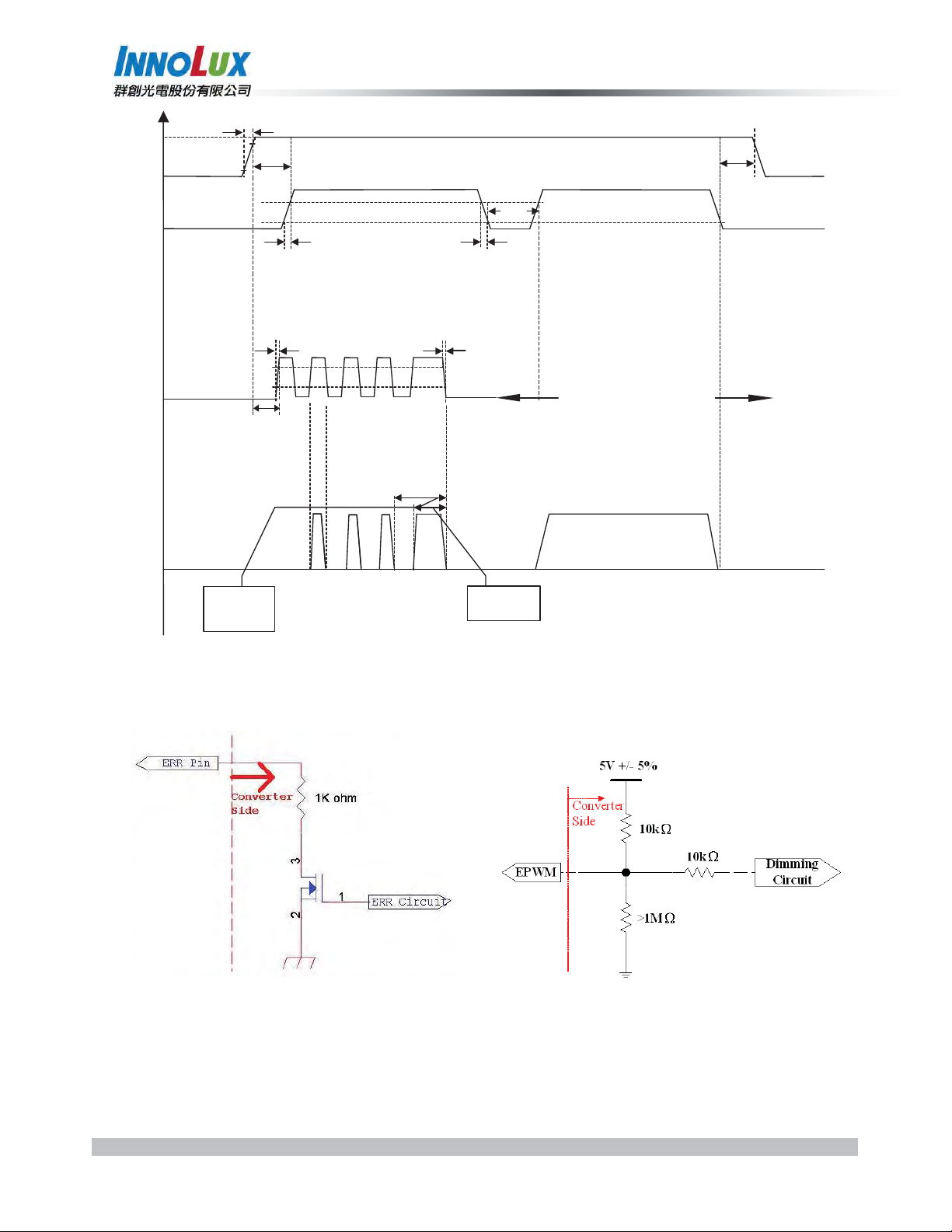

3.2.2 CONVERTER INTERFACE CHARACTERISTICS

!!!"#$%&'( )!*&+,+&-'+#.(

Parameter Symbol

ON

On/Off Control Voltage

VBLON

OFF

External PWM Control

Voltage

External PWM Frequency

HI

LO

VEPWM

F

EPWM

Error Signal ERR

VBL Rising Time Tr1

Control Signal Rising Time Tr

Control Signal Falling Time Tf

PWM Signal Rising Time TPWMR

PWM Signal Falling Tim e TPW MF

Input Impedance Rin

PWM Delay Time TPWM

T

BLON Delay Time

on

T

on1

Test

Value

Unit Note

Condition

!

!

!

!

Min. Typ. Max.

2.0

0

2.0

0

!

!

!

!

5.0 V

0.8 V

5.25 V Duty on

0.8 V Duty off

" 150 160 170 Hz Normal mode (7)

!!!!!

!

20

!!!

!!!

!!!

!!

100 ms

100 ms

50 us

ms 10%-90%V

Abnormal: Open

(6)

!!!

!

!

!

!

1

100

300

300

!!

!!

!!

!!

50 us

MΩ

ms (6)

ms

ms

EPWM, BLON

(5), (6)

BL

BLON Off Time Toff

Note (1) The Dimming signal should be valid before backlight turns on by BLON signal. It is inhibited to change the

external PWM signal during backlight turn on period.

Note (2) The power sequence and control signal timing are shown in the Fig.1. For a certain reason, the converter has a

possibility to be damaged with wrong power sequence and control signal timing.

Note (3) While system is turned ON or OFF, the power sequences must follow as below descriptions:

Turn ON sequence: VBL → PWM signal → BLON

Turn OFF sequence: BLOFF → PWM signal → VBL

Note (4) When converter protective function is triggered, ERR will output open collector status. Please refers to Fig.2.

Note (5) The EPWM interface that inserts a pull up resistor to 5V in Max Duty (100%), please refers to Fig.3.

Note (6) EPWM is available only at 2D Mode.

Note (7) EPWM signal have to input available frequency range.

Note (8) [Recommend] EPWM duty ratio is set at 100%(Max. Brightness) in 3D Mode.

!

300

!!

ms

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) 6( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 15

!!!"#$%&'( )!*&+,+&-'+#.(

V

V

V

BLON

EPWM

V

BL

!"%$

0

!"

2.0V

0

0.8V

!"#$

Ton

!"

Toff

Ton1

Backlight on duration

Tr1

Tr

Tf

Ext. Dimming Function

PWMR

T

2.0V

0

W

0.8V

PWM

T

T

PWMF

Floating

External

PWM

Period

External

PWM Duty

100%

Fig. 1

Fig. 2 Fig. 3

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) 7( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 16

!!!"#$%&'( )!*&+,+&-'+#.(

4. BLOCK DIAGRAM OF INTERFACE

4.1 TFT LCD MODULE

OUTPUT CONNECTOR

L/R_O

CON2: LM123S-010-H-TF1-3Y

TFT LCD PANEL

(3840x3x2160)

X(R) Board X(L) Board

C Board

CH1_0(+/-)

CH1_1(+/-)

CH1_2(+/-)

CH1_3(+/-)

CH1_4(+/-)

CH1_CLK(+/-)

CH2_0(+/-)

CH2_1(+/-)

CH2_2(+/-)

CH2_3(+/-)

CH2_4(+/-)

CH2_CLK(+/-)

INPUT CONNECTOR

CNF1: 187059-51221(P-TWO)

or WF23-402-5133(FCN)

2D/3D SDA

SELLVDS

VBL

L/R LD_EN VCC L/R_O GND SCL

CONVERTER

GND

ERR

E_PWM

BLON

CN1:

JH2-D4-143N(FCN) or

CI0114M1HR0-LA(CvilLux)

CONNECTOR

INPUT CONNECTOR

CNF2:

187060-41221(P-TWO) or

WF23-400-413C(FCN)

CH3_0(+/-)

CH3_1(+/-)

CH3_2(+/-)

CH3_3(+/-)

CH3_4(+/-)

CH3_CLK(+/-)

CH4_0(+/-)

CH4_1(+/-)

CH4_2(+/-)

CH4_3(+/-)

CH4_4(+/-)

CH4_CLK(+/-)

LED

BACKLIGHT

UNIT

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) 3( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 17

!!!"#$%&'( )!*&+,+&-'+#.(

5 .INPUT TERMINAL PIN ASSIGNMENT

5.1 TFT LCD MODULE

CNF1 Connector Pin Assignment (187059-51221(P-TWO) or WF23-402-5133 (FCN))

Matting connector: FI-RE51HL (JAE)

Pin Name Description

1 N.C. No Connection (1)

2 SCL I2C Clock (for mode selection & function setting)

3 SDA I2C Data (for mode selection & function setting)

4 N.C. No Connection

5 L/R_O Output signal for Left Right Glasses control

6 N.C. No Connection (1)

7 SELLVDS Input signal for LVDS Data Format Selection (3)(9)

8 N.C. No Connection

9 N.C. No Connection

10 N.C. No Connection

11 GND Gr ound

12 CH1[0]- First pixel Negative LVDS differential data input. Pair 0

13 CH1[0]+ First pixel Positive LVDS differential data input. Pair 0

14 CH1[1]- First pixel Negative LVDS differential data input. Pair 1

15 CH1[1]+ First pixel Positive LVDS differential data input. Pair 1

Note

(1)

(2)

(1)

(4)

16 CH1[2]- First pixel Negative LVDS differential data input. Pair 2

17 CH1[2]+ First pixel Positive LVDS differential data input. Pair 2

18 GND Ground

19 CH1CLK- First pixel Negative LVDS differential clock input.

(4)

20 CH1CLK+ First pixel Positive LVDS differential clock input.

21 GND Ground

22 CH1[3]- First pixel Negative LVDS differential data input. Pair 3

23 CH1[3]+ First pixel Positive LVDS differential data input. Pair 3

(4)

24 CH1[4]- First pixel Negative LVDS differential data input. Pair 4

25 CH1[4]+ First pixel Positive LVDS differential data input. Pair 4

26 2D/3D Input signal for 2D/3D Mode Selection (5)(10)

27 L/R Input signal for Left Right eye frame synchronous (6)

28 CH2[0]- Second pixel Negative LVDS differential data input. Pair 0

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) 8( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

(4)

Page 18

!!!"#$%&'( )!*&+,+&-'+#.(

29 CH2[0]+ Second pixel Positive LVDS differential data input. Pair 0

30 CH2[1]- Second pixel Negative LVDS differential data input. Pair 1

31 CH2[1]+ Second pixel Positive LVDS differential data input. Pair 1

32 CH2[2]- Second pixel Negative LVDS differential data input. Pair 2

33 CH2[2]+ Second pixel Positive LVDS differential data input. Pair 2

34 GND Ground

35 CH2CLK- Second pixel Negative LVDS differential clock input.

36 CH2CLK+ Second pixel Positive LVDS differential clock input.

37 GND Ground

38 CH2[3]- Second pixel Negative LVDS differential data input. Pair 3

(4)

39 CH2[3]+ Second pixel Positive LVDS differential data input. Pair 3

40 CH2[4]- Second pixel Negative LVDS differential data input. Pair 4

41 CH2[4]+ Second pixel Positive LVDS differential data input. Pair 4

42 LD_EN Input signal for Local Dimming Enable (7)(9)

43 N.C. No Connection (8)

44 GND Ground

45 GND Ground

46 GND Ground

47 N.C. No Connection

48 VCC +12V power supply

49 VCC +12V power supply

50 VCC +12V power supply

51 VCC +12V power supply

CNF2 Connector pin assignment (187060-41221 (P-TWO) or WF23-400-413C (FCN))

Matting connector: FI-RE41HL (JAE)

(4)

(1)

Pin Name Description Note

1 N.C. No Connection

2 N.C. No Connection

3 N.C. No Connection

4 N.C. No Connection

5 N.C. No Connection

6 N.C. No Connection

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) 9( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

(1)

Page 19

!!!"#$%&'( )!*&+,+&-'+#.(

7 N.C. No Connection

8 N.C. No Connection

9 GND Ground

10 CH3[0]- Third pixel Negative LVDS differential data input. Pair 0

11 CH 3[0] + T hird p ixel P ositi ve LVDS differ enti al data input. Pair 0

12 CH3[1]- Third pixel Negative LVDS differential data input. Pair 1

13 CH3[1]+ Third pixel Positive LVDS differential data input. Pair 1

14 CH3[2]- Third pixel Negative LVDS differential data input. Pair 2

15 CH3[2]+ Third pixel Positive LVDS differential data input. Pair 2

16 GND Ground

17 CH3CLK- Third pixel Negative LVDS differential clock input.

18 CH3CLK+ Third pixel Positive LVDS differential clock input.

19 GND Ground

(4)

(4)

20 CH3[3]- Third pixel Negative LVDS differential data input. Pair 3

21 CH3[3]+ Third pixel Positive LVDS differential data input. Pair 3

22 CH3[4]- Third pixel Negative LVDS differential data input. Pair 4

23 CH3[4]+ Third pixel Positive LVDS differential data input. Pair 4

24 GND Ground

25 GND Ground

26 CH4[0]- Fourth pixel Negative LVDS differential data input. Pair 0

27 CH4[0]+ Fourth pixel Positive LVDS differential data input. Pair 0

28 CH4[1]- Fourth pixel Negative LVDS differential data input. Pair 1

29 CH4[1]+ Fourth pixel Positive LVDS differential data input. Pair 1

30 CH4[2]- Fourth pixel Negative LVDS differential data input. Pair 2

31 CH4[2]+ Fourth pixel Positive LVDS differential data input. Pair 2

32 GND Ground

33 CH4CLK- Fourth pixel Negative LVDS differential clock input.

34 CH4CLK+ Fourth pixel Positive LVDS differential clock input.

(4)

(4)

(4)

35 GND Ground

36 CH4[3]- Fourth pixel Negative LVDS differential data input. Pair 3

37 CH4[3]+ Fourth pixel Positive LVDS differential data input. Pair 3

38 CH4[4]- Fourth pixel Negative LVDS differential data input. Pair 4

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ) :( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

(4)

Page 20

!!!"#$%&'( )!*&+,+&-'+#.(

39 CH4[4]+ Fourth pixel Positive LVDS differential data input. Pair 4

40 GND Ground

41 GND Ground

CON2 Connector Pin Assignment (LM123S010HTF13Y)

1 N.C. No Connection

2 N.C. No Connection

3 N.C. No Connection

4 GND Ground

5 N.C. No Connection

6 L/R_O Output signal for Left Right Glasses control

7 N.C. No Connection

8 N.C. No Connection

9 N.C. No Connection

10 N.C. No Connection

Note (1) Reserved for internal use. Please leave it open.

Note (2) The definition of L/R_O signal as follows

L= 0V, H=+3.3V

L/R_O Note

L Right glass turn on

H Left glass turn on

Note (3) LVDS format selection.

L= Connect to GND, H=Connect to +3.3V or Open

SELLVDS Note

L JEIDA Format

H or Open VESA Format

Note (4) LVDS Data Mapping

LVD S 4-p ort F HD 10 0/12 0Hz Inpu t

(1)

!

(1)

(2)

(1)

Port Channel of LVDS Data Stream

1st Port First Pixel 1, 5, 9, 1913, 1917

2nd Port Second Pixel 2, 6, 10, .1914, 1918

3rd Port Third Pixel 3, 7, 11, .1915, 1919

4th Port Fourth Pixel 4, 8, 12, .1916, 1920

LVD S 2po rt FH D 50 /60Hz Inp ut

Port Channel of LVDS Data Stream

1st Port First Pixel 1, 3, 5, 1917, 1919

2nd Port Second Pixel 2, 4, 6, .1918, 1920

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 +( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 21

LVD S 4-p ort Q FHD 2 4/30 Hz I nput

Port Channel of LVDS Data Stream

1st Port First Pixel 1, 5, 9, 3833, 3837

2nd Port Second Pixel 2, 6, 10, .3834, 3838

3rd Port Third Pixel 3, 7, 11, .3835, 3839

4th Port Fourth Pixel 4, 8, 12, .3836, 3840

Note (5) 2D/3D mode selection.

L= Connect to GND or Open, H=Connect to +3.3V

2D/3D Note

L or Open 2D Mode

H 3D Mode

Note (6) Input signal for left and right eye frame synchronous

V

=0~0.7 V, VIH=2.7~3.3 V

IL

L/R Note

L Right synchronous signal

H Left synchronous signal

!!!"#$%&'( )!*&+,+&-'+#.(

Note (7) Local dimming enable selection.

L= Connect to GND!H=Connect to +3.3V or Open

LD_EN Note

L Local Dimming Disable

H or Open Local Dimming Enable

Note (8) Reserved for internal use. Open is preferred. However, it is also acceptable to reserve the wire connecting with

specific High/Low voltage level.

Note (9) Interface optional pin has internal scheme as following diagram. Customer should keep the interface voltage level

requirement which including panel board loading as below.

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 )( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 22

System Board

!!!"#$%&'( )!*&+,+&-'+#.(

3.3V

10K ohm

1K ohm

IC

Interface Voltage Level

V

> V

H

IH

VL < V

IL

Note (10) Interface optional pin has internal scheme as following diagram. Customer should keep the interface voltage level

requirement which including panel board loading as below.

Panel Board

Panel Board System Board

1K ohm

IC

Interface Voltage Level

V

> V

H

IH

VL < V

IL

10K ohm

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 2( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 23

!!!"#$%&'( )!*&+,+&-'+#.(

Note (11) LVDS connector pin order defined as follows

Note (12) LVDS connector mating dimension range request is 0.93mm~1.0mm as below

5.2 BACKLIGHT UNIT

The pin configuration for the housing and leader wire is shown in the table below.

CN2: FF01-430-123A(FCN) or 196388-12041-3(P-TWO).

Pin № Symbol Feature

1 VLED+

2 VLED+

3 VLED+

4 NC NC

5 VLED-

6

7

8

9

10

11

12

VLED-

VLED-

VLED-

VLED-

VLED-

VLED-

VLED-

Positive of LED String

Negative of LED String

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 5( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 24

5.3 CONVERTER UNIT

CN1 (Header) : JH2-D4-143N(FCN) or CI0114M1HR0-LA (CvilLux)

Pin No. Symbol Feature

1

2

!!!"#$%&'( )!*&+,+&-'+#.(

3

4

5

6

7

8

9

10

11

12 BLON BL ON/OFF

13 NC NC

14

Note (1) If Pin14 is open, E_PWM is 100% duty.

Note (2) Input connector pin order defined as follows

VBL +24V

GND GND

ERR Normal (GND) ; Abnormal (Open collector)

E_PWM External PWM Control

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 6( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 25

5.4 LVDS INTERFACE

JEIDA Format : SELLVDS = L

VESA Format : SELLVDS = H or Open

VESA Format

!!!"#$%&'( )!*&+,+&-'+#.(

Current Cycle

AR 0P

AR 0N

AR 1P

AR 1N

AR 2P

AR 2N

AR 3P

AR 3N

AR 4P

AR 4N

JEIDA Format

AR 0P

AR 0N

AR 1P

AR 1N

AR0

AG1

AB2

AR6

AR4

AG5

AG0 AR5

AB1

DE VS HS AB5 AB4 AB3 AB2

REV AB7 AB6 AG7 AG6 AR7 AR6

REV AB9 AB8 AG9 AG8 AR9 AR8AR8 REV

AG4 AR7

AB5

AB0 AG5 AG4 AG3 AG2 AG1

AB4 AG7 AG6 AG5AG9 AG8

AR4 AR3 AR2 AR1 AR0

AR6 AR5 AR4AR9 AR8

AG0

AB1

DE

REV

AG4

AB5

AR 2P

AR 2N

AR 3P

AR 3N

AR 4P

AR 4N

R0~R9: Pixel R Data (9; MSB, 0; LSB)

G0~G9: Pixel G Data (9; MSB, 0; LSB)

B0~B9: Pixel B Data (9; MSB, 0; LSB)

DE : Data enable signal

DCLK : Data clock signal

Notes: (1) RSVD (reserved) pins on the transmitter shall be “H” or “L”.

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 7( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

AB6

AR2

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

DE VS HS AB7 AB6AB9 AB8

REV AB3 AB2 AG3 AG2 AR3 AR2

REV AB1 AB0 AG1 AG0 AR1 AR0AR0 REV

DE

REV

Page 26

!!!"#$%&'( )!*&+,+&-'+#.(

5.5 COLOR DATA INPUT ASSIGNMENT

The brightness of each primary color (red, green and blue) is based on the 10-bit gray scale data input for the color.

The higher the binary input the brighter the color. The table below provides the assignment of color versus data

input.

Data Signal

Color

R9 R8 R7 R6 R5 R4 R3 R2 R1 R0 G9 G8 G7 G6 G5 G4 G3 G2 G1 G0 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0

Basic

Colors

Gray

Scale

Of

Red

Gray

Scale

Of

Green

Gray

Scale

Of

Blue

Black

Red

Green

Blue

Cyan

Magenta

Ye ll ow

White

Red (0) / Dark

Red (1)

Red (2)

:

:

Red (1021)

Red (1022)

Red (1023)

Green (0) / Dark

Green (1)

Green (2)

:

:

Green (1021)

Green (1022)

Green (1023)

Blue (0) / Dark

Blue (1)

Blue (2)

:

:

Blue (1021)

Blue (1022)

Blue (1023)

0

0

1

1

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

0

0

0

0

0

0

Note (1) 0: Low Level Voltage!1: High Level Voltage

Red Green Blue

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

0

0

0

:

:

1

1

1

0

0

0

:

:

0

0

0

0

0

0

:

:

0

0

0

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

1

:

:

:

:

:

:

1

1

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

1

1

1

1

1

1

0

0

0

1

0

0

0

0

0

:

:

:

:

:

:

1

0

0

0

0

0

1

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

1

1

0

1

1

0

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

1

0

0

0

1

1

1

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

1

1

1

0

0

0

1

1

1

0

0

0

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

1

1

1

1

0

0

1

1

1

0

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

;

0

0

0

0

0

0

0

0

0

0

0

0

1

0

0

0

0

1

:

:

:

:

:

:

1

0

0

1

0

0

1

1

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

1

0

0

1

0

0

1

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

0

0

0

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

0

0

0

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

0

0

0

1

1

1

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

:

:

:

:

:

:

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

:

:

:

:

:

:

1

0

1

1

1

0

1

1

1

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 23( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/( 01#*234(2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 27

!!!"#$%&'( )!*&+,+&-'+#.(

6. INTERFACE TIMING

6.1 INPUT SIGNAL TIMING SPECIFICATIONS

The input signal timing specifications are shown as the following table and timing diagram. (Ta = 25 ± 2 ºC)

Signal Item Symbol Min. Typ. Max. Unit Note

Input cycle to

T

- - 200 ps (1)

cycle jitter

rcl

LVD S

Spread s pec trum

Receiver

modulation range

clkin_mod

F

F

-1.5% - F

clkin

+1.5% MHz

clkin

Clock

Spread s pec trum

modulation frequency

F

SSM

- - 66 KHz

LVD S

Receiver

Receiver skew margin T

RSKM

-400 - 400 ps (3)

Data

6.1.1 Input Timing Spec for FHD, Frame Rate = 50Hz

Signal Item Symbol Min. Typ. Max. Unit Note

F

LVD S Cloc k Fre quenc y

clkin

(=1/TC)

60 74.25 79 MHz (4)

Frame Rate 2D Mode Fr 47 50 53 Hz (5)

Total T v 11 04 1350 1 39 5 Th Tv= Tv d+ Tv b

(2)

Ver t ical

Active

Display

Term

Horizontal

Active

Display

Term

2D Mode

Display Tvd 1080 Th

Blank Tvb 24 270 315 Th

Front porch Tvfp 10

Back porch Tvbp 10

Vsync Tvswid 4

!!

!!

!!

Th

Th

Th

(6)

Total T h 1 06 0 110 0 1340 Tc T h= Th d+ Th b

Display Thd 960 Tc

Blank Thb 100 140 380 Tc

Front porch Thfp 5

Back porch Thbp 5

Hsync Thswid 2

!!

!!

!!

Tc

Tc

Tc

(6)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 28( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-."(/(01 #*23 4(2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 28

!!!"#$%&'( )!*&+,+&-'+#.(

6.1.2 Input Timing Spec for FHD, Frame Rate = 60Hz

Signal Item Symbol Min. Typ. Max. Unit Note

F

LVD S Cloc k Fre quenc y

Frame Rate 2D Mode Fr 57 60 63 Hz (5)

Total T v 1104 112 5 139 5 T h T v= Tvd+T vb

clkin

(=1/TC)

60 74.25 79 MHz (4)

Ver t ical

Active

Display

Term

2D Mode

Horizontal

Active

Display

Term

6.1.3 Input Timing Spec for FHD, Frame Rate = 100Hz

Signal Item Symbol Min. Typ. Max. Unit Note

Display Tvd 1080 Th

Blank Tvb 24 45 315 Th

Front porch Tvfp 10

Back porch Tvbp 10

Vsync Tvswid 4

Total T h 1 06 0 110 0 1340 Tc T h= Th d+ Th b

Display Thd 960 Tc

Blank Thb 100 140 380 Tc

Front porch Thfp 5

Back porch Thbp 5

Hsync Thswid 2

!!

!!

!!

!!

!!

!!

Th

Th

Th

Tc

Tc

Tc

(6)

(6)

F

LVD S Cloc k Fre quenc y

Frame Rate 2D Mode Fr 97 100 103 Hz (5)

2D Mode

Ver t ical

Active

Display

Term

Horizontal

Active

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 9( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Total T v 11 04 1350 1 39 5 Th Tv= Tv d+ Tv b

Display Tvd 1080 Th

Blank Tvb 24 270 315 Th

Front porch Tvfp 10

Back porch Tvbp 10

Vsync Tvswid 4

Total T h 5 30 5 50 670 Tc Th=T hd +T hb

Display Thd 480 Tc

clkin

(=1/TC)

60 74.25 79 MHz (4)

!!

!!

!!

Th

Th

Th

(6)

Page 29

!!!"#$%&'( )!*&+,+&-'+#.(

Display

Term

6.1.4 Input Timing Spec for FHD, Frame Rate = 120Hz

Signal Item Symbol Min. Typ. Max. Unit Note

LVD S Cloc k

Frame Rate

2D Mode

Blank Thb 50 70 190 Tc

Front porch Thfp 5

Back porch Thbp 5

Hsync Thswid 2

2D Mode 60 74.25 79 MHz

3D Mode

2D Mode 117 1 2 0 123 H z

3D Mode

Total T v 1104 112 5 139 5 T h Tv= Tv d+ Tv b

Display Tvd 1080 Th

Blank Tvb 24 45 315 Th

Front porch Tvfp 10

F

clkin

(=1/TC)

F

r

!!

!!

!!

74.25 MHz

120 Hz

!!

Tc

Tc

Tc

Th

(6)

(4)

(5)

Ver t ical

Active

Display

Term

Horizontal

Active

Display

Term

3D Mode

2D Mode

Back porch Tvbp 10

Vsync Tvswid 4

Total T v 1125 Th

Display Tvd 1080 Th

Blank Tvb 45 Th

Front porch Tvfp 10

Back porch Tvbp 10

Vsync Tvswid 4

Total T h 53 0 5 50 6 70 Tc T h= Th d+ Th b

Display Thd 480 Tc

Blank Thb 50 70 190 Tc

Front porch Thfp 5

Back porch Thbp 5

Hsync Thswid 2

!!

!!

!!!

!!!

!!!

!!

!!

!!

Th

Th

Tc

Tc

Tc

(6)

(6)

(6)

3D Mode

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 2 :( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Total T h 5 30 5 50 670 Tc T h=Thd +T hb

Page 30

!!!"#$%&'( )!*&+,+&-'+#.(

Display Thd 480 Tc

Blank Thb 50 70 190 Tc

Front porch Thfp 5

Back porch Thbp 5

Hsync Thswid 2

!!

!!

!!

Tc

Tc

Tc

6.1.5 Input Timing spec for QFHD, Frame Rate = 24Hz

Signal Item Symbol Min. Typ. Max. Unit Note

F

LVD S Cloc k Fre quenc y

clkin

(=1/TC)

60 74.25 79 MHz (4)

Frame Rate 2D Mode Fr 23 24 25 Hz (5)

Total T v 2208 2 25 0 24 50 T h T v=T vd +T vb

Ver t ical

Active

Display

Display Tvd 2160 Th

Blank Tvb 48 90 290 Th

Front porch Tvfp 20

!!

Th

Term

Back porch Tvbp 20

!!

Th

(6)

(6)

Vsync Tvswid 8

!!

Th

2D Mode

Total T h 9 92 13 75 1440 Tc T h= Th d+ Th b

Horizontal

Active

Display

Term

Display Thd 960 Tc

Blank Thb 32 415 480 Tc

Front porch Thfp 12

Back porch Thbp 10

Hsync Thswid 4

!!

!!

!!

Tc

Tc

Tc

6.1.6 Input Timing spec for QFHD, Frame Rate = 30Hz

Signal Item Symbol Min. Typ. Max. Unit Note

F

LVD S Cloc k Fre quenc y

clkin

(=1/TC)

60 74.25 79 MHz (4)

Frame Rate 2D Mode Fr 29 30 31 Hz (5)

Ver t ical

2D Mode

Total T v 2208 2 25 0 24 50 T h T v=T vd +T vb

Active

Display Tvd 2160 Th

(6)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 +( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 31

!!!"#$%&'( )!*&+,+&-'+#.(

Display

Term

Horizontal

Active

Display

Term

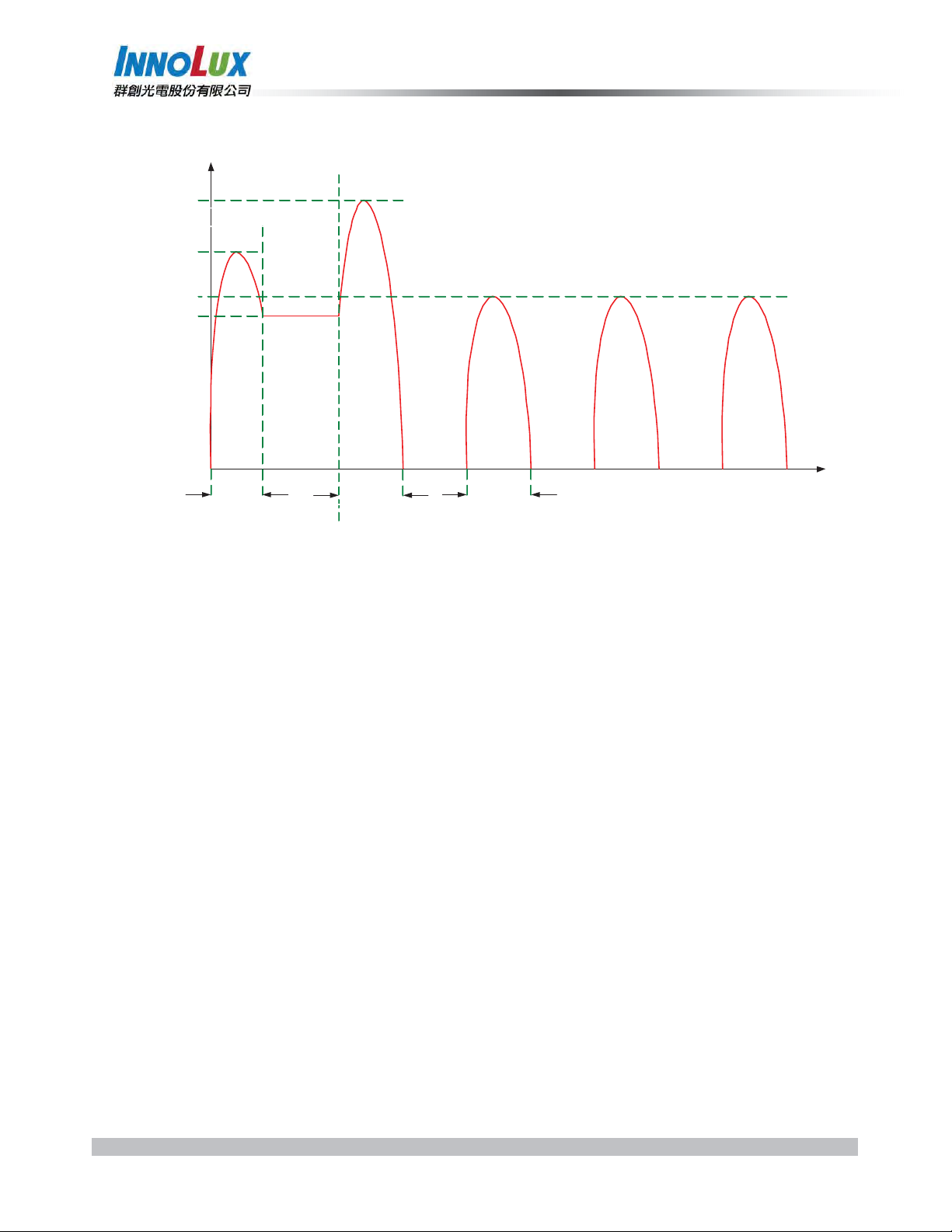

Note (1) The input clock cycle-to-cycle jitter is defined as below figures. Trcl ="T1 – T#

Blank Tvb 48 90 290 Th

Front porch Tvfp 20

Back porch Tvbp 20

Vsync Tvswid 8

Total T h 9 92 11 00 1340 Tc T h= Th d+ Th b

Display Thd 960 Tc

Blank Thb 32 140 380 Tc

Front porch Thfp 12

Back porch Thbp 10

Hsync Thswid 4

!!

!!

!!

!!

!!

!!

Th

Th

Th

Tc

Tc

Tc

(6)

(6)

Note (2) The SSCG (Spread spectrum clock generator) is defined as below figures.

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 )( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 32

!!!"#$%&'( )!*&+,+&-'+#.(

Note (3) The LVDS timing diagram and the receiver skew margin is defined and shown in following figure.

Tc

RXCLK+/-

RXn+/-

T

RSKM

Note (4) Please make sure the range of pixel clock has follow the below equations.

Fclkin (max) " (Fr Tv Th##) Fclkin(min)"

Note (5)

a. The frame-to-frame jitter of the input frame rate is defined as the following figure.

b. FRn = FRn-1 ± 1.8%.

Note (6)

c. Hsync and Vsync signals are necessary for this module.

d. The polarity of Hsync & Vsync should be positive.

e. Please follow the input signal timing diagram as below :

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 2( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 33

!!!"#$%&'( )!*&+,+&-'+#.(

6.2 POWER ON/OFF SEQUENCE

(Ta = 25 ± 2 ºC)

To p re ve nt a l at ch -u p or D C ope ra ti on of L CD mod ul e, th e po wer on /off s eq ue nc e sho ul d b e as th e dia gr am

below.

0.9Vcc

0.1VCC

T2

0.5!T1!10ms

0!T2!200ms

0!T3

500ms !T4

LVDS Signals

0V

0V

Power On

0$T7$T2

0$T8$T3

T7

Option Signals

(SELLVDS,2D/3D, LD EN)

500ms!T9

Host I2C Command

0.9Vcc

0.1Vcc

T3T1

T4

Power Off

T8

T9

Backlight (Recommended)

50%

50%

1000ms$T5

100ms$T6

T5

T10

Vcc

6

T

Vcc Dip

T10$10ms

Vcc(typ.) x 0.85

0V

Note (1) The supply voltage of external system for the module input should follow the definition of Vcc.

Note (2) Apply the lamp voltage within the LCD operation range. When the backlight turns on before the LCD operation or the

LCD turns off before the backlight turns off, the display may momentarily become abnormal screen.

Note (3) In case of VCC=off, please keep the level of input signals on the low or high impedance.

Note (4) T4 should be measured after the module has been fully discharged between power off and on period.

Note (5) Interface signal shall not be kept at high impedance when the power is on.

Note (6) Vcc must decay smoothly when power-off.

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 5( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 34

!!!"#$%&'( )!*&+,+&-'+#.(

7. OPTICAL CHARACTERISTICS

7.1 TEST CONDITIONS

Item Symbol Value Unit

Ambient Temperature Ta

Ambient Humidity Ha

Supply Voltage V

Input Signal According to typical value in "3. ELECTRICAL CHARACTERISTICS"

Ver t ical Fra m e Ra te Fr 120 Hz

The LCD module should be stabilized at given temperature for 1 hour to avoid abrupt temperature change during

measuring in a windless room.

Local Dimming Function should be Disable before testing to get the steady optical characteristics (According to

5.1 CNF1 Connector Pin Assignment, Pin no. “42”)

LCD Module

LCD Panel

CC

25±2

50±10

12±1.2

o

C

%RH

V

Field of View = 1º

500 mm

CS - 2000

Light Shield Room

(Ambient Luminance < 2 lux)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 6( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 35

!!!"#$%&'( )!*&+,+&-'+#.(

7.2 OPTICAL SPECIFICATIONS

The relative measurement methods of optical characteristics are shown in 7.2. The following items should be

measured under the test conditions described in 7.1 and stable environment shown in 7.1.

Item Symbol Condition Min. Typ. Max. Unit Note

Contrast Ratio CR

3500 5000

Response Time Gray to gray

Center Luminance of

White

White Variation

2D

L

C

3D 60 - cd/m2Note (8)

δW

280 350

2D

Cross Talk CT

3D-W

3D-D

=0°, θY =0°

θ

Red

Rx

Ry

Gx

x

Viewing angle at

normal direction

Green

Gy

Typ.-

Bx

Color

Blue

0.03

By

Chromaticity

Wx

White

Wy

- - Note (2)

6.5 13

- cd/m

ms Note (3)

2

Note (4)

1.3 - Note (6)

- 4 % Note (5)

4 - % Note (8)

11 - % Note (8)

0.639

0.334

0.312

0.615

-

-

-

-

Typ.+

0.151

-

0.03

0.058

0.280

0.290

-

-

-

Correlated color temperature

9800

K

Color

C.G.

-

72

- % NTSC

Gamut

θx+

80 88

-

Horizontal

Viewing

Angle

θ

x

θY+

-

80 88

CR≥20

80 88

Deg. (1)

-

Ver t ical

θ

-

Y

80 88

-

Transmission direction of

the up polarizer

Φ

up

- - 90

-

Deg. (7)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 7( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 36

Note (1) Definition of Viewing Angle (θx, θy) :

Viewing angles are measured by Autronic Conoscope Cono-80 (or Eldim EZ-Contrast 160R).

!!!"#$%&'( )!*&+,+&-'+#.(

Normal

θx = θy = 0º

θy- θy+

θX- = 90º

6 o’clock

θ

y- = 90º

Note (2) Definition of Contrast Ratio (CR) :

The contrast ratio can be calculated by the following expression.

Contrast Ratio (CR) =

L1023: Luminance of gray level 1023

L 0: Luminance of gray level 0

CR = CR (5), where CR (X) is corresponding to the Contrast Ratio of the point X at the figure in Note (6).

Note (3) Definition of Gray-to-Gray Switching Time :

x-

y-

θx−

θx+

L0 of LuminanceSurface

12 o’clock direction

y+

θ

y+ = 90º

x+

θX+ = 90º

L1023of LuminanceSurface

The driving signal means the signal of gray level 0, 124, 252, 380, 508, 636, 764, 892 and 1023.

Gray to gray average time means the average switching time of gray level 0, 124, 252, 380, 508, 636, 764, 892 and 1023 to

each other.

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 3( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 37

Note (4) Definition of Luminance of White (LC) :

A

(

)

A

(

)

(

)

Measure the luminance of gray level 1023 at center point.

= L (5), where L (x) is corresponding to the luminance of the point X at the figure in Note (6).

L

C

Note (5) Definition of Cross Talk (CT) :

!!!"#$%&'( )!*&+,+&-'+#.(

CT = | Y

Where :

YA = Lu mi na nc e o f m ea su red lo cati on wi thout gray leve l 10 23 pa tte rn (c d/m 2)

YB = Luminance of measured location with gray level 1023 pattern (cd/m2)

(0, 0)

– YA | / YA× 100 (%)

B

ctive Area

Y

(D/2,W/8)

A,U

Gray 512

(D/8,W/2)

Y

A,L

(D/2,7W/8)

Y

A, D

Note (6) Definition of White Variation (δW):

Measure the luminance of gray level 1023 at 5 points

δW =

Y

(7D/8,W/2)

A, R

(5)] L (4), L (3), L (2), L (1),[L Minimum

D, W

(5)] L (4), L (3), L (2), L (1),[L Maximum

0, 0

(D/8,W/2)

Y

B, L

Y

(D/4,W/4)

Y

B, D

ctive Area

(D/2,W/8)

B, U

Gray 1023

Y

A, R

(D/2,7W/8)

(7D/8,W/2)

(3D/4,3W/4)

D, W

Horizontal Line

D

W

4

W

D

4

1 2

D

2

3D

4

X

5

Test point :

X = 1 ~ 5

2

3W

3 4

4

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 58( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ,-." (/(01#*23 4(2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 38

!!!"#$%&'( )!*&+,+&-'+#.(

Note (7) This is a reference for designing the shutter glasses of 3D application. Definition of the transmission direction of the up

polarizer (Φ

) on LCD Module :

up-P

x-

12 o’clock direction

y+

!

up-P

y-

6 o’clock

x

+

!=0

o

Up Polarizer

The transmission axis of the front polarizer of the shutter glasses should be parallel to this panel transmission direction to

get a maximum 3D mode luminance.

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 9( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 39

!!!"#$%&'( )!*&+,+&-'+#.(

Note (8) Definition of the 3D mode performance (measured under 3D mode, use INX’s shutter glass) :

a. Test pattern

Left eye image and right eye image are displayed alternated

WW

Left eye image: W1023; Right eye image: W1023

WB

Left eye image: W1023; Right eye image: W0

BW

Left eye image: W0; Right eye image: W1023

BB

Left eye image: W0; Right eye image: W0

b. Measurement setup

LCD Module

LCD Panel

Right Eye Shutter

CS - 2000

Field of View = 1º

500 mm

Shutter glasses are well controlled under suitable timing, and measure the luminance of the center point of the panel

through the right eye glass. The transmittance of the glass should be larger than 40.0% under 3D mode operation.

The luminance of the test pattern “WW”, denoted L(WW); the luminance of the test pattern ”WB”, denoted L(WB) ; the

luminance of the test pattern “BW”, denoted L(BW); the luminance of the test pattern “BB”, denoted “L(BB)

c. Definition of the Center Luminance of White, Lc (3D) : L(WW)

d. Definition of the 3D mode white crosstalk, CT (3D-W) :

Light Shield Room

(Ambient Luminance < 2 lux)

)3 (

WDCT ≡

BBLWBL

BBLWWL

)()(

)()(

)( )(

)3 (

e. Definition of the 3D mode dark crosstalk, CT (3D-D) :

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 5 :( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

DDCT ≡

BWLWWL

)()(

BBLWWL

Page 40

!!!"#$%&'( )!*&+,+&-'+#.(

8. PRECAUTIONS

8.1 ASSEMBLY AND HANDLING PRECAUTIONS

(1) Do not apply rough force such as bending or twisting to the module during assembly.

(2) It is recommended to assemble or to install a module into the user’s system in clean working areas. The

dust and oil may cause electrical short or worsen the polarizer.

(3) Do not apply pressure or impulse to the module to prevent the damage of LCD panel and backlight.

(4) Always follow the correct power-on sequence when the LCD module is turned on. This can prevent the

damage and latch-up of the CMOS LSI chips.

(5) Do not plug in or pull out the I/F connector while the module is in operation.

(6) Do not disassemble the module.

(7) Use a soft dry cloth without chemicals for cleaning, because the surface of polarizer is very soft and

easily scratched.

(8) Moisture can easily penetrate into LCD module and may cause the damage during operation.

(9) High temperature or humidity may deteriorate the performance of LCD module. Please store LCD

modules in the specified storage conditions.

(10) When ambient temperature is lower than 10ºC, the display quality might be reduced. For example, the

response time will become slow, and the starting voltage of LED will be higher than that of room

temperature.

8.2 SAFETY PRECAUTIONS

(1) The startup voltage of a backlight is over 1000 Volts. It may cause an electrical shock while assembling

with the inverter. Do not disassemble the module or insert anything into the backlight unit.

(2) If the liquid crystal material leaks from the panel, it should be kept away from the eyes or mouth. In case

of contact with hands, skin or clothes, it has to be washed away thoroughly with soap.

(3) After the module’s end of life, it is not harmful in case of normal operation and storage.

8.3 SAFETY STANDARDS

The LCD module should be certified with safety regulations as follows:

Regulatory Item Stand ard

UL UL60950-1:2006 or Ed.2:2007

Information Technology equipment

Audio/Video Apparatus

cUL CAN/CSA C22.2 No.60950-1-03 or 60950-1-07

CB IEC60950-1:2005 / EN60950-1:2006+ A11:2009

UL UL60065 Ed.7:2007

cUL CAN/CSA C22.2 No.60065-03:2006 + A1:2006

IEC60065:2001+ A1:2005 / EN60065:2002 + A1:2006+

CB

A11:2008

If the module displays the same pattern for a long period of time, the phenomenon of image sticking may be occurred.

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 6 +( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 41

!!!"#$%&'( )!*&+,+&-'+#.(

9. DEFINITION OF LABELS

9.1 INX MODULE LABEL

The barcode nameplate is pasted on each module as illustration, and its definitions are as following explanation.

V420DK1-LS1 Rev. XX

X X X X X X X Y M D L N N N N

Model Name : V420DK1-LS1

Revision : Rev. XX, for example: A0, A1 B1, B2 or C1, C2 etc.

Serial ID : X X X X X X X Y M D L N N N N

Serial No.

Product Line

Ye ar, Mo nt h, D at e

INX Internal Use

INX Internal Use

Revision

Serial ID includes the information as below:

Manufactured Date:

Year : 2001=1, 2002=2, 2003=3, 2004=4 2010=0, 2011=1, 2012=2

Month: 1~9, A~C, for Jan. ~ Dec.

Day: 1~9, A~Y, for 1st to 31st, exclude I ,O, and U.

Revision Code : Cover all the change

Serial No. : Manufacturing sequence of product

Product Line : 1→Line1, 2→Line 2, etc.

INX Internal Use

MADE N CHI NA

LEOO(CAPG/CANO/V RO)

RoHS

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 6 )( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 42

!!!"#$%&'( )!*&+,+&-'+#.(

9.2 CARTON LABEL

The barcode nameplate is pasted on each box as illustration, and its definitions are as following explanation.

P. O . N O .

Parts ID.

Model Name V420DK1-LS1

Carton ID.

XXXXXXXXXXXXXX

Made In Taiwan (Made In China)

Model Name: V420DK1– LS1

Carton ID: X X X X X X X Y M D X X X X

Serial ID includes the information as below :

Manufactured Date:

Year: 2010=0, 2011=1, 2012=2 etc.

Month: 1~9, A~C, for Jan. ~ Dec.

Day: 1~9, A~Y, for 1st to 31st, exclude I ,O, and U.

Revision Code: Cover all the change

Quantities

INX Internal Use

Ye ar, Mo nt h, D at e

INX Internal Use

Revision

INX Internal Use

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 6 2( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 43

10. PACKAGING

10.1 PACKAGING SPECIFICATIONS

(1) 6 LCD TV modules / 1 Box

(2) Box dimensions : 1035(L) X 309 (W) X 625 (H)

(3) Weight: approximately 48 Kg ( modules per box)

10.2 PACKAGING METHOD

Packaging method is shown in following figures.

!!!"#$%&'( )!*&+,+&-'+#.(

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 6 5( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 44

!!!"#$%&'( )!*&+,+&-'+#.(

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 6 6( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((

!"#$%&'()*+",$-#.&/+0$,&$1//&2345$6/($3/73,"&)*8#9$30#$*0$')&"*-*,#9$

Page 45

10.3 UN-PACKAGING METHOD

Un packaging method is shown as following figures.

!!!"#$%&'( )!*&+,+&-'+#.(

Put in Protective Tools

(provide by customer-self)

!"#$%&' ()*+( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( 6 7( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( ( , -."( /( 01#*234 (2+)5((((((((