Microcontroller

XMC4000 Application Kit

For XMC4000 Family

Board U ser‘s M a nual

Revision 1.0, 2014-01-10

CPU_45A-V3

CPU Board XMC4500 General Purpose

Edition 2014-01-10

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2014 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all

warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual

property rights of any third party.

Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest

Infineon Technologies Office (www.infineon.com).

Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in

question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the

failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life

support devices or systems are intended to be implanted in the human body or to support and/or maintain and

sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other

persons may be endangered.

CPU_45A-V3

CPU Board XMC4500 General Purpose

Template: IFX_Template_2011-02-24.dot

Revision History

Page or Item

Subjects (major changes since previous revision)

Revision V1.0,

2014-01-10

Initial release

Trademarks of Infineon Technologies AG

AURIX™, C166™, CanPAK™, CIPOS™, CIPURSE™, EconoPACK™, CoolMOS™, CoolSET™,

CORECONTROL™, CROSSAVE™, DAVE™, EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPIM™,

EiceDRIVER™, eupec™, FCOS™, HITFET™, HybridPACK™, I²RF™, ISOFACE™, IsoPACK™, MIPAQ™,

ModSTACK™, my-d™, NovalithIC™, OptiMOS™, ORIGA™, PRIMARION™, PrimePACK™, PrimeSTACK™,

PRO-SIL™, PROFET™, RASIC™, ReverSave™, SatRIC™, SIEGET™, SINDRION™, SIPMOS™,

SmartLEWIS™, SOLID FLASH™, TEMPFET™, thinQ!™, TRENCHSTOP™, TriCore™.

Other Trademarks

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™,

PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by

AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum.

COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™

of Epcos AG. FLEXGO™ of Microsoft Corporation. FlexRay™ is licensed by FlexRay Consortium.

HYPERTERMINAL™ of Hilgraeve Incorporated. IEC™ of Commission Electrotechnique Internationale. IrDA™

of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR

STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc.

MICROTEC™, NUCLEUS™ of Mentor Graphics Corporation. Mifare™ of NXP. MIPI™ of MIPI Alliance, Inc.

MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE

OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc.

Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of

Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd.

Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc.

TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company

Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments

Incorporated. VXWORKS™, WIND RIVER™ of WIND RIVER SYSTEMS, INC. ZETEX™ of Diodes Zetex

Limited.

Last Trademarks Update 2011-02-24

CPU_45A-V3

CPU Board XMC4500 General Purpose

Table of Contents

Board User's Manual 4 Revision 1.0, 2014-01-10

Table of Contents

Introduction ............................................................................................................................................................ 7

1 Overview ............................................................................................................................................. 7

1.1 Key Features ........................................................................................................................................ 7

1.2 Block Diagram ...................................................................................................................................... 8

2 Hardware Description ........................................................................................................................ 9

2.1 Power Supply ..................................................................................................................................... 10

2.2 Reset .................................................................................................................................................. 12

2.3 Clock Generation................................................................................................................................ 12

2.4 Boot Option ........................................................................................................................................ 13

2.5 Debug Interface .................................................................................................................................. 14

2.5.1 On-board USB Debugger ................................................................................................................... 14

2.5.2 Cortex Debug Connector (10-pin) ...................................................................................................... 15

2.5.3 Cortex Debug+ETM Connector (20-pin) ............................................................................................ 16

2.6 Serial Flash Memory .......................................................................................................................... 18

2.7 USB .................................................................................................................................................... 19

2.8 RTC .................................................................................................................................................... 21

2.9 User LEDs and User Buttons ............................................................................................................. 22

2.10 Potentiometer ..................................................................................................................................... 22

2.11 Satellite Connectors ........................................................................................................................... 23

2.11.1 COM Connector ................................................................................................................................. 24

2.11.2 HMI Connector ................................................................................................................................... 25

2.11.3 ACT Satellite Connector ..................................................................................................................... 26

3 Differences to Board Version V2 .................................................................................................... 27

4 Production Data................................................................................................................................ 27

4.1 Schematics ......................................................................................................................................... 27

4.2 Component Placement and Geometry ............................................................................................... 32

4.3 Bill of Material (BOM) ......................................................................................................................... 33

CPU_45A-V3

CPU Board XMC4500 General Purpose

List of Figures

Board User's Manual 5 Revision 1.0, 2014-01-10

List of Figures

Figure 1 CPU_45A-V3 Board Block Diagram..................................................................................................... 8

Figure 2 CPU Board XMC4500 General Purpose (CPU_45A-V3)..................................................................... 9

Figure 3 Powering option through USB interface (5 V) .................................................................................... 10

Figure 4 CPU_45A-V3 Board Power ................................................................................................................ 11

Figure 5 Battery (VBAT Supply) ....................................................................................................................... 11

Figure 6 Reset .................................................................................................................................................. 12

Figure 7 Reset LED and Reset Switch ............................................................................................................. 12

Figure 8 Clock Generation................................................................................................................................ 13

Figure 9 Boot Options Switch ........................................................................................................................... 13

Figure 10 On-Board USB Debugger .................................................................................................................. 14

Figure 11 Cortex Debug Connector (10-pin) ...................................................................................................... 15

Figure 12 Cortex Debug Connector (10-pin) Layout .......................................................................................... 15

Figure 13 Cortex Debug+ETM Connector (20-pin) ............................................................................................ 16

Figure 14 Cortex Debug+ETM Connector (20-pin) Layout ................................................................................ 17

Figure 15 Quad SPI Flash Interface Circuit ........................................................................................................ 18

Figure 16 Quad SPI Flash .................................................................................................................................. 18

Figure 17 USB Connector Schematic ................................................................................................................ 19

Figure 18 USB power generation - Host/OTG mode ......................................................................................... 19

Figure 19 Battery Holder for Coin Cell ............................................................................................................... 21

Figure 20 RTC .................................................................................................................................................... 21

Figure 21 GPIO LED .......................................................................................................................................... 22

Figure 22 Satellite Connectors ........................................................................................................................... 23

Figure 23 Satellite Connector Type COM .......................................................................................................... 24

Figure 24 Satellite Connector Type HMI ............................................................................................................ 25

Figure 25 Satellite Connector Type ACT ............................................................................................................ 26

Figure 26 Schematic of Satellite Connectors, USB-OTG ................................................................................... 28

Figure 27 Schematic of XMC4500 ..................................................................................................................... 29

Figure 28 Schematic of Power Supply, Debug Connectors, Reset Circuit ........................................................ 30

Figure 29 Schematic of On-board Debugger ..................................................................................................... 31

Figure 30 Component Placement and Geometry ............................................................................................... 32

CPU_45A-V3

CPU Board XMC4500 General Purpose

List of Figures

Board User's Manual 6 Revision 1.0, 2014-01-10

List of Tables

Table 1 Power status LED’s ............................................................................................................................ 10

Table 2 Power Measurement .......................................................................................................................... 11

Table 3 Boot Options Settings ........................................................................................................................ 13

Table 4 Cortex Debug Connector (10 Pin) ...................................................................................................... 15

Table 5 Cortex Debug+ETM Connector (20 Pin) ............................................................................................ 16

Table 6 Quad SPI Signals ............................................................................................................................... 18

Table 7 USB micro AB connector Pinout ........................................................................................................ 19

Table 8 GPIO LED .......................................................................................................................................... 22

Table 9 User Button ........................................................................................................................................ 22

Table 10 Potentiometer ..................................................................................................................................... 22

Table 11 Differences to older board versions ................................................................................................... 27

Table 12 BOM of CPU_45A-V3 Board .............................................................................................................. 33

CPU_45A-V3

CPU Board XMC4500 General Purpose

Overview

Board User's Manual 7 Revision 1.0, 2014-01-10

Introduction

This document describes the features and hardware details of the CPU Board XMC4500 General Purpose

(CPU_45A-V3) designed to work with Infineon’s XMC4500 Microcontroller. This board is part of Infineon’s

XMC4000 Application Kits.

1 Overview

The CPU board CPU_45A-V3 houses the XMC4500 Microcontroller and three satellite connectors (HMI, COM,

ACT) for application expansion. The board along with satellite cards (e.g. HMI_OLED-V1, COM_ETH-V1,

AUT_ISO-V1, MOT_GPDLV-V boards) demonstrates the capabilities of XMC4500. The main use case for this

board is to demonstrate the generic features of XMC4500 device including tool chain. The focus is safe

operation under evaluation conditions. The board is neither cost nor size optimized and does not serve as a

reference design.

1.1 Key Features

The CPU_45A-V3 board is equipped with the following features

XMC4500 (ARM® Cortex™-M4-based) Microcontroller, 120 MHz CPU clock, 1 MByte on-chip Flash, 160

kByte RAM, LQFP-144,

Connection to XMC4500 satellite cards via satellite connectors COM, HMI and ACT

USB OTG Host/Device support via micro USB connector

Debug options

− On-board Debugger via Debug USB connector

− Cortex Debug connector 10-pin (0.05”)

− Cortex Debug+ETM connector 20-pin (0.05”)

Reset push button

32 MBit quad SPI flash memory

Boot option switch

PowerScale Connector: Ready for MCU power consumption analysis

5 LED’s

3 Power indicating LED’s

1 User LEDs (P3.9)

1 RESET LED

1 Debug LED

User Button connected to P2.15

Potentiometer, connected to analog input P14.1

Power supply

− Via Micro-USB connector in USB device mode

− Via satellite connector pins (COM/ACT satellites cards can supply power to CPU board)

− Via Debug USB connector

− RTC backup battery

CPU_45A-V3

CPU Board XMC4500 General Purpose

Overview

Board User's Manual 8 Revision 1.0, 2014-01-10

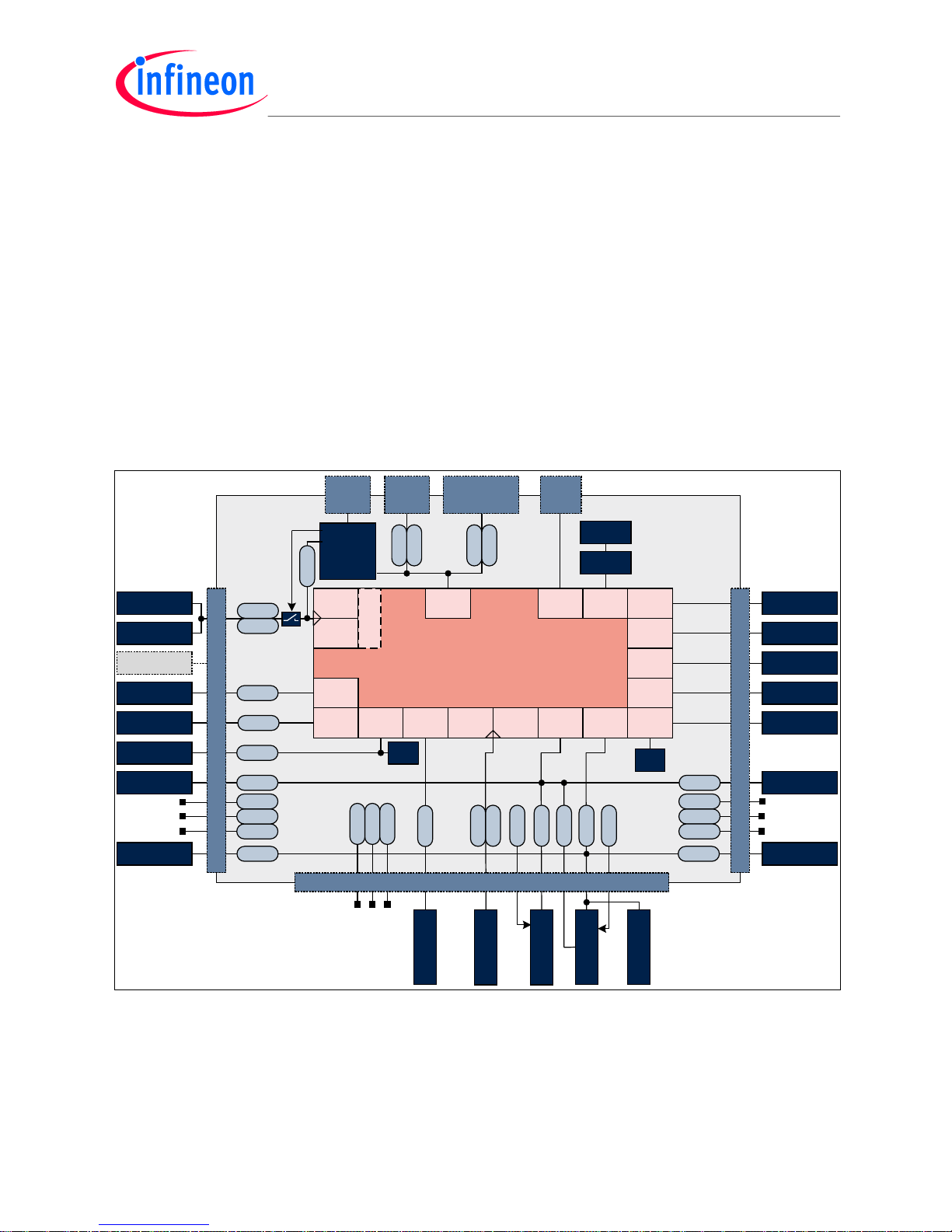

1.2 Block Diagram

Figure 1 shows the functional block diagram of the CPU_45A-V3 board. For more information about the power

supply please refer to chapter 2.1.

The CPU board has got the following building blocks:

- 3 Satellite Connectors (COM, HMI ACT)

- On-board Debugger via Debug USB connector (Micro-USB)

- User LED connected to P3.9

- User Button connected to P2.15

- Quad SPI flash memory (EE) connected to USIC1 Channel1 with Chip-Select1

- 2 Cortex Debug Connectors

- Variable resistor (POTI) connected to GPIO P14.1

- USB On-The-Go Connector (Micro-USB)

EE

XMC4500

LQFP144

EE

2xISOFACE

QSPI

I2C

CAN CAN2

CAPCOM

ENCODER

DSMOD

SENSOR

OPAMP

LED

TS

TOUCH

2x TS

U1C0

CPU Board XMC4500

General Purpose

CPU_45A-V3

U1C1

2xCS

ETH

ETHRMII

USB

OTG

USB

CCU

4/8

POSIF

DSD

DAC

ADC

GPIO

reset

QSPI

RS485

CAN

CAN

I2C_IOEX

Debug+ETM

20pin

I2C_IOEX

ACT

GPIO

GPIO

GPIO

GPIO

GPIO

CAN

UART

I2S

U2C1

SDCARD

U0C1

4xCS

GPIO

cmd

OLED

I2C_IOEX

JTAG

SWD

SWD

SWV

SDMMC

HEADSET

U0C0

CAN1

BSL

SWV

2xGPIO

POTI

SPI

I2C

GPIO

GPIO

SPI

SPI

GPIO

I2C

SPI

SD

SPI

GPIO

HMI

EXTBUS

COM

Debug

10pin

Debug

USB

On-board

Debugger

XMC4200

Button

LED

UART

Block_Diag.emf

Figure 1 CPU_45A-V3 Board Block Diagram

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 9 Revision 1.0, 2014-01-10

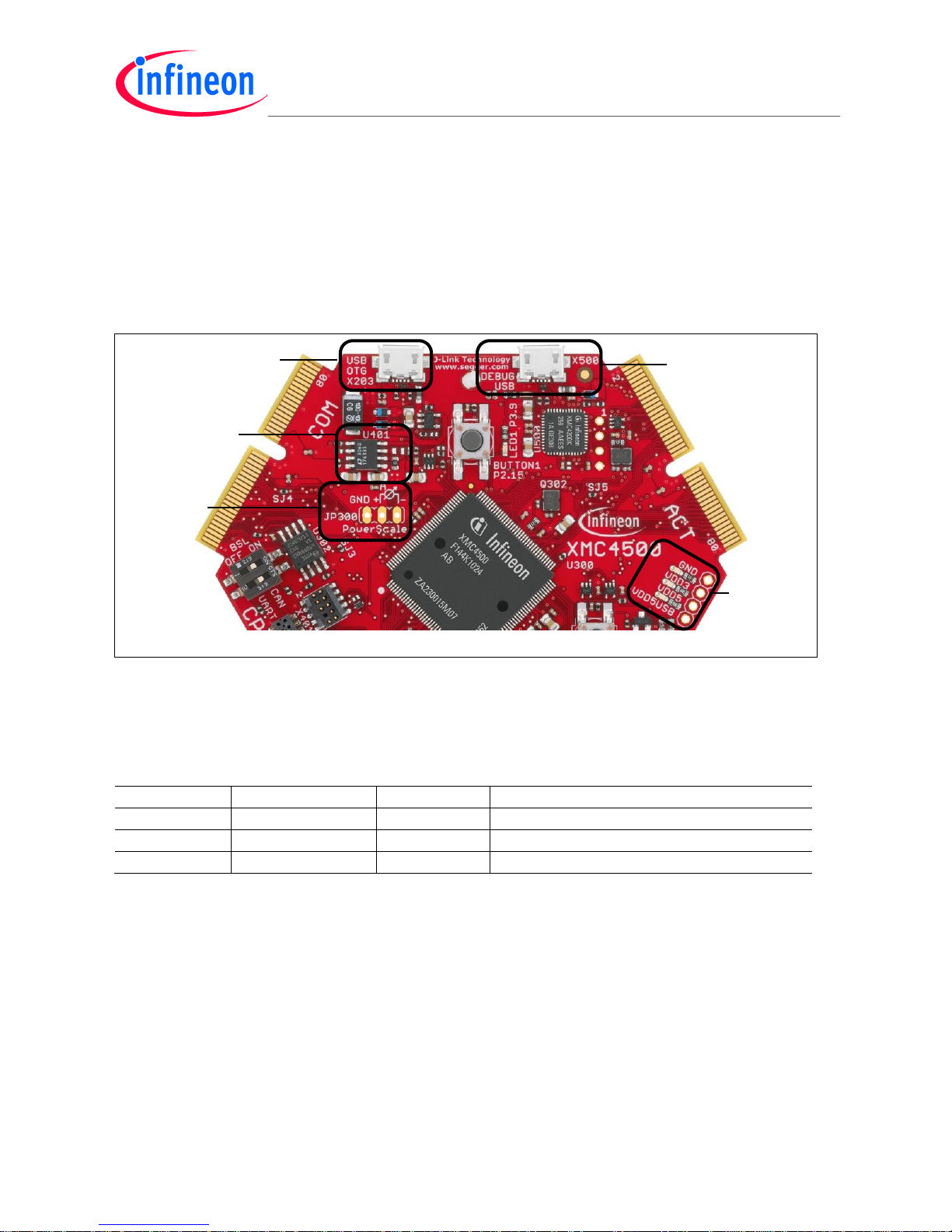

2 Hardware Description

The following sections give a detailed description of the hardware and how it can be used.

5V to 3.3V

Voltage

Regulator

Debug USB

Connector

On-board

Debugger

ACT

Satellite

Connector

Power

indicating

LEDs

Reset

Circuit

HMI Satellite

Connector

Battery

Holder

Potentiometer

Debug

Connectors

XMC4500

CPU

Boot

Option

Switch

User LEDs

and User

Buttons

Serial

Quad-SPI

Flash

Board_Interfaces.emf

COM Satellite

Connector

Figure 2 CPU Board XMC4500 General Purpose (CPU_45A-V3)

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 10 Revision 1.0, 2014-01-10

2.1 Power Supply

The CPU_45A-V3 board can be powered via the USB plug (5 V); however, there is a current limit that can be

drawn from the host PC through USB. If the CPU_45A-V3 board is used to drive other satellite cards (e.g.

AUT_ISO-V1 or MOT_GPDLV-V2) and the total current required exceeds 500 mA, then the board needs to be

powered by either an external power supply connected to USB or by a satellite card, which supports external

power supply like e.g. AUT_ISO-V1, MOT_GPDLV-V2, COM_ETH-V1.

For powering the board through USB interface, connect the USB cable provided with the kit to the Micro-USB

connector on board.

USB OTG

Debug USB

Power.emf

IFX1763

3.3V Linear

LDO Voltage

Regulator

PowerScale

Probe

Power

indicating

LEDs

Figure 3 Powering option through USB interface (5 V)

To indicate the power status of CPU_45A-V3 board three LED’s are provided on board (See Figure 3). The LED

will be “ON” when the corresponding rail is powered.

Table 1 Power status LED’s

LED Reference

Power Rail

Voltage

Note

V401

VDD5

5 V

Must always be “ON”

V402

VDD5USB

5 V

“ON” if powered by USB plug

V403

VDD3.3

3.3 V

Must always be “ON”

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 11 Revision 1.0, 2014-01-10

CPU Board XMC4400 General Purpose

CPU_45A-V3

ACT Sat.

Connector

COM Sat.

Connector

HMI Sat.

Connector

Debug

USB

VDD5USB

Lin. Voltage

Regulator

IFX1763

VDDP

U403

U401

JP300

U300

EN

Power

LED

HIB_IO_1

P3.2

VDD5 VDD5 VBAT

XMC4500

LQFP144

BATTERY

VDD3.3

On Board Devices

VDD3.3

Power_Block.emf

USB

OTG

Power

LED

Power

LED

VDD5USB +5V VDD5 +5V VDD3.3 +3.3V

Figure 4 CPU_45A-V3 Board Power

Battery

Holder

Battery.emf

Figure 5 Battery (VBAT Supply)

Hitex PowerScale probe is provided on the CPU_45A-V3 board to measure the power consumption.

Table 2 Power Measurement

Jumper

Function

Description

JP300

PowerScale

A Hitex PowerScale probe can be connected for current sensing the

VDD3.3 (CPU power source). Default: pos. 1-2 (closed)

Note: On the PCB there is a shorting trace between pin 1-2. This trace has

to be cut first, before using PowerScale. Pin 3 is GND.

The maximum current drawn by the CPU board without any satellite cards connected is about 150 mA.

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 12 Revision 1.0, 2014-01-10

2.2 Reset

The reset pin (PORST#) of the XMC45000 is a bi-directional pin. An internal pull-up resistor will keep the

PORST# pin high during normal operation. A low level at this pin will force a hardware reset. In case of an

internal reset the PORST# pin will drive a low signal. An internal circuit of the XMC4500 ensures a save Poweron-Reset. XMC4500 does not require any additional external components to generate a reset signal during

power-up. An on-board reset button (SW400, RESET) supports a hardware reset of the CPU during operation.

The reset signal is also routed to all satellite connectors. The reset state is indicated by a red LED (V407). The

LED will be “ON” during reset state and will be “OFF” during normal operation conditions.

Figure 6 Reset

Reset Button

Reset LED

RST.emf

Figure 7 Reset LED and Reset Switch

2.3 Clock Generation

An external 12 MHz crystal provides the clock signal to the XMC4500 microcontroller. The drive strength of the

oscillator is set to maximum by software, in order to ensure a safe start-up of the oscillator even under worst

case conditions. A serial 510 Ohm resistor will attenuate the oscillations during operations.

For the RTC clock a separate external 32.768 kHz crystal is used on board.

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 13 Revision 1.0, 2014-01-10

Figure 8 Clock Generation

2.4 Boot Option

During power-on-reset the XMC4500 latches the dip switch SW300 settings via the TCK and the TMS pin.

Based on the values latched different boot options are possible.

Table 3 Boot Options Settings

BSL (TMS)

CAN/UART (TCK)

Boot Option

OFF (1)

UART (0)

Normal Mode (Boot from flash)

ON (0)

UART (0)

ASC BSL Enabled (Boot from UART)

OFF (1)

CAN (1)

BMI Customized Boot Enabled

ON (0)

CAN (1)

CAN BSL Enabled (Boot from CAN)

Boot

Option

Switch

Boot_Switch.emf

Figure 9 Boot Options Switch

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 14 Revision 1.0, 2014-01-10

2.5 Debug Interface

The CPU_45A-V3 board supports JTAG debug via 3 different connectors.

On-board Debugger

Cortex Debug Connector (10-pin)

Cortex Debug+ETM Connector (20-pin)

The Hexagon Application Boards are designed to use “Serial Wire Debug” as debug interface. JTAG is not

supported by default because the GPIO P0.7 (TDI), where the required TDI function is mapped to, is used by

various Actuator boards connected to the ACT satellite connector.

Note: It is strongly recommended not to use JTAG debug mode, especially if satellites boards are

connected, which uses the GPIO 0.7. For the same reason also do not use the on-board debugger in

JTAG mode.

If you want to use the JTAG debug mode through the cortex debug connectors (X400, X401) anyway, enable

the JTAG interface of the XMC device by assembling the pull-up resistor R427 (4k7 Ohm) and the resistor R410

(0 - 33 Ohm).

2.5.1 On-board USB Debugger

The on-board debugger supports

Serial Wire Debug

Serial Wire Viewer

Full Duplex UART communication via a USB Virtual COM

The on-board debugger can be accessed through the Debug USB connector shown in Figure 10. The Debug

LED V502 shows the status during debugging.

Debugger.emf

Debug USB

On-board

Debugger

Debug LED

Figure 10 On-Board USB Debugger

When using an external debugger connected to the 10-pin/20-pin Cortex Debug Connector, the on-board

debugger is switched off.

When using the USB virtual COM port function of the on-board debugger the UART interface to the COM

satellite is disabled through the switches U301 and U303.

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 15 Revision 1.0, 2014-01-10

2.5.2 Cortex Debug Connector (10-pin)

The CPU_45A-V3 board supports Serial Wire debug operation and Serial Wire viewer operation (via the SWO

signal when Serial Wire debug mode is used) through the 10-pin Cortex Debug Connector.

When using an external debugger connected to the 10-pin Cortex Debug Connector, the on-board debugger is

switched off.

Cortex Debug

Connector (10-pin)

GNDDetect

SWDIO / TMS

SWDCLK / TCK

1 2

3 4

5 6

7 8

9 10

VCC

GND

GND

KEY

SWO / TDO

NC / TDI

nRESET

cortex-10pin.emf

Figure 11 Cortex Debug Connector (10-pin)

Table 4 Cortex Debug Connector (10 Pin)

Pin No.

Signal Name

Serial Wire Debug

JTAG Debug

1

VCC

+3.3 V

+3.3 V

2

SWDIO / TMS

Serial Wire Data I/O

Test Mode Select

3

GND

Ground

Ground

4

SWDCLK / TCK

Serial Wire Clock

Test Clock

5

GND

Ground

Ground

6

SWO / TDO

Trace Data OUT

Test Data OUT

7

KEY

KEY

KEY

8

NC / TDI

Not connected

Test Data IN

9

GNDDetect

Ground Detect

Ground Detect

10

nRESET

Reset (Active Low)

Reset (Active Low)

Cortex Debug

Connector (10 Pin)

10Pin_Conn.emf

Figure 12 Cortex Debug Connector (10-pin) Layout

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 16 Revision 1.0, 2014-01-10

2.5.3 Cortex Debug+ETM Connector (20-pin)

The CPU_45A-V3 board supports Serial Wire debug operation, Serial Wire viewer operation (via SWO

connection when Serial Wire debug mode is used) and Instruction Trace operation through the 20-pin Cortex

Debug+ETM Connector.

JTAG operation additionally would require the TDI (P0.7) signal. By default the TDI signal is disconnected from

the Cortex Debug Connectors by a not assembled resistor R410, because the pin P0.7 is used by the Actuator

boards connected to the ACT satellite connector.

cortex-20pin.emf

SWO / TDO / EXTa / TRACECTL

Cortex Debug+ETM

Connector (20-pin)

GNDDetect

SWDIO / TMS

SWDCLK / TCK

1 2

3 4

5 6

7 8

9

10

VCC

GND

GND

KEY

nRESET

11

12

13 14

15

16

17 18

19 20

NC/EXTb/TDI

TRACECLK

TRACEDATA[0]

TRACEDATA[1]

TRACEDATA[2]

TRACEDATA[3]

GND/TgtPwr+Cap

GND/TgtPwr+Cap

GND

GND

GND

Figure 13 Cortex Debug+ETM Connector (20-pin)

Table 5 Cortex Debug+ETM Connector (20 Pin)

Pin No.

Signal Name

Serial Wire Debug

JTAG Debug

1

VCC

+3.3 V

+3.3 V

2

SWDIO / TMS

Serial Wire Data I/O

Test Mode Select

3

GND

Ground

Ground

4

SWDCLK / TCK

Serial Wire Clock

Test Clock

5

GND

Ground

Ground

6

SWO / TDO

Trace Data OUT

Test Data OUT

7

KEY

KEY

KEY

8

NC / TDI

Not connected

Test Data IN

9

GNDDetect

Ground Detect

Ground Detect

10

nRESET

Reset (Active Low)

Reset (Active Low)

11

GND/TgtPwr+Cap

Ground

Ground

12

TRACECLK

Trace Clock

Trace Clock

13

GND/TgtPwr+Cap

Ground

Ground

14

TRACEDATA[0]

Trace Data 0

Trace Data 0

15

GND

Ground

Ground

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 17 Revision 1.0, 2014-01-10

Table 5 Cortex Debug+ETM Connector (20 Pin)

Pin No.

Signal Name

Serial Wire Debug

JTAG Debug

16

TRACEDATA[1]

Trace Data 1

Trace Data 1

17

GND

Ground

Ground

18

TRACEDATA[2]

Trace Data 2

Trace Data 2

19

GND

Ground

Ground

20

TRACEDATA[3]

Trace Data 3

Trace Data 3

Cortex Debug+ETM

Connector (20 Pin)

20Pin_Conn.emf

Figure 14 Cortex Debug+ETM Connector (20-pin) Layout

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 18 Revision 1.0, 2014-01-10

2.6 Serial Flash Memory

The CPU_45A-V3 board provides a 32 Mbit serial flash memory from Micron (type: N25Q03) interfaced to

XMC4500 through a SPI interface. The SPI interface can be configured as single, dual or quad SPI.

Table 6 Quad SPI Signals

Pin No.

Pin Description

Signal Name

Signal Description

P0.13

U1C1_SCLKOUT

CLK

Clock

P3.3

U1C1_SELO1

CS#

Active Low Chip Select

P3.15

U1C1_DOUT0

DI (IO0)

Data Input/Output of Flash (MTSR/MOSI)

P3.14

U1C1_DX0B

DO (IO1)

Data Input/Output of Flash (MRST/MISO )

P0.14

U1C1_HOUT3/DWIN3

HOLD# (IO3)

Data Input/Output

P0.15

U1C1_HOUT2/DWIN2

WP# (IO2)

Data Input/Output

Figure 15 Quad SPI Flash Interface Circuit

SPI-Flash.emf

32 Mbit serial

Quad-SPI

Flash (Micron,

N25Q032A13)

Figure 16 Quad SPI Flash

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 19 Revision 1.0, 2014-01-10

2.7 USB

The XMC4500 supports USB interface in host only mode, device only mode or as an OTG Dual Role Device

(DRD). In USB device mode, power is expected through VBUS (pin 1) from an external host (e.g. PC). When

the current is more than 500 mA power from an external source through satellite cards shall be used.

Note: Some PCs, notebooks or hubs have a weak USB supply which is not sufficient for proper supply. In this

case use an external 5 Volt power supply or a powered USB hub.

Figure 17 USB Connector Schematic

Port P0.9 of XMC4500 is connected to the USB ID pin (pin 4). An OTG device will detect whether a USB 3.0

Micro-A or Micro-B plug is inserted by checking the ID pin. When the ID = FALSE, Micro-A connector is plugged

and when ID = TRUE a Micro-B connector is plugged in. When ID is true the XMC4500 acts as USB host else

as USB device.

Table 7 USB micro AB connector Pinout

Pin No.

Pin Name

Pin Description

1

VBUS

5 V 2 D-

Data Minus

3

D+

Data Plus

4

ID

Identification

5

GND

Ground

Figure 18 USB power generation - Host/OTG mode

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 20 Revision 1.0, 2014-01-10

In the host only mode and OTG mode the CPU_45A-V3 board is capable of supplying power to the connected

device (e.g. USB mouse). The board has a power-switch which is controlled by the XMC4500. Port P3.2 (active

high) is used for this purpose. In the Host/OTG mode a low active FAULT signal indicates to XMC4500 via

HIB_IO_0 signal, if more than 500 mA current is drawn by the external device. HIB_IO_0 signal is used as

general purpose input pin for this implementation.

Diode V400 will allow powering the board through USB in all USB modes via e.g. a PC.

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 21 Revision 1.0, 2014-01-10

2.8 RTC

The XMC4400 CPU has two power domains, the Core Domain and Hibernate Domain. The Core Domain

(VDDP pins) is connected to the VDD3.3 rail. An on-board LDO voltage regulator generates VDD3.3 (3.3 V)

from VDD5 (5 V).

The Hibernate Domain is powered via the auxiliary supply pin VBAT, which is supplied by either a 3 V coin cell

(size 1216, 1220, 1225) plugged into the battery holder (see Figure 19) or 3.3 V (VDD3.3) generated by the onboard voltage regulator.

Battery

Holder

Battery.emf

Figure 19 Battery Holder for Coin Cell

The Real Time Clock (RTC) is located in the hibernate domain. The XMC4500 uses the HIB_IO_1 signal (active

low) to shut down the external LDO voltage regulator which generates the VDD3.3 (Core Domain). Even if the

Core Domain is not powered the Hibernate Domain will operate if VBAT is available. The RTC keeps running as

long as the Hibernate Domain is powered via the auxiliary supply VBAT. The RTC is capable to wake-up the

whole system from Hibernate mode by setting HIB_IO_1 to high.

With VDD3.3 power supply switched off and no coin cell supply the power in the capacitor connected to VBAT

will provide power to the hibernate domain for about 10 seconds (depending on which features in the hibernate

domain are enabled).

Core Domain

CPU

Internal OSC

Hibernate Domain

VBAT

32.768 kHz

XMC4500

VDDP

IFX1763

LDO

Voltage Reg.

VDD3.3

+

RTC

SPI

RTC.emf

Battery

12 MHz

External OSC

Hibernate

Control

HIBIO_1

EN

Figure 20 RTC

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 22 Revision 1.0, 2014-01-10

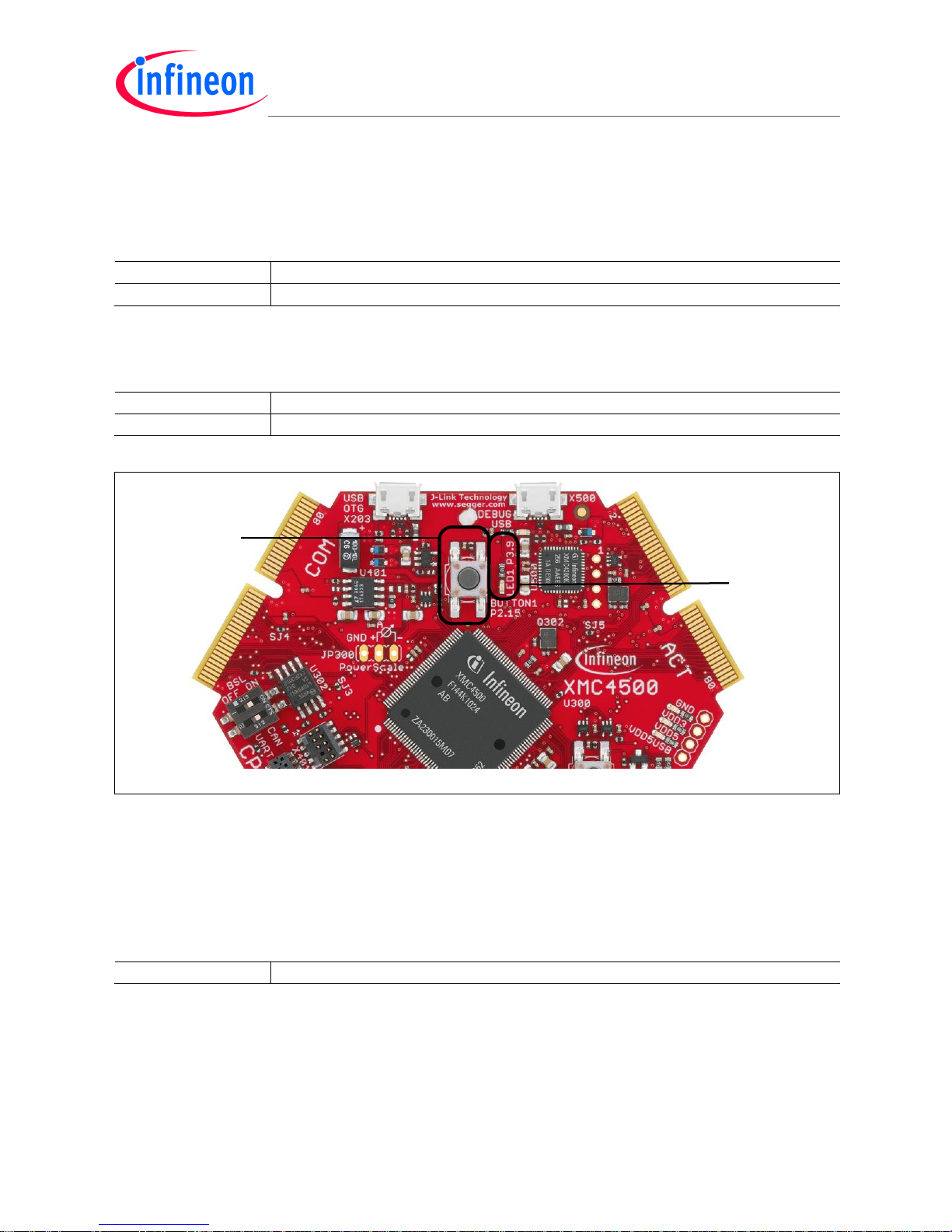

2.9 User LEDs and User Buttons

The port pin P3.9 of XMC4500 is connected to a LED V300. More user LED’s are available through I2C GPIO

expander on most of the satellite cards.

Table 8 GPIO LED

LED

Connected to Port Pin

V300

GPIO P3.9

The User Button is connected to port pin P2.15 of the XMC4500.

Table 9 User Button

Button

Connected to Port Pin

BUTTON1

P2.15

Button_LED.emf

User

Button

User

LED1

Figure 21 GPIO LED

2.10 Potentiometer

The CPU_45A-V3 board provides a potentiometer POT1 for ease of use and testing of the on-chip analog to

digital converter. The potentiometer is connected to the analog input G0_CH1 (P14.1). The analog output of the

potentiometer ranges from 0 V to 3.3 V.

Table 10 Potentiometer

R300

P14.1 / G0_CH1 (Group 0, Channel 1)

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 23 Revision 1.0, 2014-01-10

2.11 Satellite Connectors

The CPU_45A-V3 board provies three satellite connectors for application extension by satellite cards:

COM satellite connector (Communication)

HMI satellite connector (Human Machine Interface)

ACT satellite connector (Actuator)

Note: Satellite cards shall be connected to their matching satellite connectors only. (For e.g. COM

satellite cards shall be connected to COM satellite connector only)

ACT Satellite

Connector

COM Satellite

Connector

HMI Satellite

Connector

Sat_Conn.emf

Figure 22 Satellite Connectors

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 24 Revision 1.0, 2014-01-10

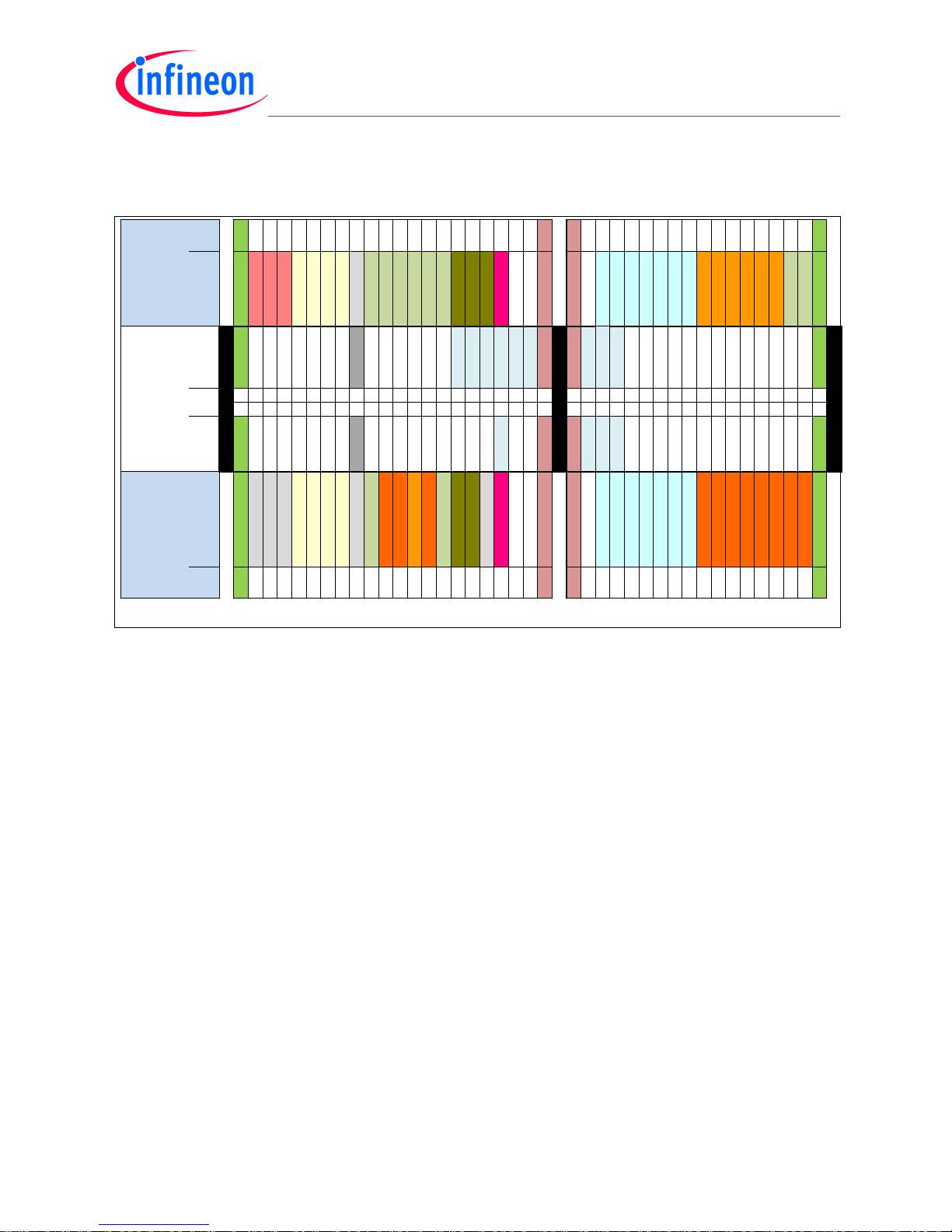

2.11.1 COM Connector

The COM satellite connector on the CPU_45A-V3 board allows interface expansion through COM satellite cards

(e.g. COM_ETH-V1)

XMC Pin

VSS

P3.15

P3.14

P0.15

P0.14

nc

P2.9

P2.8

P15.9

P5.3

P15.8

VSS

nc

P1.9

P1.8

P3.13

P2.5

P3.0

P5.8

P0.6

PORST

ncncncncncncncncncncncncncncnc

nc

VSS

XMC Function

GND

U1C1_DOUT0

U1C1_DOUT1

U1C1_DOUT2

U1C1_DOUT3

nc

ETH0_TXD1

ETH0_TXD0

ETH0_CRS_DVC

ETH0_RXERD

ETH0_CLK_RMIIC

GND

nc

CAN_N2_TXD

CAN_N2_RXDA

U0C1_DOUT0

U0C1_DX0B

U0C1_SCLKOUT

U1C0_SCLKOUT

P0.6

RESET#

ncncncncncncncncncncncncncncnc

nc

GND

Function

GND

qSPI_D0

qSPI_D1

qSPI_D2

qSPI_D3

RSVD

ETH_RMII

ETH_RMII

ETH_RMII

ETH_RMII

ETH_RMII

GND

RSVD

CAN_TXD

CAN_RXD

SPI_MTSR

SPI_MRST

SPI_SCLK

I2C_SCL

GPIO

RESET

VDD5

VDD5

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

GND

Satellite

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80

Connector

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79

Function

GND

qSPI_SCLK

qSPI_CS

qSPI_CS

RSVD

RSVD

ETH_RMII

ETH_RMII

ETH_RMII

ETH_RMII

ETH_RMII

RSVD

ASC_DIR

ASC_RXD

ASC_TXD

SPI_CSC0

SPI_CSC1

SPI_CSC2

I2C_SDA

COM_GPIO1

COM_GPIO0

VDD5

VDD5

EBU_ADV

EBU_WR

EBU_RD

EBU_BC

EBU_BC

EBU_CS

EBU_CS

GND

EBU_A

EBU_A

EBU_A

EBU_A

EBU_A

EBU_A

EBU_A

EBU_A

GND

XMC Function

GND

U1C1_SCLKOUT

U1C1_SELO0

U1C1_SELO1

nc

nc

ETH0_RXD1A

ETH0_RXD0A

ETH0_MDO

ETH0_MDC

ETH0_TX_EN

nc

P3.10

U0C0_DX0B

U0C0_DOUT0

P5.5

U0C1_SELO0

nc

U1C0_DOUT0/DX0D

P14.13

P3.7

ncncncncncncnc

GND

ncncncncncncnc

nc

GND

XMC Pin

VSS

P0.13

P0.12

P3.3

nc

nc

P2.3

P2.2

P2.0

P2.7

P5.9

nc

P3.10

P1.4 (3)

P1.5 (3)

P5.5

P3.1

nc

P2.14

P14.13

P3.7

ncncncncncncnc

VSS

ncncncncncncnc

nc

VSS

CPU_45A-V3

Pin

COM

COM

COM

CPU_45A-V3

Figure 23 Satellite Connector Type COM

(3) This pin is connected with the satellite connector via an analog switch

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 25 Revision 1.0, 2014-01-10

2.11.2 HMI Connector

The HMI satellite connector on the CPU_45A-V3 board allows interface expansion through HMI satellite cards.

XMC Pin

VSS

P0.11

P4.0

P1.7

nc

nc

P3.5

VSS

ncncnc

P5.11

P3.13

P2.5

P3.0

P3.13

P2.5

P3.0

P5.8

P0.6

PORST

VAREF

P14.8

P14.4

P14.3

P15.3

P15.2

nc

nc

P5.10

ncncnc

nc

P2.4

nc

nc

VSS

XMC Function

GND

MMC_nRST

MMC_DATA0_OUT

MMC_DATA2_OUT

nc

nc

MMC_CMD_OUT

GND

ncncnc

P5.11

U0C1_DOUT0

U0C1_DX0B

U0C1_SCLKOUT

U0C1_DOUT0

U0C1_DX0B

U0C1_SCLKOUT

U1C0_SCLKOUT

P0.6

RESET#

VAREF

VADC_G1CH0

VADC_G0CH4

VADC_G0CH3

VADC_G2CH3

VADC_G2CH2

nc

nc

LEDTS0_TSIN7A

ncncnc

nc

LEDTS0_TSIN2A

nc

nc

GND

Function

GND

MMC_nRST

MMC_DATA0

MMC_DATA2

MMC_DATA4

MMC_DATA6

MMC_CMD

MMC_LED

MMC_SDWC

RSVD

RSVD

OLED_CMD

I2S_MTSR

I2S_MRST

I2S_SCLK

SPI_MTSR

SPI_MRST

SPI_SCLK

I2C_SCL

GPIO

RESET

VDD5

VDD5

AREF

DAC0/ADC0

ADC2/DACREF

ADC14

ADC16

ADC18

RSVD

RSVD

TP7

TP6

TP5

TP4

TP3

TP2

TP1

TP0

GND

Satellite

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80

Connector

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79

Function

GND

MMC_CLK

MMC_DATA1

MMC_DATA3

MMC_DATA5

MMC_DATA7

MMC_BUSPOW

MMC_nSDCD

RSVD

RSVD

RSVD

AudioRST

I2S_WA

I2S_MCLK

I2S_SYNCLK

SPI_CSH0

SPI_CSH1

SPI_CSH2

I2C_SDA

HMI_GPIO1

HMI_GPIO0

VDD5

VDD5

AGND

DAC1/ADC1

ADC3/ORC0

ADC15

ADC17

ADC19

RSVD

RSVD

RSVD

TPx1

TPx0

COL3

COL2

COL1

COL0

COLA

GND

XMC Function

GND

MMC_CLK_OUT

MMC_DATA1_OUT

MMC_DATA3_OUT

nc

nc

GND

ncncnc

nc

P2.10

U0C1_SELO0

nc

nc

U0C1_SELO1

U0C1_SELO0

U0C1_SELO3

U1C0_DX0D/DOUT0

P15.5 Input

P5.6

AGND

VADC_G1CH1

VADC_G0CH6

VADC_G1CH4

VADC_G3CH5

VADC_G3CH4

ncncncncncncnc

nc

LEDTS0_COL1

LEDTS0_COLA

GND

XMC Pin

VSS

P3.6

P1.6

P4.1

nc

nc

VSS

ncncnc

nc

P2.10

P3.1

nc

nc

P3.12

P3.1

P3.8

P2.14

P15.5

P5.6

VAGND

P14.9

P14.6

P14.12

P15.13

P15.12

ncncncncncncnc

nc

P0.10

P5.7

VSS

CPU_45A-V3

Pin

HMI

HMI

HMI

CPU_45A-V3

Figure 24 Satellite Connector Type HMI

CPU_45A-V3

CPU Board XMC4500 General Purpose

Hardware Description

Board User's Manual 26 Revision 1.0, 2014-01-10

2.11.3 ACT Satellite Connector

The ACT satellite connector on the CPU_45A-V3 board allows interface expansion through ACT satellite cards.

XMC

Pin

VSS

P1.3

P1.2

P1.1

P0.8 (2)

P2.6

P1.6

P6.5 (3)

nc

P4.6

P4.5

P4.4

P2.13

P2.12

P6.4

P3.13

P2.5

P3.0

P5.8

P0.6

PORST

VAREF

P14.8

P14.4

P14.14

P14.15

P14.2

P15.6

P15.7

P0.5

P0.2

P0.4

P0.1

P0.3

P0.0

P6.3

P6.2

VSS

XMC Function

GND

PIF0_IN0A

PIF0_IN1A

PIF0_IN2A

DSD_DIN0A

DSD_DIN1B

DSD_DIN2A

DSD_DIN3A

nc

CCU43_IN0A

CCU43_IN1A

CCU43_IN2A

CCU43_IN2C

CCU43_IN3C

CCU43OUT1

U0C1_DOUT0

U0C1_DX0B

U0C1_SCLKOUT

U1C0_SCLKOUT

P0.6

RESET#

VAREF

VADC_G1CH0

VADC_G0CH4

VADC_G1CH6

VADC_G1CH7

VADC_G0CH2

VADC_G2CH6

VADC_G2CH7

CCU80_OUT00

CCU80_OUT01

CCU80_OUT10

CCU80_OUT11

CCU80_OUT20

CCU80_OUT21

CCU43OUT2

CCU43OUT3

GND

Function

GND

PIF0IN1

PIF0IN2

PIF0IN3

DSDIN0

DSDIN1

DSDIN2

DSDIN3

RSVD

CC_IN0

CC_IN1

CC_IN2

ENA_A

ENA_B

ENA_X

SPI_MTSR

SPI_MRST

SPI_SCLK

I2C_SCL

GPIO

RESET

VDD5

VDD5

AREF

DAC0/ADC0

ADC2/DACREF

ADC4/ORC1

ADC6/ORC3

ADC8

ADC10

ADC12

PWMA0_H

PWMA0_L

PWMA1_H

PWMA1_L

PWMA2_H

PWMA2_L

PWMX0

PWMX1

GND

Satellite

2 4 6 8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44 46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80

Connector

1 3 5 7 9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43 45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79

Function

GND

PIF1IN0

PIF1IN1

PIF1IN2

PWMN

PWMP

DSDCLK0

DSDCLK1

RSVD

CC_IN3

CC_IN4

CC_IN5

TRAP_A

TRAP_B

TRAP_X

SPI_CSA0

SPI_CSA1

SPI_CSA2

I2C_SDA

ACT_GPIO1

ACT_GPIO0

VDD5

VDD5

AGND

DAC1/ADC1

ADC3/ORC0

ADC5/ORC2

ADC7

ADC9

ADC11

ADC13

PWMB0_H

PWMB0_L

PWMB1_H

PWMB1_L

PWMB2_H

PWMB2_L

PWMX2

PWMX3

GND

XMC Function

GND

ncncnc

DSD_PWMN

DSD_PWMP

DSD_MCLK2A

DSD_MCLK3B

nc

CCU43_IN3A

CCU81_IN1B

CCU81_IN3B

CCU80_IN0A

CCU81_IN0A/1A/2A/3A

CCU43_IN0C

U0C1_SELO2

U0C1_SELO3

nc

U1C0_DX0D/DOUT0

P15.4 Input

P4.2

AGND

VADC_G1CH1

VADC_G0CH6

VADC_G0CH7

VADC_G0CH0

VADC_G2CH1

VADC_G3CH6

VADC_G3CH7

CCU81_OUT00

CCU81_OUT01

CCU81_OUT10

CCU81_OUT11

CCU81_OUT20

CCU81_OUT21

CCU81_OUT31

CCU81_OUT30

GND

XMC

Pin

VSS

ncncnc

P1.0

P5.1

P1.7

P3.4ncP4.3

P5.2

P5.4

P0.7 (1)

P5.0

P4.7

P3.11

P3.8

nc

P2.14

P15.4

P4.2

VAGND

P14.9

P14.6

P14.7

P14.0

P14.5

P15.14

P15.15

P1.15

P1.12

P1.14

P1.11

P1.13

P1.10

P6.0 (3)

P6.1 (3)

VSS

CPU_45A-V3

Pin

ACT

ACT

ACT

CPU_45A-V3

Figure 25 Satellite Connector Type ACT

(1) P0.7 can also be used for JTAG Debugging (TDI)

(2) P0.8 is used as TRST in order to enable JTAG Debug

(3) This pin is connected with the satellite connector via an analog switch

CPU_45A-V3

CPU Board XMC4500 General Purpose

Differences to Board Version V2

Board User's Manual 27 Revision 1.0, 2014-01-10

3 Differences to Board Version V2

Table 11 Differences to older board versions

Topic of Change

Description

Debugger

An on-board debugger has been added. The debugger has an USB

interface (X500). An external debugger can still be used via X400 / X401.

User Push Button

A user button as been added. The user button is connected to P2.15. In

V2 versions P2.15 was connected to P2.14.

I2C Connection

The SDA signal of the I2C is connected to P2.14 only. In V2 versions the

SDA signal was connected to P2.14 and P2.15.

USB Shielding

The USB shield has been connected to ground through a 1 MOhm

resistor and a 100 nF capacitor

4 Production Data

4.1 Schematics

This chapter contains the schematics for the CPU board:

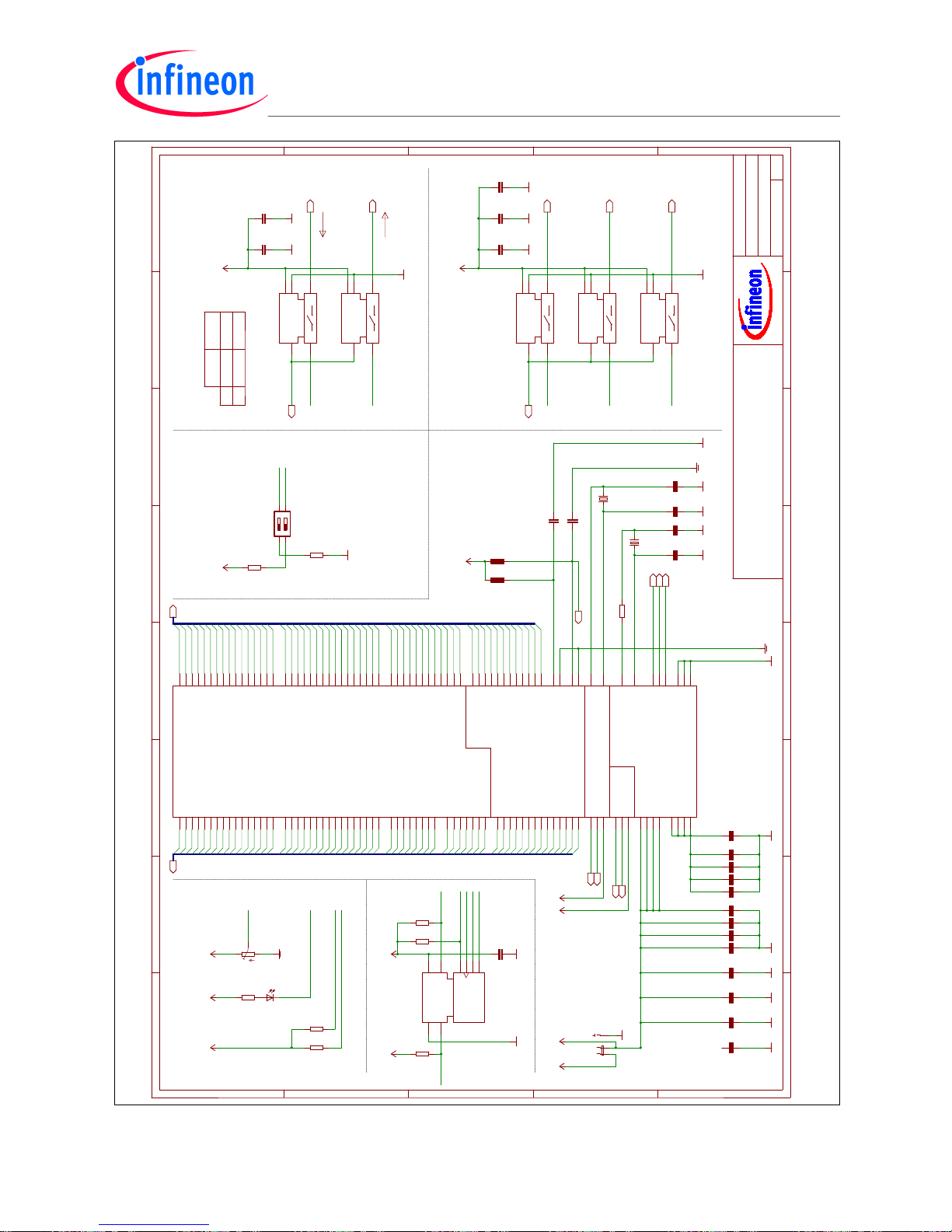

Schematic of Satellite Connectors, USB-OTG

Schematic of XMC4500

Schematic of Power Supply, Debug Connectors, Reset Circuit

Schematic of On-board Debugger

The board has been designed with Eagle. The PCB design data of this board can be downloaded from

www.infineon.com/xmc-dev.

CPU_45A-V3

CPU Board XMC4500 General Purpose

Production Data

Board User's Manual 28 Revision 1.0, 2014-01-10

Figure 26 Schematic of Satellite Connectors, USB-OTG

AGND

AGND

100nF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

GND GND

GND

GND GND

GND GND GND GND

GNDGND

GND GND GNDGND GND

BLM18PG600

1M/0402

33R/0402

33R/0402

10k/0402

VDD5

VDD5

VDD5

VDD5

VDD5

VDD5

VDD3.3

VDD5

VDD5USB

VDD5

VDD5

VDD5

VDD5

VDD5

ESD8V0L2B-03L

HSEC8_MATING-CARD HSEC8_MATING-CARD HSEC8_MATING-CARD

ZX62-AB-5PA

P0.[0..15],P1.[0..15],P2.[0..15],P3.[0..15],P4.[0..7],P5.[0..11],P6.[0..6],P14.[0..15],P15.[2..15]

CCU81_OUT30

CCU81_OUT31

COM_RXD

COM_TXD

DSD_DIN3A

OTG_FS_DM

OTG_FS_DP

P0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6 P0.6P0.6

P0.7

P0.8

P0.9

P0.10

P0.11

P0.12

P0.13

P0.14

P0.15

P1.0

P1.1

P1.2

P1.3

P1.6

P1.6

P1.7

P1.7

P1.8

P1.9

P1.10

P1.11

P1.12

P1.13

P1.14

P1.15

P2.0

P2.2

P2.3

P2.4

P2.5 P2.5 P2.5

P2.5

P2.6

P2.7

P2.8

P2.9

P2.10

P2.12

P2.13

P2.14 P2.14P2.14

P3.0

P3.0 P3.0 P3.0

P3.1

P3.1 P3.1

P3.3

P3.4

P3.5

P3.6

P3.7

P3.8

P3.8

P3.10

P3.11 P3.12P3.13 P3.13 P3.13

P3.13

P3.14

P3.15

P4.0

P4.1

P4.2

P4.3

P4.4

P4.5

P4.6

P4.7

P5.0

P5.1

P5.2

P5.3

P5.4

P5.5

P5.6

P5.7

P5.8 P5.8P5.8

P5.9

P5.10

P5.11

P6.2

P6.3

P6.4

P14.0

P14.2

P14.3

P14.4 P14.4

P14.5

P14.6 P14.6

P14.7

P14.8P14.8 P14.9P14.9

P14.12

P14.13

P14.14

P14.15

P15.2

P15.3

P15.4 P15.5

P15.6

P15.7

P15.8

P15.9

P15.12

P15.13

P15.14

P15.15

RESET#RESET# RESET#

VAREF VAREF

C200

C201

C202

C205

C206

C209

C210

L201

R200

R202

R203

R204

1 2

SJ3

1 2

SJ4

1 2

SJ5

1 2

SJ6

1 2

SJ7

1

2

3

V201

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

X200

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

X201

1

1

2

2

3

3

4

4

5

5

6

6

7

7

8

8

9

9

10

10

11

11

12

12

13

13

14

14

15

15

16

16

17

17

18

18

19

19

20

20

21

21

22

22

23

23

24

24

25

25

26

26

27

27

28

28

29

29

30

30

31

31

32

32

33

33

34

34

35

35

36

36

37

37

38

38

39

39

40

40

41

41

42

42

43

43

44

44

45

45

46

46

47

47

48

48

49

49

50

50

51

51

52

52

53

53

54

54

55

55

56

56

57

57

58

58

59

59

60

60

61

61

62

62

63

63

64

64

65

65

66

66

67

67

68

68

69

69

70

70

71

71

72

72

73

73

74

74

75

75

76

76

77

77

78

78

79

79

80

80

X202

12345

X203C

X203S

COM

ACT

HMI

1 2 3 4 5 6 7 8

A

B

C

D

E

87654321

E

D

C

B

A

CPU_45A-V3-2

05.11.2013 09:55:58

2/5

Sheet:

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

D1

D2

Satellite Conn., USB-OTG

USB-OTG Connector

V3 / 01.02.2012 / Ma

MMC_LED

MMC_BUSPOW

I2S_WA I2S_MTSR

I2S_MRST

I2S_SCLK

CPU_45A-V3

CPU Board XMC4500 General Purpose

Production Data

Board User's Manual 29 Revision 1.0, 2014-01-10

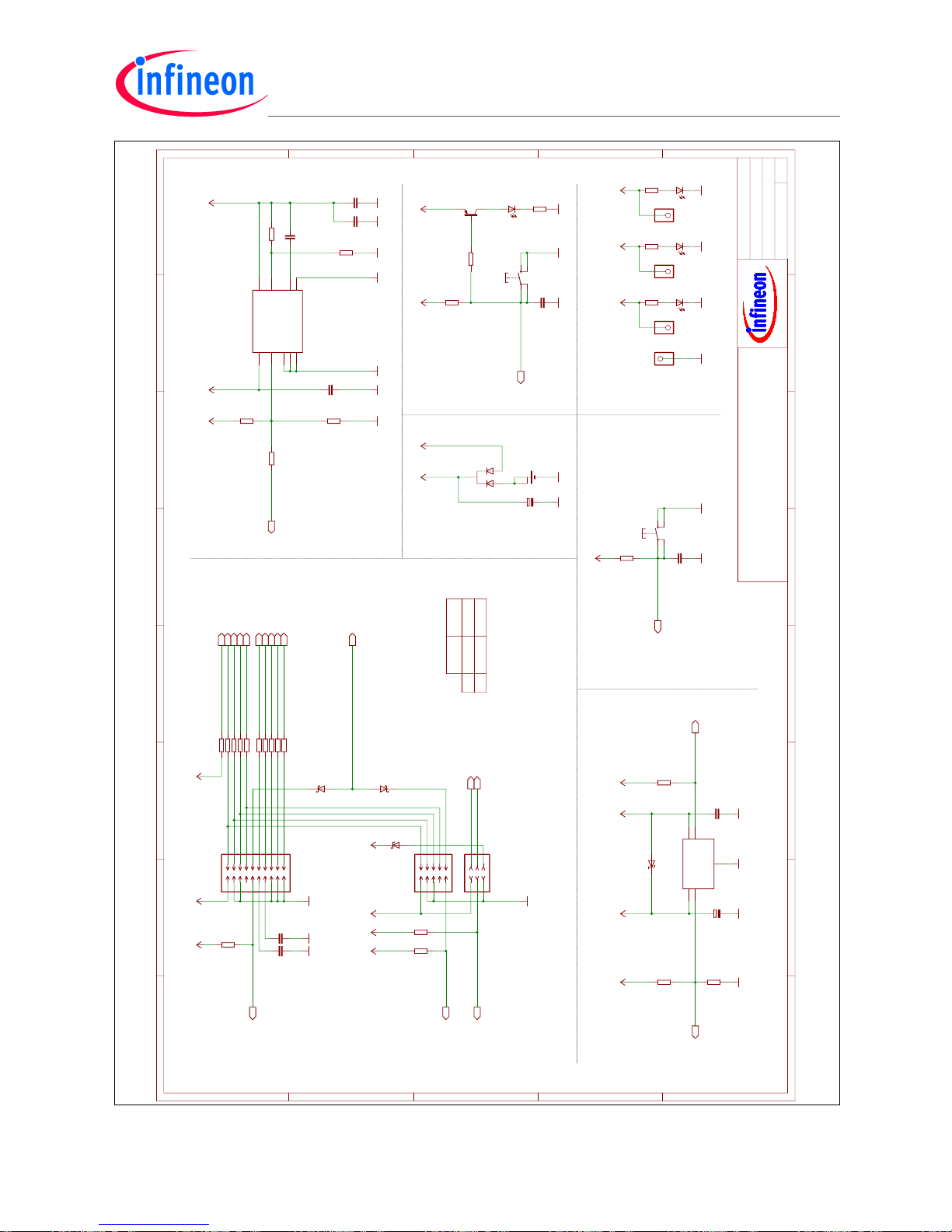

Figure 27 Schematic of XMC4500

AGND

AGND

AGND

100nF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

10uF/10V/0805

100nF/0402

100nF/0402

100nF/0402

15pF/0402

15pF/0402

15pF/0402

15pF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

100nF/0402

10uF/10V/0805

10uF/10V/0805

10uF/10V/0805

10uF/10V/0805

GND

GNDGNDGND

GND

GND

GND GND GND

GND

GND

GND

GND GND

GND

GND

GNDGNDGNDGND

GND GND

GND

BLM18PG600

BLM18PG600

32.768kHz

12MHZ/S/3.2X2.5

POTI/10K/VERT

680R/0603

4k7/0402

10k/0402

4k7/0402

2k2/0603

2k2/0603

10k/0402

10k/0402

510R/0603

219-02

VDDP

VDD5USB

VDD3.3

VDDP

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VBAT

XMC4500_LQFP144

74LVC1G66DCK

N25Q032A13ESE40

74LVC1G66DCK

74LVC1G66DCK

74LVC1G66DCK

74LVC1G66DCK

LED-GE/D/0603

P0.[0..15],P1.[0..15],P2.[0..15],P3.[0..15],P4.[0..7],P5.[0..11],P6.[0..6],P14.[0..15],P15.[2..15]

P0.[0..15],P1.[0..15],P2.[0..15],P3.[0..15],P4.[0..7],P5.[0..11],P6.[0..6],P14.[0..15],P15.[2..15]

CCU81_OUT30

CCU81_OUT31

COMDIS#

COM_RXD

COM_TXD

DBGPRES#

DSD_DIN3A

HIB_IO_0

HIB_IO_1

OTG_FS_DM

OTG_FS_DP

P0.0

P0.1

P0.2

P0.3

P0.4

P0.5

P0.6

P0.7

P0.8

P0.9

P0.10

P0.11

P0.12

P0.13

P0.13

P0.14

P0.14

P0.15

P0.15

P1.0

P1.1

P1.2

P1.3

P1.4

P1.4

P1.5

P1.5

P1.6

P1.7

P1.8

P1.9

P1.10

P1.11

P1.12

P1.13

P1.14

P1.15

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P2.8

P2.9

P2.10

P2.11

P2.12

P2.13

P2.14

P2.14

P2.15

P3.0

P3.1

P3.2

P3.3

P3.3

P3.4

P3.5

P3.6

P3.7

P3.8

P3.9

P3.9

P3.10

P3.11

P3.12

P3.13

P3.14

P3.14

P3.15

P3.15

P4.0

P4.1

P4.2

P4.3

P4.4

P4.5

P4.6

P4.7

P5.0

P5.1

P5.2

P5.3

P5.4

P5.5

P5.6

P5.7

P5.8

P5.8

P5.9

P5.10

P5.11

P6.0

P6.0

P6.1

P6.1

P6.2

P6.3

P6.4

P6.5

P6.5

P6.6

P14.0

P14.1

P14.1

P14.2

P14.3

P14.4

P14.5

P14.6

P14.7

P14.8

P14.9

P14.12

P14.13

P14.14

P14.15

P15.2

P15.3

P15.4

P15.5

P15.6

P15.7

P15.8

P15.9

P15.12

P15.13

P15.14

P15.15

RESET#

TCK

TCK

TMS

TMS

VAREF

VDDC

C300

C301

C302

C303

C304

C305

C306

C307

C308

C309

C310

C311

C312

C315

C316

C317

C318

C319

C320

C321

C322

C323

C324

C325

C326

3

2

1

JP300

L300

L301

Q301

Q302

A E

S

R300

R301

R302

R303

R304

R306

R307

R309

R310

R313

1

2 3

4

SW300

EPAD

EXP

HIB_IO_021HIB_IO_1

20

P0.02P0.11P0.2

144

P0.3

143

P0.4

142

P0.5

141

P0.6

140

P0.7

128

P0.8

127

P0.94P0.103P0.11

139

P0.12

138

P0.13

137

P0.14

136

P0.15

135

P1.0

112

P1.1

111

P1.2

110

P1.3

109

P1.4

108

P1.5

107

P1.6

116

P1.7

115

P1.8

114

P1.9

113

P1.10

106

P1.11

105

P1.12

104

P1.13

103

P1.14

102

P1.15

94

P2.074P2.173P2.272P2.371P2.470P2.569P2.676P2.775P2.868P2.9

67

P2.1066P2.1165P2.1264P2.1363P2.1460P2.15

59

P3.07P3.16P3.25P3.3

132

P3.4

131

P3.5

130

P3.6

129

P3.714P3.813P3.9

12

P3.1011P3.1110P3.129P3.138P3.14

134

P3.15

133

P4.0

124

P4.1

123

P4.2

122

P4.3

121

P4.4

120

P4.5

119

P4.6

118

P4.7

117

P5.084P5.183P5.282P5.381P5.480P5.579P5.678P5.777P5.858P5.9

57

P5.1056P5.11

55

P6.0

101

P6.1

100

P6.299P6.398P6.497P6.596P6.6

95

P14.042P14.141P14.240P14.339P14.438P14.537P14.636P14.735P14.852P14.951P14.1234P14.1333P14.1432P14.15

31

P15.230P15.329P15.428P15.527P15.626P15.725P15.854P15.9

53

P15.1250P15.1349P15.1444P15.15

43

PORST#

91

RTC_XTAL_1

22

RTC_XTAL_2

23

TCK

93

TMS

92

USB_D+16USB_D-

15

VAGND

45

VAREF

46

VBAT24VBUS

17

VDDA

48

VDDC19VDDC161VDDC290VDDC3

125

VDDP18VDDP162VDDP286VDDP3

126

VSS

85

VSSA

47

VSSO

89

XTAL187XTAL2

88

U300

A

1

B2EN

4

GND

3

VCC

5

U301

CLK6CS#

1DI5DO2

GND

4

HOLD#

7

VCC

8

WP#

3

U302

A

1

B2EN

4

GND

3

VCC

5

U303

A

1

B2EN

4

GND

3

VCC

5

U304

A

1

B2EN

4

GND

3

VCC

5

U305

A

1

B2EN

4

GND

3

VCC

5

U306

V300

+ -

PS

12

ON

1 2 3 4 5 6 7 8

A

B

C

D

E

87654321

E

D

C

B

A

CPU_45A-V3-2

05.11.2013 09:55:58

3/5

Sheet:

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

USB

Supply

Analog

Digital

Hibernate/RTC

(IO0)

(IO1)

(IO3)(IO2)

CPU

PowerScale

Jumper closed with a cutable trace on bottom layer

CPU COM Board Switch

Trace Signal / ACT Board Switch

qSPI FLASH

Boot Options

Hitex

Potentiometer, GPIO LED, I2C Pullups

BSL

OFF ON

CAN

UART

USIC0CH0

UART

Node1

CAN

P1.4 USIC_RxD

USIC_TxD

CAN_RxD

CAN_TxDP1.5

V3 / 01.02.2012 / Ma

LED1

CPU_45A-V3

CPU Board XMC4500 General Purpose

Production Data

Board User's Manual 30 Revision 1.0, 2014-01-10

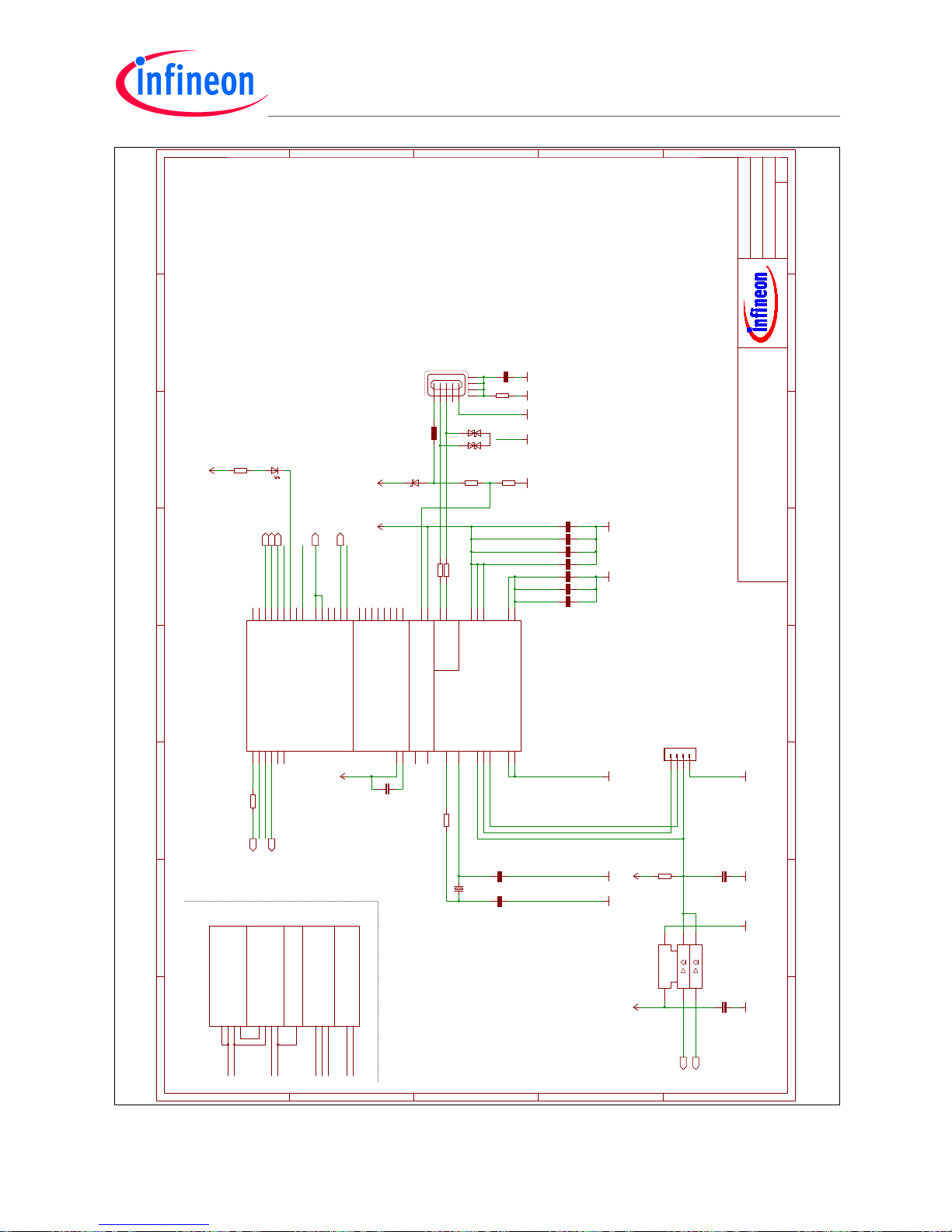

Figure 28 Schematic of Power Supply, Debug Connectors, Reset Circuit

100nF/0402 100nF/0402

10uF/10V/0805

10nF/040210uF/10V/0805

100uF/T/10V/C

4u7F/0805

100nF/0402

100uF/T/10V/C

10nF/0402

100nF/0402

GND

GNDGND

GNDGND GND

GND GNDGNDGND

GND

GND

GNDGND GND

GND GND GNDGND

GND

GND GNDGND

GND

GNDGND

BC858C

10k/0402

10k/0402

33R/0402

33R/0402

33R/0402

1k5/0603

1k5/0603

680R/0603

10k/0402

no ass./33R/0402

no ass./10k/0402

10k/0402

no ass./10k/0402

10k/0402

270k/0402

0R/0603

no ass./0R/0603

10k/0402

2k2/0603

33R/0402

10k/0402

33R/0402

33R/0402

33R/0402

33R/0402

no ass./4k7/0402

10k/0402

10k/0402

TMPS2-SMD

TMPS2-SMD

no ass.

no ass.

no ass.

no ass.

VDD5

VDD5

VDD5

VDD3.3

VDD5

VDD5

VDD5USB

VDD5USB

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3 VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VDD3.3

VBAT

IFX1763_PADNOP

TPS2051BDBV

BAS3010A-03W

LED-GN/D/0603

LED-GN/D/0603

LED-GN/D/0603

BAT54-02VBAT54-02V

BAV70

LED-RT/D/0603

BAS3010A-03W

S2*10/1.27SO

XE3K_DM2+CTX

BK-885

COMDIS#

DBG2PRES#

DBGPRES#

HIB_IO_0

HIB_IO_1

P0.7

P0.8

P1.4

P1.5

P2.1

P2.11

P2.15

P3.2

P6.0

P6.1

P6.5

P6.6

RESET#

RESET#

TCK

TMS

C400 C401

C405

C406

C407

C411

C412

C413

C414

C415

C416

Q404

R400

R401

R402

R403

R404

R405

R406

R407

R408

R410

R411

R412

R413

R414

R415

R416

R417

R419

R420

R421

R422

R423

R424

R425

R426

R427

R428

R429

P

P1

S

S1

SW400

P

P1

S

S1

SW401

1

TP404

1

TP405

1

TP406

1

TP407

BYP

4

EN

5

EXP

9

GND3GND6GND

7

IN

8

OUT

1

SENSE/ADJ

2

U401

EN

4

FAULT#

3

GND

2

VIN

5

VOUT

1

U403

AC

V400

V401

V402

V403

2 1

V404

21

V405

1

2

3

V406

V407

A C

V408

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

X400

C1 C2

C3 C4

C5 C6

C7 C8

C9 C10

D1 D2

D3 D4

D5 D6

X401

1+2+-

X402

+

+

1 2 3 4 5 6 7 8

A

B

C

D

E

87654321

E

D

C

B

A

CPU_45A-V3-2

05.11.2013 09:55:58

4/5

Sheet:

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

FTSH-105-01-L-DV-K

FLE-103-01-G-DV

Power, Debug, Reset

VDD3.3 Supply

USB-OTG Supply Power LED and Testpoints

RTC Battery Reset

Debug Connectors

Debugger pulls signal to GND,

disconnects trace signals

Ext. device pulls signal to GND

and disconnects UART/CAN signals

from ACT connector

from COM connector

USIC0CH0

UART

Node1

CAN

P1.4 USIC_RxD

USIC_TxD

CAN_RxD

CAN_TxDP1.5

V3 / 01.02.2012 / Ma

Battery Holder

and keeps the On-board

Debugger in reset state

Debugger pulls signal to GND

and keeps the On-board

Debugger in reset state

Push Button

BUTTON1

TDO/SWO

TRACECLK

TRACED[0]

TRACED[1]

TRACED[2]

TRACED[3]

TDI

TRST

CPU_45A-V3

CPU Board XMC4500 General Purpose

Production Data

Board User's Manual 31 Revision 1.0, 2014-01-10

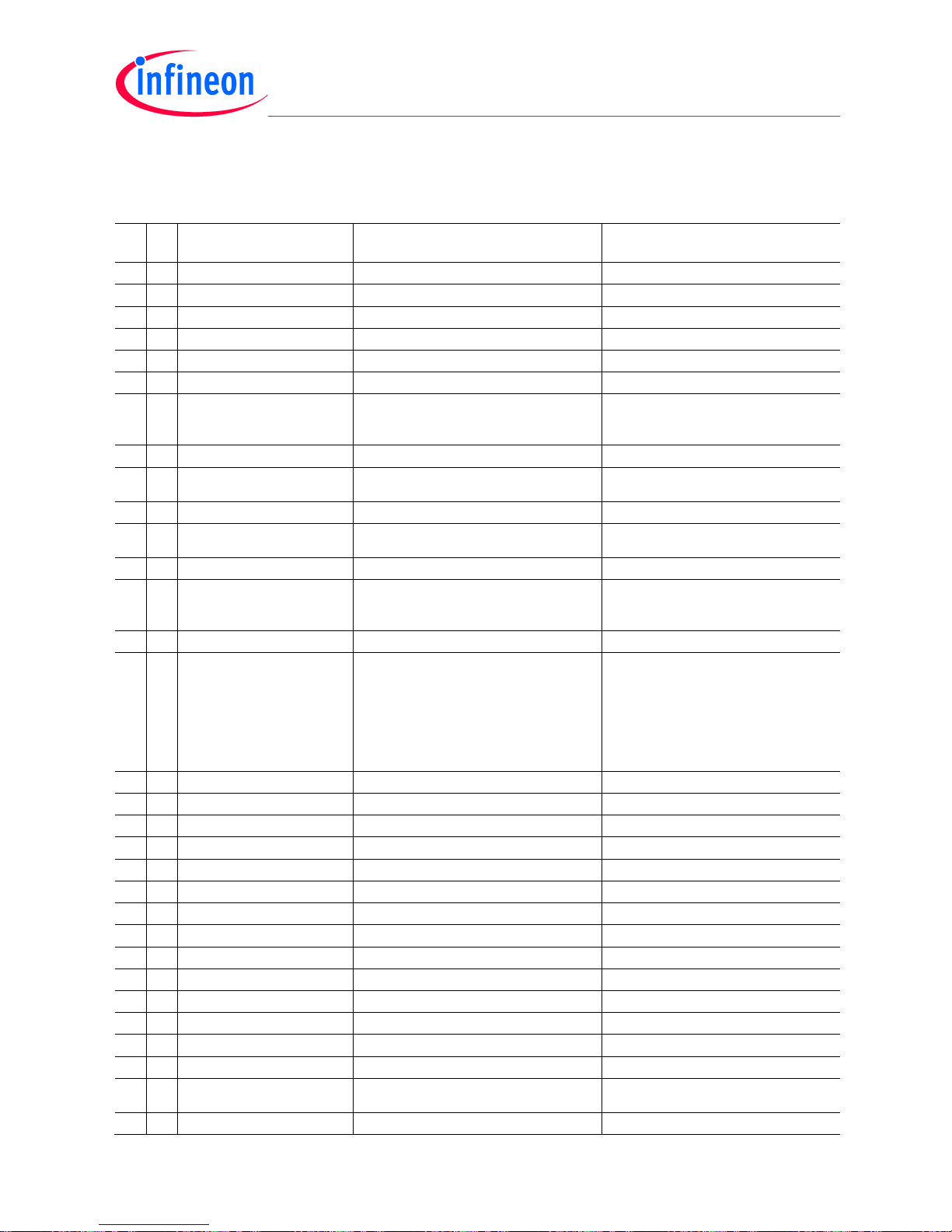

Figure 29 Schematic of On-board Debugger

15pF/0402

15pF/0402

100nF/0402

no ass./10nF/0402

100nF/0402

100nF/0402

4u7F/0805

100nF/0402

100nF/0402

100nF/0402

10uF/10V/0805

100nF/0402

100nF/0402

GND GND

GND

GNDGND

GND

GND

GND

GNDGND GND

GND GND

GND

BLM18PG600

12MHZ/S/3.2X2.5

510R/0603

33R/0402

33R/0402

10k/0402

680R/0603

1M/0402

4k7/040210k/0402

no ass./33R/0402

VDD3.3

VDD3.3

VDD5

VDD3.3

VDD3.3

VDD3.3

XMC4200_QFN48

NC7WZ07P6X

ESD8V0L2B-03L

BAS3010A-03W

LED-GN/D/0603

ZX62-AB-5PA

no ass.

COMDIS#

CS

CS

DBG2PRES#

DBGPRES#

DEBUG_LED#

P0.7

P1.4

P1.5

P2.1

P2.1

RESET#

TCK

TCK

TMS

WPORST#

WTCK

WTMS

C500

C501

C502

C503

C504

C505

C506

C507

C508

C509

C510

C511

C512

L500

Q500

R500

R501

R502

R503

R504

R505

R506R507

R508

EPAD

EPAD

HIB_IO_0

7

P0.02P0.11P0.248P0.347P0.446P0.545P0.644P0.743P0.8

42

P1.040P1.139P1.238P1.337P1.436P1.5

35

P2.026P2.125P2.224P2.323P2.422P2.5

21

P14.016P14.315P14.414P14.513P14.612P14.711P14.820P14.9

19

PORST#

32

RTC_XTAL_1

8

RTC_XTAL_2

9

TCK34TMS

33

USB_D+

4

USB_D-

3

VAGND17VAREF

18

VBAT

10

VDDC

6

VDDC1

31

VDDP

5

VDDP128VDDP2

41

VSS

27

XTAL129XTAL2

30

U500

1A

1

1Y

6

2A

3

2Y

4

GND

2

VCC

5

U501

1

2

3

V500

A C

V501

V502

12345

X500C

X500S

123

4

X501

1 2 3 4 5 6 7 8

A

B

C

D

E

87654321

E

D

C

B

A

CPU_45A-V3-2

05.11.2013 09:55:58

5/5

Sheet:

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

USB

Supply

Analog

Digital

Hibernate/RTC

D1

D2

V3-2 / 05.11.2013 / Ma

On-board Debugger

SCLKOUT-P1.1

DX0B-P1.4

DX0D-P0.0

DOUT0-P2.5

DX0A-P2.2

SPI Slave

TMS

TCK

TDI

TDO

MOSI

CLK_OUT

MISO

MISO

CS_IN

CLK_IN

MOSI

CS_OUT

SPI Master

RXD

UART

U0C0

U0C1

U1C1

DOUT0-P1.5

SELO0-P1.0

DX2A-P2.3

DX1A-P2.4

RXD

TXD

UART2 (DM2)

RXD

TXD

DX0A-P0.4

DOUT0-P0.5

U1C0

SWV

On-board Debugger Concept

TXACTIVE# GPIO-P0.6EN#

RESET# RESET# GPIO-P0.3

DEBUG_LED# DEBUG_LED# GPIO-P0.2

On-board Debugger

TDO

TDI

SWV

TCK

TMS

Configure COMDIS# as open-drain output

Configure Debugger-P0.5 as USIC_Tx but only active while X-spy function is selected

Configure Debugger-P0.4 as USIC_Rx but only active while X-spy function is selected

Configure Debugger-P0.3 as RESET# detect input but with additional open-drain output capabilities

EN#

TXD

RXD

CPU_45A-V3

CPU Board XMC4500 General Purpose

Production Data

Board User's Manual 32 Revision 1.0, 2014-01-10

4.2 Component Placement and Geometry

All dimensions in mm

2.4 21.0317.82

25.08

86.60

14.70

20.99

37.50

93.57

75.00

81.03

1234

+ -

A

PS

ON

1

2

80

46

44

2

80

46

44

2

80 46 44 2

FLE

FTSH

A D J_ 1

A D J_ 2

A D J_ 3

C200

C201

C202

C205

C206

C209

C210

C300

C301

C302

C303

C304

C305

C306

C307

C308

C309

C310

C311

C312

C315

C316

C317

C318

C319

C320

C321

C322

C323

C324

C325

C326

C400

C401

C405

C406

C407

C411

C412

C413

C414

C415

C416

C500

C501

C502

C503

C504

C505

C506

C507

C508

C509

C510

C511

C512

JP 300

L201

L300

L301

L500

Q301

Q302

Q404

Q500

R200

R202

R203

R204

R300

R301

R302

R303

R304

R306

R307

R309

R310

R313

R400

R401

R402

R403

R404

R405

R406

R407

R408

R410

R411

R412

R413

R414

R415

R416

R417

R419

R420

R421

R422

R423

R424

R425

R426

R427

R428

R429

R500

R501

R502

R503

R504

R505

R506

R507

R508