Data Sheet, V1.2, March 2007

XC164GM

16-Bit Single-Chip Microcontroller

with C166SV2 Core

Microcontrollers

Edition 2007-03

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2007 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or

characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any

information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties

and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest

Infineon Technologies Office (www.infineon.com).

Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in

question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

Data Sheet, V1.2, March 2007

XC164GM

16-Bit Single-Chip Microcontroller

with C166SV2 Core

Microcontrollers

XC164GM

Revision History: V1.2, 2007-03

Previous Version(s):

V1.1, 2006-08

V1.0, 2005-11

Page Subjects (major changes since last revision)

6 Design steps of the derivatives differentiated.

52 Power consumption of the derivatives differentiated.

53 Figure 10 adapted.

54 Figure 12 adapted.

64 Packages of the derivatives differentiated.

XC164GM

Derivatives

65 Thermal resistances of the derivatives differentiated.

all “Preliminary” removed

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

Data Sheet V1.2, 2007-03

XC164GM

Derivatives

Table of Contents

Table of Contents

1 Summary of Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 General Device Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.1 Pin Configuration and Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.1 Memory Subsystem and Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.2 Central Processing Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.3 Interrupt System . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

3.4 On-Chip Debug Support (OCDS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

3.5 Capture/Compare Unit (CAPCOM2) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

3.6 General Purpose Timer (GPT12E) Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.7 Real Time Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

3.8 A/D Converter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.9 Asynchronous/Synchronous Serial Interfaces (ASC0/ASC1) . . . . . . . . . . 36

3.10 High Speed Synchronous Serial Channels (SSC0/SSC1) . . . . . . . . . . . . 37

3.11 TwinCAN Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.12 LXBus Controller (EBC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.13 Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

3.14 Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

3.15 Parallel Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3.16 Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

3.17 Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4 Electrical Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.1 General Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.2 DC Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

4.3 Analog/Digital Converter Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

4.4 AC Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.4.1 Definition of Internal Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

4.4.2 On-chip Flash Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

4.4.3 External Clock Drive XTAL1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5 Package and Reliability . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.1 Packaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.2 Flash Memory Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Data Sheet 3 V1.2, 2007-03

XC164GM16-Bit Single-Chip Microcontroller with C166SV2 Core

XC166 Family

1 Summary of Features

For a quick overview or reference, the XC164GM’s properties are listed here in a

condensed way.

• High Performance 16-bit CPU with 5-Stage Pipeline

– 25 ns Instruction Cycle Time at 40 MHz CPU Clock (Single-Cycle Execution)

– 1-Cycle Multiplication (16 × 16 bit), Background Division (32 / 16 bit) in 21 Cycles

– 1-Cycle Multiply-and-Accumulate (MAC) Instructions

– Enhanced Boolean Bit Manipulation Facilities

– Zero-Cycle Jump Execution

– Additional Instructions to Support HLL and Operating Systems

– Register-Based Design with Multiple Variable Register Banks

– Fast Context Switching Support with Two Additional Local Register Banks

– 16 Mbytes Total Linear Address Space for Code and Data

– 1024 Bytes On-Chip Special Function Register Area (C166 Family Compatible)

• 16-Priority-Level Interrupt System with up to 63 Sources, Sample-Rate down to 50 ns

• 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via

Peripheral Event Controller (PEC), 24-Bit Pointers Cover Total Address Space

• Clock Generation via on-chip PLL (factors 1:0.15 … 1:10), or

via Prescaler (factors 1:1 … 60:1)

• On-Chip Memory Modules

– 2 Kbytes On-Chip Dual-Port RAM (DPRAM)

– 0/2/4 Kbytes

– 2 Kbytes On-Chip Program/Data SRAM (PSRAM)

– 32/64/128

• On-Chip Peripheral Modules

– 14-Channel A/D Converter with Programmable Resolution (10-bit or 8-bit) and

Conversion Time (down to 2.55 μs or 2.15 μs)

– 16-Channel General Purpose Capture/Compare Unit (CAPCOM2)

– Multi-Functional General Purpose Timer Unit with 5 Timers

– Two Synchronous/Asynchronous Serial Channels (USARTs)

– Two High-Speed-Synchronous Serial Channels

– On-Chip TwinCAN Interface (Rev. 2.0B active) with 32 Message Objects

(Full CAN/Basic CAN) on Two CAN Nodes, and Gateway Functionality

– On-Chip Real Time Clock, Driven by the Main Oscillator

• Idle, Sleep, and Power Down Modes with Flexible Power Management

1)

On-Chip Data SRAM (DSRAM)

1)

Kbytes On-Chip Program Memory (Flash Memory)

1) Depends on the respective derivative. See Table 1 “XC164GM Derivative Synopsis” on Page 6.

Data Sheet 4 V1.2, 2007-03

XC164GM

Derivatives

Summary of Features

• Programmable Watchdog Timer and Oscillator Watchdog

• Up to 47 General Purpose I/O Lines,

partly with Selectable Input Thresholds and Hysteresis

• On-Chip Bootstrap Loader

• On-Chip Debug Support via JTAG Interface

• 64-Pin Green LQFP Package for the -16F derivatives, 0.5 mm (19.7 mil) pitch (RoHS

compliant)

• 64-Pin TQFP Package for the -4F/8F derivatives, 0.5 mm (19.7 mil) pitch (RoHS

compliant)

Ordering Information

The ordering code for Infineon microcontrollers provides an exact reference to the

required product. This ordering code identifies:

• the derivative itself, i.e. its function set, the temperature range, and the supply voltage

• the package and the type of delivery.

For the available ordering codes for the XC164GM please refer to your responsible sales

representative or your local distributor.

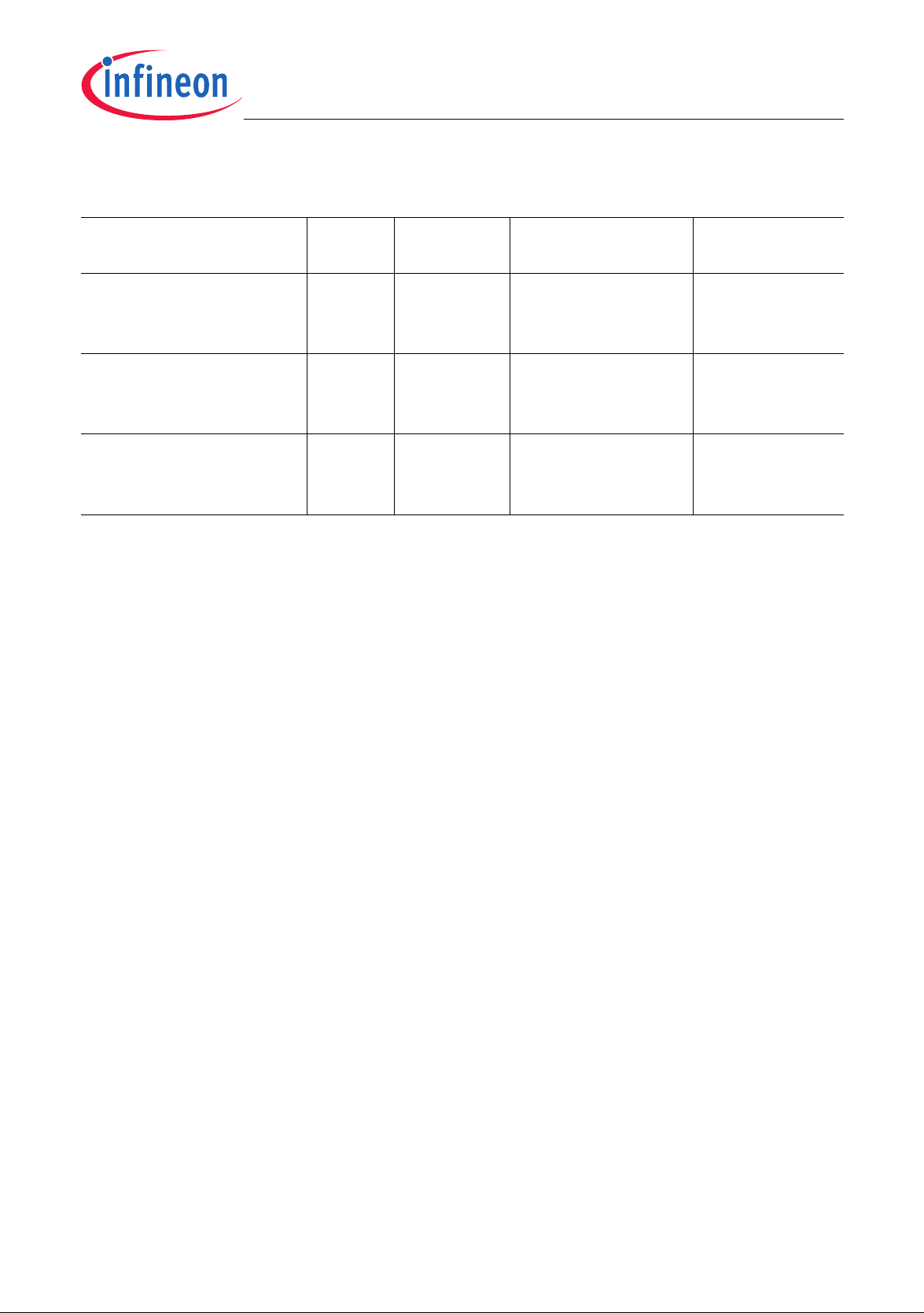

This document describes several derivatives of the XC164GM group. Table 1

enumerates these derivatives and summarizes the differences. As this document refers

to all of these derivatives, some descriptions may not apply to a specific product.

For simplicity all versions are referred to by the term XC164GM throughout this

document.

Data Sheet 5 V1.2, 2007-03

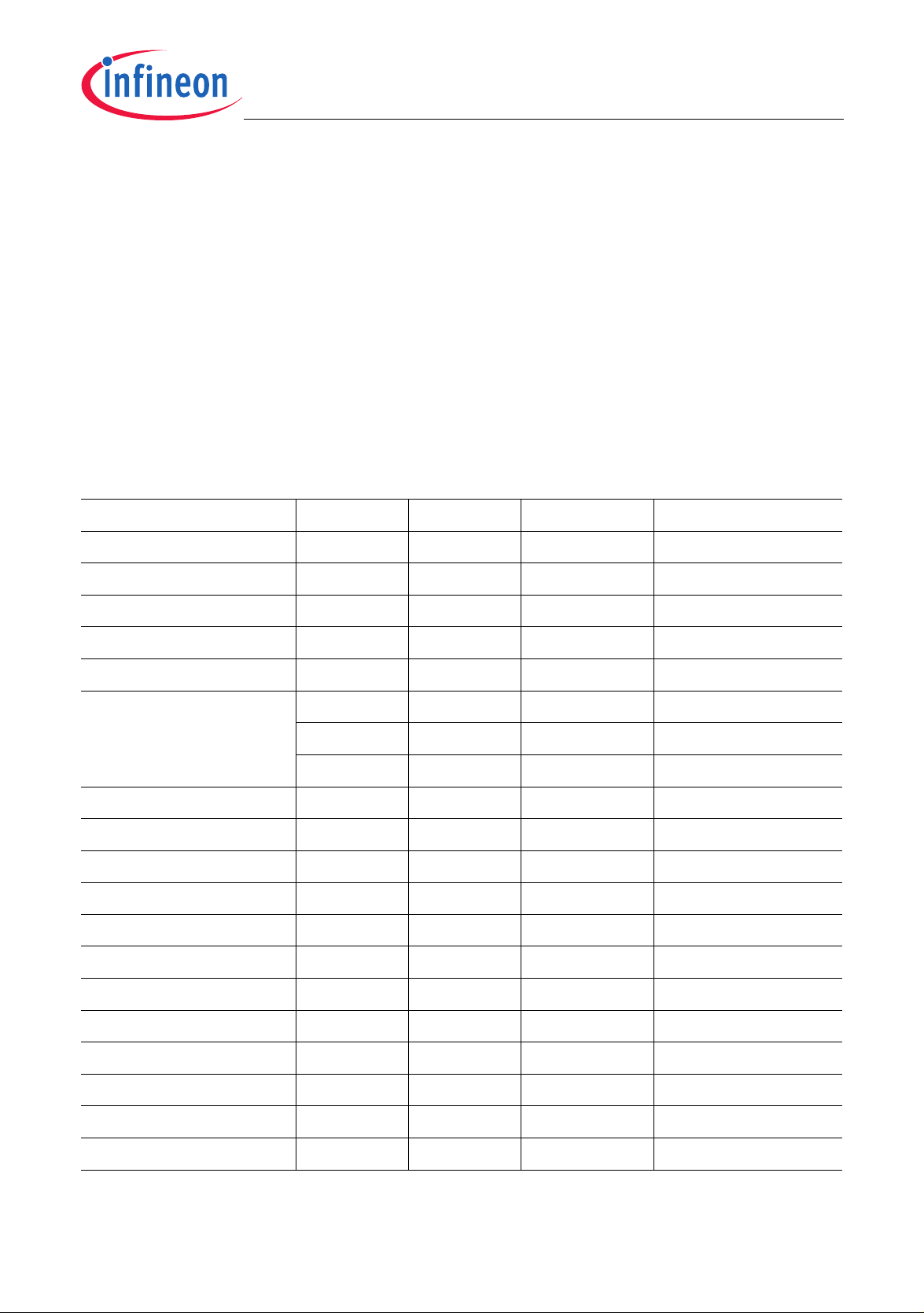

Table 1 XC164GM Derivative Synopsis

Derivative

1)

Temp.

Range

Program

Memory

XC164GM

Derivatives

Summary of Features

On-Chip RAM Interfaces

SAF-XC164GM-16F40F

SAF-XC164GM-16F20F

-40 to

85 °C

128 Kbytes

Flash

2 Kbytes DPRAM,

4 Kbytes DSRAM,

2 Kbytes PSRAM

SAF-XC164GM-8F40F

SAF-XC164GM-8F20F

-40 to

85 °C

64 Kbytes

Flash

2 Kbytes DPRAM,

2 Kbytes DSRAM,

2 Kbytes PSRAM

SAF-XC164GM-4F40F

SAF-XC164GM-4F20F

1) This Data Sheet is valid for:

devices starting with and including design step BA for the -16F derivatives, and for

devices starting with and including design step AA for -4F/8F derivatives.

-40 to

85 °C

32 Kbytes

Flash

2 Kbytes DPRAM,

2 Kbytes PSRAM

ASC0, ASC1,

SSC0, SSC1,

CAN0, CAN1

ASC0, ASC1,

SSC0, SSC1,

CAN0, CAN1

ASC0, ASC1,

SSC0, SSC1,

CAN0, CAN1

Data Sheet 6 V1.2, 2007-03

XC164GM

Derivatives

General Device Information

2 General Device Information

The XC164GM derivatives are high-performance members of the Infineon

XC166 Family of full featured single-chip CMOS microcontrollers. These devices extend

the functionality and performance of the C166 Family in terms of instructions (MAC unit),

peripherals, and speed. They combine high CPU performance (up to 40 million

instructions per second) with high peripheral functionality and enhanced IO-capabilities.

They also provide clock generation via PLL and various on-chip memory modules such

as program Flash, program RAM, and data RAM.

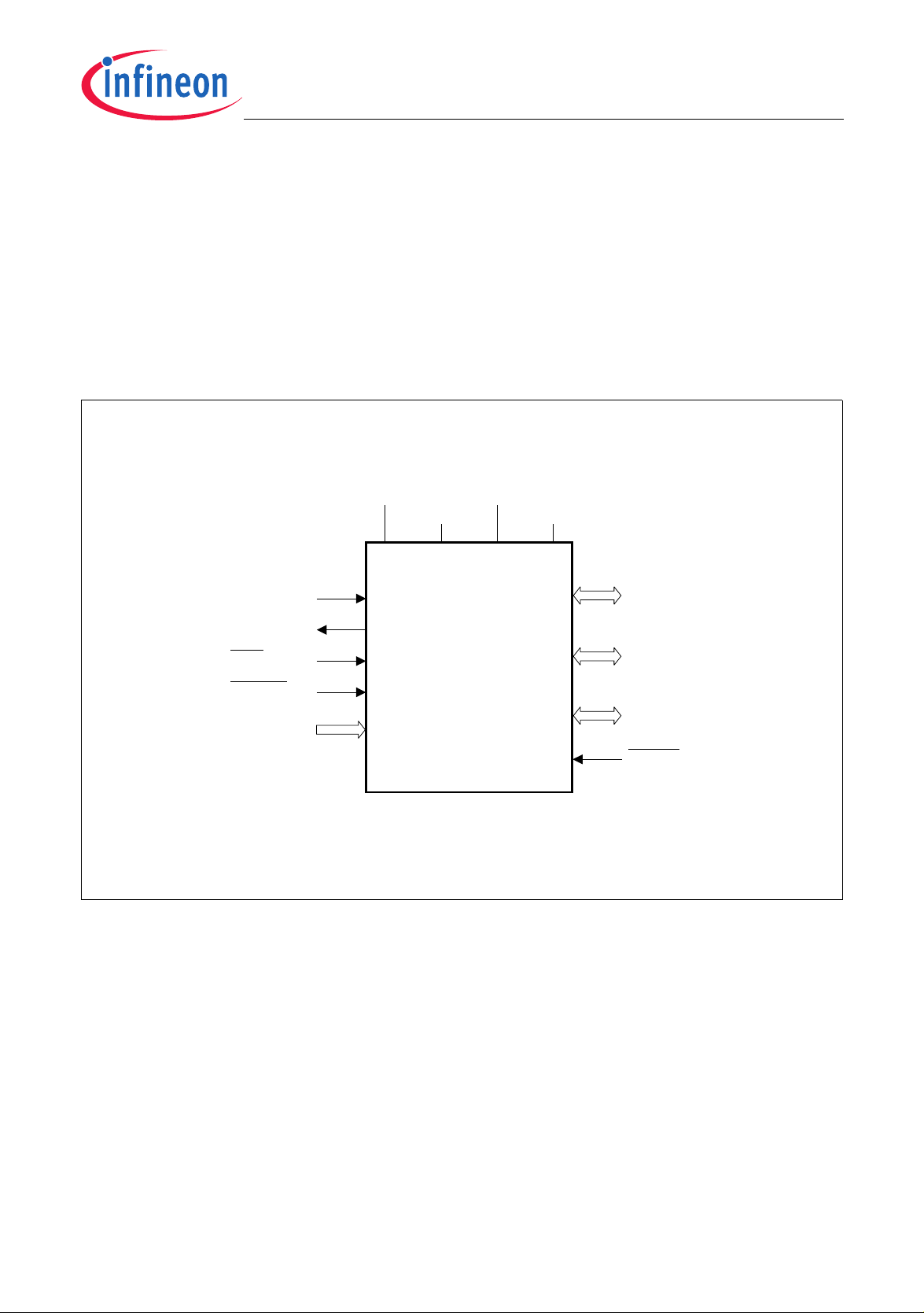

XTAL1

XTAL2

NMI

RSTIN

Port 5

14 bit

Figure 1 Logic Symbol

V

AREF

V

V

AGND

DDI/P

XC164GM

V

SS

PORT1

14 bit

Port 3

15 bit

Port 9

6 bit

TRST

MCA05554_XC164GM

Data Sheet 7 V1.2, 2007-03

XC164GM

*

*

Derivatives

General Device Information

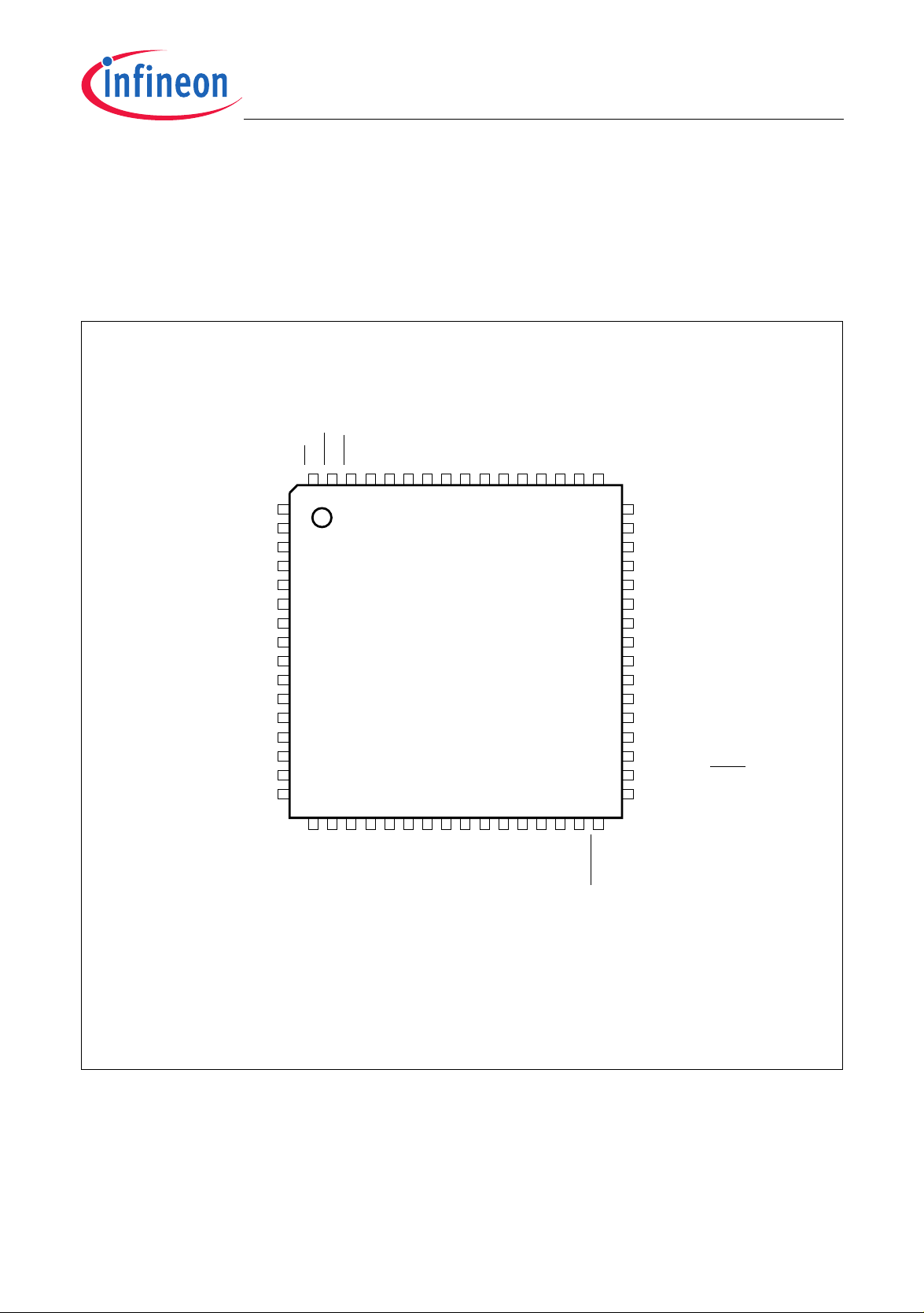

2.1 Pin Configuration and Definition

The pins of the XC164GM are described in detail in Table 2, including all their alternate

functions. Figure 2 summarizes all pins in a condensed way, showing their location on

the 4 sides of the package. E* marks pins to be used as alternate external interrupt

inputs.

DDP

DDI

SS

V

TRST

RSTIN

NMI

V

XTAL1

XTAL2

P1 L.6

P1L.7/CC22IO

V

P1L.3

P1L.4

P1L.5

P1L.0

P1L.1

P1L.2

P1 H. 0/ EX0I N/ CC 23 IO

P1 H. 1/ EX1I N/ MR ST1

P1 H. 2/ EX2I N/ MT RS1

P1 H. 3/ EX3I N/ T7I N/ SCL K1

P1H.4/CC24IO/EX4IN

5

I

/

E

5

X

I

O

2

C

5

/

C

.

P

1

H

V

SS

V

DDP

P5.0/AN0

P5.1/AN1

P5.2/AN2

P5.3/AN3

P5.4/AN4

P5.5/AN5

P5.10/AN10/T6EUD

P5.11/AN11/T5EUD

49505152535455565758596061626364

P9.5/CC21IO

1

2

3

4

5

N

6

7

8

9

XC164GM

10

11

12

13

14

15

16

48

P9.4/CC20IO

47

46

P9.3/CC19IO/CAN1_TxD

P9.2/CC18IO/CAN1_RxD/E

45

P9.1/CC17IO/CAN2_TxD

44

43

P9.0/CC16IO/CAN2_RxD/E

42

P3.15/CLKOUT/FOUT

V

41

SS

40

V

DDP

39

P3 .1 3/SC LK0 /E*

P3.11/RxD0/E*

38

P3.10/TxD0/E*

37

P3 .9 /M TSR 0

36

P3 .8 /M RST0

35

34

P3 .7 /T 2I N/ BRKIN

33

P3 .6 /T 3I N

32313029282726252423222120191817

SS

DDI

AREF

AGND

V

V

P5.6/AN6

P5.7/AN7

P5.12/AN12/T6IN

P5.13/AN13/T5IN

P5.14/AN14/T4EUD

P5.15/AN15/T2EUD

DDP

V

V

V

P3.2/CAPIN/TDI

P3.3/T3OUT/TDO

P3.4/T3EUD/TMS

P3.1/T6OUT/RxD1/TCK/E*

P3.5/T4IN/TxD1/BRKOUT

mc_xc164gm_pinout .vsd

Figure 2 Pin Configuration (top view)

Data Sheet 8 V1.2, 2007-03

Table 2 Pin Definitions and Functions

XC164GM

Derivatives

General Device Information

Symbol

Pin

Num.

Input

Outp.

Function

RSTIN 63 I Reset Input with Schmitt-Trigger characteristics. A low-level

at this pin while the oscillator is running resets the XC164GM.

A spike filter suppresses input pulses < 10 ns. Input pulses

> 100 ns safely pass the filter. The minimum duration for a

safe recognition should be 100 ns + 2 CPU clock cycles.

Note: The reset duration must be sufficient to let the

hardware configuration signals settle.

External circuitry must guarantee low-level at the

RSTIN

pin at least until both power supply voltages

have reached the operating range.

NMI

64 I Non-Maskable Interrupt Input. A high to low transition at this

pin causes the CPU to vector to the NMI trap routine. When

the PWRDN (power down) instruction is executed, the NMI

pin must be low in order to force the XC164GM into power

down mode. If NMI

is high, when PWRDN is executed, the

part will continue to run in normal mode.

If not used, pin NMI

should be pulled high externally.

Port 9

P9.0

P9.1

P9.2

P9.3

P9.4

P9.5

43-48

43

44

45

46

47

48

IO

I/O

I

I

I/O

O

I/O

I

I

I/O

O

I/O

I/O

Port 9 is a 6-bit bidirectional I/O port. Each pin can be

programmed for input (output driver in high-impedance state)

or output (configurable as push/pull or open drain driver). The

input threshold of Port 9 is selectable (standard or special).

The following Port 9 pins also serve for alternate functions:

CC16IO: (CAPCOM2) CC16 Capture Inp./Compare Outp.,

CAN2_RxD: (CAN Node 2) Receive Data Input

1)

,

EX5IN: (Fast External Interrupt 5) Input (alternate pin A)

CC17IO: (CAPCOM2) CC17 Capture Inp./Compare Outp.,

CAN2_TxD: (CAN Node 2) Transmit Data Output,

CC18IO: (CAPCOM2) CC18 Capture Inp./Compare Outp.,

CAN1_RxD: (CAN Node 1) Receive Data Input

1)

,

EX4IN: (Fast External Interrupt 4) Input (alternate pin A)

CC19IO: (CAPCOM2) CC19 Capture Inp./Compare Outp.,

CAN1_TxD: (CAN Node 1) Transmit Data Output,

CC20IO: (CAPCOM2) CC20 Capture Inp./Compare Outp.

CC21IO: (CAPCOM2) CC21 Capture Inp./Compare Outp.

Note: At the end of an external reset P9.4 and P9.5 also may

input startup configuration values.

Data Sheet 9 V1.2, 2007-03

Table 2 Pin Definitions and Functions (cont’d)

XC164GM

Derivatives

General Device Information

Symbol

Port 5

P5.0

P5.1

P5.2

P5.3

P5.4

P5.5

P5.10

P5.11

P5.6

P5.7

P5.12

P5.13

P5.14

P5.15

Pin

Num.

9-18,

21-24

9

10

11

12

13

14

15

16

17

18

21

22

23

24

Input

Outp.

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Function

Port 5 is a 14-bit input-only port.

The pins of Port 5 also serve as analog input channels for the

A/D converter, or they serve as timer inputs:

AN0

AN1

AN2

AN3

AN4

AN5

AN10 (T6EUD): GPT2 Timer T6 Ext. Up/Down Ctrl. Inp.

AN11 (T5EUD): GPT2 Timer T5 Ext. Up/Down Ctrl. Inp.

AN6

AN7

AN12 (T6IN): GPT2 Timer T6 Count/Gate Input

AN13 (T5IN): GPT2 Timer T5 Count/Gate Input

AN14 (T4EUD): GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.

AN15 (T2EUD): GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.

TRST

62 I Test-System Reset Input. For normal system operation, pin

TRST

edge of RSTIN

should be held low. A high level at this pin at the rising

enables the hardware configuration and

activates the XC164GM’s debug system. In this case, pin

TRST

must be driven low once to reset the debug system.

Data Sheet 10 V1.2, 2007-03

Table 2 Pin Definitions and Functions (cont’d)

XC164GM

Derivatives

General Device Information

Symbol

Port 3

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

P3.8

P3.9

P3.10

P3.11

P3.13

P3.15

Pin

Num.

28-39,

42

28

29

30

31

32

33

34

35

36

37

38

39

42

Input

Outp.

IO

O

I/O

I

I

I

I

O

O

I

I

I

O

O

I

I

I

I/O

I/O

O

I

I/O

I

I/O

I

O

O

Function

Port 3 is a 13-bit bidirectional I/O port. Each pin can be

programmed for input (output driver in high-impedance state)

or output (configurable as push/pull or open drain driver). The

input threshold of Port 3 is selectable (standard or

special).The following Port 3 pins also serve for alternate

functions:

T6OUT: [GPT2] Timer T6 Toggle Latch Output,

RxD1: [ASC1] Data Input (Async.) or Inp./Outp. (Sync.),

EX1IN: [Fast External Interrupt 1] Input (alternate pin A),

TCK: [Debug System] JTAG Clock Input

CAPIN: [GPT2] Register CAPREL Capture Input,

TDI: [Debug System] JTAG Data In

T3OUT: [GPT1] Timer T3 Toggle Latch Output,

TDO: [Debug System] JTAG Data Out

T3EUD: [GPT1] Timer T3 External Up/Down Control Input,

TMS: [Debug System] JTAG Test Mode Selection

T4IN: [GPT1] Timer T4 Count/Gate/Reload/Capture Inp.

TxD1: [ASC0] Clock/Data Output (Async./Sync.),

BRKOUT

: [Debug System] Break Out

T3IN: [GPT1] Timer T3 Count/Gate Input

T2IN: [GPT1] Timer T2 Count/Gate/Reload/Capture Inp.

BRKIN

: [Debug System] Break In

MRST0: [SSC0] Master-Receive/Slave-Transmit In/Out.

MTSR0: [SSC0] Master-Transmit/Slave-Receive Out/In.

TxD0: [ASC0] Clock/Data Output (Async./Sync.),

EX2IN: [Fast External Interrupt 2] Input (alternate pin B)

RxD0: [ASC0] Data Input (Async.) or Inp./Outp. (Sync.),

EX2IN: [Fast External Interrupt 2] Input (alternate pin A)

SCLK0: [SSC0] Master Clock Output / Slave Clock Input.,

EX3IN: [Fast External Interrupt 3] Input (alternate pin A)

CLKOUT: System Clock Output (= CPU Clock),

FOUT: Programmable Frequency Output

Data Sheet 11 V1.2, 2007-03

Table 2 Pin Definitions and Functions (cont’d)

XC164GM

Derivatives

General Device Information

Symbol

PORT1

P1L.7

P1H.0

P1H.1

P1H.2

P1H.3

P1H.4

P1H.5

Pin

Num.

1-6,

49-56

56

1

2

3

3

5

6

Input

Outp.

IO

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

Function

PORT1 consists of one 8-bit and one 6-bit bidirectional I/O

port P1L and P1H. Each pin can be programmed for input

(output driver in high-impedance state) or output.

The following PORT1 pins also serve for alt. functions:

CC22IO: [CAPCOM2] CC22 Capture Inp./Compare Outp.

EX0IN: [Fast External Interrupt 0] Input (default pin),

CC23IO: [CAPCOM2] CC23 Capture Inp./Compare Outp.

EX1IN: [Fast External Interrupt 1] Input (default pin),

MRST1: [SSC1] Master-Receive/Slave-Transmit In/Out.

EX2IN: [Fast External Interrupt 2] Input (default pin),

MTSR1: [SSC1] Master-Transmit/Slave-Receive Out/Inp.

T7IN: [CAPCOM2] Timer T7 Count Input,

SCLK1: [SSC1] Master Clock Output / Slave Clock Input,

EX3IN: [Fast External Interrupt 3] Input (default pin),

CC24IO: [CAPCOM2] CC24 Capture Inp./Compare Outp.,

EX4IN: [Fast External Interrupt 4] Input (default pin)

CC25IO: [CAPCOM2] CC25 Capture Inp./Compare Outp.,

EX5IN: [Fast External Interrupt 5] Input (default pin)

XTAL2

XTAL16160

V

V

V

AREF

AGND

DDI

19 – Reference voltage for the A/D converter

20 – Reference ground for the A/D converter

26, 58 – Digital Core Supply Voltage (On-Chip Modules):

O

I

Note: At the end of an external reset P1H.4 and P1H.5 also

may input startup configuration values

XTAL2: Output of the oscillator amplifier circuit

XTAL1: Input to the oscillator amplifier and input to the

internal clock generator

To clock the device from an external source, drive XTAL1,

while leaving XTAL2 unconnected. Minimum and maximum

high/low and rise/fall times specified in the AC Characteristics

must be observed.

Note: Input pin XTAL1 belongs to the core voltage domain.

Therefore, input voltages must be within the range

defined for

V

DDI

.

+2.5 V during normal operation and idle mode.

Please refer to the Operating Condition Parameters

Data Sheet 12 V1.2, 2007-03

Table 2 Pin Definitions and Functions (cont’d)

XC164GM

Derivatives

General Device Information

Symbol

V

DDP

Pin

Num.

8, 27,

40, 57

Input

Function

Outp.

– Digital Pad Supply Voltage (Pin Output Drivers):

+5 V during normal operation and idle mode.

Please refer to the Operating Condition Parameters

V

SS

7, 25,

41, 59

– Digital Ground

Connect decoupling capacitors to adjacent

as close as possible to the pins.

All

V

pins must be connected to the ground-line or ground-

SS

plane.

1) The CAN interface lines are assigned to port P9 under software control.

V

DD/VSS

pin pairs

Data Sheet 13 V1.2, 2007-03

XC164GM

d

Derivatives

Functional Description

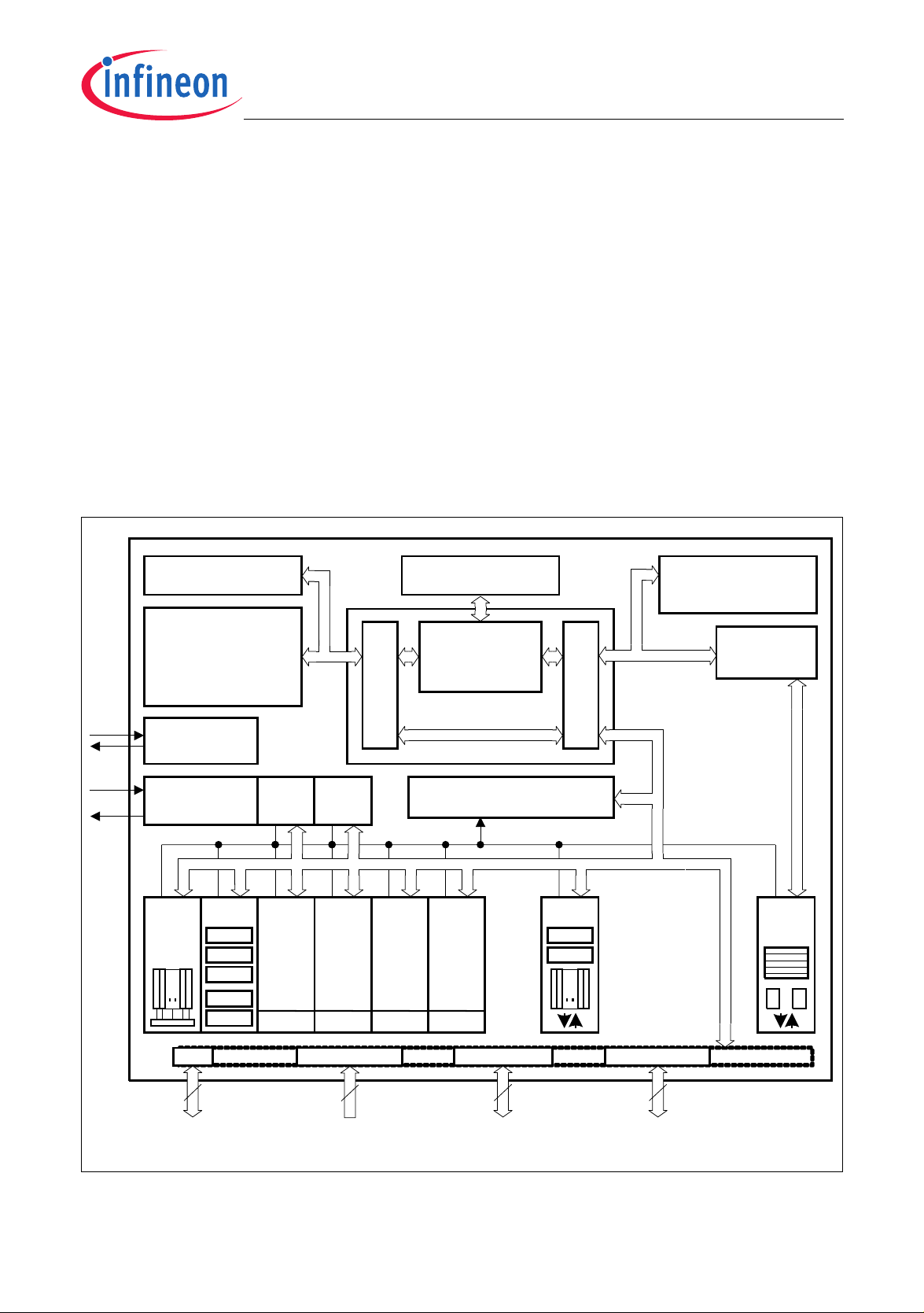

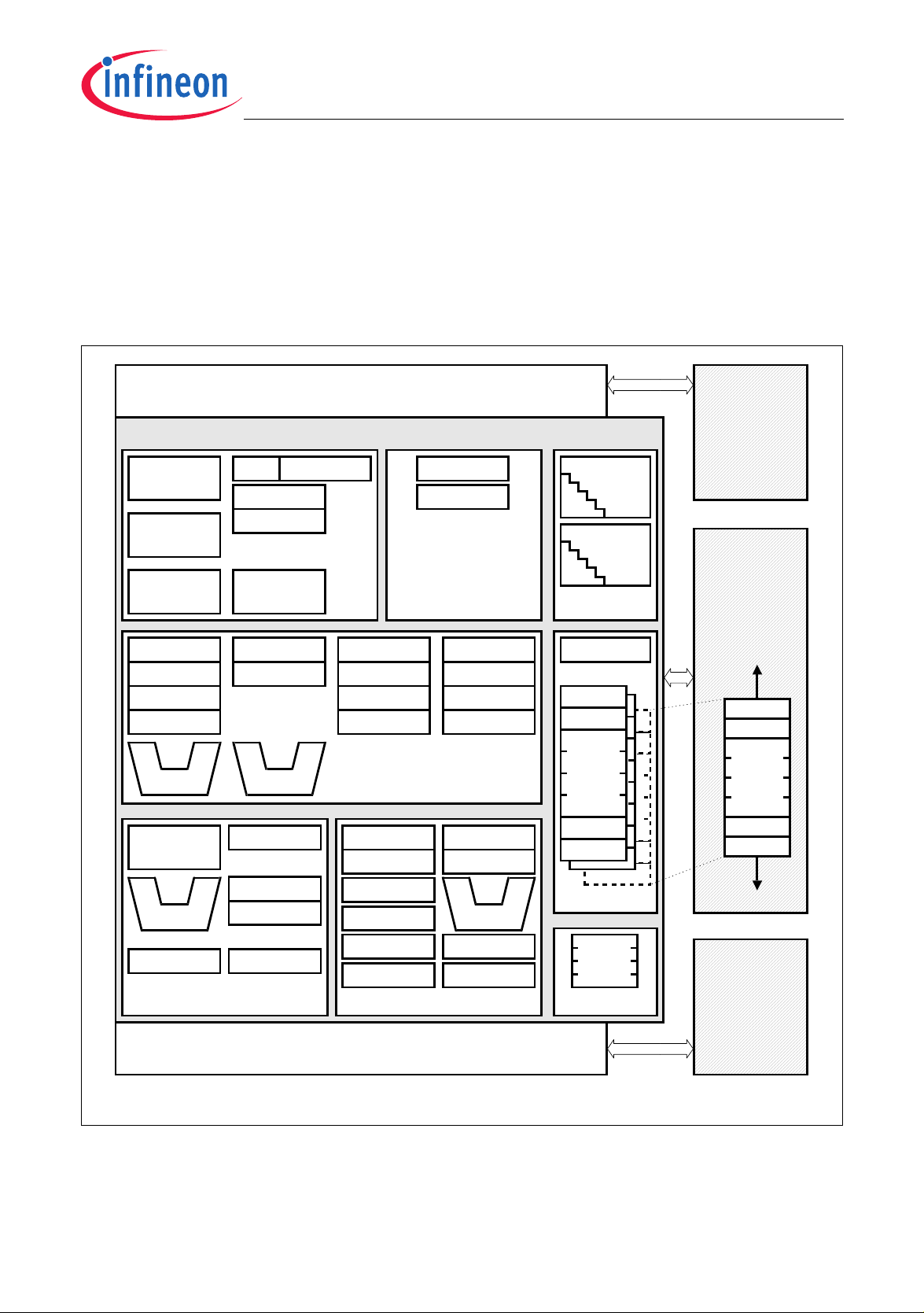

3 Functional Description

The architecture of the XC164GM combines advantages of RISC, CISC, and DSP

processors with an advanced peripheral subsystem in a very well-balanced way. In

addition, the on-chip memory blocks allow the design of compact systems-on-silicon with

maximum performance (computing, control, communication).

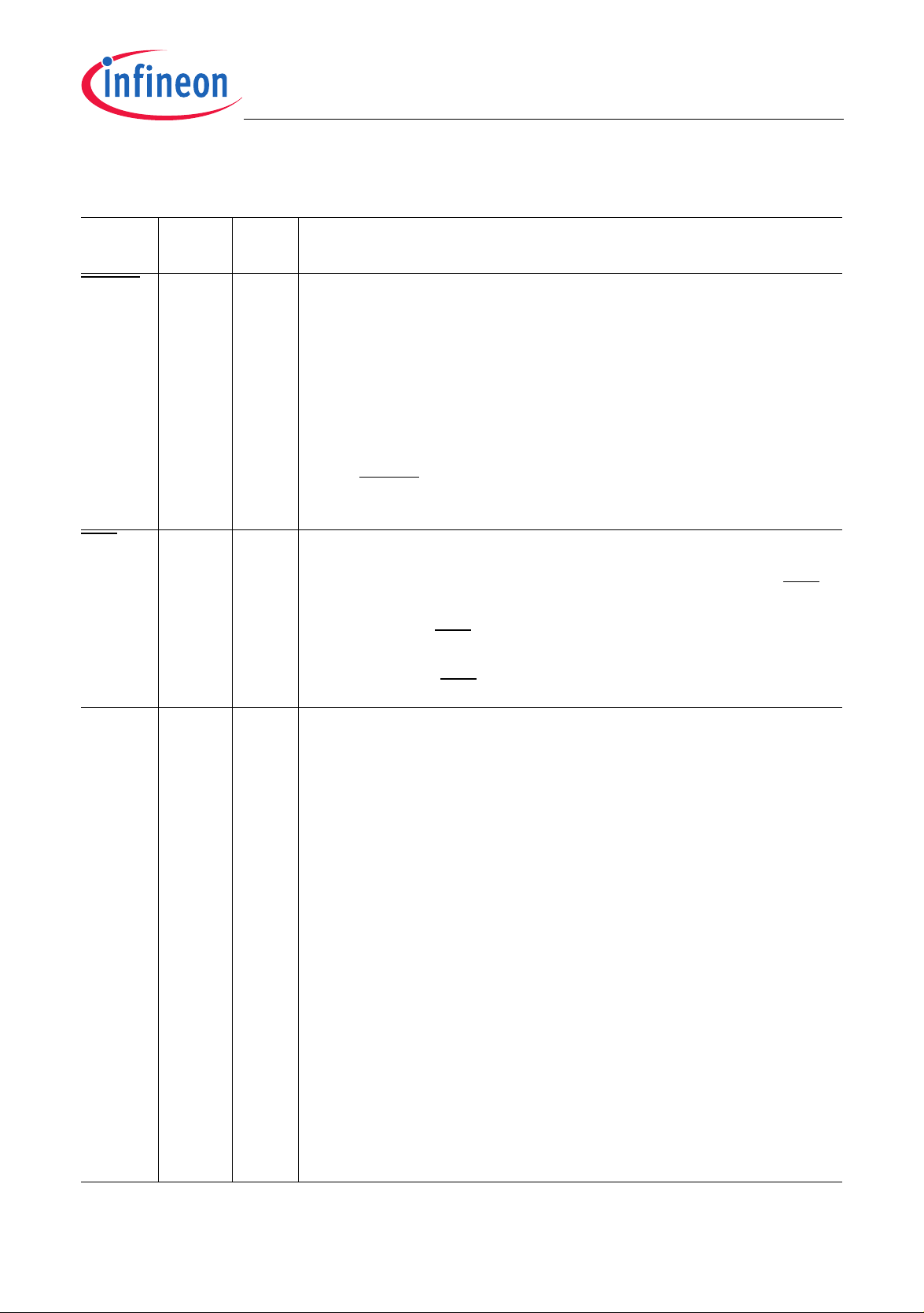

The on-chip memory blocks (program code-memory and SRAM, dual-port RAM, data

SRAM) and the set of generic peripherals are connected to the CPU via separate buses.

Another bus, the LXBus, connects additional on-chip resources (see Figure 3).

This bus structure enhances the overall system performance by enabling the concurrent

operation of several subsystems of the XC164GM.

The following block diagram gives an overview of the different on-chip components and

of the advanced, high bandwidth internal bus structure of the XC164GM.

XTAL

PSRAM

2 Kbytes

ProgMem

Flash

32/64/128 Kbytes

OCDS

Debug Support

Osc / PLL

Clock Generation

ADC

8/10-Bit

C hannels

GPT

14

T2

T3

T4

T5

T6

RTC WDT

ASC0

(USART)

BRGen

ASC1

(USART)

BRGen

PMU

SSC0

(SPI)

BRGen

DPRAM

2 Kbytes

CPU

C166SV2-Core

Interrupt & PEC

SSC1

(SPI)

BRGen

DMU

Interrupt B us

P eripheral Dat a Bus

CC2

T7

T8

DSRAM

0/2/4 Kbytes

reduced

LXBus

EBC

Control

Twin

LXBus

CAN

A B

Port 5

6

14

13

POR T1Port 3Port 9

14

Mc_xc164gm_block1.vs

Figure 3 Block Diagram

Data Sheet 14 V1.2, 2007-03

XC164GM

Derivatives

Functional Description

3.1 Memory Subsystem and Organization

The memory space of the XC164GM is configured in a von Neumann architecture, which

means that all internal and external resources, such as code memory, data memory,

registers and I/O ports, are organized within the same linear address space. This

common memory space includes 16 Mbytes and is arranged as 256 segments of

64 Kbytes each, where each segment consists of four data pages of 16 Kbytes each.

The entire memory space can be accessed byte wise or word wise. Portions of the

on-chip DPRAM and the register spaces (E/SFR) have additionally been made directly

bit addressable.

The internal data memory areas and the Special Function Register areas (SFR and

ESFR) are mapped into segment 0, the system segment.

The Program Management Unit (PMU) handles all code fetches and, therefore, controls

accesses to the program memories, such as Flash memory and PSRAM.

The Data Management Unit (DMU) handles all data transfers and, therefore, controls

accesses to the DSRAM and the on-chip peripherals.

Both units (PMU and DMU) are connected via the high-speed system bus to exchange

data. This is required if operands are read from program memory, code or data is written

to the PSRAM, or data is read from or written to peripherals on the LXBus (such as

TwinCAN). The system bus allows concurrent two-way communication for maximum

transfer performance.

32/64/128 Kbytes

1)

of on-chip Flash memory store code or constant data. The on-chip

Flash memory is organized as four 8-Kbyte sectors and up to three 32-Kbyte sectors.

Each sector can be separately write protected

2)

, erased and programmed (in blocks of

128 Bytes). The complete Flash area can be read-protected. A password sequence

temporarily unlocks protected areas. The Flash module combines very fast 64-bit onecycle read accesses with protected and efficient writing algorithms for programming and

erasing. Thus, program execution out of the internal Flash results in maximum

performance. Dynamic error correction provides extremely high read data security for all

read accesses.

Programming typically takes 2 ms per 128-byte block (5 ms max.), erasing a sector

typically takes 200 ms (500 ms max.).

2 Kbytes of on-chip Program SRAM (PSRAM) are provided to store user code or data.

The PSRAM is accessed via the PMU and is therefore optimized for code fetches.

0/2/4 Kbytes

1)

of on-chip Data SRAM (DSRAM) are provided as a storage for general

user data. The DSRAM is accessed via the DMU and is therefore optimized for data

accesses. DSRAM is not available in the XC164GM-4F derivatives.

1) Depends on the respective derivative. See Table 1 “XC164GM Derivative Synopsis” on Page 6.

2) Each two 8-Kbyte sectors are combined for write-protection purposes.

Data Sheet 15 V1.2, 2007-03

XC164GM

Derivatives

Functional Description

2 Kbytes of on-chip Dual-Port RAM (DPRAM) are provided as a storage for user

defined variables, for the system stack, general purpose register banks. A register bank

can consist of up to 16 word wide (R0 to R15) and/or byte wide (RL0, RH0, …, RL7, RH7)

so-called General Purpose Registers (GPRs).

The upper 256 bytes of the DPRAM are directly bit addressable. When used by a GPR,

any location in the DPRAM is bit addressable.

1024 bytes (2 × 512 bytes) of the address space are reserved for the Special Function

Register areas (SFR space and ESFR space). SFRs are word wide registers which are

used for controlling and monitoring functions of the different on-chip units. Unused SFR

addresses are reserved for future members of the XC166 Family. Therefore, they should

either not be accessed, or written with zeros, to ensure upward compatibility.

Table 3 XC164GM Memory Map

Address Area Start Loc. End Loc. Area Size

Flash register space FF’F000

H

FF’FFFF

H

4 Kbytes

1)

Notes

2)

Reserved (Acc. trap) F8’0000

Reserved for PSRAM E0’0800

Program SRAM E0’0000

Reserved for pr. mem. C2’0000

Program Flash C0’0000

C0’0000

C0’0000

Reserved 20’0800

TwinCAN registers 20’0000

Reserved 01’0000

SFR area 00’FE00

Dual-Port RAM 00’F600

Reserved for DPRAM 00’F200

ESFR area 00’F000

XSFR area 00’E000

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

FF’FFFF

F7’FFFF

E0’07FF

DF’FFFF

C1’FFFF

C0’FFFF

C0’7FFF

BF’FFFF

20’07FF

1F’FFFF

00’FFFF

00’FDFF

00’F5FF

00’F1FF

00’EFFF

508 Kbytes –

H

< 1.5 Mbytes Minus PSRAM

H

2 Kbytes –

H

< 2 Mbytes Minus Flash

H

128 Kbytes XC164GM-16F

H

64 Kbytes XC164GM-8F

H

32 Kbytes XC164GM-4F

H

< 10 Mbytes Minus TwinCAN

H

2 Kbytes Accessed via EBC

H

< 2 Mbytes Minus segment 0

H

0.5 Kbyte –

H

2 Kbytes –

H

1 Kbyte –

H

0.5 Kbyte –

H

4 Kbytes –

H

Reserved 00’D000

Data SRAM 00’C000

Reserved for DSRAM 00’8000

Reserved 00’0000

1) The areas marked with “<” are slightly smaller than indicated, see column “Notes”.

H

H

H

H

00’DFFF

00’CFFF

00’BFFF

00’7FFF

6 Kbytes –

H

4 Kbytes

H

16 Kbytes –

H

32 Kbytes –

H

3)

Data Sheet 16 V1.2, 2007-03

XC164GM

Derivatives

Functional Description

2) Not defined register locations return a trap code (1E9BH).

3) Depends on the respective derivative. See Table 1 “XC164GM Derivative Synopsis” on Page 6.

Data Sheet 17 V1.2, 2007-03

XC164GM

Derivatives

Functional Description

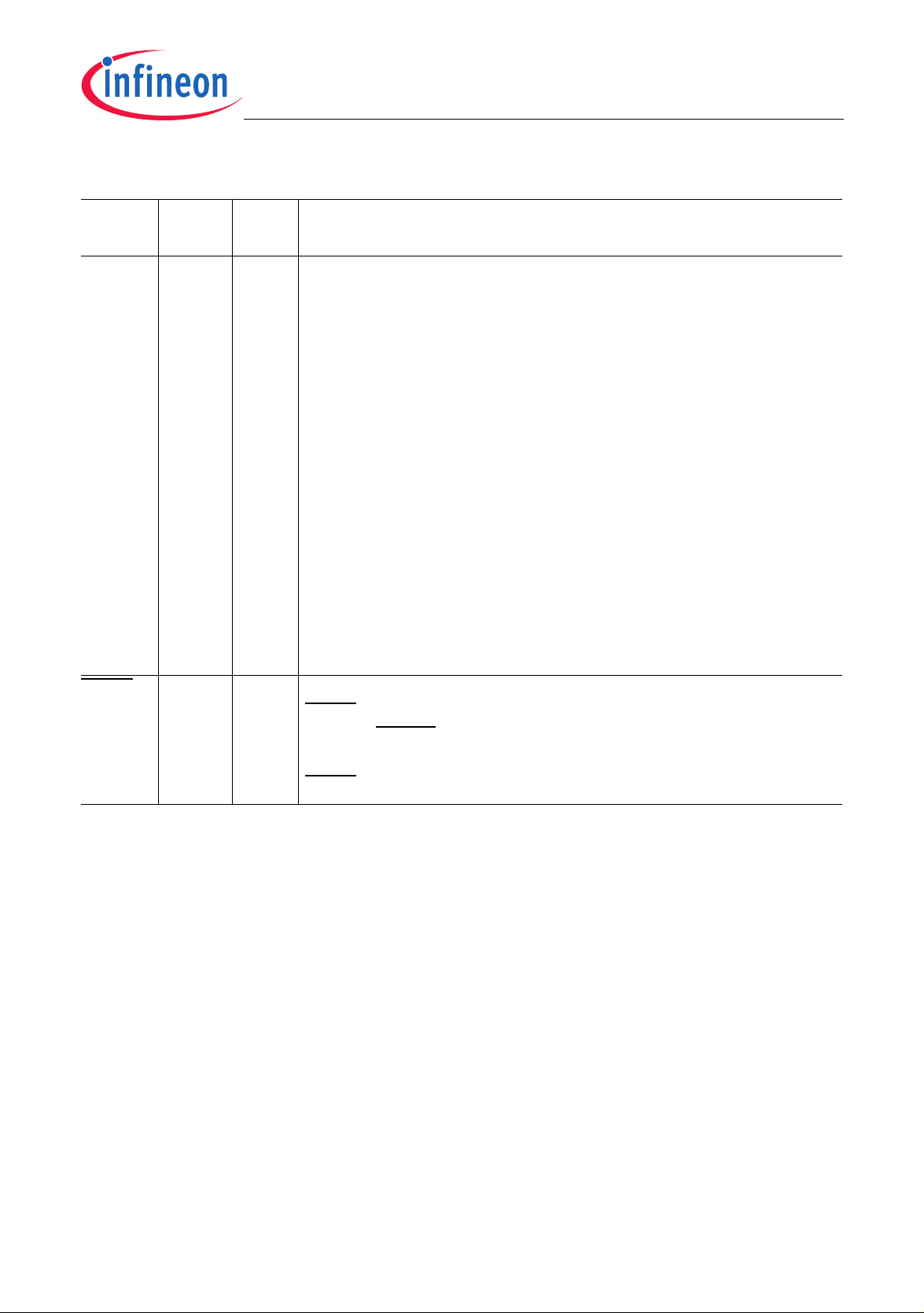

3.2 Central Processing Unit (CPU)

The main core of the CPU consists of a 5-stage execution pipeline with a 2-stage

instruction-fetch pipeline, a 16-bit arithmetic and logic unit (ALU), a 32-bit/40-bit multiply

and accumulate unit (MAC), a register-file providing three register banks, and dedicated

SFRs. The ALU features a multiply and divide unit, a bit-mask generator, and a barrel

shifter.

CPU

Prefetch

Branch

Multiply

Unit

Unit

FIFO

IDX0

IDX1

QX0

QX1

+/-

Unit

+/-

CSP IP

CPUCON1

CPUCON2

Return

Stack

QR0

QR1

+/-

MRW

MCW

MSW

IFU

DPP0

DPP1

DPP2

DPP3

Division Unit

M u ltiply U n it

MDC

PSW

VECSEG

TFR

Injection/

Exception

Handler

SPSEG

SP

STKOV

STKUN

Bit-Mask-Gen.

Barrel-Shifter

+/-

ADU

PMU

2-Stage

5-Stage

R15

R14

GPRs

GPRs

RF

Prefetch

Pipeline

Pipeline

CP

R15

R15

R14

R14

GPRs

R1

R1

R0

R1

R0

R0

PSRAM

Flash/ROM

DPRAM

IPIP

R15

R14

GPRs

R1

R0

MAC

MAH

MAL

MDH

ZEROS

MDL

ONES

ALU

Buffer

DMU

WB

DSRAM

EBC

Peripherals

mca04917_x.vsd

Figure 4 CPU Block Diagram

Based on these hardware provisions, most of the XC164GM’s instructions can be

executed in just one machine cycle which requires 25 ns at 40 MHz CPU clock. For

Data Sheet 18 V1.2, 2007-03

XC164GM

Derivatives

Functional Description

example, shift and rotate instructions are always processed during one machine cycle

independent of the number of bits to be shifted. Also multiplication and most MAC

instructions execute in one single cycle. All multiple-cycle instructions have been

optimized so that they can be executed very fast as well: for example, a 32-/16-bit

division is started within 4 cycles, while the remaining 15 cycles are executed in the

background. Another pipeline optimization, the branch target prediction, allows

eliminating the execution time of branch instructions if the prediction was correct.

The CPU has a register context consisting of up to three register banks with 16 word

wide GPRs each at its disposal. One of these register banks is physically allocated within

the on-chip DPRAM area. A Context Pointer (CP) register determines the base address

of the active register bank to be accessed by the CPU at any time. The number of

register banks is only restricted by the available internal RAM space. For easy parameter

passing, a register bank may overlap others.

A system stack of up to 32 Kwords is provided as a storage for temporary data. The

system stack can be allocated to any location within the address space (preferably in the

on-chip RAM area), and it is accessed by the CPU via the stack pointer (SP) register.

Two separate SFRs, STKOV and STKUN, are implicitly compared against the stack

pointer value upon each stack access for the detection of a stack overflow or underflow.

The high performance offered by the hardware implementation of the CPU can efficiently

be utilized by a programmer via the highly efficient XC164GM instruction set which

includes the following instruction classes:

• Standard Arithmetic Instructions

• DSP-Oriented Arithmetic Instructions

• Logical Instructions

• Boolean Bit Manipulation Instructions

• Compare and Loop Control Instructions

• Shift and Rotate Instructions

• Prioritize Instruction

• Data Movement Instructions

• System Stack Instructions

• Jump and Call Instructions

• Return Instructions

• System Control Instructions

• Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes

and words. A variety of direct, indirect or immediate addressing modes are provided to

specify the required operands.

Data Sheet 19 V1.2, 2007-03

Loading...

Loading...