Page 1

Auto Training: Traveo™ II SDL – restricted

AUTO TRAINING: TRAVEO(TM) II

Sample Driver Library

Rammohan K N (ATV MC BCH)

September 2020

Page 2

Copyright © Infineon Technologies AG 2020. All rights reserved.

2

Agenda

What is SDL? What does the SDL include?

Supported Toolchain

Folder Structure, Drivers, Middleware

Startup Sequence

Sample Blinky Main

Workspaces – Open, Build, Download, Debug, Run, Pause, Reset, and Stop

External Links

Support

1

2

3

4

5

6

7

8

2020-08-19, restricted

Page 3

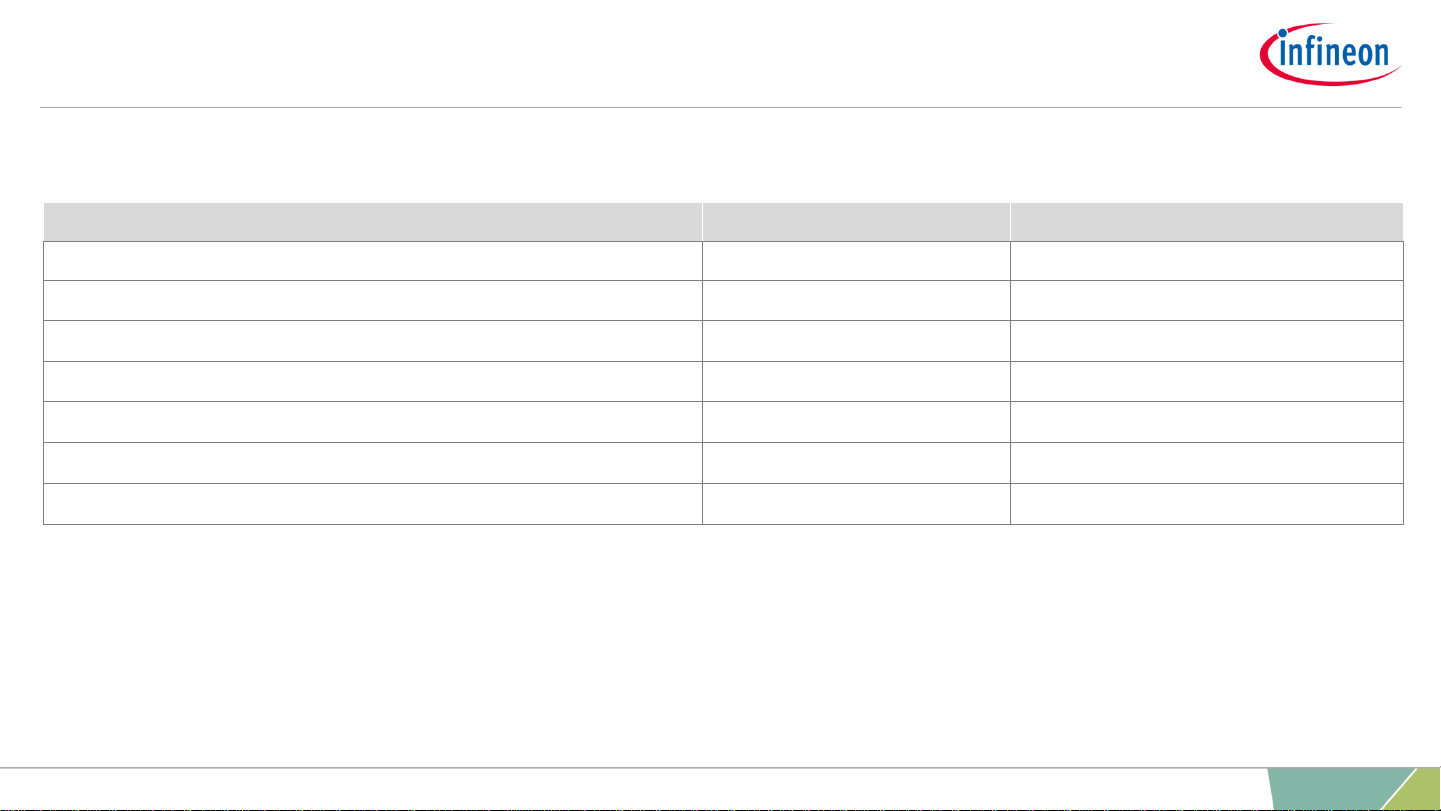

Target Products

Target product list for this training material

Family Category

Series

Code Flash Memory Size

Traveo™

II Automotive Body Controller Entry

CYT2B7

Up

to 1088KB

Traveo

II Automotive Body Controller Entry

CYT2B9

Up

to 2112KB

Traveo

II Automotive Body Controller Entry

CYT2BL

Up to 4160KB

Traveo

II Automotive Body Controller High

CYT3BB/4BB

Up to 4160KB

Traveo

II Automotive Body Controller High

CYT4BF

Up to 8384KB

Traveo

II Automotive Cluster

CYT3DL

Up to 4160KB

Traveo

II Automotive Cluster

CYT4DN

Up to 6336KB

3

2020-08-19, restricted Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 4

What is SDL

› Infineon’s Sample Driver Library (SDL) simplifies software development for

Traveo™ II devices

– Drivers for the extensive set of peripherals supported

– Arm®Cortex®Microcontroller Software Interface Standard (CMSIS) core access header

files directly from the CMSIS 5.0 release

– CMSIS complaint device header files, startup code (platform initialization), and device

configuration header files

– SDL Application Programming Interface Reference Manual

– Examples to evaluate various peripherals

› SDL is provided as an executable, tested on Windows 10 with a minimum

installation size requirement of around 350MB.

2020-08-19, restricted

4

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 5

Disclaimer

› SDL sample software is available for evaluation purposes only

› It does not adhere to any industry standard and it is not a production software

› Infineon may, but is not required to, provide technical support for the SDL

2020-08-19, restricted

5

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 6

What does the SDL Include

› The SDL contains

– Device-specific header files that provide a complete definition of all peripheral registers

and bits in the device

– CMSIS-compliant startup code to initialize the system after device reset, and transfer the

code execution to main()

– Linker files for each supported device and toolchain (IAR and GHS)

– SVD files with a detailed description of peripherals, registers, fields, and bit values

– GRD files to support register level debugging in GHS

2020-08-19, restricted

6

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 7

Supported Toolchain

› Green Hills MULTI: 7.1.4, Compiler: 2017.1.4, Probe Version: 5.6.5

– Development Autobuild 5.6 634260/AB as of patch #12996, or higher

– Flash loaders are not available as part of SDL and will be provided on case by case basis

through Infineon Customer Support (since the patches are in GBs, SDL becomes bulky)

› IAR Embedded Workbench for Arm 8.42.1 (EWARM-CD-8421-xxxxx.exe),

IAR I-Jet Debugger

– Flash loaders are available at the location

“\misc\tools\iar\ IAR_EWARM_8421_FlashLoader_Patch_TraveoII”

– Refer to “\misc\tools\iar\Readme_Patch.txt” to update the Traveo II patch for IAR

2020-08-19, restricted

7

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 8

Copyright © Infineon Technologies AG 2020. All rights reserved.

8

SDL Patch for the Tools

› Green Hills Tool Chain

– Install GHS MULTI, set license, and set probe firmware in advance

– Using the scripts tvii_detect.py and multi.irc, in \misc\tools\ghs\debugging\AppData_GHS,

execute the run process

– Copy the files to the <%APPDATA%\GHS> folder

(C:\Users\<LOGIN_NAME>\AppData\Roaming\GHS) on the PC

› IAR Patch: /misc/tools/iar/IAR_EWARM_8421_FlashLoader_Patch_TraveoII.7z

– Copy files of \misc\tools\iar\IAR_EWARM_8421_FlashLoader_Patch_TraveoII.7z to the

IAR install folder (do not copy anything at folder level)

– Restart IAR EWARM

– Rebuild All

– Download & Debug

2020-08-19, restricted

Page 9

Copyright © Infineon Technologies AG 2020. All rights reserved.

9

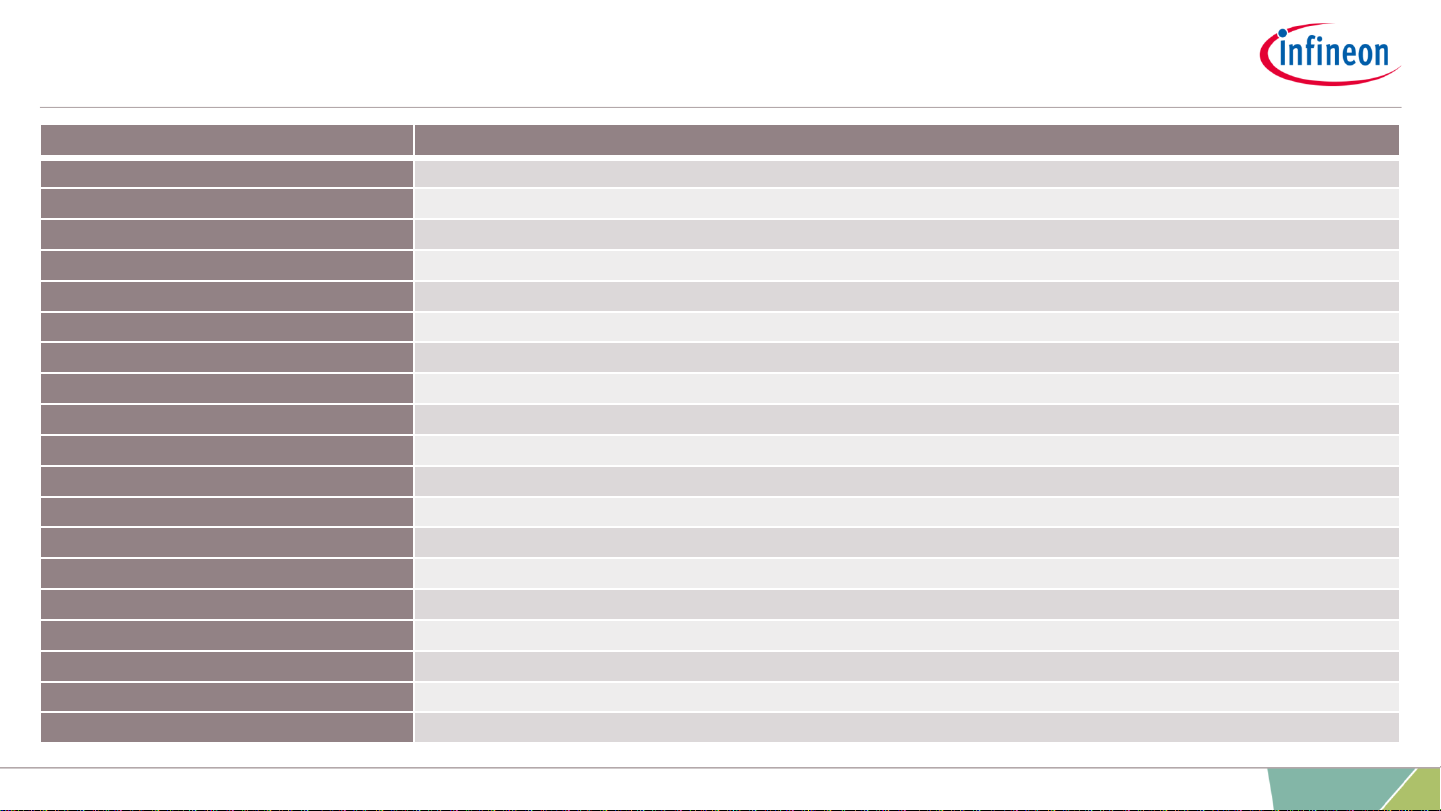

SDL Folder Structure (1/2)

2020-08-19, restricted

Path/Folder Description

common/ hdr/cmsis CMSIS core access headers

common/ src/drivers Drivers common across all the devices

common/ src/mw Middleware common across all the devices

common/ src/startup Tool specific startup code for all the devices

docs SDL API Documentation

misc/tools GHS/IAR specific flash loaders

tviibe1m/tviibe2m/tviibe4m

hdr Device specific header files, BSP for TV II Base Board, GPIO assignments

hdr/ip Device IP specific headers

hdr/mcureg IP Specific Register Addresses

src/drivers Driver source and respective headers specific to TVIIBE1M/2M/4M device

src/examples Code examples in accordance to TVIIBE1M/2M/4M device

src/system TVIIBE1M/2M/4M system specific code and system header for clock configurations

src/main_cm0plus.c Sample main source file for CM0+ core

src/cy_interrupt_map_cm0plus.h User interrupt mapping file used in case “CY_LINK_SYSTEM_IRQ_TABLE_TO_RAM” not defined

src/main_cm4.c Sample main source file for CM4 core

src/cy_interrupt_map_cm4.h User interrupt mapping file used in case “CY_LINK_SYSTEM_IRQ_TABLE_TO_RAM” not defined

tools/ghs GHS MULTI workspaces for SRAM/Flash for CM0+/CM4 cores, linker specific files, CMSIS SVD files, and GRD files

tools/iar IAR workspaces for SRAM/Flash for CM0+/CM4 cores, linker specific files, CMSIS SVD files

Page 10

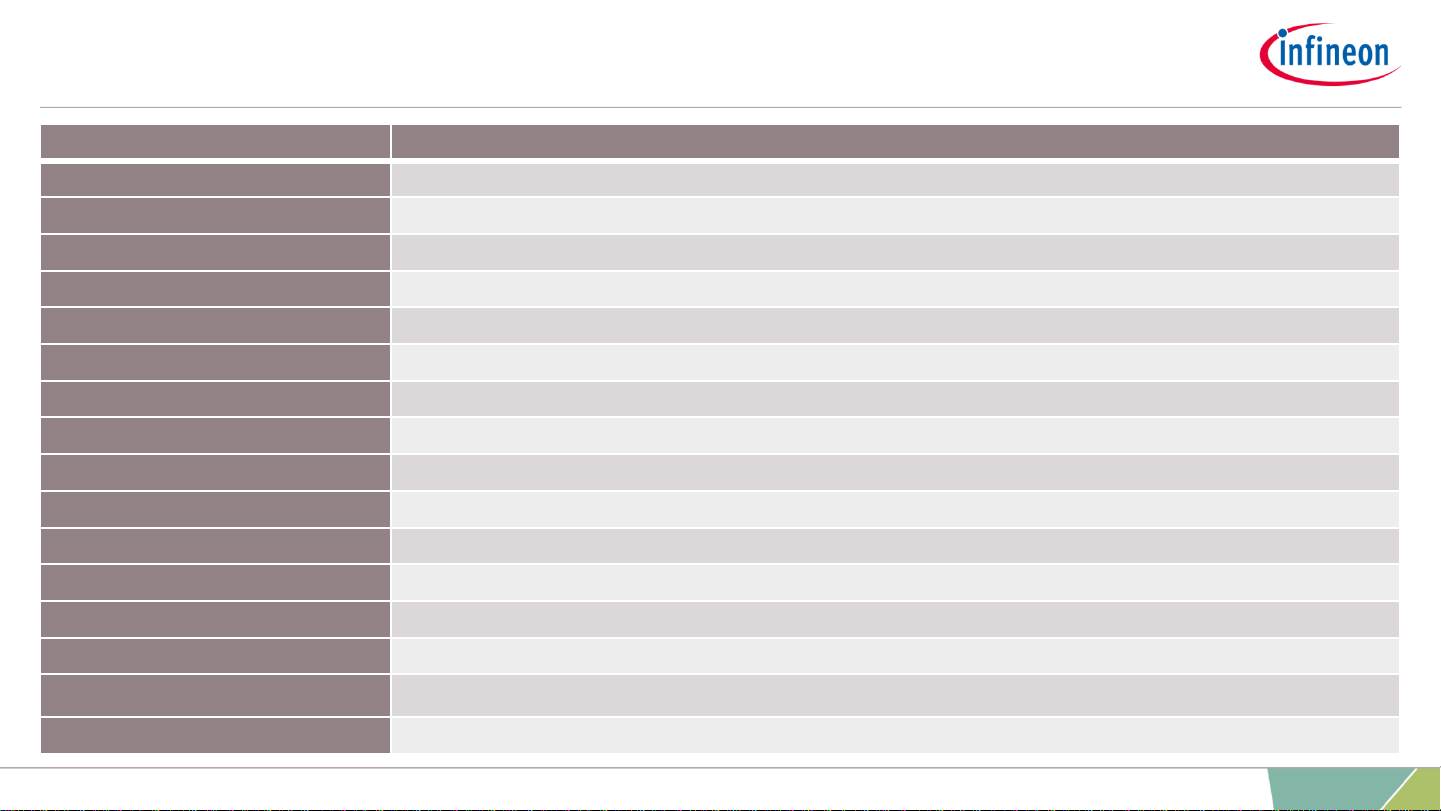

SDL Folder Structure (2/2)

2020-08-19, restricted

Path/Folder Description

tviibh4m/tviibh8m/tviic2d4m/tviic2d6m

hdr Device specific header files, BSP for TV II Base Board, GPIO assignments

hdr/ip Device IP specific headers

hdr/mcureg IP Specific Register Addresses

src/drivers Driver source and respective headers specific to TVIIBH4M/TVIIBH8M/TVIIC2D4M/TVIIC2D6M devices

src/mw/ Middleware support

src/examples Code examples in accordance device specific

src/system Device system specific code and system header for clock configurations

src/main_cm0plus.c Sample main source file for CM0+ core

src/cy_interrupt_map_cm0plus.h User interrupt mapping file used in case “CY_LINK_SYSTEM_IRQ_TABLE_TO_RAM” not defined

src/main_cm7_0.c Sample main source file for CM7_0 core

src/cy_interrupt_map_cm7_0.h User interrupt mapping file used in case “CY_LINK_SYSTEM_IRQ_TABLE_TO_RAM” not defined

src/main_cm7_1.c Sample main source file for CM7_0 core

src/cy_interrupt_map_cm7_1.h User interrupt mapping file used in case “CY_LINK_SYSTEM_IRQ_TABLE_TO_RAM” not defined

tools/ghs

GHS MULTI workspaces for SRAM/Flash for CM0+/CM7_0/CM7_1 cores, linker specific files, CMSIS SVD files, and GRD files

tools/iar IAR workspaces for SRAM/Flash for CM0+/CM7_0/CM7_1 cores, linker specific files, CMSIS SVD files

10

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 11

SDL Drivers (1/3)

2020-08-19, restricted

Driver Description API Functionality

ADC Analog to Digital Converter Manage ADC operations

Audioss

Sound Subsystem for I2S, DAC, Mixer, PWM,

SG, TDM (TVIIC2D6M only)

Manages I2S, Audio DAC, Mixer, PCM-PWM, Sound Generator, TDM as part of sound

subsystem

AXIDMA M-DMA on AXI bus Memory to memory transfer over AXI bus

CAN FD Controller Area Network Flexible Data-Rate Manages Classic and FD operations

CPU CPU driver Enables core of CPU specific features

CRYPTO Cryptographic Operations Perform cryptographic operations on user-designated data. Available as libraries

CXPI Clock eXtension Peripheral Interface Manages communication over CXPI interface

DMA Direct Access Memory

Perform memory-to-memory (M-DMA) and peripheral-to-memory (P-DMA) (and vice versa)

operations

ETHERNET Ethernet Basic ethernet driver supporting automotive and gigabit ethernet PHYs

EVTGEN Event Generator Performs event generation for interrupts and triggers in active power mode

FLASH Flash Memory Manage code/work flash memory operations

FLEXRAY FlexRay Interface Manages FlexRay communication

FPDLINK FDP-Link or LVDS Analog LVDS video driver

GPIO General Purpose I/O Ports Configure and access device input/output pins

GFX_ENV Graphics Environment Setup Sets up the Graphics environment

I2S Inter-IC Sound (TVII-B-H-8M Only)

Manage Inter-IC Sound. I2S is used to send digital audio streaming data to external I2S devices,

such as audio codecs or simple DACs. It can also receive digital audio streaming data

11

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 12

SDL Drivers (2/3)

2020-08-19, restricted

Driver Description API Functionality

IPC

Inter Process Communication

Manage data transfer between CPUs or processes in a device

LIN

Local Interconnect Network

Provides master and slave data transfer capabilities

LVD

Low Voltage Detection

Provides LVD capabilities

MCWDT

Multi

-counter Watchdog timer

Provides control and status capabilities

MIPICSI2

Video Input

Manage and control analog video inputs

MPU

Memory Protection Unit

Manages the configuration of MPU

PROT

Memory and Peripheral Protection

Manage the MPU, Shared MPU (SMPU), and Peripheral Protection Unit (PPU)

SCB

Serial Communication Block

Manage serial communication as I2C, SPI, or UART

SD_HOST

Secure

Digital Host Controller

Manages SD and eMMC devices

SMART IO

Smart I/O

Configure and access the Smart I/O hardware present between the GPIOs (pins) and HSIOMs (pin

muxes) on select device ports. It can be used to perform simple logic operations on peripheral and

GPIO signals at the GPIO port

SMIF

Serial Memory Interface

SPI

-based communication interface for interfacing external memory devices to TVII. The SMIF

supports Octal

-SPI, Dual Quad-SPI, Quad-

SPI, DSPI, and SPI. This interface also supports Hyper Bus

interfaces like HyperRAM and HyperFlash devices.

SROM

Internal SROM driver

APIs to support some basic access to SROM System calls

SYSCLK

System Clock

Provides APIs to control and read status of various clocking capabilities of the device

SYSFLT

System Fault

Controls CPUs fault processing Subsystem

SYSINT

System Interrupt

Manage interrupts and exceptions, in conjunction with the CMSIS core NVIC API

SYSLIB

System Library

Utility functions to handle delays, register read/write, asserts, silicon unique ID, and more

12

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 13

SDL Drivers (3/3)

2020-08-19, restricted

Driver Description API Functionality

SYSLIB

System Library

Utility functions to handle delays, register read/write, asserts, silicon unique ID, and more

SYSPM

System Power Modes

Controls device power modes

SYSREGHC/

SYSPMIC

REGHC/PMIC Control and Status

Controls High Current Regulator or the PMIC module

SYSRESET

System Reset

Provides APIs for reading reset reason and clearing them

SYSRTC

System Real Time Clock

Provides capabilities to handle RTC, Alarms etc.

SYSTICK

Systick Timer

Manage a 24

-bit down-counter timer

SYSWDT

Free running Watchdog timer

Provides control and status capabilities

TCPWM

Timer Counter PWM

Manage a 16

- or 32-bit periodic Counter, PWM, Quadrature decoder, Shift register

TRIGMUX

Trigger Multiplexer

Manage the multiplexing of trigger outputs to specific trigger inputs across multiple peripherals

13

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 14

SDL Middleware

› Device Specific

› Common

2020-08-19, restricted

Middleware Description API Functionality

GFX_ENV Graphics Environment Setup Supported only for TVIIC2D6M/TVIIC2D4M (Graphics environment setup support)

MIPI_SENSOR MIPI CSI2 controller Support top level MIPI CSI2 APIs for camera access map to capture interface of VIDEOSS IP

POWER

Reghc or PMIC based power control

REGHC or PMIC controller middleware (REGHC/TVIIBH4M/TVIIBH8M, PMIC/TVIIC2D6M/TVIIC2D4M)

SMIF_MEM SMIF SPI/Hyper Access Control SPI or HyperBus specific device support

Middleware Description API Functionality

Button Button middle layer APIs to support buttons

Semihosting SCB/UART middle layer Support top level UART APIs for debugging

SW_Timer Software Timer Enables multiple software timers

Flash Code and work flash User level APIs for ease of use

14

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 15

Device Startup Sequence

1. System Reset (@0x0000 0000)

2. CM0+ executes ROM boot (@0x0000 0004)

a. Applies trims

b. Applies debug access port (DAP) access restrictions and system protection from eFuse and supervisory

flash

c. Authenticates flash boot (only in SECURE life-cycle stage) and transfers control to it

3. CM0+ executes flash boot (from supervisory flash @0x1700 2000)

a. Configures debug pins as per the SWD/JTAG

b. Sets CM0+ vector offset register to the beginning of flash (@0x1000 0000)

c. CM0+ branches to its Reset handler

4. CM0+ starts execution

a. Moves CM0+ vector table to SRAM (updates CM0+ vector table base)

b. Sets CM4/7_VECTOR_TABLE_BASE to the location of CM4/7 vector table mentioned in flash

c. Releases CM4/7 from reset

d. Continues execution of CM0+ user application

5. CM4/7 executes directly from either code-flash or SRAM

a. CM4/7 branches to its Reset handler

b. Continues execution of CM4/7 user application

2020-08-19, restricted

15

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 16

Application Startup Sequence

1. System reset (@0x1000 0000)

2. Enables CM4/7 application core

3. CM0+ executes application main and calls “SystemInit”, which does the following:

a. Disables WDT

b. Applies flash wait states

c. Sets clock configuration

d. Enables generic system IRQ

e. Continues execution of CM0+ user application

2020-08-19, restricted

16

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 17

SDL Sample Blinky Example

› Location: \device\src\main_cm0plus.c

#include "cy_project.h“

#include "cy_device_headers.h“

#define USER_LED_PORT CY_LED0_PORT

#define USER_LED_PIN CY_LED0_PIN

#define USER_LED_PIN_MUX CY_LED0_PIN_MUX

cy_stc_gpio_pin_config_t user_led_port_pin_cfg =

{

.outVal = 0x00,

.driveMode = CY_GPIO_DM_STRONG_IN_OFF,

.hsiom = USER_LED_PIN_MUX,

.intEdge = 0,

.intMask = 0,

.vtrip = 0,

.slewRate = 0,

.driveSel = 0,

.vregEn = 0,

.ibufMode = 0,

.vtripSel = 0,

.vrefSel = 0,

.vohSel = 0,

};

2020-08-19, restricted

17

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 18

Copyright © Infineon Technologies AG 2020. All rights reserved.

18

SDL Sample Blinky Example (Continued)

int main(void)

{

SystemInit();

__enable_irq();

/* Enable CM4. CY_CORTEX_M4_APPL_ADDR is calculated in linker script, check it in case of

problems. */

Cy_SysEnableApplCore(CY_CORTEX_M4_APPL_ADDR);

/* Place your initialization/startup code here (e.g. MyInst_Start()) */

Cy_GPIO_Pin_Init(USER_LED_PORT, USER_LED_PIN, &user_led_port_pin_cfg);

for(;;)

{

// Wait 0.05 [s]

Cy_SysTick_DelayInUs(50000);

Cy_GPIO_Inv(USER_LED_PORT, USER_LED_PIN);

}

}

2020-08-19, restricted

Page 19

SDL Supported Workspaces

› Workspaces supported

– Flash

– Sram

› Flash workspace downloads the example application code onto device code flash

area and is permanent; the program will stay in between resets

› Sram workspace downloads the example application code onto device’s SRAM

area; a power on and off will wipe out the program

2020-08-19, restricted

19

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 20

SDL GHS Toolchain

› Green Hills Tool Chain

– Start the MULTI Project Manager and open the SDL project file

TVII_Sample_Driver_Library_rev/*device*/tools/ghs/*device*_*rev*_template.gpj

– Select the template

2020-08-19, restricted

20

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 21

SDL GHS Toolchain – Build (1/2)

› Building a project

2020-08-19, restricted

21

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 22

SDL GHS Toolchain – Build (2/2)

› Build a project

2020-08-19, restricted

22

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 23

SDL GHS Toolchain – Debug (1/2)

› Start the Debugger

2020-08-19, restricted

23

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 24

SDL GHS Toolchain – Debug (2/2)

› Detect the Debugger

2020-08-19, restricted

24

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 25

SDL GHS Toolchain - Load

› Load the program

2020-08-19, restricted

25

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 26

SDL GHS Toolchain - Run

› Run/Execute the program

2020-08-19, restricted

26

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 27

SDL IAR Toolchain

› IAR Embedded Workbench for Arm

– Refer to SDL Readme.txt for the installer

– Open the IDE

(Typical path: C:\Program Files (x86)\IAR Systems\Embedded Workbench 8.4\common\bin\IarIdePm.exe)

– Ensure the licenses are properly set for the build process

2020-08-19, restricted

27

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 28

SDL IAR Toolchain – Flash Workspace Example

› Open workspace from the IDE

2020-08-19, restricted

28

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 29

SDL IAR Toolchain - Build

› Build or Rebuild

2020-08-19, restricted

29

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 30

SDL IAR Toolchain – Download, Run

› Download

– Ensure power to the device

is enabled

› Run

– Observe the LED blink

2020-08-19, restricted

30

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 31

SDL IAR Toolchain – Debug

› Debug

– F10 – step over a function

– F11 – step into a function or

a statement

2020-08-19, restricted

31

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 32

SDL IAR Toolchain – Pause, Reset

› Pause

– Random pause halts at

any random instruction

– Use breakpoints to methodically

halt at a needed statement

› Reset

– Brings the control to the

beginning of main

2020-08-19, restricted

32

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 33

SDL IAR Toolchain – Stop

› Stop the debugger

› Make sure you do this before the power to the CPU board is removed

2020-08-19, restricted

33

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 34

SDL Examples Usage

› Using the examples provided

– Copy any example “main_**core**.c”1into the “\device\src” location

– Rebuild the project in the IDE

– Download and debug

– Go through the Readme.txt inside the example being used, understand the description,

do necessary hardware connections if required

2020-08-19, restricted

34

Copyright © Infineon Technologies AG 2020. All rights reserved.

1

**core** may indicate cm0plus or cm4 or cm7_0 or cm7_1

Page 35

SDL API Documentation

› API Documentation (\TVII-SampleSW\docs\SDL_**device**.chm)

› Modules supported are listed on the left pane

2020-08-19, restricted

35

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 36

Tools External Links

› External Links

– Overview EWARM

https://www.youtube.com/watch?v=sMLS4S3-htI

– IAR EWARM Download

http://files.iar.com/ftp/pub/box/EWARM-CD-8421-23878.exe

– IAR debuggers

https://www.iar.com/iar-embedded-workbench/add-ons-and-integrations/in-circuitdebugging-probes/

– Licensing

https://www.iar.com/iar-embedded-workbench/#!?architecture=Arm¤tTab=editionsand-licensing

2020-08-19, restricted

36

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 37

Technical Support

› If you have any questions, our technical support team is happy to assist you

– Create a support request on the Infineon Technical Support page

› You can also use the following support resources if you need quick assistance

– Local Sales Office Locations

2020-08-19, restricted

37

Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 38

38

002-31149 **

Page 39

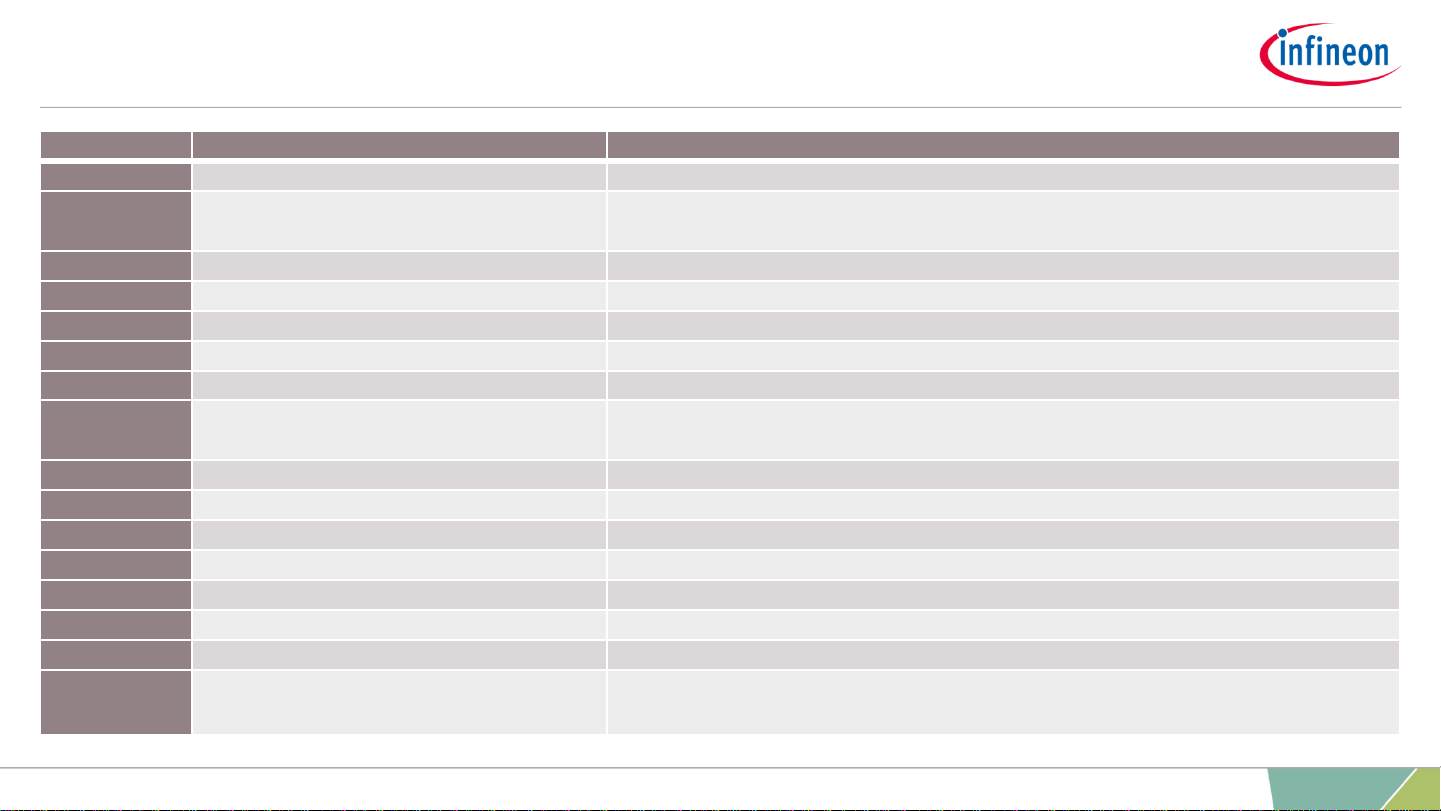

Revision History

Revision

ECN

Submission Date

Description

of Change

**

6971522

09/25/2020

Initial release

39

2020-08-19, restricted Copyright © Infineon Technologies AG 2020. All rights reserved.

Loading...

Loading...