Page 1

Data Sheet Please read the Important Notice and Warnings at the end of this document Revision 1.2

www.infineon.com 2020-05-14

SP400-11-01

SP40PLUS

Tire Pressure Monitoring Sensor

Quality Requirement Category: Automotive

Features

• Patented Glass-Silicon-Glass MEMS pressure sensor with best-in-class media compatibility

• Calibrated pressure sensor for absolute air pressure measurement

• Z-axis accelerometer for motion detection and angular measurement

• Temperature and supply voltage sensors

• Industry-standard 8051 microcontroller with 12K of Flash memory

• System Controller with flexible wake-up and power management features

• RF Transmitter with fractional-N sigma-delta PLL

• Unique firmware functions for determination of angular wheel position, supporting tire localization (APS)

• LF Receiver allows carrier detection and modulated telegram reception

Applications

• Valve based TPMS-Modules

•OEM

•Aftermarket

•Retrofit

• In Tire TPMS Modules

Description

The SP40PLUS provides a very high level of integration, and is optimized to perform all of the functions necessary

to implement a state-of-the-art Tire Pressure Monitoring System (TPMS) sensor module. With its integrated micro

controller, sensors, and convenient peripherals, the SP40PLUS needs the addition of only a few passive

components and a battery to form a complete TPMS sensor assembly.

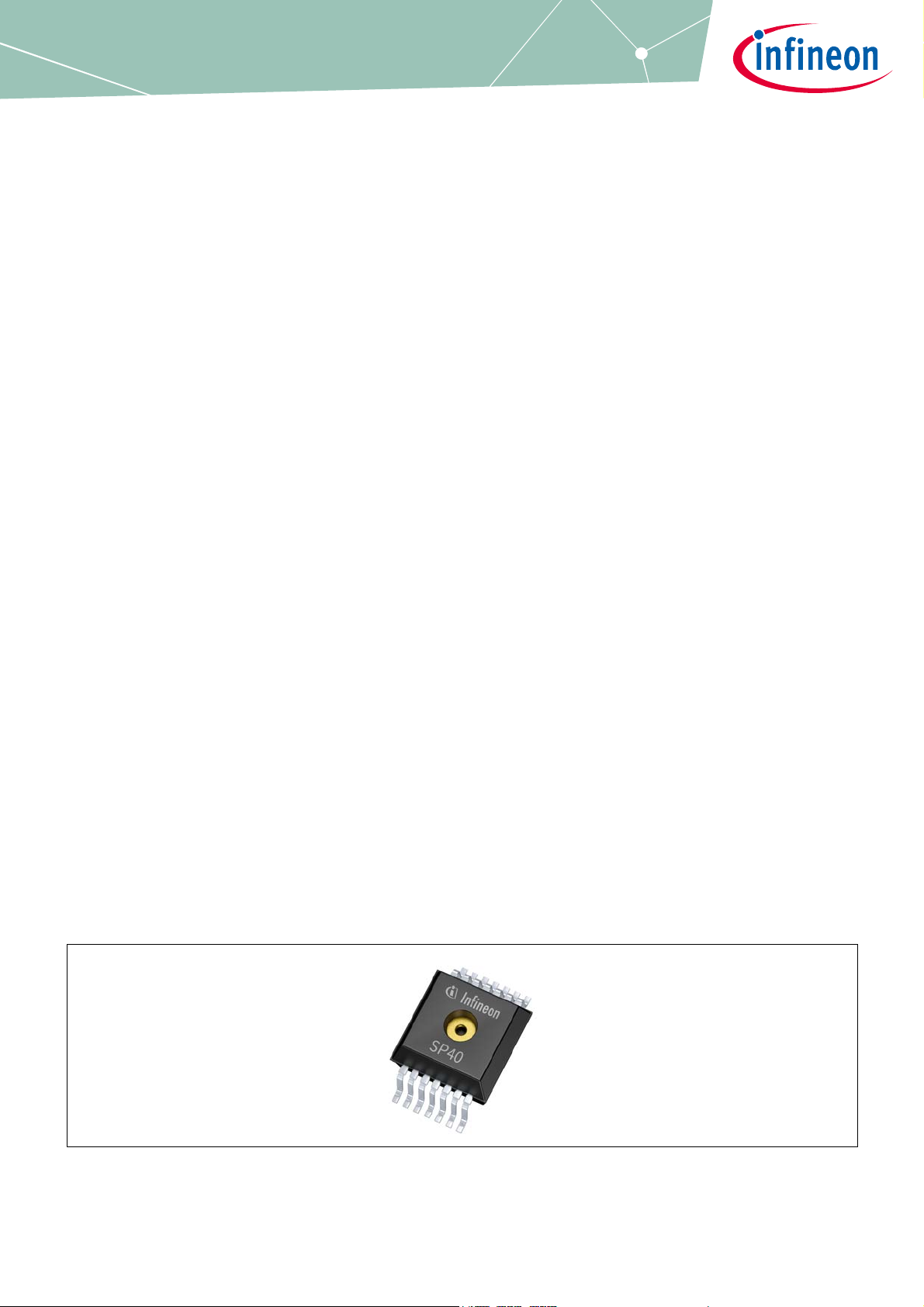

Figure 1

PG-DSOSP-14-82

Page 2

SP40PLUS

Tire Pressure Monitoring Sensor

Table of Contents

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

2 Specification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

2.2 Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

2.3 Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.3.1 Pressure Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.3.2 z-axis Acceleration Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.3.3 Temperature Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3.4 Battery Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3.5 Thermal Shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.3.6 General Purpose Digital I/O Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3.7 Voltage Monitoring and Power On . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3.8 Flash memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

2.3.9 Supply Currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

2.3.10 LF-Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.3.11 RF-Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

2.3.12 RC Oscillators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

2.3.13 Wake-up and power-on timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

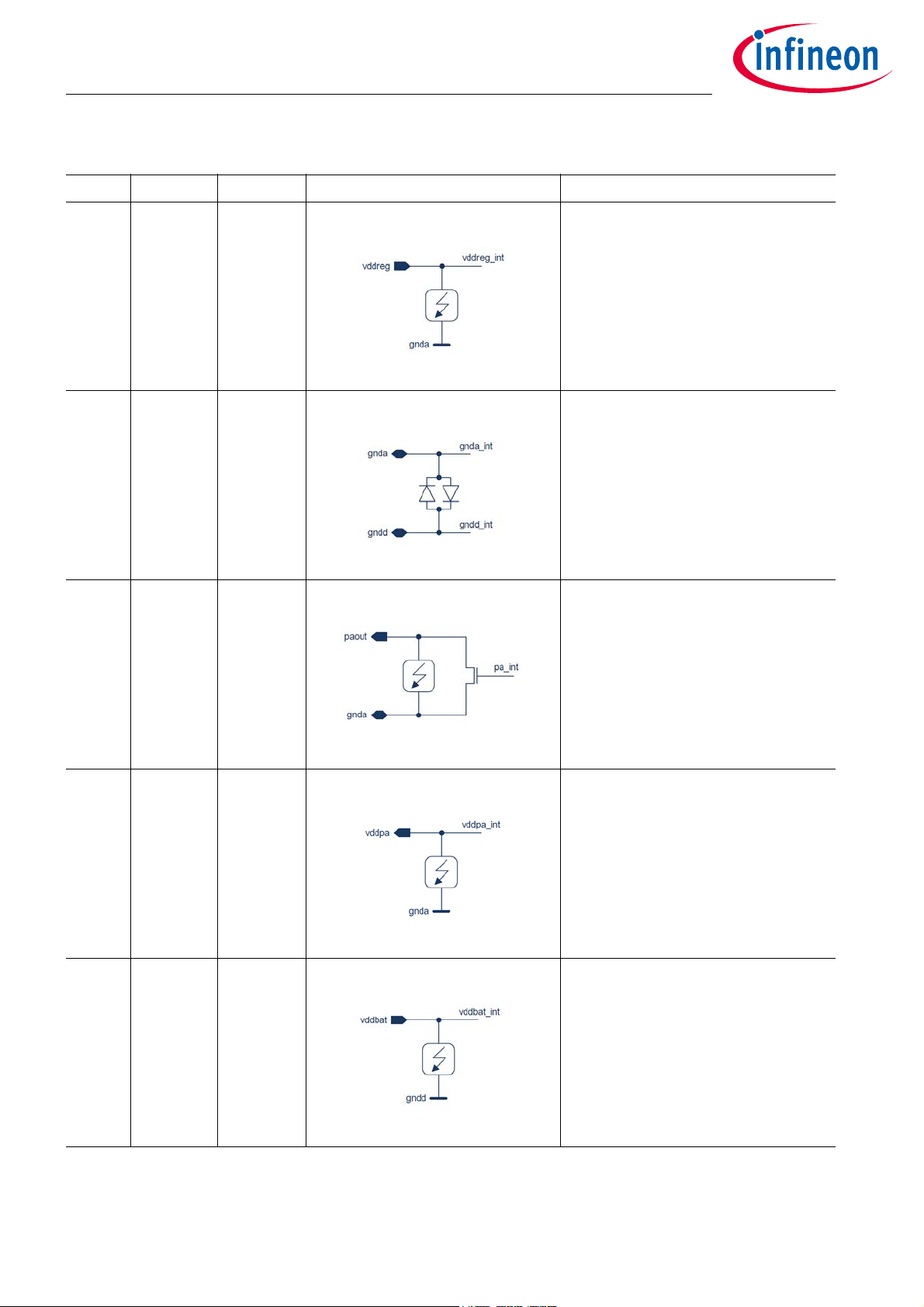

3 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.1 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.2 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

4 Special Features of the SP40PLUS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.1 Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.2 Device states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

4.3 State Transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

5 Functional Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.1 SP40PLUS Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.2 Wake-up Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

5.2.1 Interval Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

5.2.2 LF ON-OFF Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2.3 LF receiver wake-up/resume events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2.4 General purpose I/O PP2 wake-up/resume event . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

5.2.5 Power-on and under-voltage reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.2.6 Software reset, watchdog reset and flash error reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

5.2.7 Thermal Shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5.3 System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

5.3.1 Sampling Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

5.4 Clock Generators . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

5.5 Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

5.5.1 Timer Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

5.5.2 Watchdog . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Data Sheet 2 Revision 1.2

2020-05-14

Page 3

SP40PLUS

Tire Pressure Monitoring Sensor

5.5.3 Hardware CRC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

5.5.4 I2C Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

5.5.5 UART Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

5.6 Memories . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.6.1 Lock-byte concept overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

5.6.2 Flash programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.6.3 Retention RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.6.4 Data RAM and SFRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

5.6.5 Retention SFRs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.7 Power Supply and Reset Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.7.1 TX battery voltage detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

5.8 Measurement Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.9 RF transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

5.9.1 Manchester/Biphase Encoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

5.9.2 SD-PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

5.9.3 FSK Modulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.9.4 Gaussian filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

5.9.5 RF Power Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.9.6 ASK modulator and ASK ramping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

5.9.7 Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

5.9.8 RF Baud-Rate Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.10 RF Transmission Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

5.10.1 SOM and EOM Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

5.10.2 Voltage measurement at end of transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

5.11 LF Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

5.11.1 LF Analog Front End (AFE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.11.2 LF Digital baseband (DBB) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

5.11.3 LF Telegram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

5.11.4 LF state machine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

5.12 I/O-Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

6 Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

7 Data Sheet Reference Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

8 Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

8.1 Package Outline . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

8.2 Marking . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

8.3 Package axis definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 67

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

Terminology . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

Data Sheet 3 Revision 1.2

2020-05-14

Page 4

SP40PLUS

Tire Pressure Monitoring Sensor

Introduction

1 Introduction

Measurements of pressure, acceleration, temperature, and battery voltage are performed under software

control, allowing the application software to format and prepare the data for RF transmission. An intelligent

system controller provides flexible wake-up capability in order to reduce energy usage. A calibrated Interval

Timer is included to permit periodic wake-up of the CPU, which in turn can then perform measurements and

transmit data to a receiver. The integrated Z-axis accelerometer may be used by the application software to

detect motion and distinguish between parking and driving situation.

The integrated microcontroller is instruction set compatible to the standard 8051 processor and is supported by

commercially available C compilers and IDE tool chains. The microcontroller core is supplemented with various

peripherals (e.g. hardware Manchester/BiPhase Encoder/Decoder, CRC Generator/Checker, I2C- and UARTinterface) that enable an easy implementation of TPMS application software.

For user specific application code the SP40PLUS includes 12k of on-chip flash memory.

The RF Transmitter block covers both 315 and 434 MHz UHF bands and supports FSK and ASK modulation. The

transmitter contains a fractional-N sigma-delta PLL synthesizer which allows for precise control of carrier

frequency and accurate FSK frequency modulation. A flexible baseband encoder and advanced power

management techniques are used to hold the peak current consumption during RF transmission to a minimum.

An integrated autonomous LF Receiver allows the SP40PLUS to receive diagnostic or operating state commands,

supporting application features such as pressure-on-demand or tire position localization.

Finally, a comprehensive firmware library supports using all above mentioned hardware blocks effectively.

Especially a unique set of Angular Position Sensing (APS) functions allows calculating the instantaneous angular

position of the TPMS module relative to the car chassis which may be used for wheel localization on system level.

Data Sheet 4 Revision 1.2

2020-05-14

Page 5

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

2 Specification

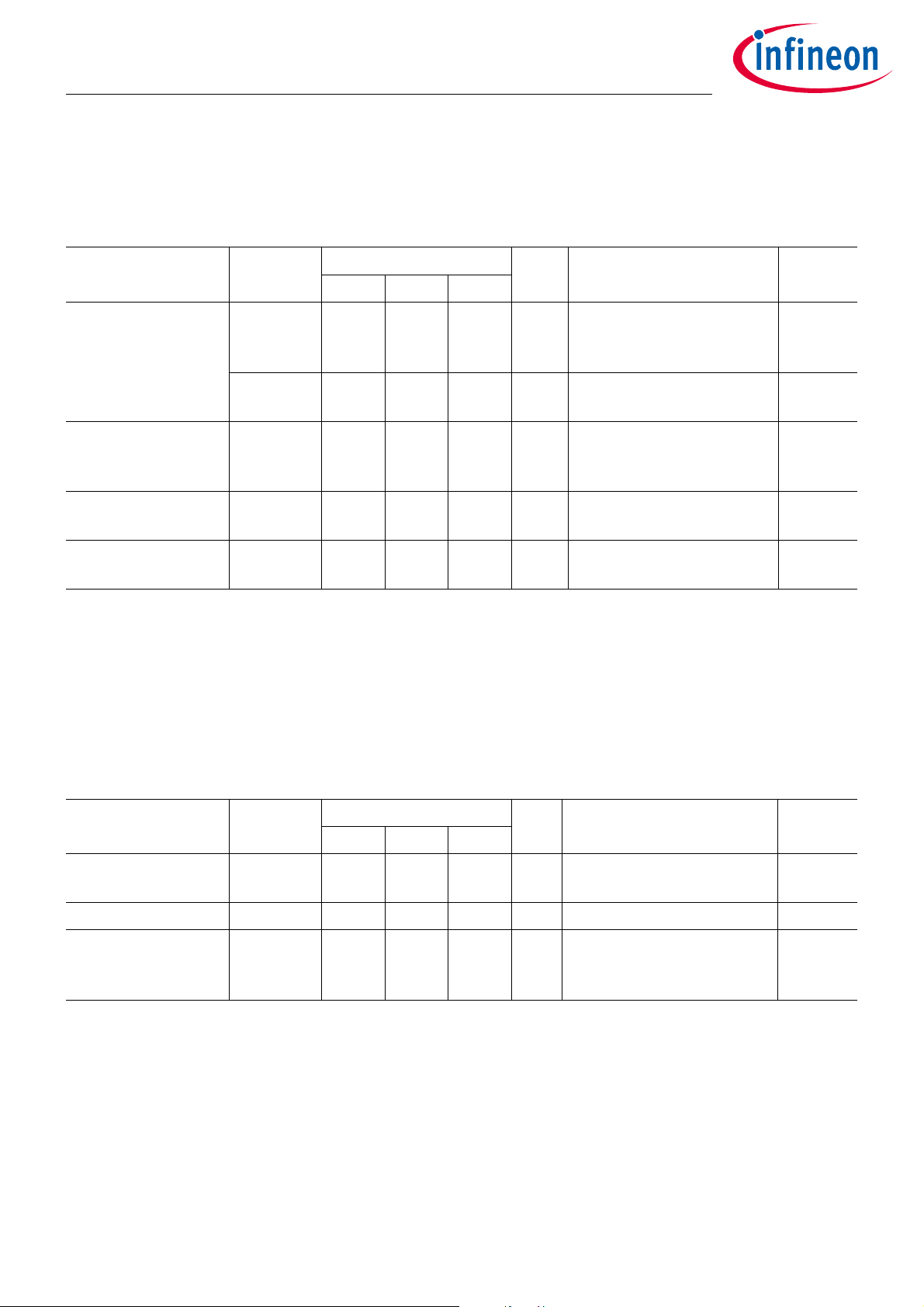

2.1 Absolute Maximum Ratings

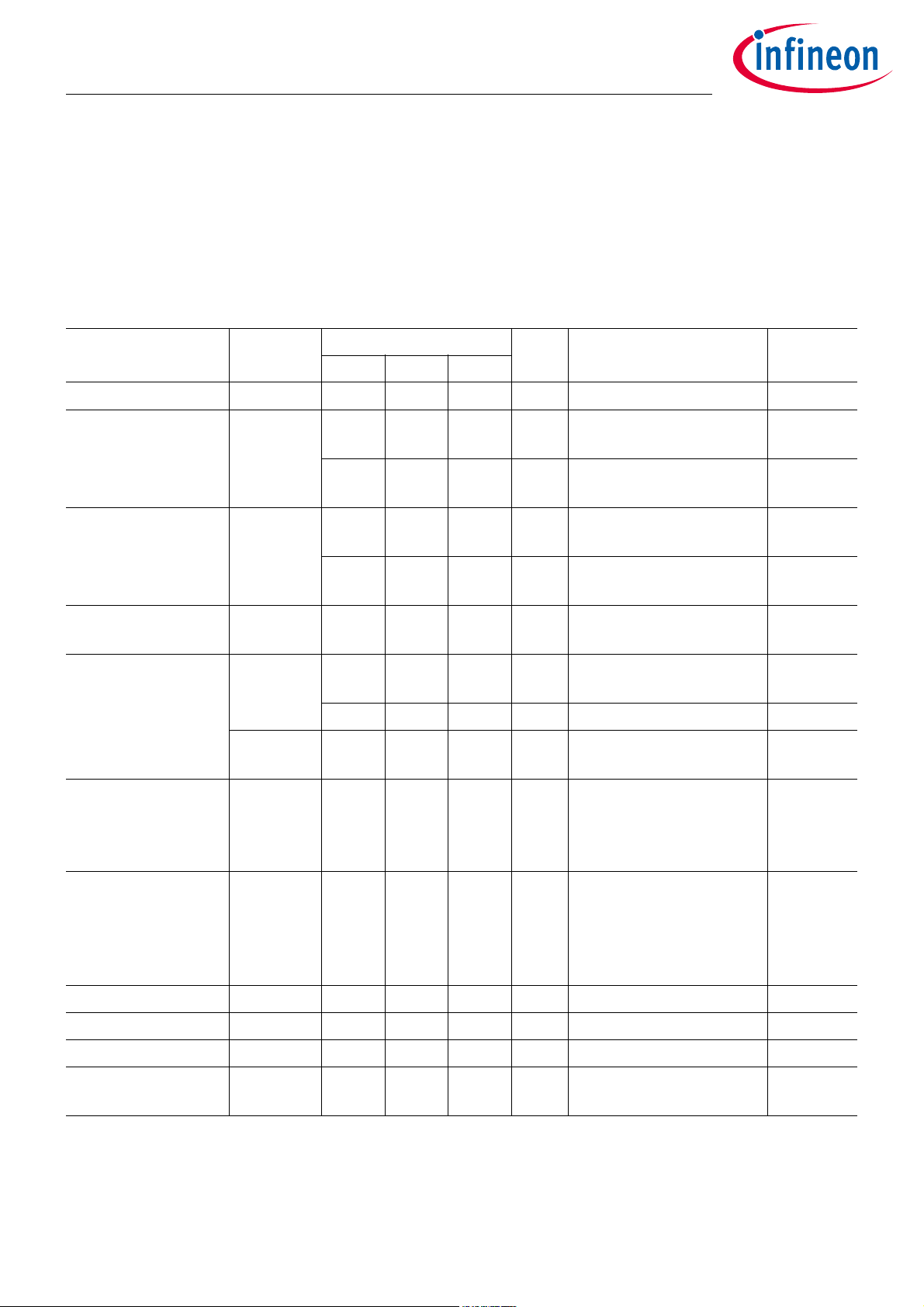

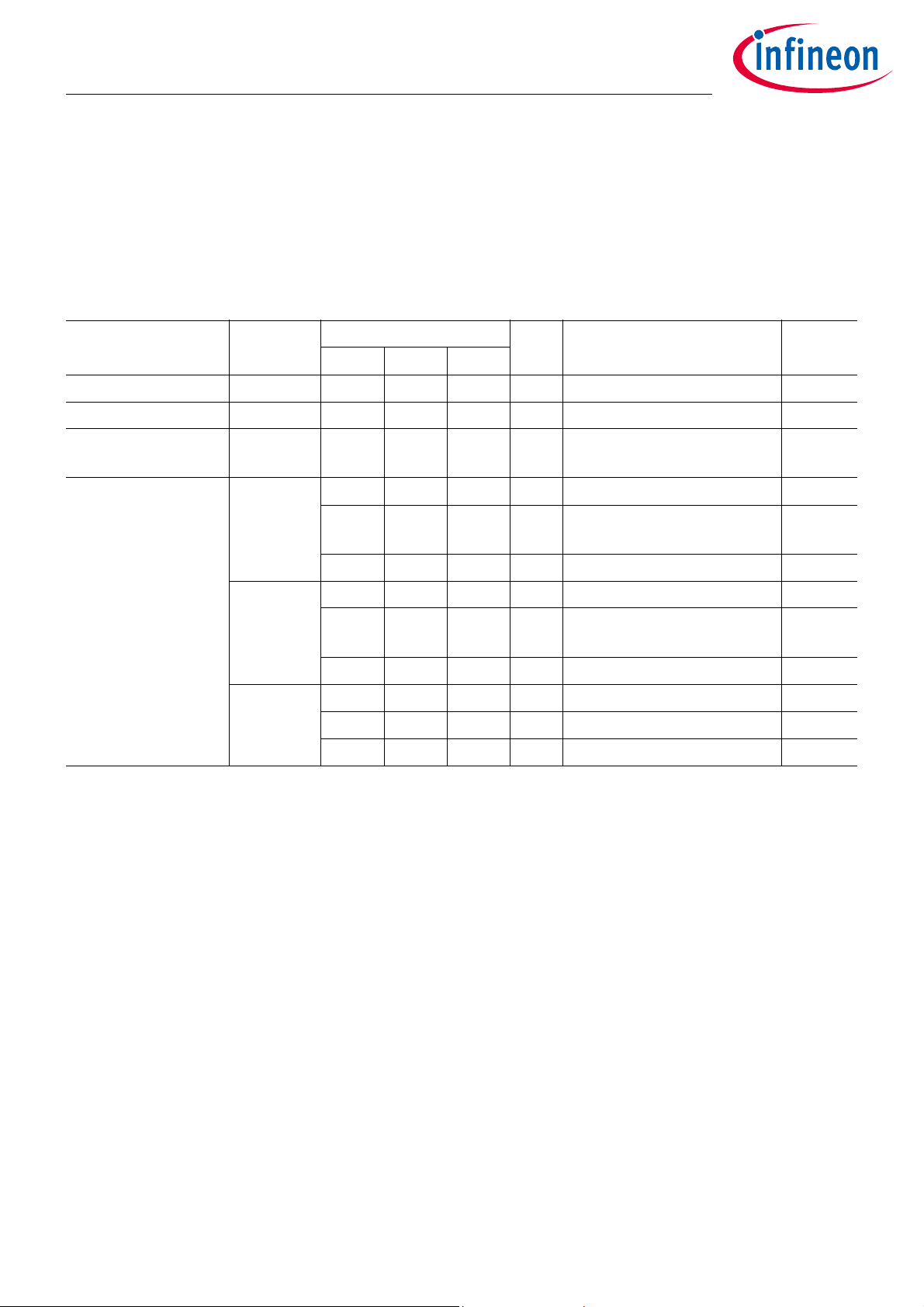

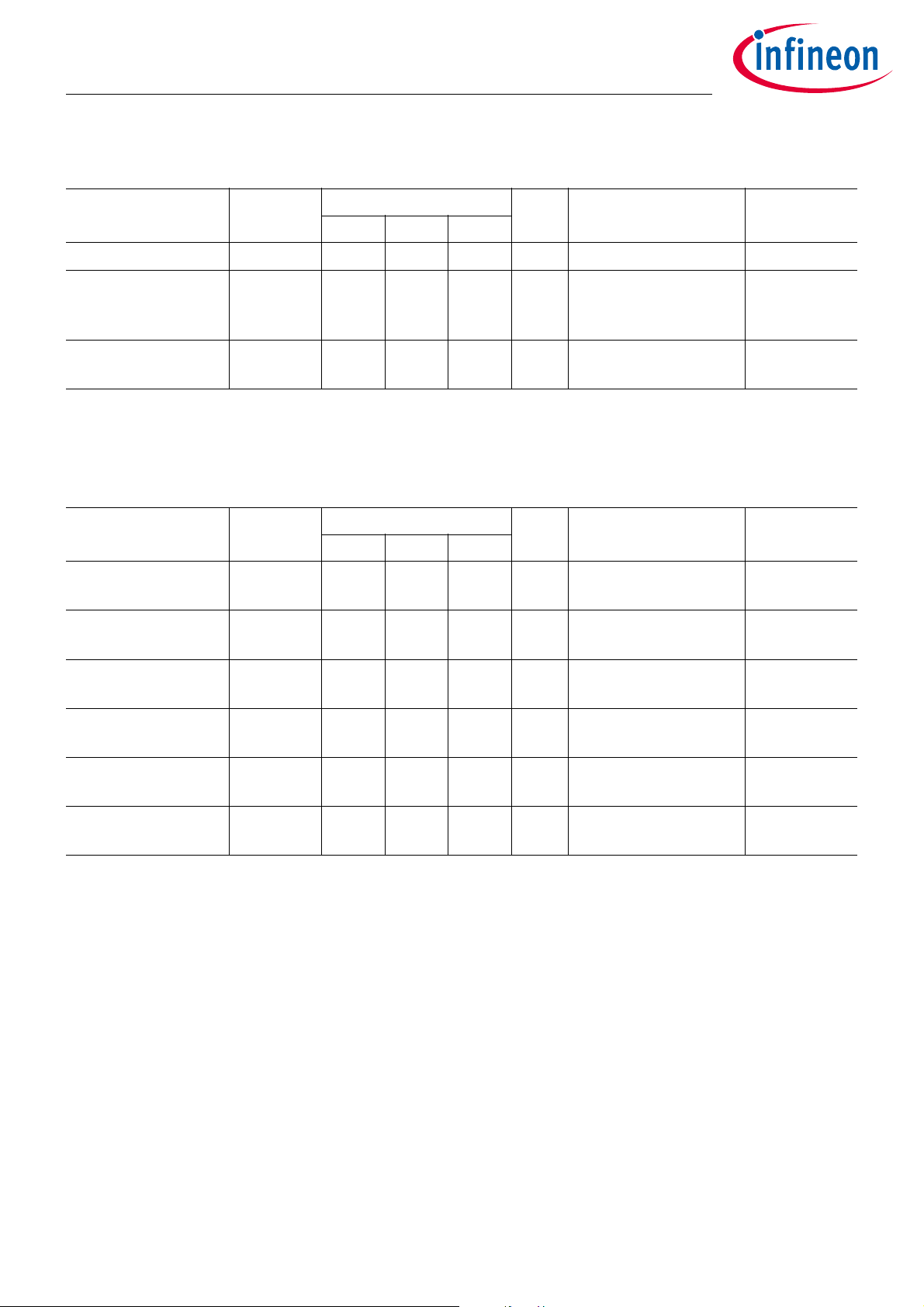

Table 1 Absolute Maximum Ratings

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Max. Supply Voltage V

ESD robustness HBM V

ESD robustness CDM V

Latch up I

Input voltage V

Peak voltage at

PAOUT pin

DDmax

ESD_HBM

ESD_CDM

LU

In

V

In_LF

V

PAOUT_peak

-0.3 +3.8 V 1.1

-2000 2000 V All pins according to

1.2

EIA/JESD22-A114-B

-4000 4000 V PAOUT pin according to

1.3

EIA/JESD22-A114-B

-500 500 V All pins (According to ESDA

1.4

STM 5.3.1)

-750 750 V Corner pins (According to

1.5

ESDA STM 5.3.1)

-100 +100 mA AEC-Q100 (transient

1.6

current)

-0.3 VDD +

V PP0, PP1, PP2, PP3 1.7

0.3

-0.3 +1.8 V LFP, LFN, XIN 1.8

-0.3 +0.3 V Differential input at LFP

1.9

and LFN

8 V The matching network

1.10

must be designed such

that the peak-voltage at PA

does not exceed this value

Output short-circuit

capability

1)

V

SC

0 3.8 V Short to VDD, GND or

neighbor pin for max.

1.11

10min at VDD=3.8V. Note:

VDDREG and XOUT must

not be shorted to VDD

DC current I

Over pressure p

Burst pressure p

Static acceleration a

DC

max

burst

static

-10 10 mA all pins 1.13

2000 kPa static load 1.14

2000 kPa 10 times 1 sec 1.15

3000 g Device unpowered. Tested

1.16

in z-direction.

Data Sheet 5 Revision 1.2

2020-05-14

Page 6

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

Table 1 Absolute Maximum Ratings

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Mechanical shock a

shock

6000 g 0.3 ms half sine pulses.

1.17

5 shocks in +/- x,y,zdirection, respectively.

Device unpowered.

Storage temperature T

storage

-50 +150 °C Maximal 1000 hours

1.18

accumulated over

lifetime between 125°C

and 150°C. Device not

powered. Temperature

cycling only allowed

between -40°C and 125°C.

1) Refers to following pins: PP0 to PP3 if configured as output, XOUT, VDDREG, PAOUT and VDDPA. For input pins see

parameter input voltage.

Note: Absolute maximum ratings are values beyond recommended operating conditions. They describe

those conditions which the device can withstand for some limited time. After exposure to

maximum ratings the device will remain functional, but the reliability is no longer guaranteed.

Data Sheet 6 Revision 1.2

2020-05-14

Page 7

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

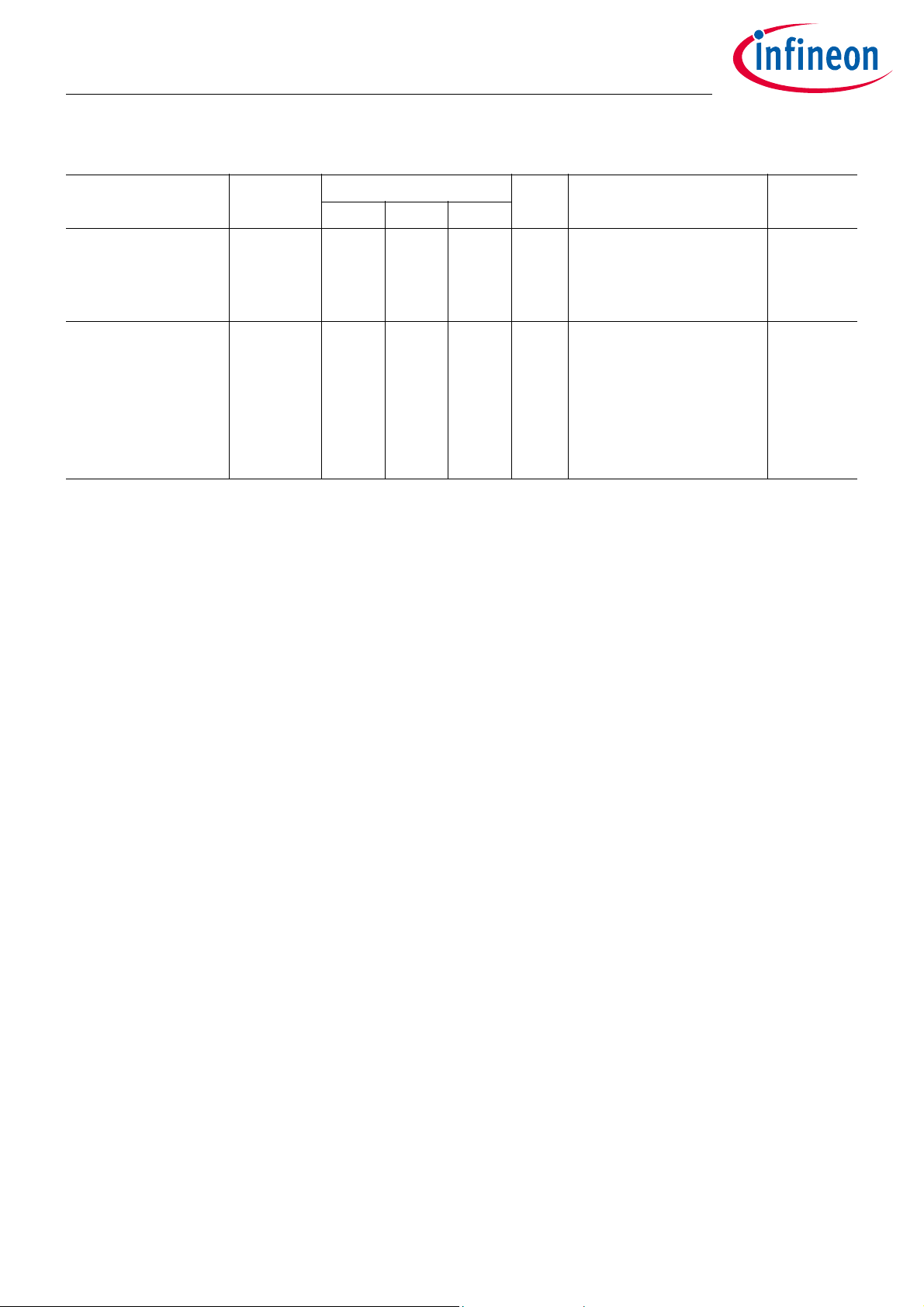

2.2 Operating Range

The operating range defines the ambient conditions where the device operates as specified. Certain specified

parameters in this data sheet may depend on additional operating conditions. These additional conditions are

indicated in the corresponding sections.

Table 2 Operating Range

Parameter Symbol Values Unit Note or

Test Condition

Supply Voltage

Min. Typ. Max.

1)

V

DD

VUVRA – 3.6 V Device not in power

down state

VUVRPD – 3.6 V Device in power down

state

Ambient Temperature T

Operating

T

Flash

-40 – 125 °C Normal Operation 3.3

-20 – 90 °C FLASH

programming/erasing

Extended

Temperature Range

T

EXT

-50 150 °C Thermal shutdown

functional. V

to 3.6 V. Exposure to

125°C...150°C maximal

24h over lifetime

z-axis Acceleration a

Operating

-1600 – 1600 g Exceeding this

acceleration will result

in a higher pressure

error as specified.

1) Supply voltage must be connected to VDDBAT pin.

DD

= V

UVRA

Number

3.1

3.2

3.4

3.5

3.6

Data Sheet 7 Revision 1.2

2020-05-14

Page 8

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

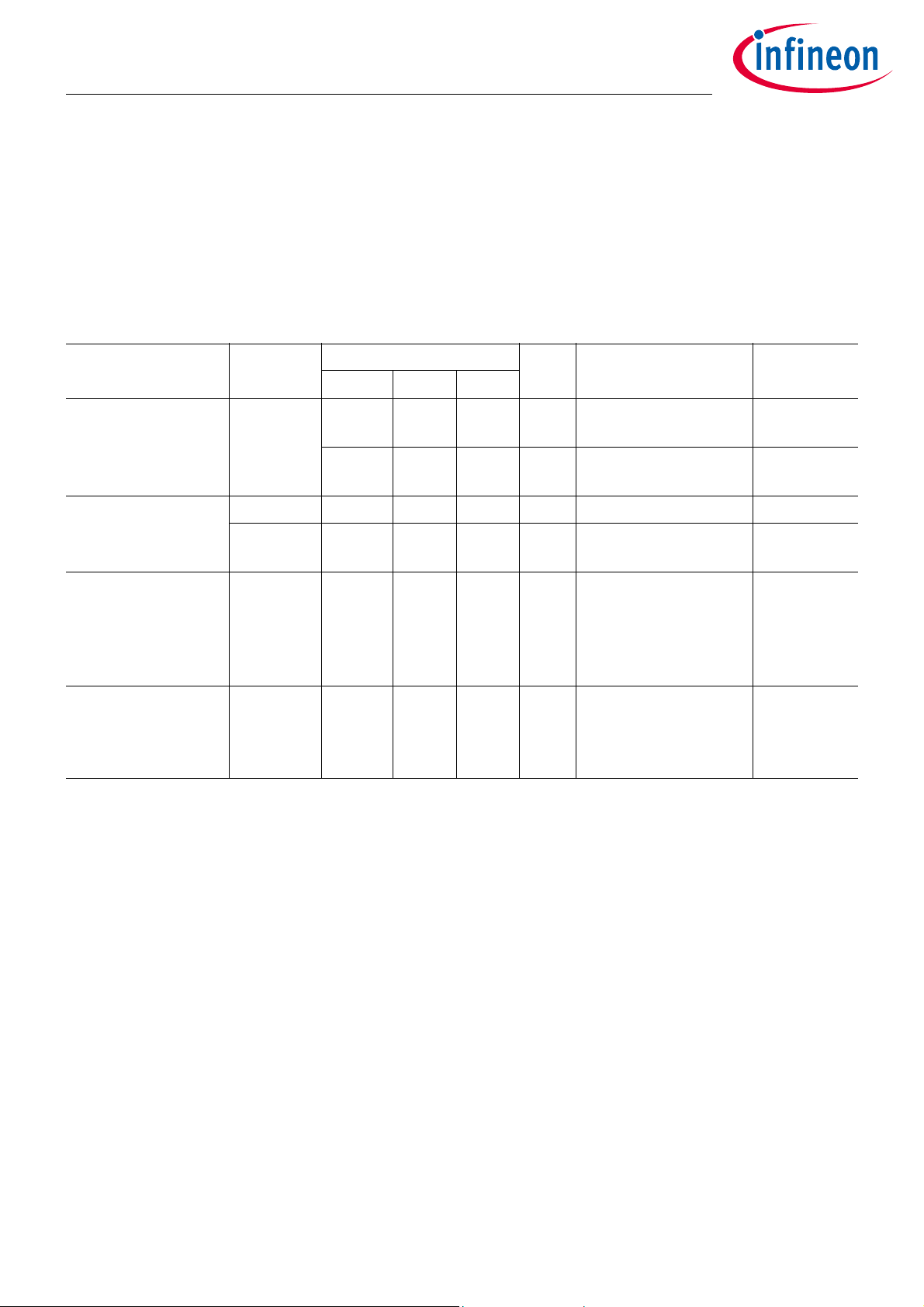

2.3 Characteristics

2.3.1 Pressure Sensor

Table 3 Pressure Sensor 500/750/900kPa Variant

1)2)

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Input Pressure Range p

Random Error p

ADC resolution p

Measurement Error

3)

in

random

ADC_res

p

Error 100-500

100 900 kPa 7.1

-1.37 1.37 kPa 95% of all measurements 7.2

0.5 kPa/

LSB

1 LSB of a raw measurement

corresponds to 0.5 kPa or less

7.3

-5 5 kPa 0°C to +90°C 7.4

-7 7 kPa -20°C to 0°C

7.5

+90°C to +125°C

-9 9 kPa -40°C to -20°C 7.6

p

Error 500-750

-1.2 1.2 %

-1.6 1.6 %

4)

0°C to +90°C 7.7

4)

-20°C to 0°C

7.8

+90°C to +125°C

4)

-40°C to -20°C 7.9

p

Error 750-900

-2.0 2.0 %

-12 12 kPa 0°C to +125°C 7.10

-14 14 kPa -20°C to 0°C 7.11

-15 15 kPa -40°C to -20°C 7.12

1) Based on averaging two raw values for each measurement

2) Exceeding the maximum z-axis acceleration (parameter 3.6) as defined in the operating range will result in a higher

pressure measurement error than specified

3) The measurement error is understood as total error, including random error (noise)

4) Percentage of actual pressure value

Data Sheet 8 Revision 1.2

2020-05-14

Page 9

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

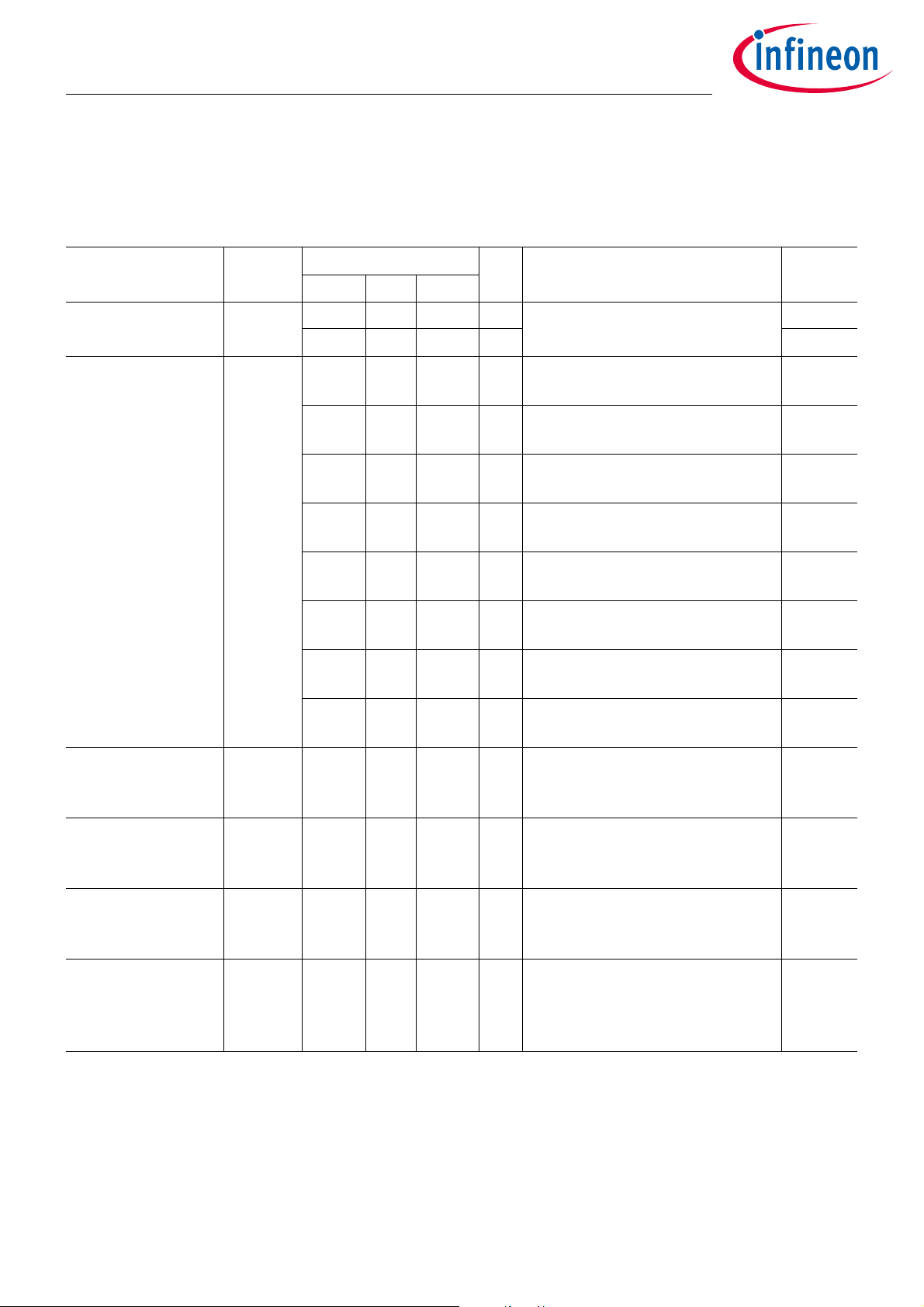

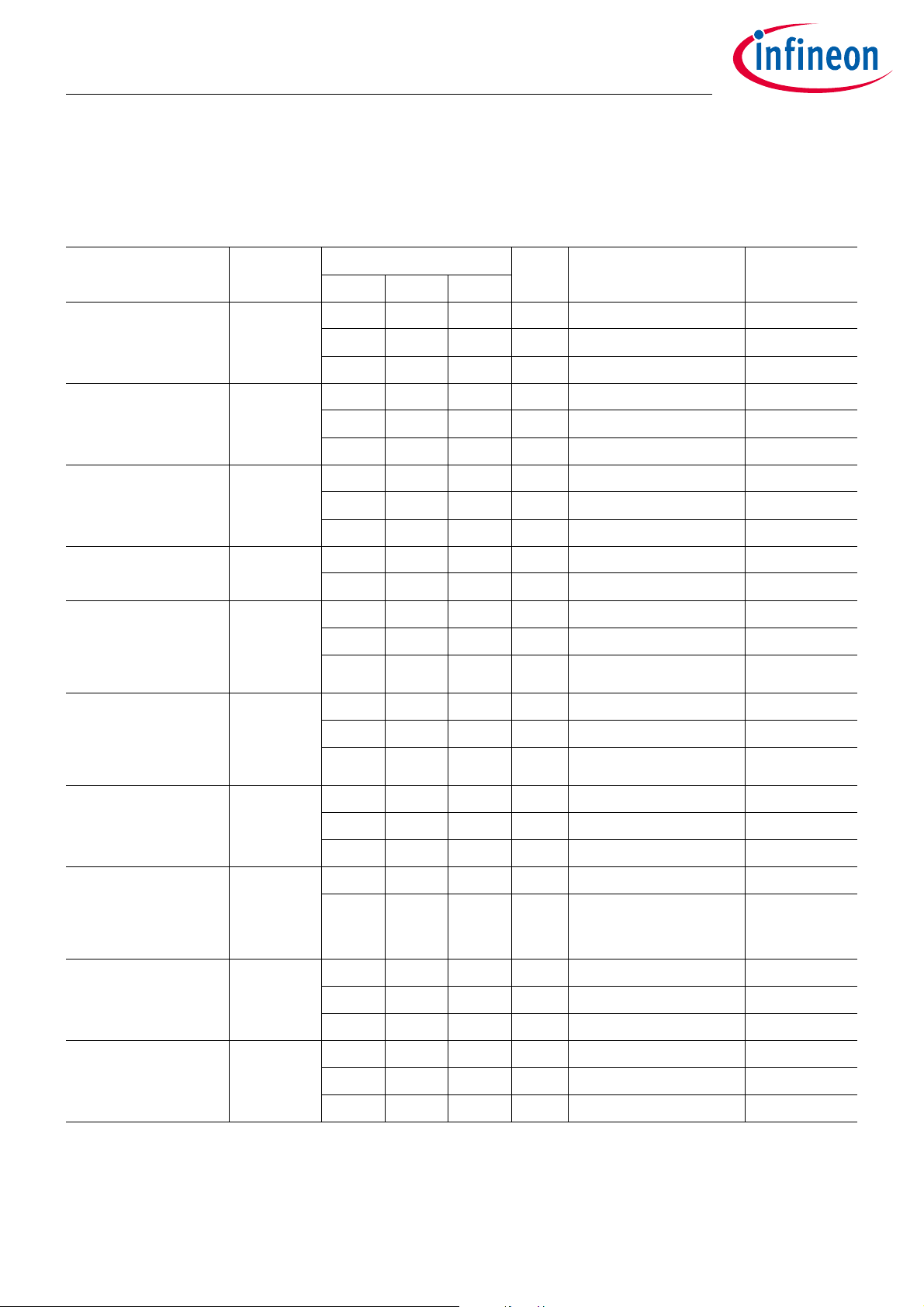

2.3.2 z-axis Acceleration Sensor

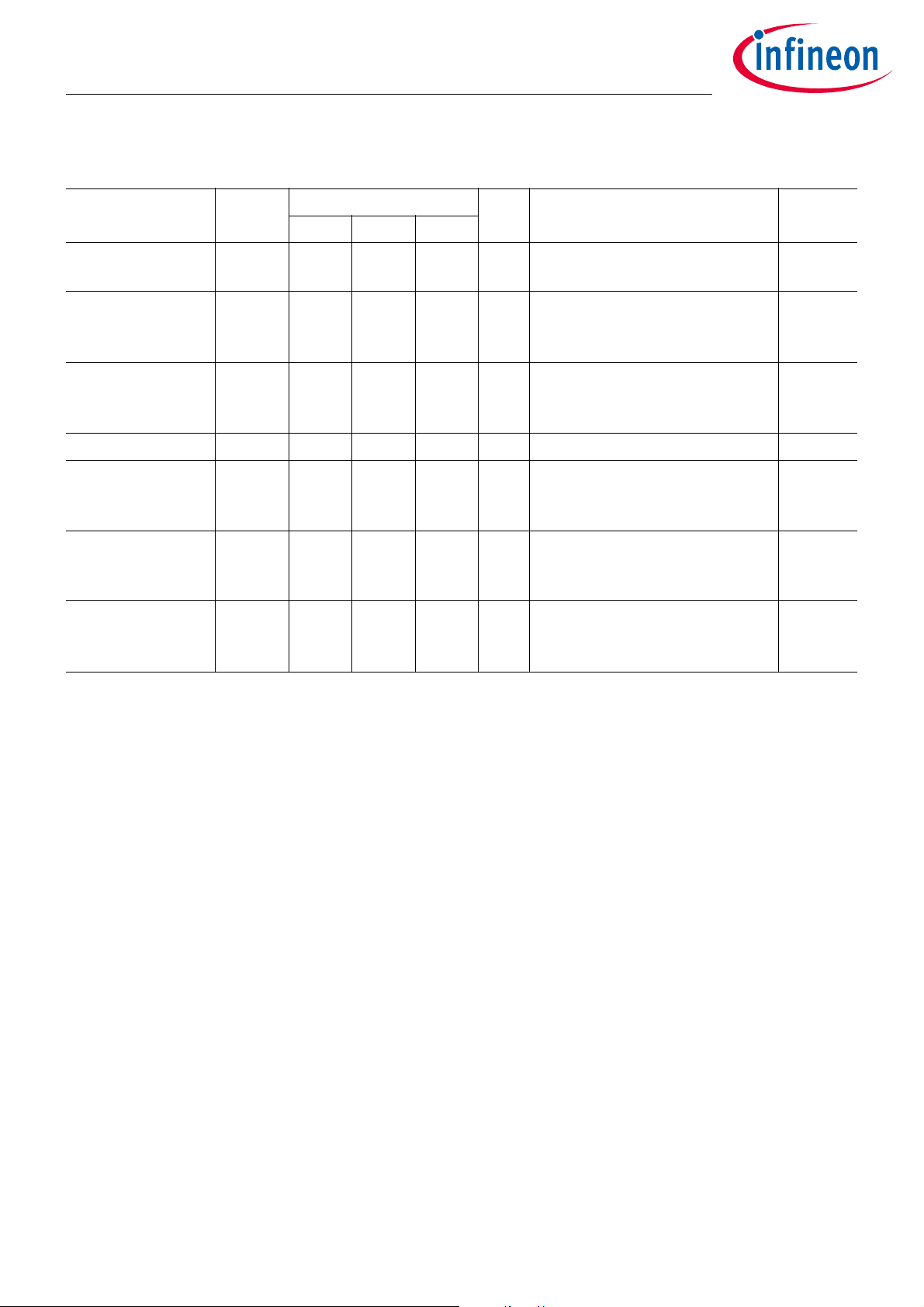

Table 4 z-axis Acceleration Sensor

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Input acceleration

Range

Total Acceleration

1)

Error

Random error of

acceleration

compensated values

a

in

a

err_tot

a

rnd_comp_

16

-20 355 g Selectable by firmware function 12.1

-355 20 g 12.2

-6.5

(-3.0)

-8.5

(-5.0)

-8.5

(-5.0)

-10.5

(-7.0)

-12.5

(-9.0)

-14.5

(-11.0)

-22.5

(-19.0)

-24

(-20.5)

-0.35 +0.35 g 99.7% of all measurements.

+6.5

(+3.0)

+8.5

(+5.0)

+8.5

(+5.0)

+10.5

(+7.0)

+12.5

(+9.0)

+14.5

(+11.0)

+22.5

(+19.0)

+24

(+20.5)

g|a

T = -40°C...90°C

g|a

T = 90°C...125°C

g|a

T = -40°C...90°C

g|a

T = 90°C...125°C

g|a

T = -40°C...90°C

g|a

T = 90°C...125°C

g|a

T = -40°C...90°C

g|a

T = 90°C...125°C

|=0g ... 20g

in

|=0g ... 20g

in

|>20g ... 100g

in

|>20g ... 100g

in

|>100g ... 200g

in

|>100g ... 200g

in

|>200g ... 355g

in

|>200g ... 355g

in

12.3

12.4

12.5

12.6

12.7

12.8

12.9

12.10

12.11

Averaging of 16 ADC-samples.

No external noise sources present.

ADC resolution a

ADC_res

0.057 0.175 g/

1 LSB of a raw measurement

LSB

corresponds to minimal 0.057g and

12.14

maximal 0.175g

Random error of

acceleration raw

values

Accelerometer

resonance frequency

a

rnd_raw_16

f

res_acc

-4 +4 LSB 99.7% of all measurements.

Averaging of 16 ADC-samples.

No external noise sources present.

5.1 6 6.9 kHz Mechanical excitation of the

SP40PLUS in this frequency range

12.16

12.17

must be avoided (e.g. PCB sawing

process)

1) Total error specifications are based on averaging 16 raw values for each measurement and they include random error

(noise). The total error may be reduced by 3.5g by periodically (e.g. every 3 months) using the automatic acceleration

offset compensation function Lib_Comp_Auto_Acc_Offset(). The reduced errors are put into brackets.

Data Sheet 9 Revision 1.2

2020-05-14

Page 10

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

2.3.3 Temperature Sensor

Table 5 Temperature Sensor

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Measurement range T

Measurement error

1)

Random error T

range

T

Error

random

-40 +125 °C 14.1

-3 +3 °C 14.2

-1 +1 °C 95% of all

14.4

measurements

1) The measurement error is understood as total error, including random error (noise)

2.3.4 Battery Sensor

Table 6 Battery Sensor

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Measurement range V

Measurement error

1)

V

range

Error

VUVRA 3.6 V see Table 10 for V

-3 – +3 % percentage of

UVRA

15.1

15.2

measurement value

1) The measurement error is understood as total error, including random error (noise)

2.3.5 Thermal Shutdown

Table 7 Thermal Shutdown

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Thermal Shutdown

T

HOT TH

119 122 125 °C 16.1

HOT threshold

Thermal Shutdown

T

HOT RE

115 120 123.5 °C 16.2

HOT release

Hysteresis T

Thermal Shutdown

HYST

T

COLD TH

1.5 4 °C 16.3

-40 -37 -34 °C 16.4

COLD threshold

Thermal Shutdown

T

COLD RE

-38.5 -35 -30 °C 16.5

COLD release

Data Sheet 10 Revision 1.2

2020-05-14

Page 11

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

2.3.6 General Purpose Digital I/O Pins

Table 8 Digital I/O Pins - Operating Range

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Digital Pin Output

I

out DIG

-4 4 mA Pins PP0 to PP3 17.1

Current

Digital Pin Input High

Voltage

Digital Pin Input Low

Voltage

V

IH

V

IL

0.8V

DD

V

- 0.05 V for lowest current

DD

0.2V

50 mV for lowest current

V functional 17.2

consumption

V functional 17.4

DD

1)

17.3

17.5

consumption

1) If the digital I/O pins are left open and the internal pull resistors are activated the +/-50mV criterion is fulfilled

Table 9 Digital I/O Pins - Electrical Characteristics

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Digital Pin-Output High

V

OH

V

-0.3 V at 1 mA load current 18.1

DD

Voltage

Digital Pin-Output Low

V

OL

0.3 V 18.2

Voltage

Digital Pin Input

Capacitance

C

in

10 pF PP0, PP1 and PP3 18.3

20 pF PP2 18.4

Digital Pin Input current

(PP0, PP1, PP3)

Digital Pin Input current

(PP2)

I

in_PP0_1_3

I

in_PP2

-1 1 µA PP0, PP1, PP3 configured

as input

-1 1 µA PP2 configured as input

T = -40°C...+90°C

-1.5 1.5 µA PP2 configured as input

T = +90°C...+125°C

18.5

18.6

18.7

Data Sheet 11 Revision 1.2

2020-05-14

Page 12

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

2.3.7 Voltage Monitoring and Power On

Table 10 Voltage Monitoring and Power On

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Under Voltage Reset

(measured at VDDBAT

pin)

V

UVRA

V

UVRPD

1.6 1.7 V applies in run- and idle-state

and if RF transmission is

ongoing

1)

1.2 1.6 V applies in all other device

19.1

19.2

states

Reset Release

Threshold

2)

V

THR

1.8 1.9 V applies for a reset triggered

by under voltage and power-

19.3

on reset

RF Undervoltage

V

MIN

1.8 1.9 V 19.4

3)

Warning Level

Brown-out Detection

Threshold

1) During TX-interframe in TX-low-power, when the analog circuits are switched off, 19.1 does not apply

2) The device will be released from undervoltage reset or power-on reset only if voltage at VDDBAT pin exceeds V

3) A flag is set if voltage at VDDBAT pin falls below V

4) The brown-out detector monitors the internal 1.5V domain

4)

V

THR_BOD

1.15 1.25 V 19.5

during RF transmission

MIN

2.3.8 Flash memory

THR

Table 11 Flash Memory

1)

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Flash memory data

retention time

Flash write cycles N

Flash line write time t

t

Ret Flash

write

write_line

10 y Defect rate < 1ppm over

lifetime.

100 20.2

6msIncluding time for

20.1

20.3

verification. I2C Baud-rate =

400 kbit/s

1) Endurance, data retention, and operational life qualified according AEC-Q100-005D1

Data Sheet 12 Revision 1.2

2020-05-14

Page 13

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

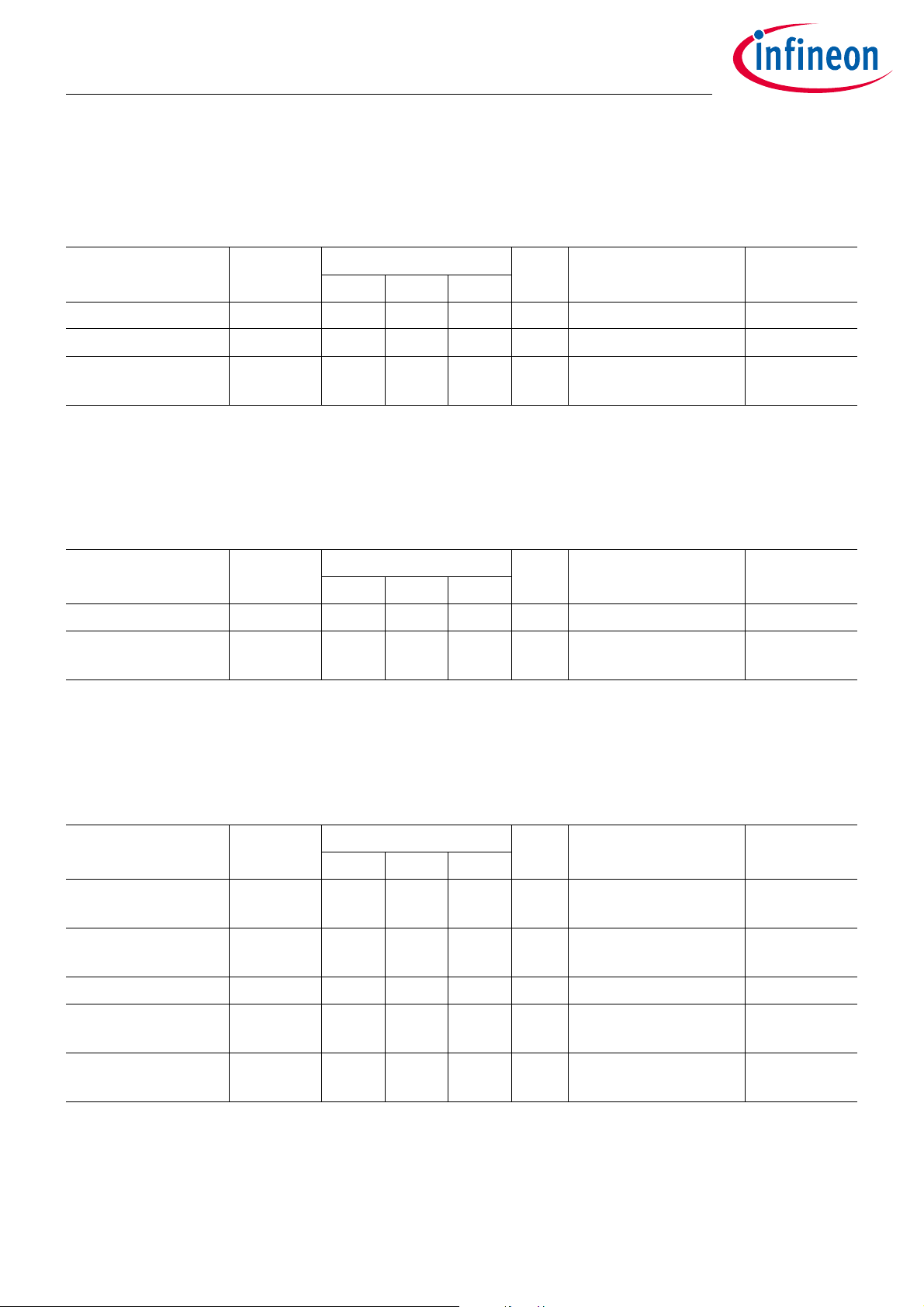

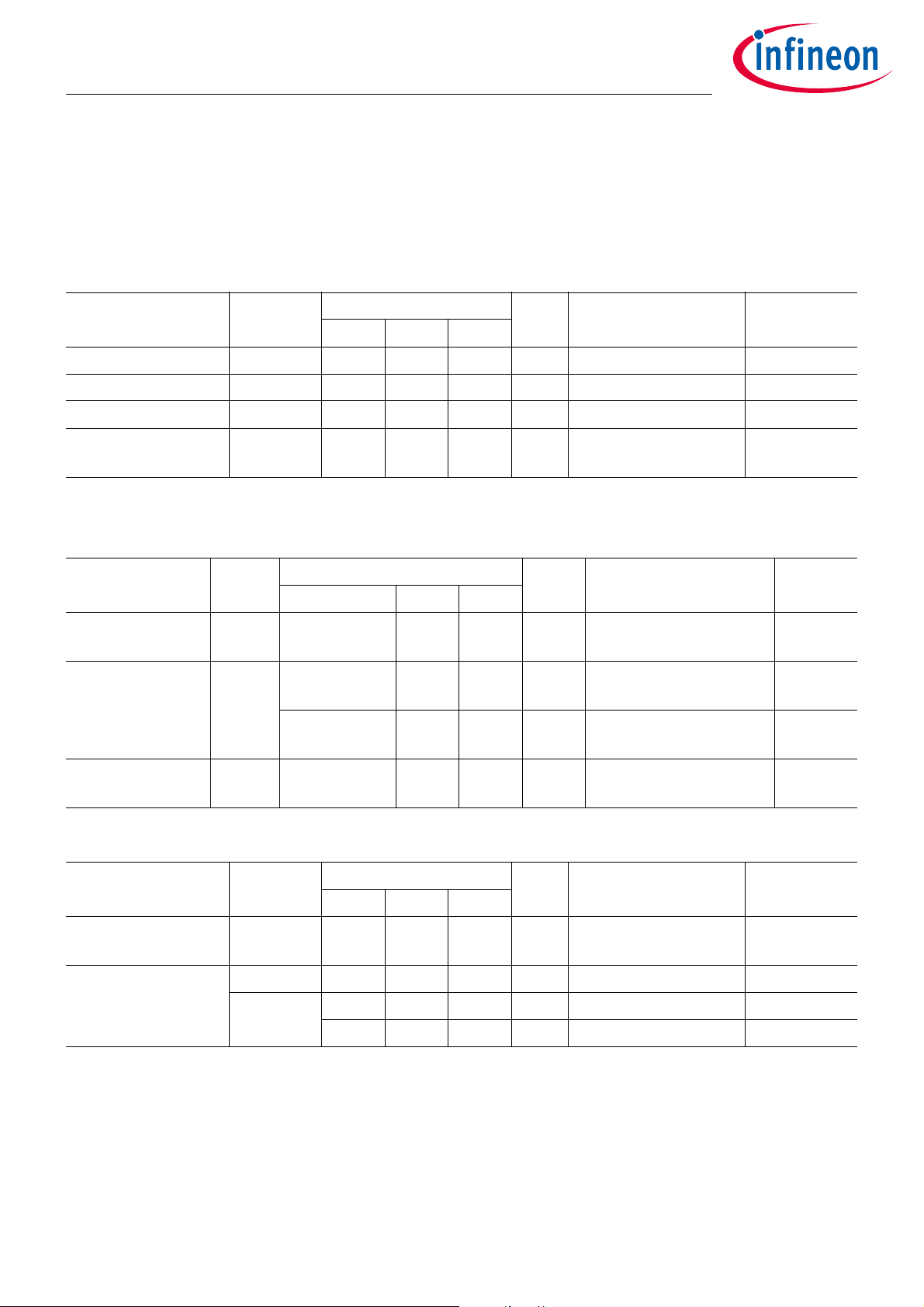

2.3.9 Supply Currents

Table 12 Supply Currents at 3.0V supply voltage

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Supply current in

power down state

1)

Supply current in idle

state (CPU gated off)

Supply current in run

2)

state

Supply current at

thermal shutdown

3)

LF-receiver supply

current in LF carrier

detection mode

(digital filter off)

4)

LF-receiver supply

current in LF carrier

detection mode

(digital filter on)

4)

I

PWD_3V

I

IDLE_3V

I

RUN_3V

I

TSD_3V

I

LFCD_3V

I

LFCDFilter_3V

245 540 nA +25°C 21.1

8.5 µA +125°C 21.2

0.15 µA -40°C 21.3

280 400 µA +25°C 21.4

400 µA +125°C 21.5

280 µA -40°C 21.6

0.85 1.05 mA +25°C 21.7

0.95 mA +125°C 21.8

0.83 mA -40°C 21.9

85 116 µA +125°C 21.10

62 110 µA -40°C 21.11

3.3 4 µA +25°C 21.12

10 µA +125°C 21.13

3.5 µA -40°C 21.14

4 6 µA +25°C 21.15

11 µA +125°C 21.16

4 µA -40°C 21.17

LF-receiver supply

current in LF data

reception mode

4)

Supply current at RFtransmission

I

LF_3V

I

RFTX_3V

3.85 6 µA +25°C 21.18

11 µA +125°C 21.19

4 µA -40°C 21.20

5.5 7 mA 315MHz, -40...+125°C 21.21

5.7 7 mA 434MHz, -40...+125°C 21.22

CW or FSK

CPU off

Supply current during

RF interframe timing

(CPU off)

Supply current in

deep idle state

5)

I

TXIF_3V

2.1 12 µA +25°C 21.24

34 µA +125°C 21.25

1.8 µA -40°C 21.26

I

DEEP_3V

2.1 12 µA +25°C 21.27

25 100 µA +125°C 21.28

1.7 µA -40°C 21.29

1) PP0, PP1, PP2, PP3 not connected

2) Measured while code is running from flash, executing a mix of read/write operations on retention RAM, SFRs and RAM

3) I

is the always ON current. Average current for clocked operation is I

TSD

4) The LF-receiver supply currents at each temperature are measured by substracting the power down current with LFReceiver being turned off from the power down current with LF-Receiver being activated in the specific mode.

TSD_avg=IPWD

+(I

TSD-IPWD

)*2.9/16/Interval_Mul_16ms

Data Sheet 13 Revision 1.2

2020-05-14

Page 14

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

5) Measured with the Data Sheet Reference Board, 50 Ohm RF output terminated with 50Ohm, VDDPA = 2.1V

2.3.10 LF-Receiver

Table 13 LF Receiver Operating Conditions

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

LF Carrier Frequency

LF Data Rate DR

LF Data Duty Cycle DC

LF Data amplitude

change speed

1) LF sensitivity levels are only valid for the specified carrier frequency range.

1)

f

LF

AC

LF

LF

SLF

115 125 135 kHz 22.1

3.8 3.9 4.2 kbit/s 22.2

45 50 55 % 22.3

1.5 Vpp/s Valid for input signals

22.4

up to 10mVpp

Table 14 LF Receiver Characteristics

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Input differential

C

LF diff

2.5 3.9 10 pF at 125kHz 23.1

capacitance

Input differential

resistance

R

LF diff

1 MOhm at 125kHz, AGC inactive, -

40°C to 90°C

1-(T/°C -90)/70 MOhm at 125kHz, AGC inactive,

23.4

23.5

90°C <=T<= 125°C

LF Receiver settling

t

ON_Set.

3.9 ms After receiver power-on 23.6

time after power on

Table 15 LF Receiver Characteristics (Data Reception Mode)

1)2)

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

LF Data Threshold

settling time

LF Telegram

Detection Sensitivity

t

Settling

S

nodet

S

det

2 ms During LF- telegram

preamble

0.1 mVpp 24.2

1.3 mVpp -20°C to 90°C 24.3

24.1

2.5 mVpp -40°C to 125°C 24.4

1) LF telegram detection sensitivity specified for 100% modulation depth.

2) Specified sensitivities require calling Lib_LF_Sensitivity() in application code, [1].

Data Sheet 14 Revision 1.2

2020-05-14

Page 15

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

Table 16 LF Receiver Characteristics (Carrier Detection Mode)

1)

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

LF Carrier Detection

Sensitivity

Carrier Detector Filter

2)

Time

1) Specified sensitivities require calling Lib_LF_Sensitivity() in application code, [1].

2) Specified carrier detector filter times require calling Lib_LF_Pulse_Width() in application code, [1].

S

S

t

t

t

CD 1

CD 2

CD 3

nodet

det

0.33 mVpp 25.1

3.35 mVpp 25.2

140 200 240 µs 25.9

350 500 650 µs 25.10

700 1000 1300 µs 25.11

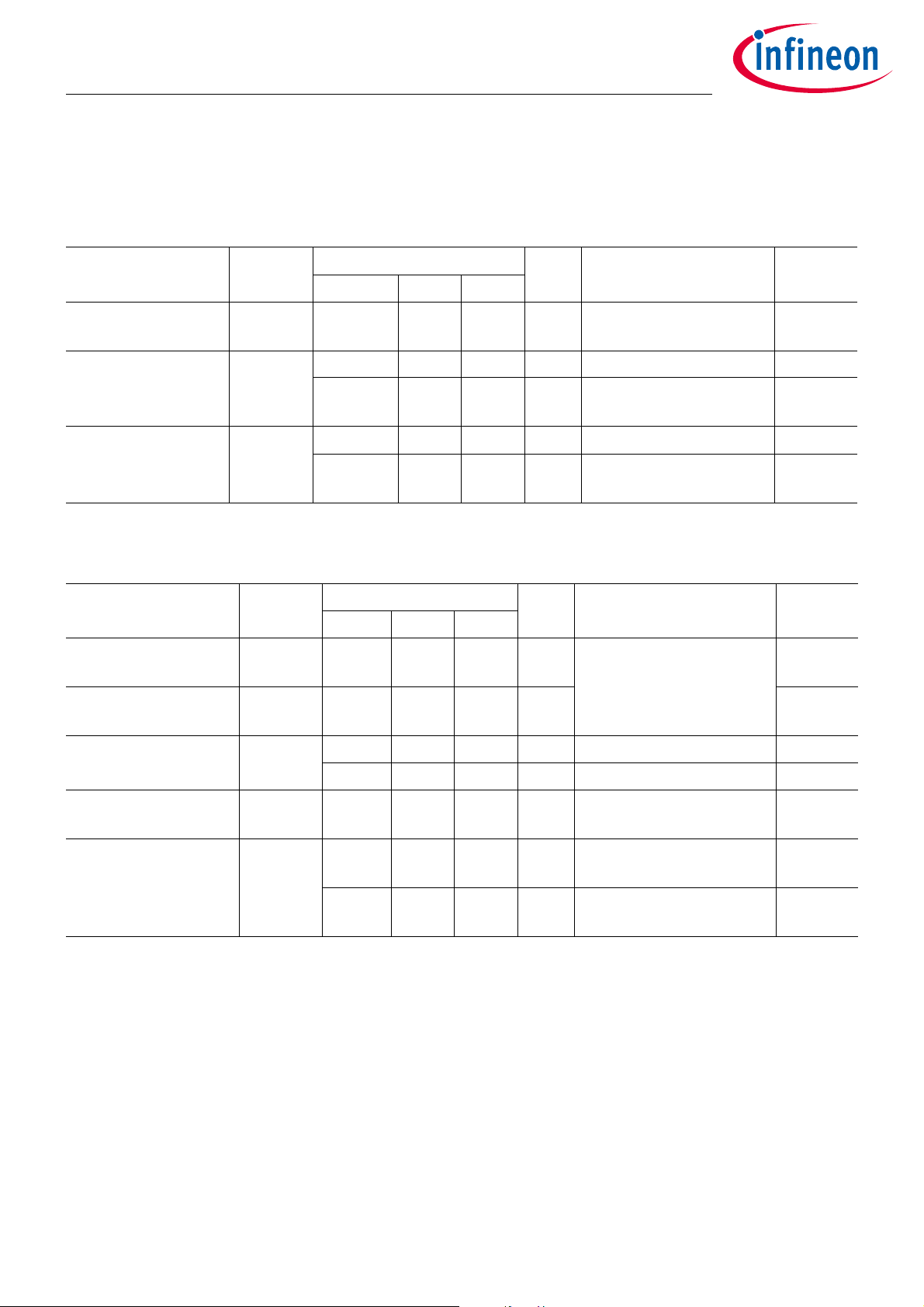

2.3.11 RF-Transmitter

Table 17 RF Transmitter Characteristics

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Transmit Frequency f

TX

314 316 MHz 28.1

433 435 MHz 28.2

1)

RF Data Rate DR

RF Data Rate

tolerance

2)

RF Output Power

3)

DR

P

RF

RF

RF TOL

-1 1 % 28.4

4 5 6 dBm 2.5V <=VDD<=3.6V

20 kbit/s Manchester Coded 28.3

28.5

+25 to +60 °C

3 7 dBm 1.8V<=VDD < 2.5V

28.6

-40 to 0 °C

3 7 dBm 2.5V <=VDD<=3.6V

28.7

-40 to +25 °C

3 6 dBm 2.5V <=VDD<=3.6V

28.8

+60 to +125 °C

2 6 dBm 1.8V<=VDD < 2.5V

28.9

0 to +125 °C

FSK frequency shift 0 +/-40 +/-75 kHz programmable

28.10

see [2]

RF Data Duty Cycle DC

ASK Modulation depth MD

1) Parameters have been measured with the Data Sheet Reference Board at the 50 Ohm RF output.

2) Specification applies for following data-rates: 4096, 4200, 9600, 10000 and 19200 Baud. For other data-rates the

tolerance may increase to up to +/- 1.5%.

3) Valid for voltage at pin VDDPA = 2.1V

4) FSK duty cycle is characterized by eye-diagram evaluation

5) ASK duty cycle is defined at -3dB of the maximum RF power during ASK on

RF

RF

45 50 55 % valid for FSK4) and ASK5)

90 % 28.12

28.11

Data Sheet 15 Revision 1.2

2020-05-14

Page 16

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

Table 18 RF Crystal Oscillator

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Crystal Frequency f

Crystal oscillator drive

current

XTAL

I

Xtal_drive

25.920 26 26.080 MHz 29.1

1.5 mA This parameter reflects

29.2

the driving capability of

the crystal oscillator

Crystal Oscillator

startup time

t

Xtal_start

1msFor crystals

recommended by IFX

29.3

2.3.12 RC Oscillators

Table 19 RC Oscillator Characteristics

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Temperature drift of

2.2kHz oscillator

Total tolerance of

2.2kHz oscillator

1)

Temperature drift of

90kHz oscillator

TD2k -0.075 +0.075 %/K 30.1

TOL2k

tot

-30 30 % -40 to +125°C and over

30.2

lifetime

TD90k -0.05 +0.05 %/K 30.4

Total tolerance of

90kHz oscillator

2)

Temperature drift of

TOL90k

TD12M -0.05 +0.05 %/K 30.7

-5 5 % -40 to +125°C and over

tot

lifetime

30.5

12MHz oscillator

Total tolerance of

TOL12M

12MHz oscillator

1) The 2.2kHz oscillator is the clock source for the interval timer and the ON-OFF timer. The timers can be calibrated with

firmware functions. The calibration error is reported in the description of the FW function. This error is only valid if

temperature stays constant.

2) The 90kHz oscillator is the clock source for the sampling timer and the interframe timer. The timers can be calibrated

with firmware functions. The calibration error is reported in the description of the FW function. This error is only valid if

temperature stays constant.

-8 8 % -40 to +125°C and over

tot

lifetime

30.8

2.3.13 Wake-up and power-on timing

Data Sheet 16 Revision 1.2

2020-05-14

Page 17

SP40PLUS

Tire Pressure Monitoring Sensor

Specification

Table 20 Wake-up and power-on timing

Parameter Symbol Values Unit Note or Test Condition Number

Min. Typ. Max.

Power on time t

ini

10.2 ms Time after exceeding V

THR

until

31.1

start of I2C handler

Normal mode delay

time

t

NM_delay

110 µs Time after I2C command for

normal mode sent until

31.2

application code execution start

Resume from deep

idle time

t

resume

750 µs Time from resume event during

deep-idle to application code

31.3

execution start.

Mode selection time t

LF Wake-up time

1)

MS

t

LF wake-up

2.1 2.8 4.2 s see Chapter 4.2.5 31.4

5.3 ms Time from LF wake-up event

31.5

during power-down to

application code execution start.

IT Wake-up time

1)

t

IT wake-up

6 ms Time from interval timer elapsed

31.6

during power-down to

application code execution start.

PP2 Wake-up time

t

PP2 wake-

up

6 ms Time from level-change detected

at PP2 during power-down to

31.7

1)

application code execution start.

1) Note: the device stays in power-down most of the wake-up time and only 550µs(max) in run-state before application

code execution starts

Data Sheet 17 Revision 1.2

2020-05-14

Page 18

131412

11

10

9

8

213

4

5

6

7

output_en

SP40PLUS

Tire Pressure Monitoring Sensor

Pin Description

3 Pin Description

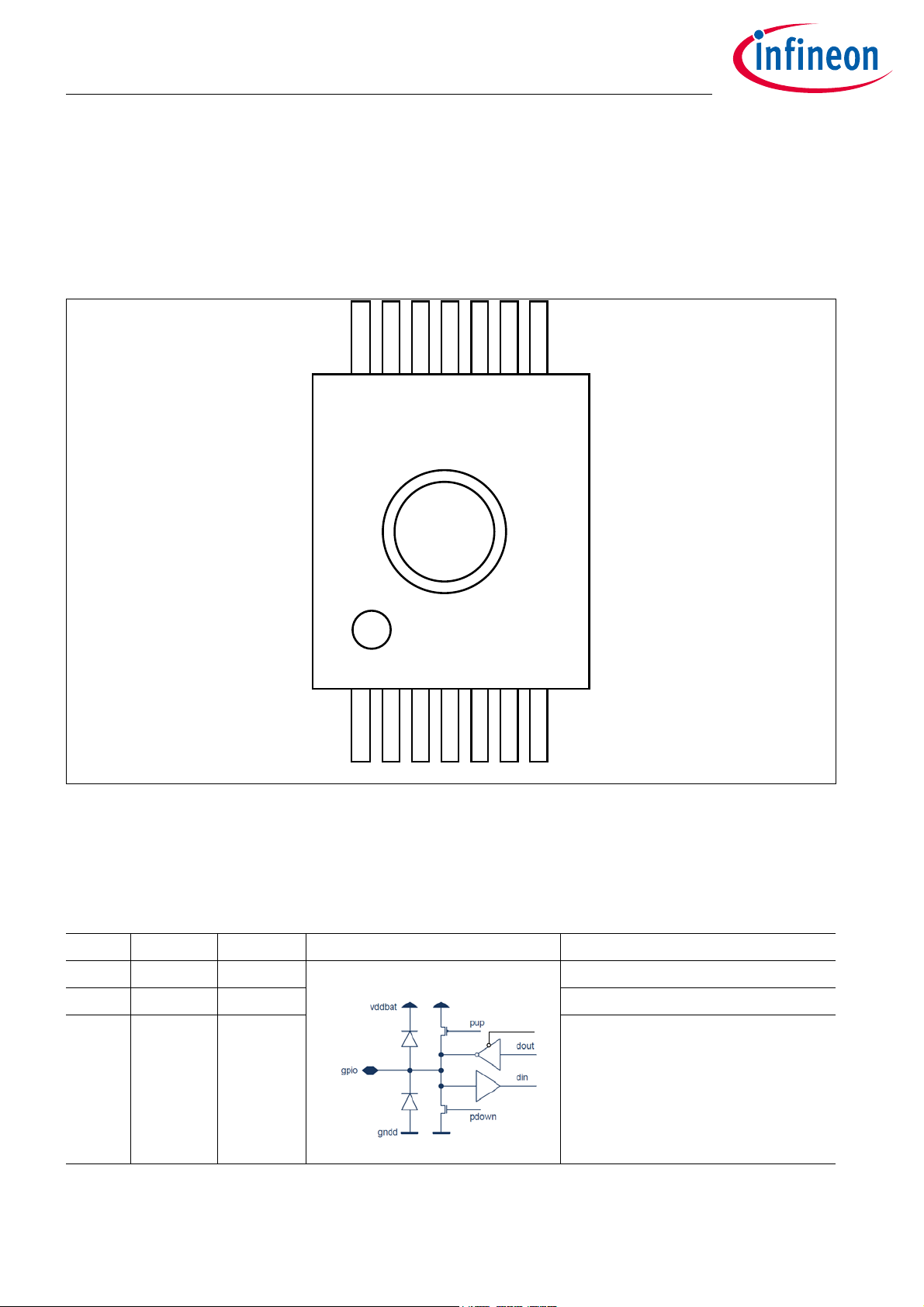

3.1 Pin Configuration

Figure 1 Pin Configuration

3.2 Pin Description

Table 21 Pin Description

Pin No. Name Pin Type Buffer Type Function

1SCL/PP0Digital I/O General Purpose-I/O I2C Clock

2 SDA/PP1 Digital I/O General Purpose-I/O I2C Data

3 PP2 Digital I/O General Purpose-I/O UART RX data

Data Sheet 18 Revision 1.2

2020-05-14

Page 19

output_en

SP40PLUS

Tire Pressure Monitoring Sensor

Pin Description

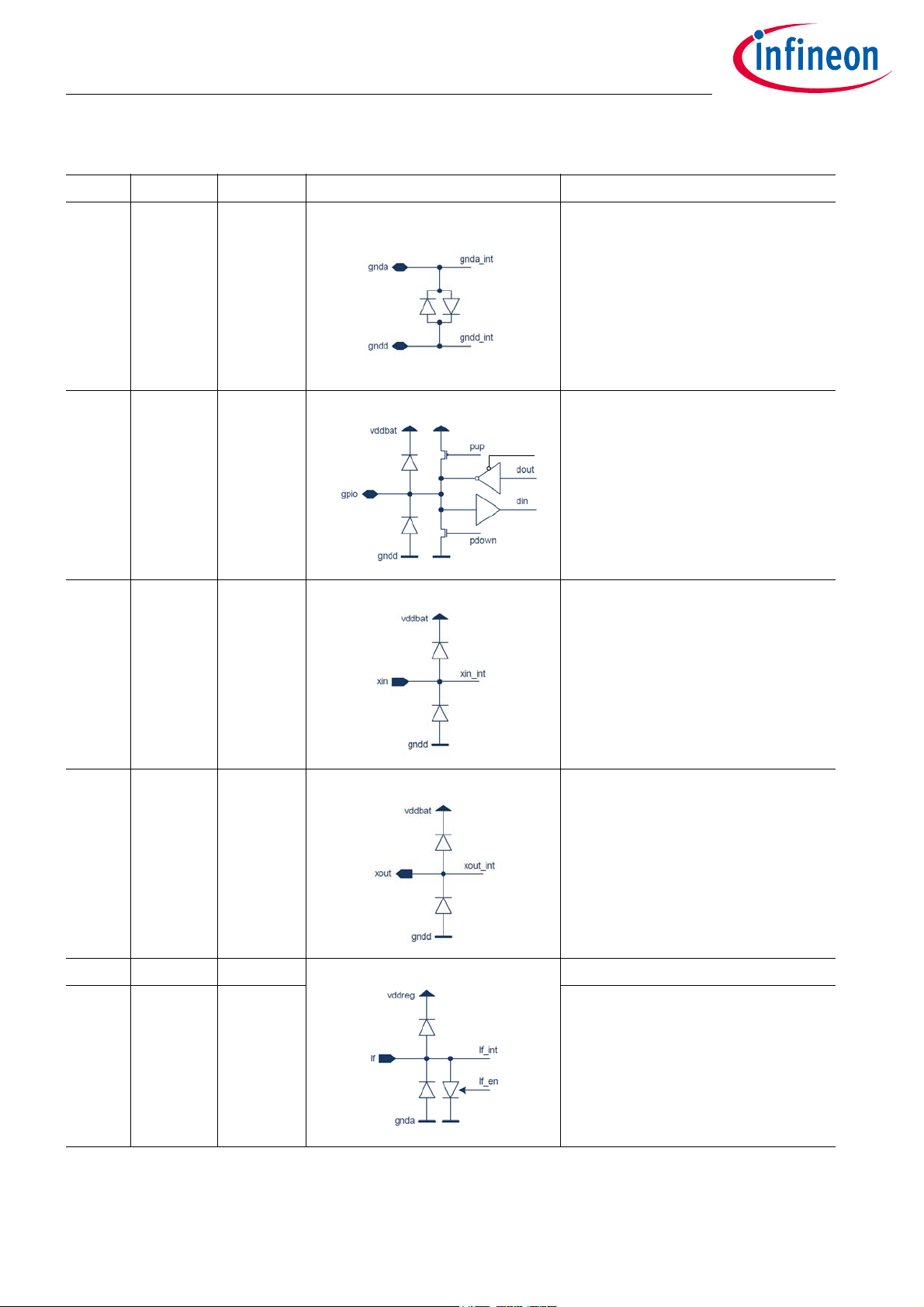

Table 21 Pin Description (cont’d)

Pin No. Name Pin Type Buffer Type Function

4GNDD

5 PP3 Digital I/O General Purpose-I/O UART TX data

1)

Supply Digital Ground

6XINAnalog Crystal oscillator input

7XOUTAnalog Crystal oscillator output

8LFNAnalog LF receiver negative input

9LFPAnalog LF receiver positive input

Data Sheet 19 Revision 1.2

2020-05-14

Page 20

SP40PLUS

Tire Pressure Monitoring Sensor

Pin Description

Table 21 Pin Description (cont’d)

Pin No. Name Pin Type Buffer Type Function

10 VDDREG Supply Regulated voltage output (1.5V)

2)

11 GNDA

1)

Supply Analog Ground

12 PAOUT Analog

output

13 VDDPA Analog

output

RF power amplifier output

Regulated voltage for PA

14 VDDBAT Supply Power supply

1) GNDD and GNDA are shorted internally via leadframe

2) Note: this pin is only intended for stabilization of the internal voltage of the SP40PLUS by an external capacitor. It

must not be used as external current source.

Data Sheet 20 Revision 1.2

2020-05-14

Page 21

SP40PLUS

Tire Pressure Monitoring Sensor

Special Features of the SP40PLUS

4 Special Features of the SP40PLUS

4.1 Operating Modes

Apart from normal operating mode the SP40PLUS provides additional operating modes for debugging and

programming purposes. These additional operating modes can be selected by sending a proper I2C command

within a specified time interval after power on reset (POR). The I2C command starts with the device address (6C

followed by a code for the operating mode to be selected. If the SP40PLUS does not receive any I2C command

after POR or a wrong command it starts up in normal operating mode (“Normal mode”).

Table 22 Operating Modes Overview

H

)

Operating mode Device

controlled by

Normal mode application

Short Description I2C

command

Normal operating mode for TPMS application 9876

1)

H

code

Program mode external I2C-

Master

Used for programming application code and user

configuration data. Additional I2C commands allow reading

1F5A

H

sensor measurement values.

Debug mode external I2C-

Master

Used for application code development. Commands for

RAM read/write, program counter manipulation, execute

FEDC

H

single step and run until breakpoint/interrupt are available.

1) The complete I2C sequence is: [0x6C] [command high byte] [command low byte]

4.2 Device states

In normal operation mode the SP40PLUS can be switched into several device states which differ in the number of

enabled circuit blocks. For lowest power consumption unused blocks are disconnected from power supply,

hence not even idle currents remain.

Table 23 Device states overview

Device state Short description Important activated blocks

Run state application code execution.

Idle state

1)

No code execution. Device is

waiting for a wake-up/resume

event. Fast recovery on wakeup/resume event.

• CPU with 12 MHz RC-oscillator

• All other blocks can be activated if needed

• 12 MHz CPU clock and CPU timer (CPU disabled)

•Optional: ADC

•Optional: TX-state machine, RF-transmitter

•Optional: Timer 0/1

• Optional: LF Receiver with 90 kHz oscillator

Deep idle state

2)

No code execution. Device is

waiting for a resume event from

sampling timer or wake-up

• Wake-up controller with 2.2kHz RC-oscillator

• 90 kHz oscillator

•System controller

event. Intended for equidistant

acceleration raw measurements.

Data Sheet 21 Revision 1.2

2020-05-14

• Optional: LF-receiver

Page 22

Run state

Power down

state

Deep idle

state

Thermal

shutdown

Idle state

TX low power

state

I2C

Handler

Valid I2C

comman

d or time-

out

Resume

Enter

idle

System

Reset

Enter

power-

down

Wake-

up

Resume

Enter

deep

idle

Enter

TX low

power

Enter

power

down

Resume

Wakeup/

Resume boot

sequence

Resume

Enter

thermal

SD

SequenceDevic e state

Reset boot

sequence

SP40PLUS

Tire Pressure Monitoring Sensor

Special Features of the SP40PLUS

Table 23 Device states overview (cont’d)

Device state Short description Important activated blocks

Power-down state No code execution. Device is

waiting for a wake-up event.

Lowest current consumption.

TX low power state Power-down state where TX

state-machine can be operated.

Device wakes-up/resumes on

interval-timer elapsed or

transmission end. Other events

are postponed.

Thermal shutdown

3)

state

Almost all circuits shut off.

Resume only if temperature

returns to normal operating

range.

1) In idle state the CPU is halted. When device resumes from idle code execution immediately continues behind the point

of entering idle state.

2) In deep idle the CPU is shut off. When device resumes from deep idle code execution restarts from reset vector.

3) In thermal shutdown the CPU is shut off. When device resumes from thermal shutdown code execution restarts from

reset vector.

• Wake-up controller with 2.2kHz RC-oscillator

• Optional: LF-receiver with 90 kHz oscillator

• Wake-up Controller with 2.2kHz RC-oscillator

• Optional: LF Receiver with 90 kHz oscillator

• 90kHz oscillator

•TX state machine

• RF-transmitter when needed by TX state machine

• Temperature detector

• Wake-up Controller with 2.2kHz RC-oscillator

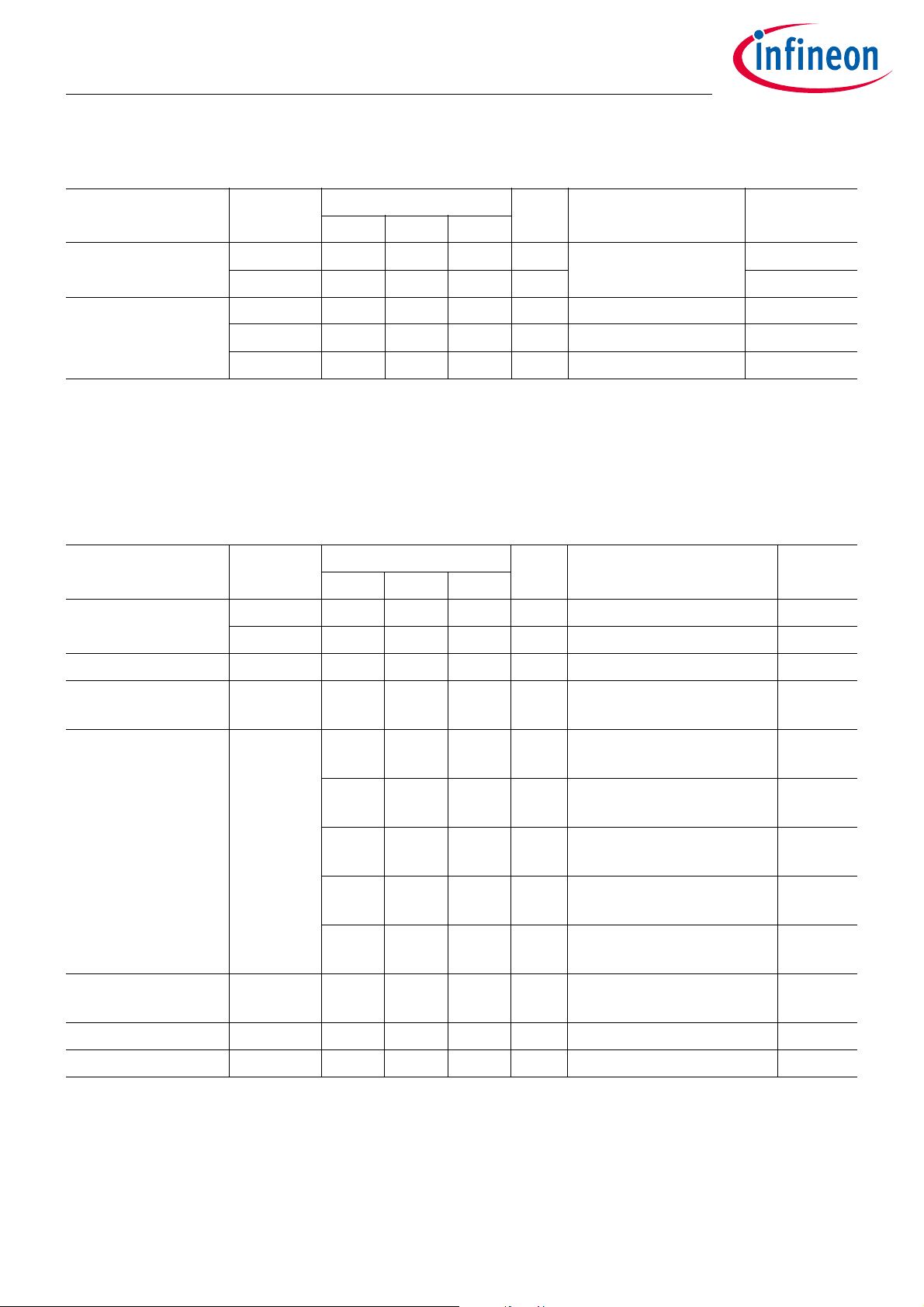

4.3 State Transitions

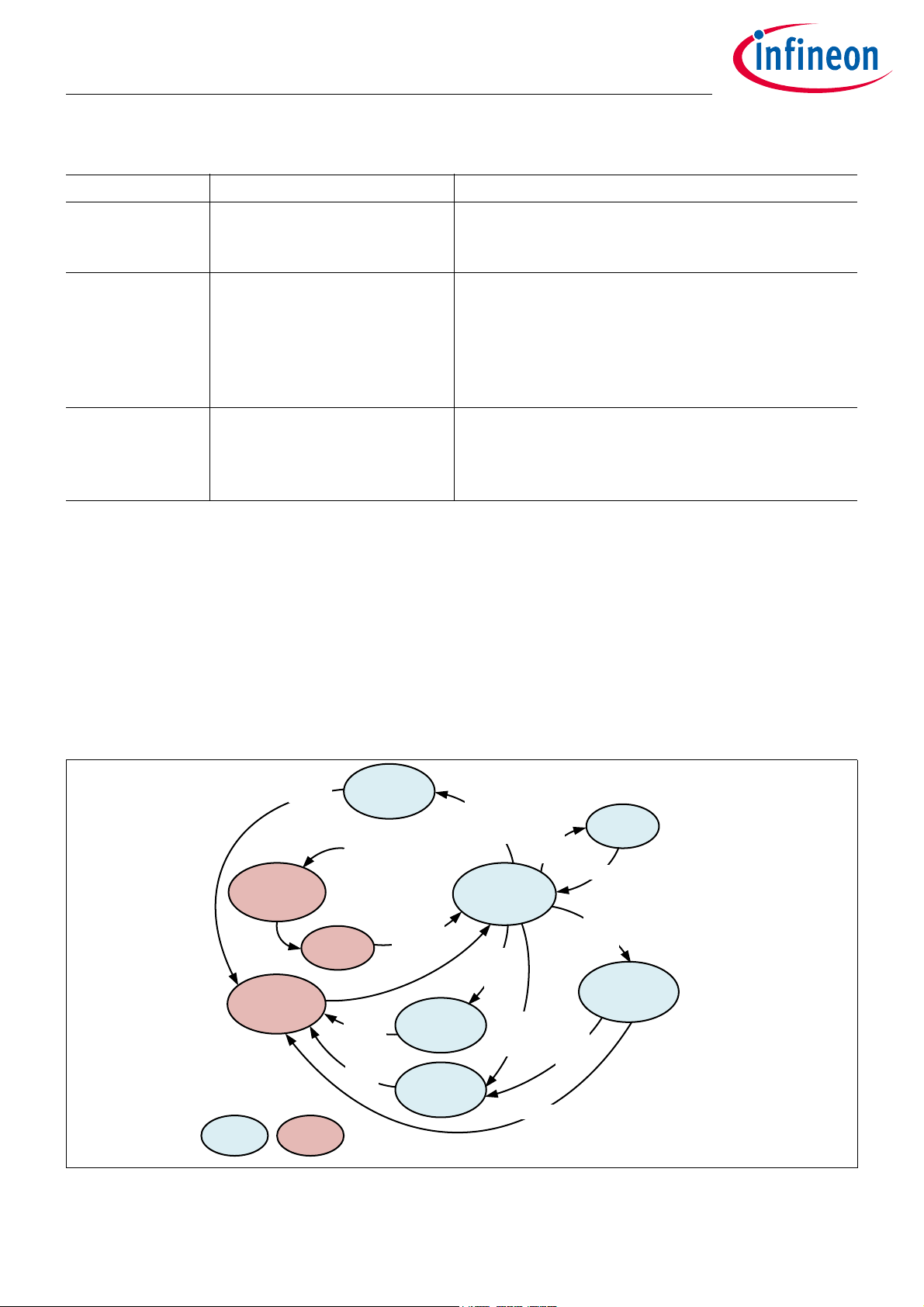

Figure 2 shows the possible state transitions in normal mode. The central device state is run state because only

in run state the state transitions can be configured. Entering other states from run state is controlled by

application code, either by calling firmware functions [1] or setting control bits [2]. State transitions from other

states are controlled by hardware events, e.g. timer events or LF receiver events.

Figure 2 State transitions in normal mode

Data Sheet 22 Revision 1.2

2020-05-14

Page 23

SP40PLUS

Tire Pressure Monitoring Sensor

Special Features of the SP40PLUS

Table 24 gives an overview of the event sources and the corresponding indicator flags. For each indicator flag

there is an accordant masking flag. However, it does not matter if an event is masked out or not, the indicator flag

will always be set if the event occurs, provided that the indicator register is powered. The masking flag only

determines if the event generates a wake-up/resume. Because not all event sources and all registers are powered

in all power states the actual event indicator flag behavior depends on power state. This behavior is also reported

in Table 24. Furthermore the table shows if the event will generate a resume/wake-up from the respective power

state. Especially in TX low power state certain wake-up/resume events are blocked by hardware in order not to

interrupt a running RF transmission.

(The flag SYSST.TDET, which indicates resume from thermal shutdown, works somewhat differently than the

other wake-up /resume flags. Therefore it is not reported in Table 24 but in Table 25, instead.)

Table 24 Event sources and indicator flags for all device states

Event Event indicator

flag

Power down Deep idle TX low

power

Idle state Run state

indicator flag behavior / event generates wake-up/resume

Interval timer elapsed WUF.ITIM_FLAG raised / yes raised / yes raised / yes raised / yes raised / n.a.

External signal at PP2 WUF.EXT_FLAG raised / yes raised / yes raised / no raised / yes raised / n.a.

LF carrier detected WUF.CD_FLAG raised / yes raised / yes raised / no raised / yes raised / n.a.

LF sync match WUF.SYNC_FLAG raised / yes raised / yes raised / no raised / yes raised / n.a.

LF pattern 0 match WUF.PM0_FLAG raised / yes raised / yes raised / no raised / yes raised / n.a.

LF pattern 1 match WUF.PM1_FLAG raised / yes raised / yes raised / no raised / yes raised / n.a.

LF end of message WUF.EOM_FLAG raised / yes raised / yes raised / no raised / yes raised / n.a.

LF buffer full WUF.BF_FLAG raised / yes raised / yes raised / no raised / yes raised / n.a.

Timer 0 underflow REF.RET0 cleared / no unchanged / no unchanged / no raised / yes raised / n.a.

Timer 1 underflow REF.RET1 cleared / no unchanged / no unchanged / no raised / yes raised / n.a.

1)

/ no

2)

raised / yes raised / n.a.

/ no

raised / yes raised / n.a.

TX encoder buffer empty REF.RERFU cleared / no unchanged / no undefined

TX encoder shift register empty REF.RERFF cleared / no unchanged / no undefined

ADC end of conversion (reserved) cleared / no unchanged / no raised / no raised / yes raised / n.a.

Sampling timer elapsed REF.RESTF cleared / no unchanged / no unchanged / no raised / yes raised / n.a.

Sampling timer power-up (reserved) n.a. / no n.a. / yes n.a. / no n.a. / no n.a / n.a.

1) Bit RERFU is only used for CPU transmission mode. It has no meaning if the transmission controller ist used.

2) Bit RERFF is only used for CPU transmission mode. It has no meaning if the transmission controller ist used.

Complementary to the flags in Table 24 there are four additional flags which indicate from which power state the

device woke-up/resumed. Further there is a flag which is set if any unmasked wake-up event was detected and

another flag which is set if any unmasked resume event was detected. These six flags and their behavior are listed

in Table 25. Figure 4-1 shows how all the flags from Table 24 and Table 25 are connected.

Table 25 Additional wake-up/resume indicator flags

Condition for raising the flag Flag name Power

down

Wake-up from power down

Resume from thermal shutdown

Resume from deep idle

SYSST.WUPDWN raised

SYSST.TDET raised

RESYSCF.REDIDLE raised

Resume from TX low power RESYSCF.RETXLP

A non-masked wake-up event DSR0.WUPEND

raised raised raised raised raised raised

A non-masked resume event DSR1.REPEND

Data Sheet 23 Revision 1.2

2020-05-14

Thermal SDDeep

idle

TX low

power

Idle Run

state

raised

raised raised raised

Page 24

Wake-Up Controller

CD_FLAG

SYNC_FLAG

PM0_FLAG

PM1_FLAG

EOM_FLAG

BF_FLAG

ITIM_FLAG

EXT_FLAG

WUF

CD_MASK

SYNC_MASK

PM0_MASK

PM1_MASK

EOM_MASK

BF_MASK

ITIM_MASK

EXT_MASK

WUM

TDET

SYSST

State-

machine

OR

logic

OR

logic

WUPEND

WUPDWN

DSR0

SYSST

System Controller

RET0

RET1

RERFU

RERFF

reserved

reserved

reserved

RESTF

REF REFM

State-

machine

OR

logic

OR

logic

REPEND

REDIDLE

DSR1

RESYSCF

RET0M

RET1M

RERFUM

RERFFM

reserved

reserved

reserved

RESTFM

reserved

(Sample Timer

power-up trigger)

RETXLP

SP40PLUS

Tire Pressure Monitoring Sensor

Special Features of the SP40PLUS

Figure 4-1 Connection between all wake-up/resume related flags

Data Sheet 24 Revision 1.2

2020-05-14

Page 25

Encoder

Manchester

Biphase

SDPLL

FSK

Modulator

ASK

Modulator

PA

PAOUT

XOSC

XIN

XOUT

RF-Transmitter

8051 Based

MCU

I2C

Controller

Timer 0/1 Watchdog

CRC

Core

FSM

RF-Transmission Controller

DMA

RC OSC

2.2kHz

RC OSC

90kHz

RC OSC

12MHz

Clock Generators

Peripheral Ports / I2C /UART

IO-PORT

PP0/SCL

PP1/SDA

PP2

PP3

ROM

Memories

Flash

RAM

Retention

RAM

SFR

Digital

Baseband

Processor

Carrier

Detector

125kHz

Receiver

LFN

LFP

LF Receiver

FSM

Power

Switch

Controller

System Co ntroller

Clock &

Reset

Controller

ADC Controll er

FSM

Clock &

Reset

Controller

Power

Switch

Controller

LF

ON/OFF

Timer

Interval

Timer

Wake Up Controller

IO-Port

Control

GNDA

Power Supply & Reset Generator

VMIN

TEMP

Detector

PA Voltage

Regulator

VDDPA

VDDREG

VDDBAT

GNDD

Measurement Interface

A

D

Ref Voltage

& Offset

DAC

Bandgap &

PTAT

MUX

RD

V1P

V1M

V1N

V2P

V2M

V2N

VDD

VDD

Data & Address Bus

Sensor Interface

Bond Wire

Surveillance

High Power

Voltage

Regulator

Brown Ou t

Detector

Low Power

Voltage

Regulator

MEMS Sensor

Die

A-Cell

P-Cell

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

5 Functional Descriptions

5.1 SP40PLUS Block Diagram

Figure 2 SP40PLUS Block Diagram

5.2 Wake-up Controller

In a typical TPMS application the SP40PLUS is in power-down state most of its operating lifetime. In power-down

state, which is triggered by calling the firmware function Lib_Serv_Low_Power(2), the device is controlled only

by the wake-up controller. The wake-up controller is the block with highest priority in terms of power

management. It is always powered and waits for a wake-up event from different sources. For lowest power

consumption the wake-up controller is clocked by the 2.2 kHz oscillator. If a wake-up event happens and the

event is not masked then the wake-up controller powers on the system controller which takes over device

control. The device wakes up in the same mode (normal- or debug- mode) from which power-down was called.

Before code execution starts the CPU runs a firmware boot sequence and all registers are initialized with their

wake-up values. In case of normal mode the time from wake-up event occurrence until start of application code

execution is in the range of several milliseconds (see Table 20) . The implemented wake-up sources are:

•Interval timer

• LF-Receiver: carrier detector

• LF-Receiver: sync pattern detector

Data Sheet 25 Revision 1.2

2020-05-14

Page 26

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

• LF-Receiver: data pattern matching circuit

• LF-Receiver: data buffer full

• LF-Receiver: end of message

• General purpose I/O PP2

• Temperature detector when device is in thermal shutdown

The second main function of the wake-up controller is reset handling. The reset signals themselves are generated

in the block “power supply & reset generator”. A system-reset may be trigged by:

• Brown out (internal regulated voltage drops below a certain threshold)

• Power on

• Under voltage (battery voltage below a certain threshold, see Table 10)

•Software

• Watchdog

• Flash Error (detected via error correction code, ECC)

Apart from the flash error all other system-reset events are not maskable. The register SYSST indicates the reset

source after restart of the device and can be read in application code. After reset release a firmware boot

sequence is executed, the registers are initiated with their reset values, and an I2C handler is called. The handler

waits a certain time (see “mode selection time”, Table 20) for an valid I2C mode selection command [2]. If no

valid I2C signal is received the device starts application code execution after mode selection time elapses.

Although thermal shutdown state is not identical with power-down state, thermal shutdown release event

behaves like a wake-up and all registers are initiated with their wake-up values.

The flag WUPEND allows to distinguish if a wake-up or another restart, i.e. reset or resume, occurred. In case of

thermal shutdown release WUPEND indicates the wake-up, too.

For identification each wake-up source has its own flag in register WUF (only flag TDET is located in SYSST.)

Several flags may be set in WUF if more than one wake-up event occur before reading WUF. Since WUF is cleared

on read, it is recommended not to read single bits but copy WUF into RAM before analyzing it. The flags in the

corresponding WUM register are used for masking individual wake-up sources. Although there is a masking flag

for the interval-timer this flag has no effect: the interval-timer wake-up is not maskable for fail-safe reasons. Note

that if masking a wake-up event in the WUM register the corresponding wake-up is not triggered when the event

occurs, but the corresponding flag in the WUF register is always set, independent of the WUM setting and

independent on device state (low power, run state etc.). This way it is possible to check the WUF for events that

did not trigger a wake-up in order to process these events at a later point in time.

Furthermore the wake-up controller comprises the LF ON-OFF timer that allows operating the LF-receiver with a

configurable duty cycle for power saving reasons. Details see Chapter 5.11.

Important registers associated with the wake-up controller are:

• DSR0 (bit WUPEND. This bit indicates a pending wake-up event)

• SYSST (indicates the system reset source)

• RMASK (Reset mask register)

•WUF (indicates the wake-up source)

• WUM (for masking certain wake-up sources)

• CFG0 (bit SRESET for triggering software reset)

5.2.1 Interval Timer

The purpose of the interval timer is to periodically wake-up the device from power down. The timer is active in

any low power state and is clocked by the 2.2kHz oscillator. The interval timer is counting down, a wake-up event

Data Sheet 26 Revision 1.2

2020-05-14

Page 27

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

is triggered upon timer underflow. Although there is a masking bit available in WUM register for the interval timer,

the wake-up event cannot be masked in normal mode. Especially when using the TX-low-power or deep-idle state

it must be made sure by proper timing setting that the interval timer does not interrupt the telegram transmission

or the data acquisition.

The interval timer is separated into a 12 bit pre-counter (SFRs IT0 and IT1) and a 12 bit post-counter (SFRs IT2 and

IT3). For calibrating the pre-counter a firmware function is provided. The post-counter is set by directly writing to

IT2/IT3. This concept allows for quick changing of the timer interval by just changing IT2/3 without running the

calibration routine. Note that writing to IT0/1/2/3 is setting the pre- and post-counter preload value, reading

IT0/1/2/3 provides the current counter reading. The timer is automatically reloaded after underflow.

In thermal shutdown the interval timer is used for periodically checking the temperature detector.

The associated registers are:

• IT0, IT1: interval timer pre-counter (also referred to as tick counter)

• IT2, IT3: interval timer post-counter (also referred to as period counter)

• CFG0.ITINIT: Setting this bit initializes the interval timer with the preload value

5.2.2 LF ON-OFF Timer

The ON-OFF timer is used for switching on and off the LF receiver with a low duty cycle in order to save energy.

Consequently the timer supports long OFF-times of up to 5.7 sec and shorter ON-times of maximal 0.36 sec. Note

that the LF reception is inhibited 3.9 ms by design after being switched on because the LF receiver needs some

time to settle, i.e. the effective On-time is accordingly shorter.

Here are the minimum ON-times for some use cases:

• Carrier Detection for LF-CW signal: minimum ON-time = 3.9 ms + 0.1 ms = 4 ms

• Carrier detection for pulsed LF carrier: minimum ON-time = 3.9 ms + 4.75 ms = 8.7ms

• Data reception mode for periodic repetition of LF-telegram: minimum ON-time = 3.9 ms + period time

The user does not need to directly access the ON-OFF timer registers since the firmware function

Lib_Serv_OnOff_Timer_Calib() can be used for configuration. Setting bits ENLFRX and ENOOTIM activates the

ON-OFF timer. The current count value of the ON-OFF timer cannot be read by software.

Associated registers:

• LFRXC, bits ENTOOM and ENLFRX

5.2.3 LF receiver wake-up/resume events

All wake-up events generated by the LF receiver are maskable. The events are:

• Carrier detected

• Sync pattern detected

• Wake-up pattern match

• Data buffer full detected

• End of message

Refer to Chapter 5.11 for more details.

5.2.4 General purpose I/O PP2 wake-up/resume event

I/O Port PP2 allows maskable wake-up from an external source. In order to use this wake-up source, PP2 needs

to be configured as input (Flag PPD2=1), the corresponding pull resistor must be enabled (Flag PPO2 = 1) and the

corresponding wake-up must be enabled (Flag EXT_MASK = 0).

Data Sheet 27 Revision 1.2

2020-05-14

Page 28

Device

Operable

Device Operable

Device

in Res et

Device

in

Reset

0V

3V

time

V

UVRA

V

THR

VDDBAT

t

MS

t

ini

t

MS

t

ini

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

The flag PPS2 is used to define whether the wake-up is triggered on high or low level. If PPS2 = 1 wake-up is

triggered on high level at PP2 pin.

5.2.5 Power-on and under-voltage reset

Figure 3 shows the device behavior depending on voltage at VDDBAT pin. If the voltage falls below a certain

threshold V

reset release threshold V

After the initialization phase the operation mode of the device can be selected by sending an I2C command. The

mode selection is only possible during the time interval t

command, the device goes into normal mode. If a valid I2C command is received during t

in the corresponding mode right after command reception. Table 26 shows the behavior of the device during t

depending on received I2C command.

a system-reset is triggered. The device stays in reset until the voltage at VDDBAT pin exceeds the

UVRA

. After reset release the device initialization is started which takes a certain time, t

THR

. If tMS elapses without reception of any valid I2C

MS

the device starts up

MS

ini

MS

.

Figure 3 Power-on and under-voltage behavior

Table 26 SP40PLUS behavior during mode selection phase

I2C Command Device behavior

None Start with normal mode after t

Wrong I2C address Start with normal mode after t

Invalid mode selection command Start with normal mode after t

Valid mode selection command Start with selected mode immediately after command reception

5.2.6 Software reset, watchdog reset and flash error reset

After a reset triggered by software, watchdog or flash-error the device runs through the reset boot sequence and

the mode selection phase.

The software reset can be triggered by setting the bit SRESET (located in register CFG0) in application code.

A flash-error reset occurs if the flash error correction logic (ECC) detects a non-correctable double bit error (ECC2)

when reading a byte from flash.

Register SYSST is used to identify the reset source after a system reset.

elapsed

MS

elapsed

MS

elapsed

MS

Data Sheet 28 Revision 1.2

2020-05-14

Page 29

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

5.2.7 Thermal Shutdown

Thermal shutdown is triggered by calling the firmware function Lib_Serv_Thermal_Shutdown() in application

code. This firmware function brings the SP40PLUS into shutdown if the temperature is either above the hot

temperature threshold T

temperature detector. Once in thermal shutdown the device is only released if the on-chip temperature detector

indicates a temperature below the hot release temperature T

T

. In order to save energy during thermal shutdown the temperature detector is not powered continuously

COLD_RE

but switched on periodically by the interval-timer. The period is defined by function parameter when calling

Lib_Serv_Thermal_Shutdown().

After release from thermal shutdown a wake-up is performed and flag WUPEND is set. However, in this case the

wake-up source is not indicated by WUF register, but by bit SYSST.TDET.

5.3 System Controller

Main function of the system controller is power management after device wake-up from power-down or device

resume from idle, deep idle state or TX-low-power state. Unlike the wake-up controller most other circuits can be

disconnected from power individually. Depending on the device state the system controller connects the

required blocks to the power domain. Here the device states are listed, ordered by current consumption, starting

with the state with highest current consumption:

or below the cold temperature threshold T

HOT_TH

HOT_RE

by using a dedicated

COLD_TH

or above the cold release temperature

• TX low power state during RF transmission

•Run state

• Idle state (run state with CPU disconnected from system clock)

• TX low power state during interframe time

• Deep idle state

• Power-down state (optional with LF receiver enabled)

1)

Important registers associated with the system controller are:

• REF (maskable resume event flag register)

• RESYSCF (indicates resume from deep-idle and TX-low-power)

• REFM (resume event mask register)

• DSR1 (bit REPEND. This bit indicates a pending resume event)

• CLKCFG (field DIVIC for selecting an optional system clock division factor)

1) The power-down state is controlled by the wake-up controller and not by the system controller

Data Sheet 29 Revision 1.2

2020-05-14

Page 30

x Ca librate s ampling ti mer

x Start sampling timer

Idle state

All measurements done?

Deep Idle

no

x Stop sampling timer

Start sampling sequence

Stop sampling sequence

x Call Lib_Acq_Meas_Acceleration()

Resume from idle state

Resume from deep idle state

Resumed from

deep idle?

Idle state

yes

no

CPU start-up period

Resume from idle state

Sampling period

Sampling timer

ADC-trigger event

x S tore measurement value in

Retention RAM

Execute other application code

Code execution started at reset

vecto r

Color code:

Application code

executed

Jump point (label)

No app lication co de

execution

Sampling timer

ADC-trigger event

Sampli ng time r

power-up event

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

5.3.1 Sampling Timer

In certain applications periodic acceleration measurements must be carried out over a longer period of time.

There are two major requirements for this application: low power consumption and exact keeping of time

(sampling interval) between two acceleration measurements. In order to meet these requirements a timer is

needed which runs in a device state with very low power consumption, namely the deep idle state. Unlike in

power-down, in deep idle the 90 kHz oscillator is running for providing the needed timing accuracy.

Figure 4 Sampling timer application flow

In order to use the sampling timer it needs to be calibrated and started in application code (see flow diagram in

Figure 4). Subsequently idle state must be entered immediately because resume from idle (ADC triggered event)

occurs only a few 10µs after starting the timer. After resume from idle, when application code execution

continues, the acceleration acquisition function should be called at first. Thereafter additional application code

can be carried out in order to store measurement values in retention RAM.

If more samples must be acquired, application code then enters deep idle state in order to save energy; otherwise

the sampling timer can be stopped and the sequence is terminated. The sampling timer resumes the device from

deep idle state by power-up event. The CPU is re-started and code execution starts from the reset vector. Here

the application code must decide if the device was restarted from deep idle state or not. If yes, idle state is

Data Sheet 30 Revision 1.2

2020-05-14

Page 31

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

entered and the next sample is measured when idle state ends. If not, the CPU was restarted due to another event

and the corresponding application code must be executed.

The implementation of the two trigger events allows exact keeping of sampling period because resuming from

idle state occurs without time delay and the idle state period buffers possible variations of the start-up time. In

order to save energy the idle period should be kept as short as possible.

There is no need to configure the sampling timer registers directly because the library function

Lib_Serv_Sample_Timer_Calib() is available for this purpose [1]. The execution time of the application code

marked by the dashed rectangle in Figure 4 is an input parameter for this function. The function calculates the

point of time for resume from deep idle by considering the code run time and the power-up time (the power-up

time is composed of hardware start-up time and firmw are boot sequence, for the exact value see Table 20). This

way the idle period is kept no longer than necessary because power consumption in idle state is higher than in

deep idle state.

Note that the deep idle state can be terminated by LF-receiver events , interval-timer or PP2 event. Hence it must

be made sure in application that sampling phase is not affected by one of these event sources, e.g. by masking

the corresponding flags.

Associated registers:

•STIMCFG0 (sampling timer low byte)

• STIMCFG1 (bit EN for enabling sampling timer and sampling timer high bits)

• STIMCFG2 (power up period configuration)

5.4 Clock Generators

The SP40PLUS comprises three on-chip RC oscillators in order to fulfill the extremely different requirements in

terms of power consumption and cycle time for different operating states. A 2.2 kHz oscillator is operated in

power-down for lowest power consumption. A 90 kHz oscillator is implemented for clocking the system

controller, the interframe timer, the sampling timer, and the digital part of th e LF receiver. Finally a 12 MHz

oscillator is used for the CPU. This clock may be divided (controlled by bit field DIVIC) and is called system clock.

The 90 kHz and 12 MHz clock sources are switched on by the wake-up controller and the system controller,

respectively, and only if needed. The 90 kHz and 12 MHz oscillators are trimmed in production.

For RF transmission and calibration purposes a crystal oscillator is implemented as well. Details about the

implementation of the crystal oscillator are described in Chapter 5.9.7.

Figure 5 shows a fundamental clock distribution diagram, i.e. which clock source is used for which digital block.

The white triangles (gates) indicate for which blocks the clock can be gated in order to save energy. For most

blocks the gating is done automatically. In some cases gating can be controlled by application code. In this case

the corresponding control bit is drawn next to the gate.

Most SFRs are always clocked by system clock if the CPU is running. But there are some exceptions which are

depicted in Figure 5, namely registers RFD, RFS and RFENC. Clock distribution to these registers is controlled by

internal control bits TXMASTER and RFENC. These control bits are configured by firmware function

Lib_Serv_Config_RF_Transmission. The bits are mentioned for information only.

Data Sheet 31 Revision 1.2

2020-05-14

Page 32

RC OSC

2.2kHz

RC OSC

90kHz

Wake-Up

Controller

FSM

Timer 0/1

Watchdog

LF-Digital

Baseband

LF

ON/OFF

Timer

ENOOTIM

Sampling

Timer

System

Controller

FSM

Interframe

Timer

EN

RC OSC

12Mhz

I2CMEIF UART

I2CEN

Divider

CRC

Interval

Timer

UARTEN

TIMEN

XOSC

26MHz

DIVIC

Encoder

Manchester

Biphase

RF

Transmitter

FSM

PLL

RFD

RFENC.RFDLEN

RFENC.RFMODE

0 1

TXMASTER

1)

TXDEN

1)

CPU

OBW

Controller

OBWCE N

RFS

1) Internal registers, see text

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

Figure 5 Clock distribution diagram

5.5 Core

The Core comprises a 8051 based MCU and the following peripherals:

•Timer Module

•Watchdog

• Hardware CRC

•I2C Controller

•UART interface

Data Sheet 32 Revision 1.2

2020-05-14

Page 33

SP40PLUS

Tire Pressure Monitoring Sensor

Functional Descriptions

5.5.1 Timer Module

The timer module consists of six registers TCON, TMOD, TL0, TH0, TL1 and TH1. The timer module enable bit

TIMEN is located in register CFG2. Those firmware routines that are using timers disable the timer module prior

to returning to application code. Therefore generally TIMEN should be set before timer module is configured and