Page 1

RIF

Radar interface

AURIX™ TC3xx Microcontroller Training

V1.0 2020-06

Please read the Important Notice and Warnings at the end of this document

Page 2

RIF

Radar Interface

Key Features Customer Benefits

Highlights

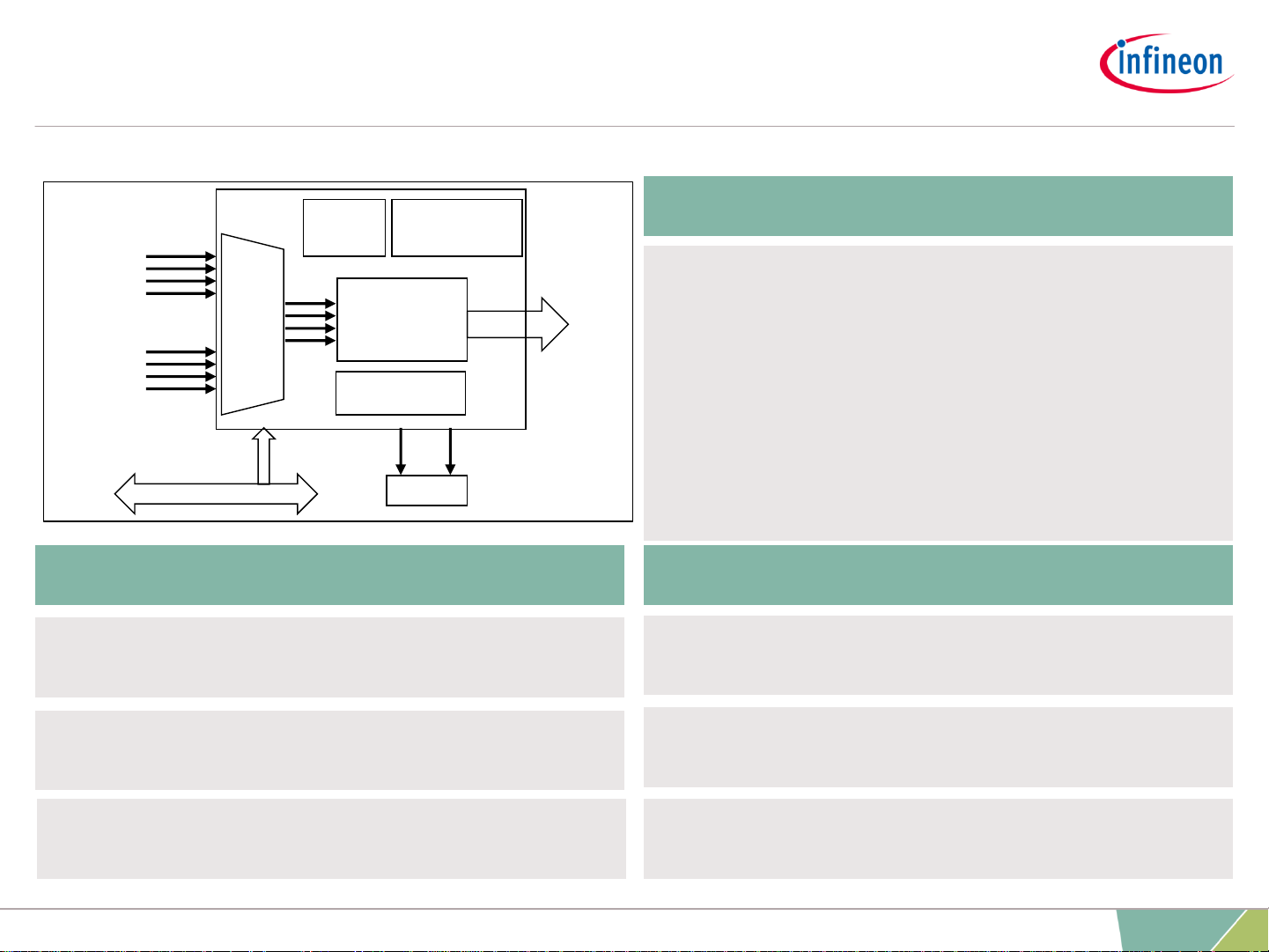

› The RIF is responsible for the interface

between the Radar ADC (Internal or

External) and an SPU module

› The RIF handles formatting the incoming

data so it matches the SPU RIF input

format

› The RIF can assert a safe communication

with external ADC and SPU

Input selection

Data formatting

› Compatibility with many MMIC and not

only Infineon products

› Wide range of data formats can be used

› Enabling ASIL-B radar processingSafety features

RIF

SPU

Internal ADC

LVDS

0

1

Formatting

Frame wd

IR

Dual RIF

synchro

INT

ERR

BBB

Reg config

CRC

2

2020-06-05 Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 3

RIF

Input selection

› The RIF can retrieve the data from up to 4 channels

› The data can come either from internal ADC or external ADC via LVDS

lines

AURIX™ TC3xx

Internal

ADC

RF

Front-End

RF

Front-End

External

ADC

LVDS

RIF

0

1

SPU

3

2020-06-05 Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 4

RIF

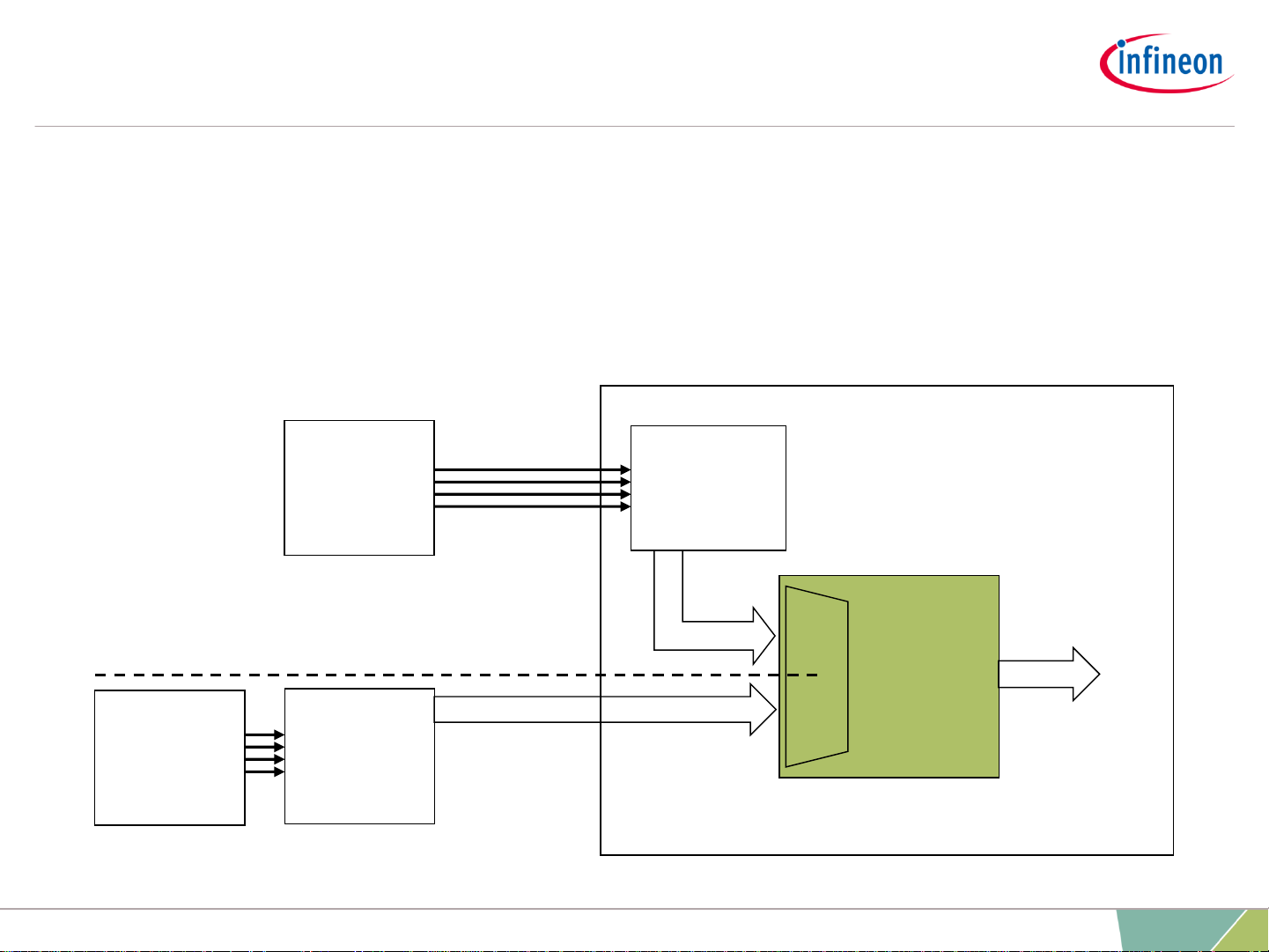

Data formatting

› SPU expects 16bit signed Qm.n integers as an input from the RIF, which

are delivered to the SPU in 32bit packet

› On the other hand, the RIF accepts a wider range of formats and is

responsible for adjusting the direction (lsb/msb), data length (16 bits) and

format of the incoming ADC data so it fits the SPU RIF input format

External

ADC

Internal

ADC

RIF

SPU

› uint 10-16 bit

› int 10-16 bit

› signed/unsigned

Q1.9, Q1.11,

Q1.13

› unsigned fixed

point Q1.15

› uint 12 bit

16bit signed Qm.n integer

4

2020-06-05 Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 5

RIF

Safety features

› In order to enable up to ASIL-B safety requirements, the RIF implements

several safety features:

– For external ADC: the possibility to add a CRC check at the end of every

ramp

– Safety critical configuration register can be CRC checked

– CRC check can be added to the output data of the RIF in order to assert

safe communication with the SPU

– Partial Lockstep: certain safety critical sub-blocks are duplicated to create

redundancy. If enabled, an alarm can be raised in case of mismatch

SPU

RIF

External ADC

Serial CRC

RIGISTER CRC

Partial lockstep

SPU CRC

5

2020-06-05 Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 6

RIF

System integration

RIF

Internal

ADC

LVDS

SPU

BBB

Register File

IR

CPUs

DMA

INT

ERR

› The RIF is connected to the internal ADC, the LVDS pad and the SPU in

order to enable ADC data transfers

› The RIF is capable of communicating events and errors to the application

via several Interrupt and Error lines through the Interrupt router

6

2020-06-05 Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 7

Application example

Radar frame reception

› In this example, the RIF is programmed to receive a frame from 4

channels

RIF SPUADC

1

1. Receiving a complete frame from 4 channels

2. Signaling a frame is ready to be transmitted

3. Transmit the formatted frame in 32bit packets to the SPU

2

3

7

2020-06-05 Copyright © Infineon Technologies AG 2020. All rights reserved.

Page 8

IMPORTANT NOTICE

The information given in this document shall in no

event be regarded as a guarantee of conditions or

characteristics (“Beschaffenheitsgarantie”).

With respect to any examples, hints or any typical

values stated herein and/or any information

regarding the application of the product, Infineon

Technologies hereby disclaims any and all

warranties and liabilities of any kind, including

without limitation warranties of non-infringement

of intellectual property rightsof any third party.

In addition, any information given in this

document is subject to customer’s compliance

with its obligations stated in this document and

any applicable legal requirements, norms and

standards concerning customer’s products and

any use of the product of Infineon Technologies in

customer’s applications.

The data contained in this document is exclusively

intended for technically trained staff. It is the

responsibility of customer’s technical

departments to evaluate the suitability of the

product for the intended application and the

completeness of the product information given in

this document with respectto suchapplication.

For further information on the product,

technology, delivery terms and conditions and

prices please contact your nearest Infineon

Technologies office (www.infineon.com).

WARNINGS

Due to technical requirements products may

contain dangerous substances. For information

on the types in question please contact your

nearest Infineon Technologies office.

Except as otherwise explicitly approved by

Infineon Technologies in a written document

signed by authorized representatives of Infineon

Technologies, Infineon Technologies’ products

may not be used in any applications where a

failure of the product or any consequences of the

use thereof can reasonably be expected to result

in personal injury.

Edition 2020-06

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2020 Infineon Technologies AG.

All Rights Reserved.

Do you have a question about this

document?

Email: erratum@infineon.com

Document reference

AURIX_Training_1_Radar_Interface

Trademarks

All referenced product or service names andtrademarksare the propertyof their respective owners.

Loading...

Loading...