Preliminary Data Sheet, V0.9, April 2008

PMA7110

RF Transmitter IC with embedded 8051

Microcontroller, LF 125kHz ASK Receiver

and FSK/ASK 315/434/868/915 MHz

Transmitter

Sense & Control

Edition 2008-04-28

Published by Infineon Technologies AG,

Am Campeon 1-12

85579 Neubiberg, Germany

© Infineon Technologies AG 2008-04-28.

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding

circuits, descriptions and charts stated herein.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office in Germany or the Infineon Technologies Companies and our Infineon Technologies

Representatives worldwide (www.infineon.com).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

Preliminary Data Sheet, V0.9, April 2008

PMA7110

RF Transmitter IC with embedded 8051

Microcontroller, LF 125kHz ASK Receiver

and FSK/ASK 315/434/868/915 MHz

Transmitter

Sense & Control

PMA7110

Revision History:2008-04-28 V0.9

PMA7110

Page 129

Page 132 Update RF characterization for D9 ~ D17

Page 128, Page 141 Update flash code/data memory program temeprature and erase cycle: B4, O1,

update typical value of transmit current consumption

O2, O6 ~ O8.

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

sensors@infineon.com

Preliminary Data Sheet 4 V0.9, 2008-04-28

PMA7110

Preliminary Data Sheet 5 V0.9, 2008-04-28

PMA7110

1 Product Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

1.3 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.1 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

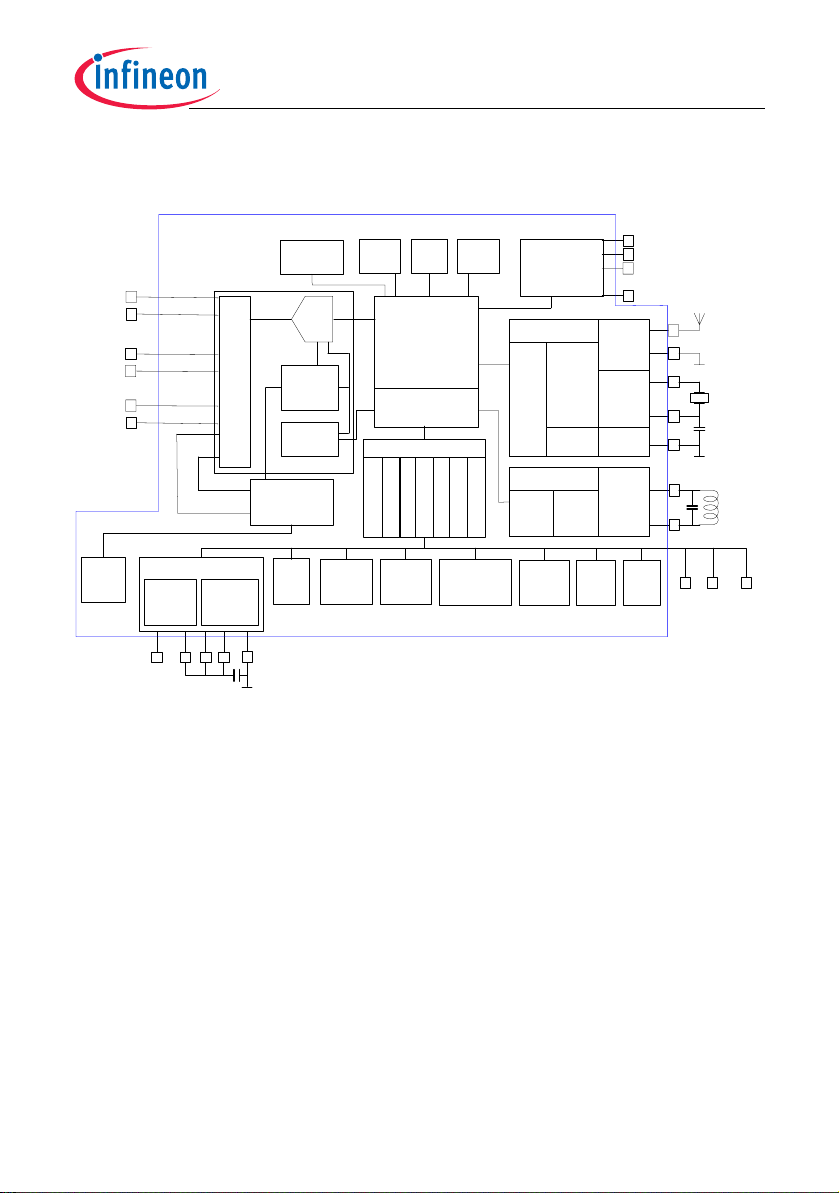

2.2 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.3 Operating Modes and States . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.3.1 Operating mode selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

2.3.2 State Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3.2.1 INIT State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3.2.2 RUN State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.3.2.3 IDLE State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.3.2.4 POWER DOWN State . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2.3.2.5 THERMAL SHUTDOWN state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

2.3.2.6 State Transitions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3.2.7 Status of PMA7110 Blocks in Different States . . . . . . . . . . . . . . . . . . . . . . . 37

2.4 Fault protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.4.1 Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.4.2 VMIN Detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.4.3 FLASH Memory Checksum . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.4.4 ADC Measurement Overflow & Underflow . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.4.5 TMAX Detector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.5 Functional Block Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.5.1 Sensor Interfaces and Data Acquisition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.5.1.1 Sensor Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

2.5.1.2 Two differential high sensitive interfaces to external Sensors . . . . . . . . . . . . 43

2.5.1.3 Interface to other signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.5.1.4 Reference voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

2.5.1.5 Temperature Sensor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.5.1.6 Battery Voltage Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

2.5.2 Memory Organization and Special Function Registers (SFR) . . . . . . . . . . . . . . 47

2.5.2.1 ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.5.2.2 FLASH . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

2.5.2.3 RAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.5.2.4 Special Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.5.3 Microcontroller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

2.5.4 System Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

2.5.5 General Purpose Registers (GPR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

2.5.6 System Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

2.5.6.1 Wakeup Logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

2.5.6.2 Interval Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Preliminary Data Sheet 6 V0.9, 2008-04-28

PMA7110

2.5.6.3 Interval Timer Calibration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

2.5.7 Clock Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 70

2.5.7.1 2 kHz RC LP Oscillator (Low Power) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

2.5.7.2 12 MHz RC HF Oscillator (High Frequency) . . . . . . . . . . . . . . . . . . . . . . . . 71

2.5.7.3 Crystal Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

2.5.8 Interrupt Sources on the <Dev_NameShort1> . . . . . . . . . . . . . . . . . . . . . . . . . . 74

2.5.9 RF 315/434/868/915 MHz FSK/ASK Transmitter . . . . . . . . . . . . . . . . . . . . . . . 78

2.5.9.1 Phase Locked Loop PLL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

2.5.9.2 Power Amplifier PA . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

2.5.9.3 ASK Modulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

2.5.9.4 Voltage Controlled Oscillator (VCO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

2.5.9.5 Manchester/BiPhase Encoder with bit Rate Generator . . . . . . . . . . . . . . . . . . 81

2.5.10 LF Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.5.11 16Bit CRC (Cyclic Redundancy Check) Generator/Checker . . . . . . . . . . . . . . . 86

2.5.12 Pseudo Random Number Generator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

2.5.13 Timer Unit (Timer 0, Timer 1, Timer 2, Timer 3) . . . . . . . . . . . . . . . . . . . . . . . 90

2.5.13.1 Basic Timer Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

2.5.13.2 General Operation Description Timer 0 and Timer 1 . . . . . . . . . . . . . . . . . . . 93

2.5.13.3 Timer Modes for Timer 2 and Timer 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

2.5.14 General Purpose Input/Output (GPIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

2.5.14.1 Peripheral Port Basic Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

2.5.14.2 Spike Suppression on Input Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

2.5.14.3 External Wakeup on PP1-PP4 and PP6-PP9 . . . . . . . . . . . . . . . . . . . . . . . . 109

2.5.14.4 Alternative Port Functionality . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

2.5.15 I2C- Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

2.5.15.1 Slave mode sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

2.5.15.2 General call sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

2.5.15.3 Master mode sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

2.5.16 Serial Peripheral Interface SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

2.5.17 PROGRAMMING mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

2.5.17.1 FLASH Write Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

2.5.17.2 FLASH Erase . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 118

2.5.17.3 FLASH Check Erase Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 120

2.5.17.4 FLASH Read Line . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

2.5.17.5 FLASH Set Lockbyte 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

2.5.17.6 FLASH Set Lockbyte 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 121

2.5.17.7 Read Status . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 122

2.5.18 DEBUG mode Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

2.5.18.1 Debug Special Function Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

2.5.18.2 Debugging Facility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 123

2.5.18.3 Debugger Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 124

3 Reference . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

Preliminary Data Sheet 7 V0.9, 2008-04-28

PMA7110

3.1 Electrical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

3.1.1 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 126

3.1.2 Operating Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

3.1.3 Product Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

3.2 Reference SFR Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

3.3 Reference Documents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

4 Package Outlines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

Preliminary Data Sheet 8 V0.9, 2008-04-28

PMA7110

Product Description

1 Product Description

1.1 Overview

The PMA7110 is a low power wireless FSK/ASK Transmitter with embedded microcontroller, which offers a single chip solution for various industrial, consumer and automotive applications in frequency bands 315/434/868/915 MHz. With its highly integrated

mixed signal peripherals, PMA7110 requires only few external components. The operating voltage range is 1.9 - 3.6 V.

The PMA7110 contains

• 8051 based microcontroller

• Advanced power control system to minimize power consumption

• RF transmitter

•LF receiver

• Multifunctional interface for external Sensors and embedded temperature and

battery voltage sensor

Measurement via embedded temperature and voltage sensor, reading signal from

analog inputs (e.g. from external analog sensor) are performed under software control,

so that the microcontroller can format and prepare this data for the RF transmission.

An intelligent power control system enables the build of ultra low power applications by

using powersaving modes.

The integrated microcontroller is instruction set compatible to the standard 8051

processor. It is equipped with various peripherals (e.g. a hardware Manchester/BiPhase

Encoder/Decoder and CRC Generator/Checker) enabling an easy implementation of

customer-specific applications.

The low power consumption FSK/ASK Transmitter for 315/434/868/915 MHz frequency

bands contains a fully integrated VCO, a PLL synthesizer, an ASK/ FSK modulator and

an efficient power amplifier. Fine tuning of the center frequency can be done by an onchip capacitor bank.

To store the microcontroller application program code and its unique ID-Number, an onchip FLASH memory is integrated. Additional ROM storage is provided for the ROM

library functions covering standard tasks required by various applications.

Preliminary Data Sheet 9 V0.9, 2008-04-28

PMA7110

Product Description

1.2 Features

• Supply voltage range from 1.9 V up to 3.6 V

• Operating temperature range -40 to +85 °C

• Low supply current

• Temperature sensor

• Battery voltage measurement

• Integrated RF- transmitter for ISM band 315/434/868/915 MHz

• Selectable transmit power 5/8/10 dBm into 50 Ohm load

• Transmit data rates up to 32kbit/s or 64kchips/s in manchester code

• FSK/ASK modulation capability

• Frequency deviation up to 100 kHz in FSK mode

• Fully integrated VCO and PLL synthesizer

• Crystal oscillator tuning on chip

• LF receiver with input signal amplitude of min. 0.25 mVpp

• LF receiver data rate from 2000 bit up to 4000 bit (Manchester/BiPhase coded)

• 8051 instruction set compatible microcontroller (cycle-optimized)

• 6 kbyte Flash Code and 2x128 bytes flash data memory (for user-application like

EEPROM emulation)

• 12 kbyte ROM (for ROM library functions)

• 256 bytes RAM (128 bytes configurable to keep content in Power Down mode), 16

bytes XData memory (supplied in PowerDown)

2

C bus interface

•I

• SPI bus interface

• 10 free programmable bidirectional GPIO pins with on chip pull-up/down resistors

• 4 independent 16 bit timers

• 10bit ADC with 3 pair differential channels (e.g. as IO for external sensors)

• Wakeup from POWER DOWN state using the Interval Timer, the LF receiver or

external wakeup sources connected via a GPIO

• Manchester/BiPhase encoder and decoder

• Hardware CRC generator

• Pseudo Random Number Generator

• Watchdog timer

• on chip debugging via I

2

C interface

Note:In PMA7110 the Thermal Shout down function is not used.

1.3 Applications

• Remote control systems for industrial and consumer applications

• Security- and Alarm-systems

• Home automation systems

• Automatic meter reading

• Active Tagging

Preliminary Data Sheet 10 V0.9, 2008-04-28

2 Functional Description

7

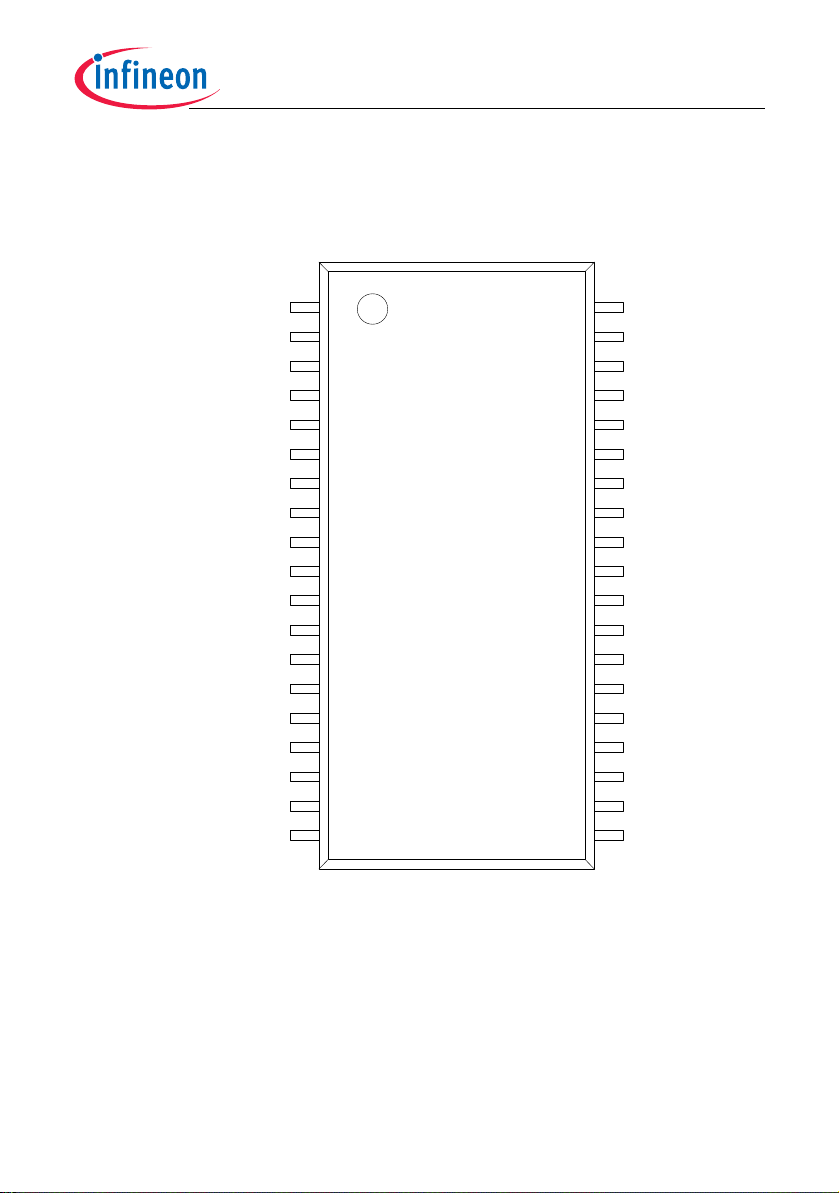

2.1 Pin Description

PMA7110

Functional Description

VDD (sens )

V1N (s ens)

VM1 (sens)

V1P (sens )

GNDB

GNDA

VBat

PGND

PA

GND

PP2/W U1/ TXDATAOut

PP1/W U0/ I2C _SDA/OPM ode2

PP0/I 2C_SC L/OPMode1

PP3/SPI _CS/WU2

PP4/W U3/ SPI_MISO

PP5/SPI _MOSI

PP6/W U4/ SPI_Clk

xRes et

PP7/Ext_Int1/WU5

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

PMA7110

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

V2N (sens)

VM2 (s ens)

V2P (sens)

RD (sens)

GNDC

VDDA

VDDD

VReg

LF

xLF

AMUX2

AMUX1

XGND

XTAL/SCLK

XTALCAP

TME

MSE

PP9/Ext_Int0/WU

PP8/WU6

Figure 1 Pin-out of PMA7110 in TSSOP38 package

Preliminary Data Sheet 11 V0.9, 2008-04-28

PMA7110

Functional Description

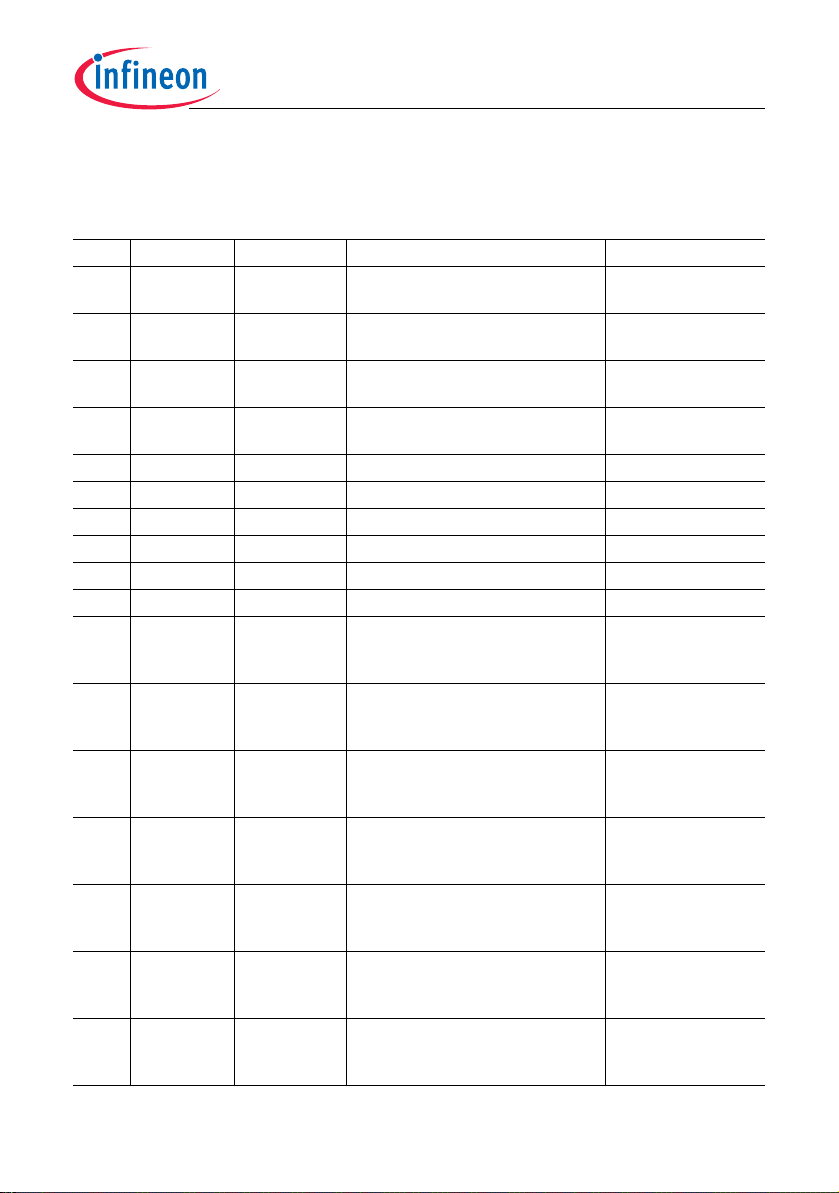

Table 1 Pin Description

Pin Name Type Description Comments

1 VDD(sens.) Supply Sensor positive supply same voltage as chip

2 V1N(sens.) Analog Channel1, negative sensor input output of wheatstone

3 VM1(sens.) Supply Sensor negative supply same voltage as chip

4 V1P(sens.) Analog Channel1, positive sensor input output of wheatstone

5 GNDB Supply Ground

6 GNDA Supply Ground

7 VBat Supply Battery supply voltage

8 PGND Supply RF transmitter ground

9 PA Analog RF transmitter output

10 GND Analog Ground

11 PP2/WU1/

TXDATAOut

12 PP1/WU0/

I2C_SDA/

OPMode2

13 PP0/

I2C_SCL/

OPMode1

14 PP3/SPI_CS/

WU2

15 PP4/WU3

/SPI_MISO

16 PP5/

SPI_MOSI

17 PP6/WU4

/SPI_Clk

Digital GPIO, External wakeup source,

Serial output of

Manchester/Biphase encoded data

Digital GPIO, External wakeup source, I2C

bus interface data, Select operation

mode

Digital GPIO, I2C bus interface clock,

Select operation mode

Digital GPIO, SPI bus interface chip select,

External wakeup source

Digital GPIO, SPI bus interface master in

slave out, External wakeup source

Digital GPIO, SPI bus interface master out

slave in

Digital GPIO, SPI bus interface clock,

External wakeup source

analog supply

bridge sensor

GND

bridge sensor

internal

pullup/pulldown

switchable

internal

pullup/pulldown

switchable

internal

pullup/pulldown

switchable

internal

pullup/pulldown

switchable

internal

pullup/pulldown

switchable

internal

pullup/pulldown

switchable

internal

pullup/pulldown

switchable

Preliminary Data Sheet 12 V0.9, 2008-04-28

PMA7110

Functional Description

Table 1 Pin Description

Pin Name Type Description Comments

18 xReset Digital External reset low active

19 PP7/WU5

/Ext_Int1

20 PP8/WU6 Digital GPIO, External wakeup source internal

21 PP9/WU7

/Ext_Int1

22 MSE Digital Mode select enable high active, set to

23 TME Digital Test mode enable high active, set to

24 XTALCAP Analog Crystal oscillator load capacitance

25 XTAL/SCLK Analog Crystal oscillator input, External

26 XGND Supply Crystal oscillator ground

27 AMUX1 Analog additional differential ADC standard

28 AMUX2 Analog additional differential ADC standard

29 XLF Analog Differential LF receiver Input2

30 LF Analog Differential LF receiver Input1

31 VReg Supply Internal voltage regulator output connect to

32 VDDD Supply Digital supply

33 VDDA Supply Analog supply

34 GNDC Supply Ground

35 RD(sens.) Analog use only by having

Digital GPIO, External wakeup source internal

Digital GPIO, External wakeup source,

External Interrupt source

reference clock

input1 for external sensor

input2 for external sensor

pullup/pulldown

switchable

pullup/pulldown

switchable

internal

pullup/pulldown

switchable

GND in normal mode

GND in normal mode

connect to GND if not

connect to GND if not

decoupling capacitor

diagnostic resistor on

use

use

=100nF)

(C

BCAP

sensor bridge,

otherwise none

connection

Preliminary Data Sheet 13 V0.9, 2008-04-28

PMA7110

Functional Description

Table 1 Pin Description

Pin Name Type Description Comments

36 V2P(sens.) Analog Channel2, positive sensor input output of wheatstone

37 VM2(sens.) Supply Sensor negative supply same voltage as chip

38 V2N(sens.) Analog Channel2, negative sensor input output of wheatstone

bridge sensor

GND

bridge sensor

Preliminary Data Sheet 14 V0.9, 2008-04-28

PMA7110

Functional Description

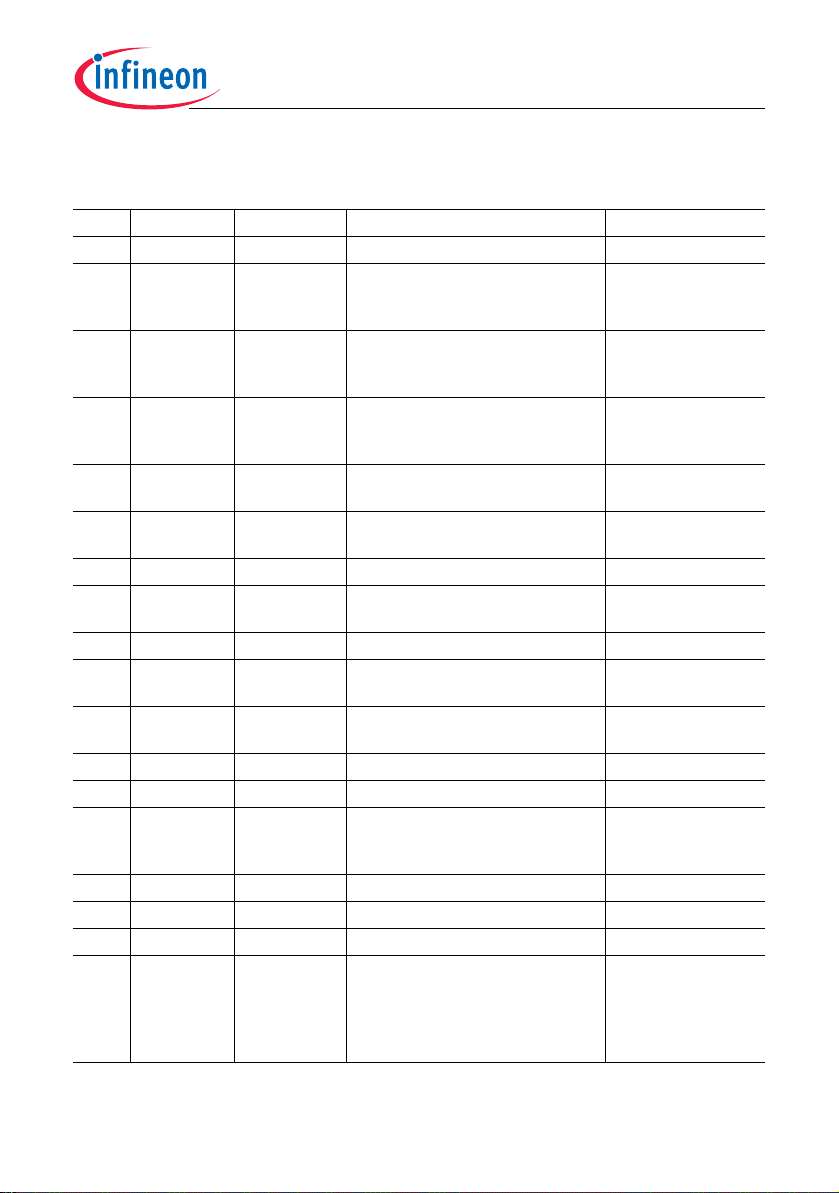

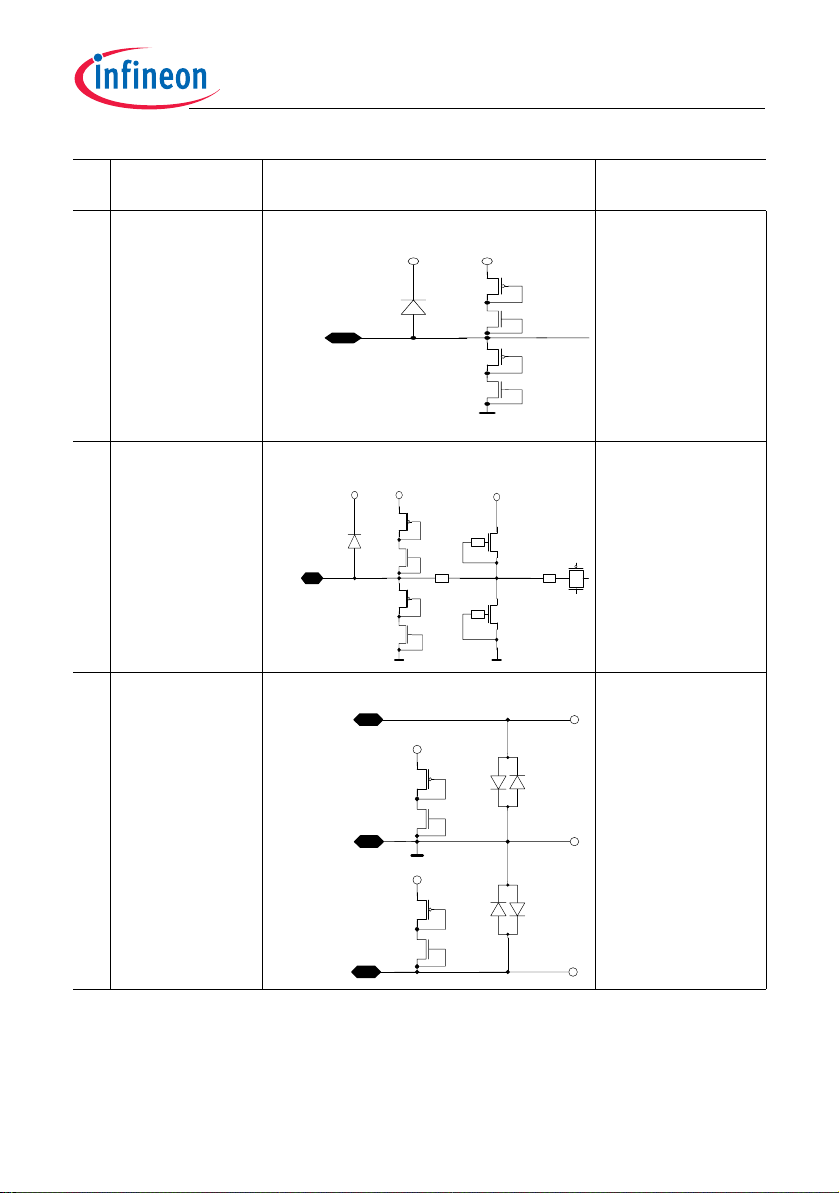

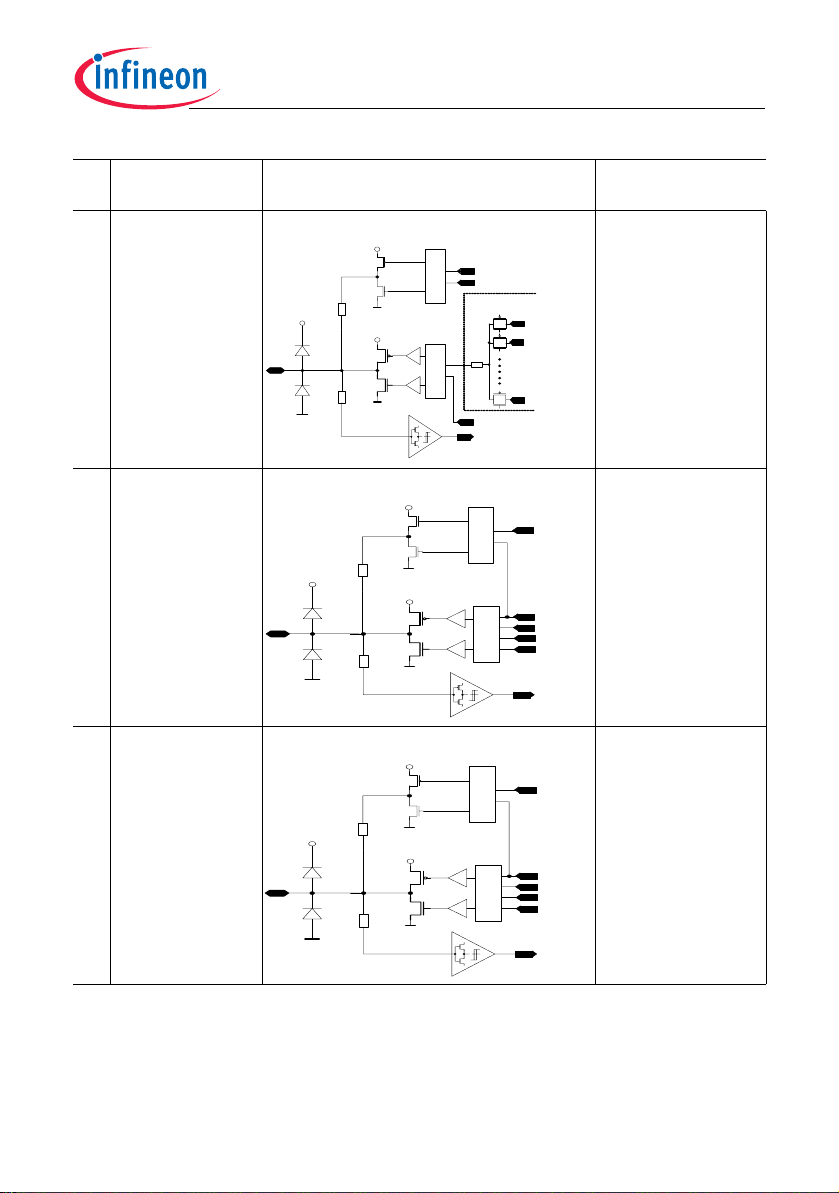

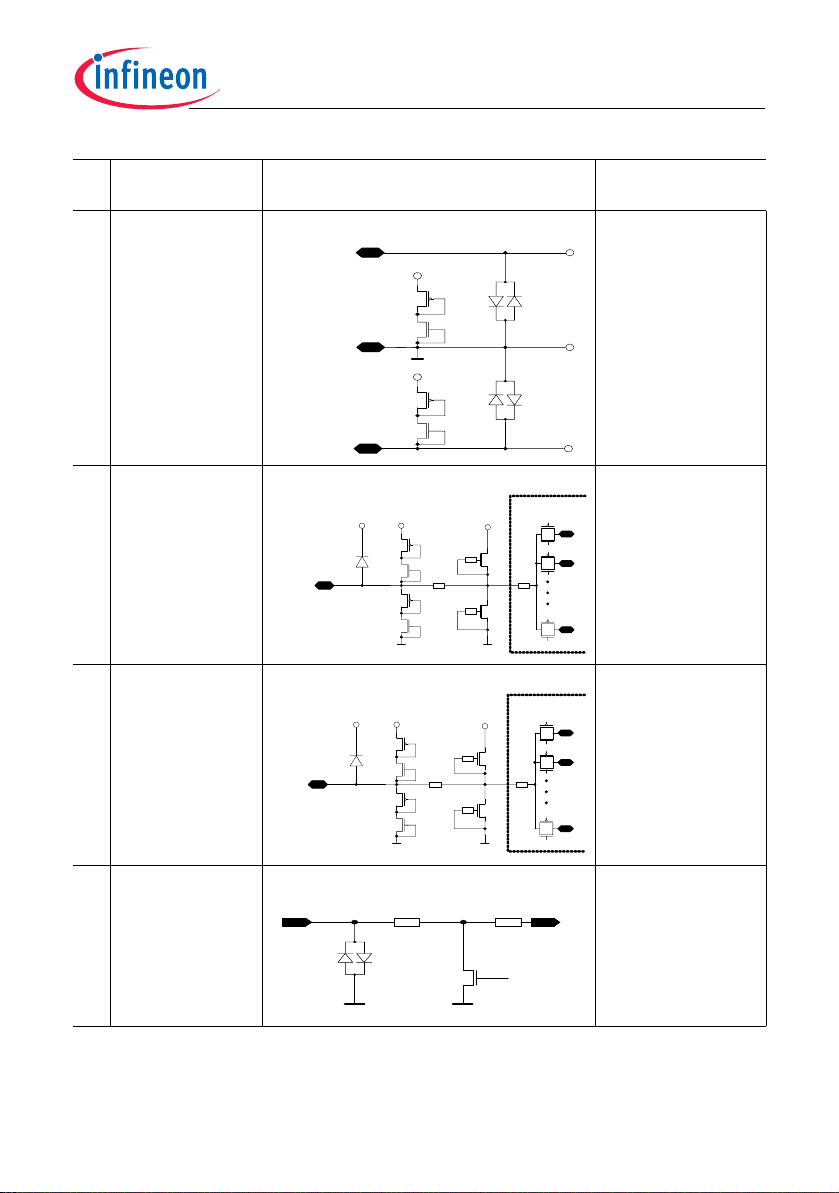

Table 2 Pin I/O equivalent schematics

Pin

PAD name Equivalent I/O Schematic Function

No.

1 VDD (Sens.) Sensor Positive

Volt ag e

Regulator

Supply

VBat

VReg

VDD (sens)

GND

GND

Swit ch

GND

2 V1N (Sens.) Channel 1

Negative Signal

2k

V1N

VDD A

500

Preliminary Data Sheet 15 V0.9, 2008-04-28

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

3 VM1 (Sens.) Channel 1

VDD A

VM1

GND

Negative Supply

4 V1P (Sens.) Channel 1

VDD A

Positive Signal

PMA7110

V1P

500

2k

5 GNDB Ground

PGND

GNDB

XGND

Preliminary Data Sheet 16 V0.9, 2008-04-28

PMA7110

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

6 GNDA

PGND

GNDA

XGND

7 VBat Power supply

VBat

voltage regulators

Volta ge

Regulator

VReg

8PGND

double bond

PGND

GND

XGND

Power amplifier

ground

Preliminary Data Sheet 17 V0.9, 2008-04-28

PMA7110

t

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

9 PA Power amplifier

10 GND

PA

PROGRAM7V

10

PGND PGND

100

output stage

11 PP2/WU1

/TXDATAOut

PP2

VBat

VBat

Pullup

Pulldow n

Tristate

GND

250k

1.8 ... 3.6V

VBat

Data

Tristate

500

GND

AMUX3 TG

Combinatorial

VBat

GND

PPS2

PPO2

Core

DMUX1

2k

Logic

PPD2

TXDATA

RfTXPEn

Core

AMUX3

2k

analog

signals

PPI2

GPIO port

WU1

Serial output of

Manchester/Biphase

encoded data

PPO2

DMUX2

tmd1_xclkdiv

tmd1_wucde

tmd1_lfraw

tmd1_clk_cpu

tmd1_pll_fc

PPO2

0

1

7

Preliminary Data Sheet 18 V0.9, 2008-04-28

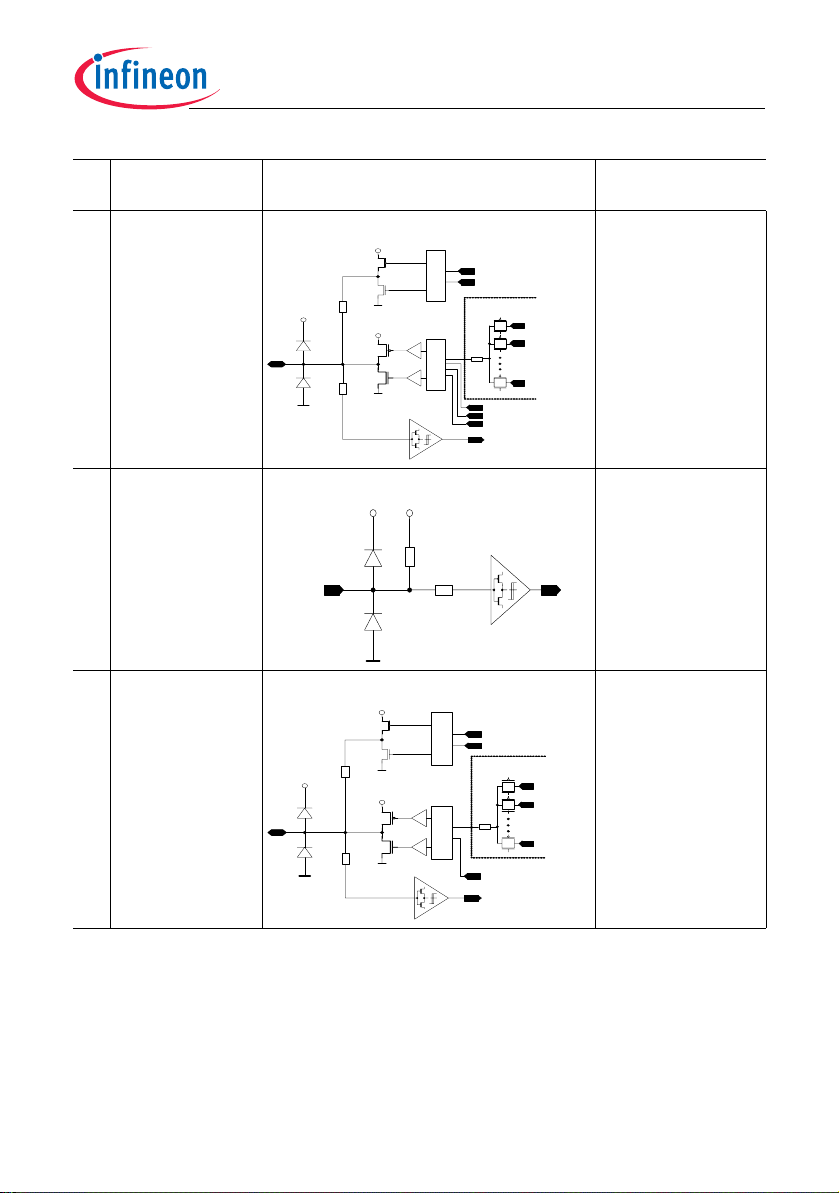

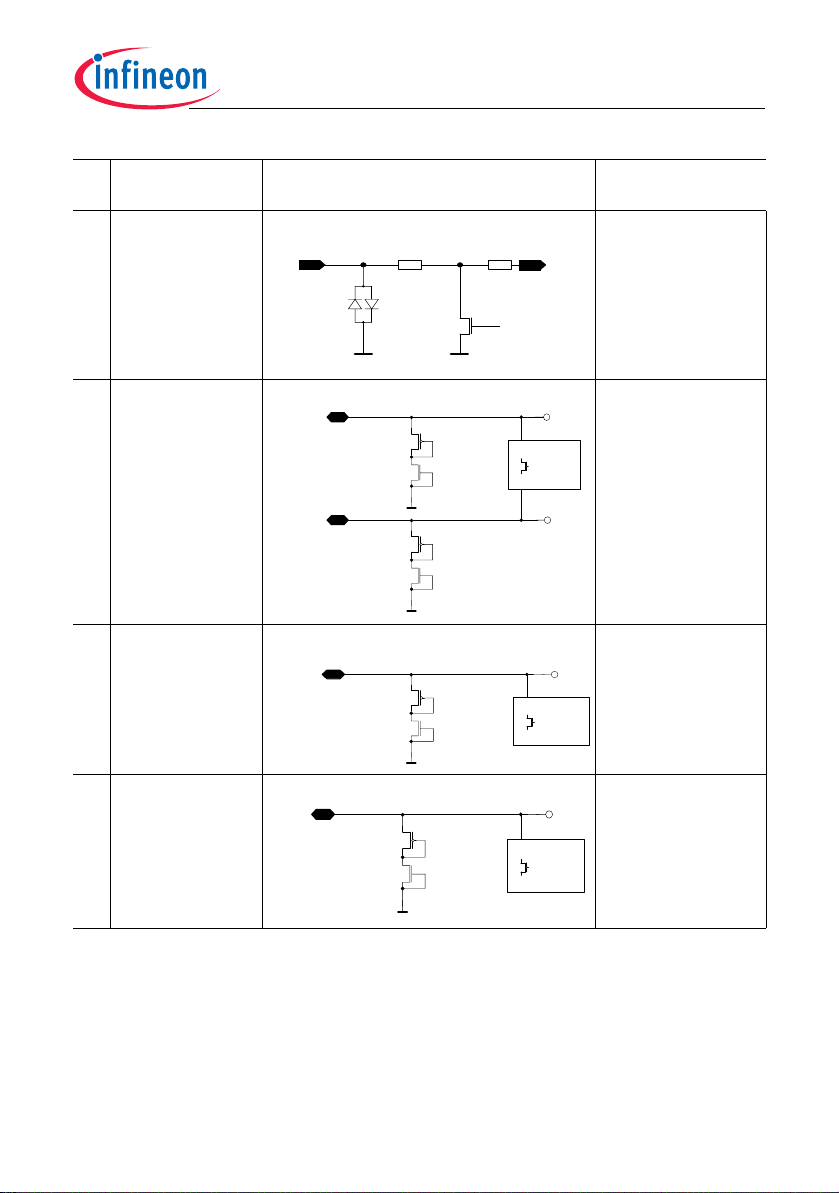

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

12 PP1/

WU0/I2C_SDA

/OPMode2

VBat

VBat

Pullup

Pulldown

Trist ate

Combinatorial

GND

50k

PPS1

Logic

PMA7110

GPIO port

WU0

I2C_SDA

OPMode2

13 PP0/I2C_SCL

/OPMode1

PP1

PP0

VBat

Data

Data

50k

500

500

VBat

VBat

VBat

GND

GND

Data

Trist ate

Pullup

Pulldow n

Tri stat e

GND

Data

Tristate

PPO1

PPD1

I2CD

Logic

Combinatorial

I2CEn

PPI1

GPIO port

I2C_SCL

OPMode1

PPS0

Logic

Combinatorial

PPO0

PPD0

I2CClk

Logic

Combinatorial

I2CEn

PPI0

Preliminary Data Sheet 19 V0.9, 2008-04-28

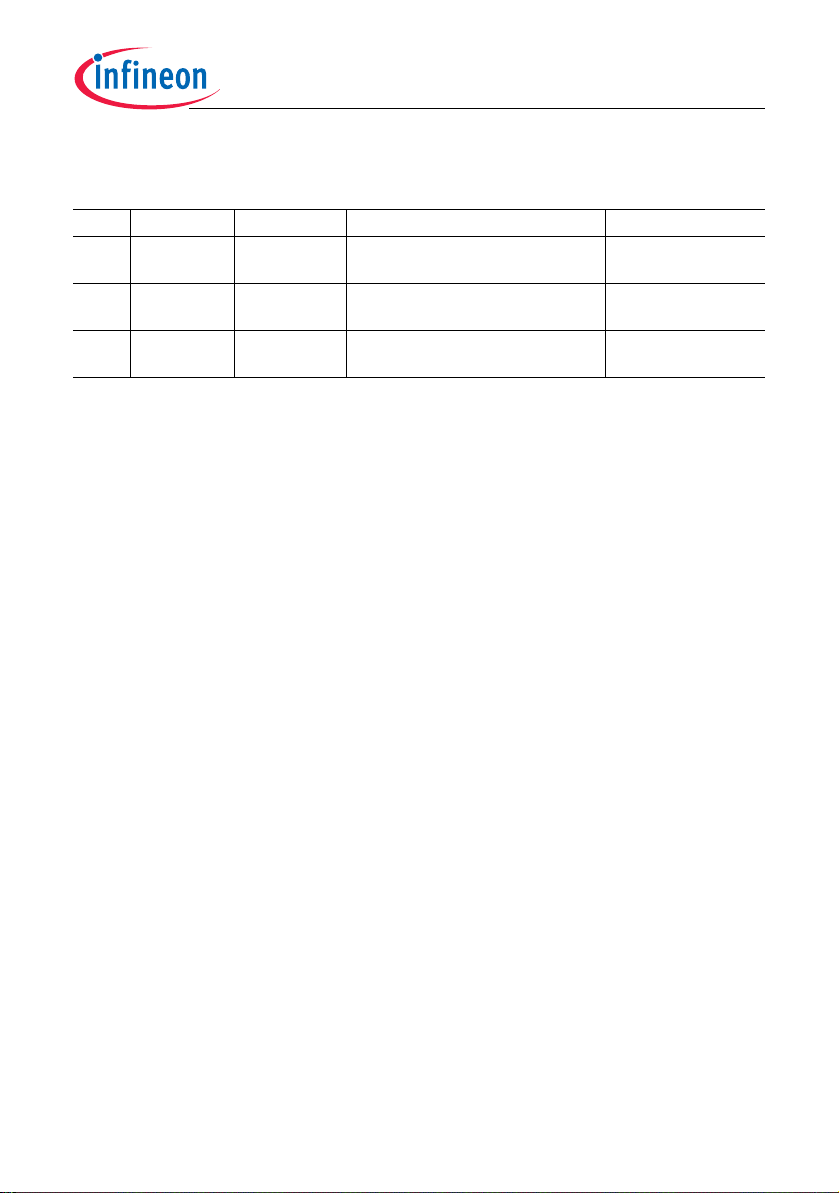

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

14 PP3/SPI_CS

/WU2

PP3

VBat

Pullup

Pulldown

Trista te

GND

250k

VBat

Data

Data

Trista te

500

GND

PPS3

Logic

PPO3

Comb i n at or i al

Core

DMUX2

PPO3

DMUX4

DMUX3

2k

tmd2_wucdet

Logi c

Combinatorial

tmd2_lfraw

tmd2_bitbounddet

tmd2_decerr

PPO3

PPD3

PPI3

PMA7110

GPIO port

WU2

SPI_CS

15 PP4/WU3

/SPI_MISO

VBat

PP4

Data

16 PP5/SPI_MOSI GPIO port

VBat

PP5

Data

VBat

Pullup

Pulldown

Trist ate

GND

50k

VBat

Trist ate

500

GND

VBat

Pullup

Pulldown

Tristat e

GND

50k

VBat

Tristate

500

GND

Data

Data

Logic

Combinat ori al

Logic

Combinator i al

Logic

Combinat ori al

Logic

Combinator i al

PPS4

PPO4

PPD4

SPI_MISO

SPIEn

PPI4

PPS5

PPO5

PPD5

SPI_MOSI

SPIEn

PPI5

GPIO port

WU3

SPI_MISO

SPI_MOSI

Preliminary Data Sheet 20 V0.9, 2008-04-28

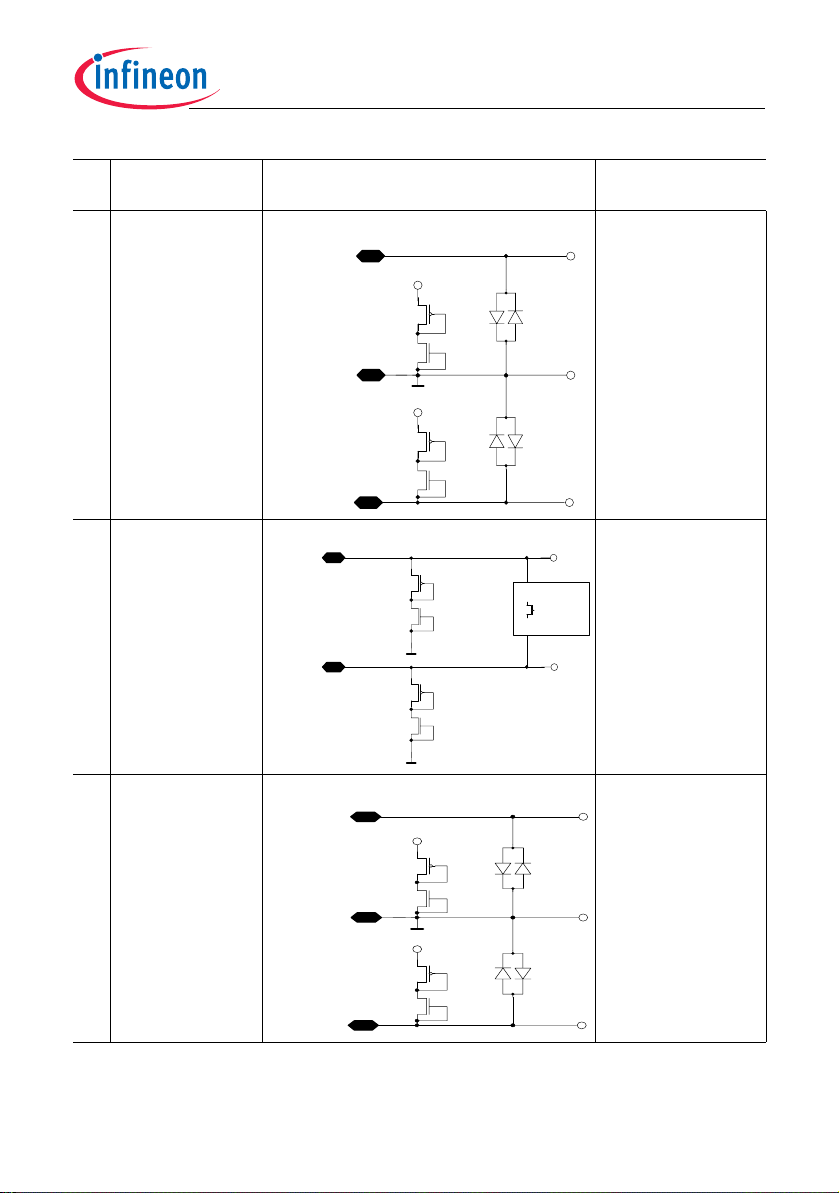

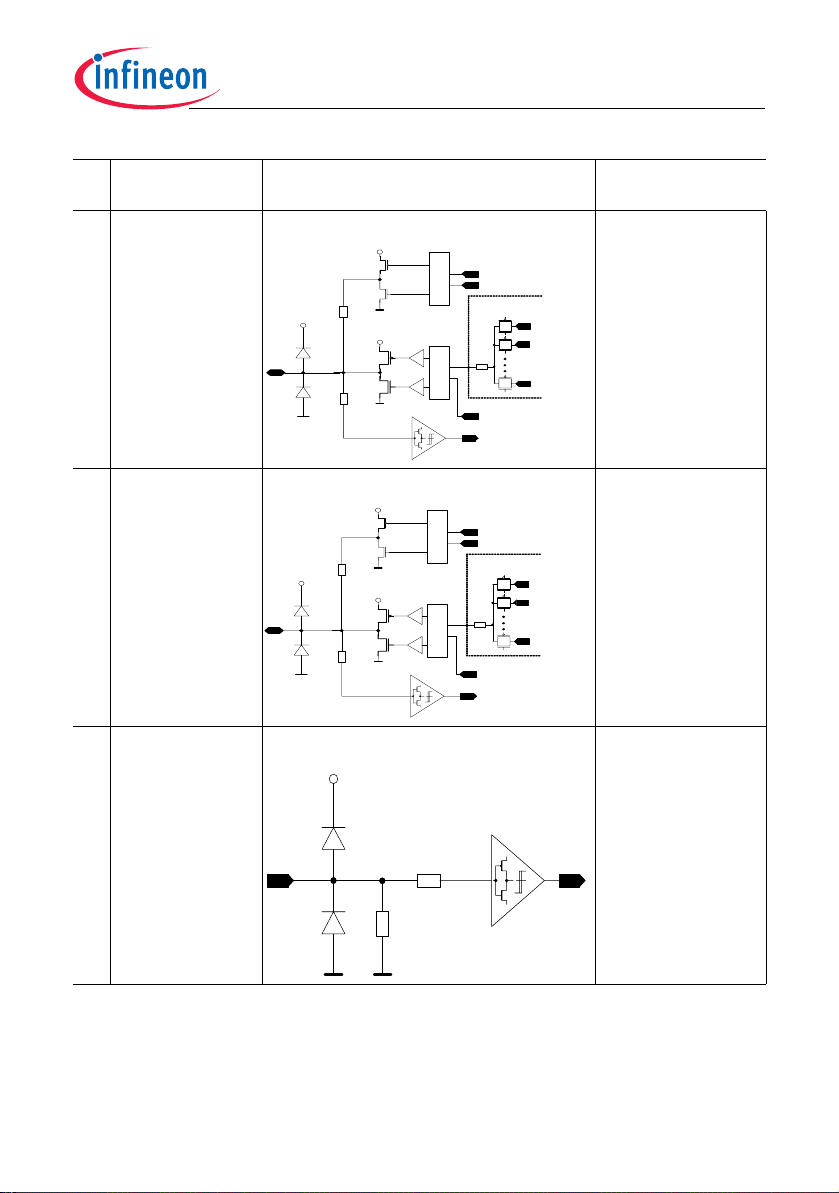

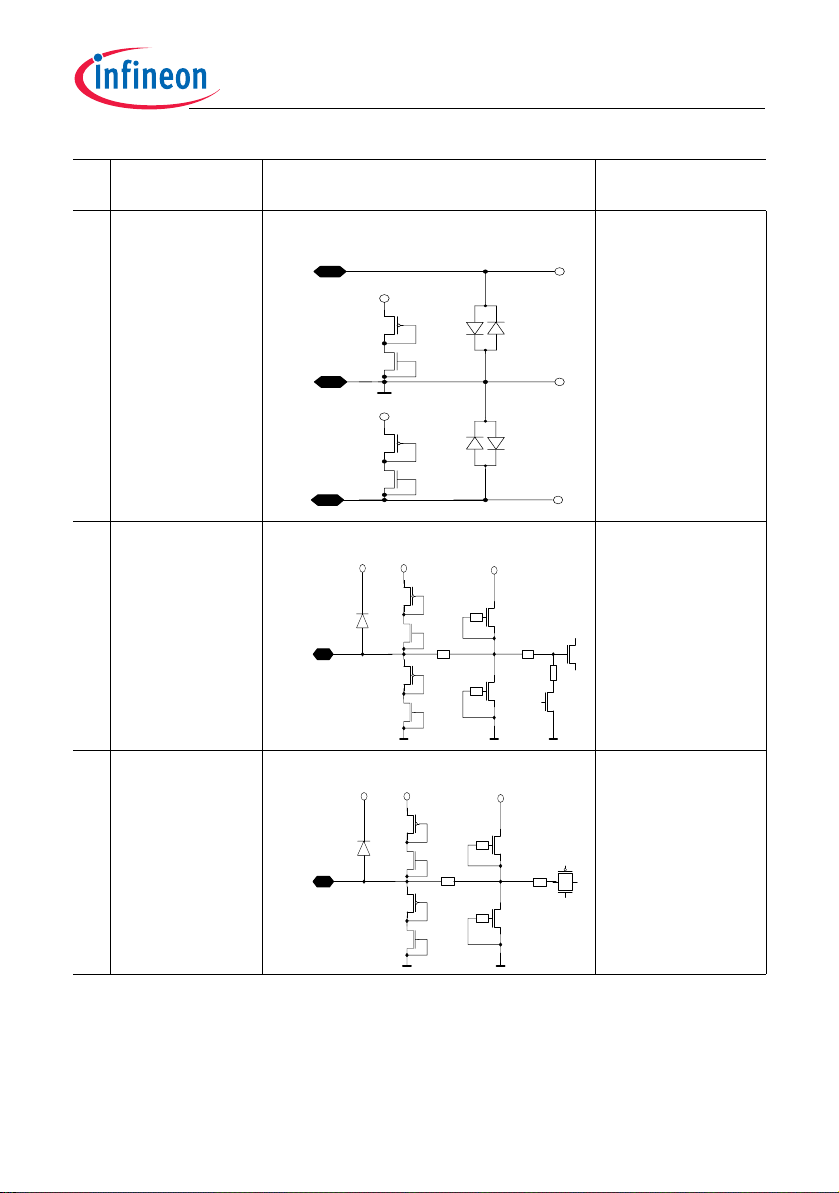

Functional Description

t

Pin

PAD name Equivalent I/O Schematic Function

No.

17 PP6/WU4

/SPI_Clk

PP6

VBat

Pullup

Pulldown

Tristate

GND

50k

VBat

Data

Data

Tristate

500

GND

PPS6

Logic

PPO6

Combinatorial

Core

DMUX3

PPO6

DMUX5

2k

PPD6

SPI_Clk

SPIEn

PPI6

tmd3_syncmat ch

PPO6

Logic

Combinatorial

GPIO port

WU4

SPI_Clk

18 xReset Reset input

VBat

50k

xRese t

500

Rese

PMA7110

19 PP7/WU5

/Ext_Int1

PP7

VBat

Pullup

Pulldown

Tristate

GND

50k

VBat

Data

Data

Tristate

500

GND

PPS7

Logic

PPO7

Comb i na to r i a l

Core

DMUX4

2k

Logi c

Combinator ial

PPD7

PPI7

GPIO port

WU5

Ext_Int1

PPO7

DMUX6

tmd4_chipvalid

PPO7

Preliminary Data Sheet 21 V0.9, 2008-04-28

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

20 PP8/WU6 GPIO port

PP8

VBat

Pullup

Pulldown

Tristate

GND

250k

VBat

Data

Data

Tristate

500

GND

PPS8

Logic

PPO8

Comb i na t or i a l

Core

DMUX5

HiRC Clock

tmd6_tr_so

2k

Logi c

Combinatorial

tmd5_flash_dig0

PPO8

PPD8

PPI8

WU6

PMA7110

21 PP9/WU7

/Ext_Int0

PP9

Data

250k

VBat

Pullup

Pulldown

Tristate

GND

VBat

Data

Tristate

500

GND

PPS9

Logic

PPO9

Combinatori al

Core

DMUX6

LoRC Clock

tmd5_chip

2k

Logi c

Combinato ri a l

tmd6_flash_dig1

PPO9

PPD9

PPI9

GPIO port

WU7

Ext_Int0

22 MSE Mode Select Enable

VBat

MSE

500

250k

MSE_i

Preliminary Data Sheet 22 V0.9, 2008-04-28

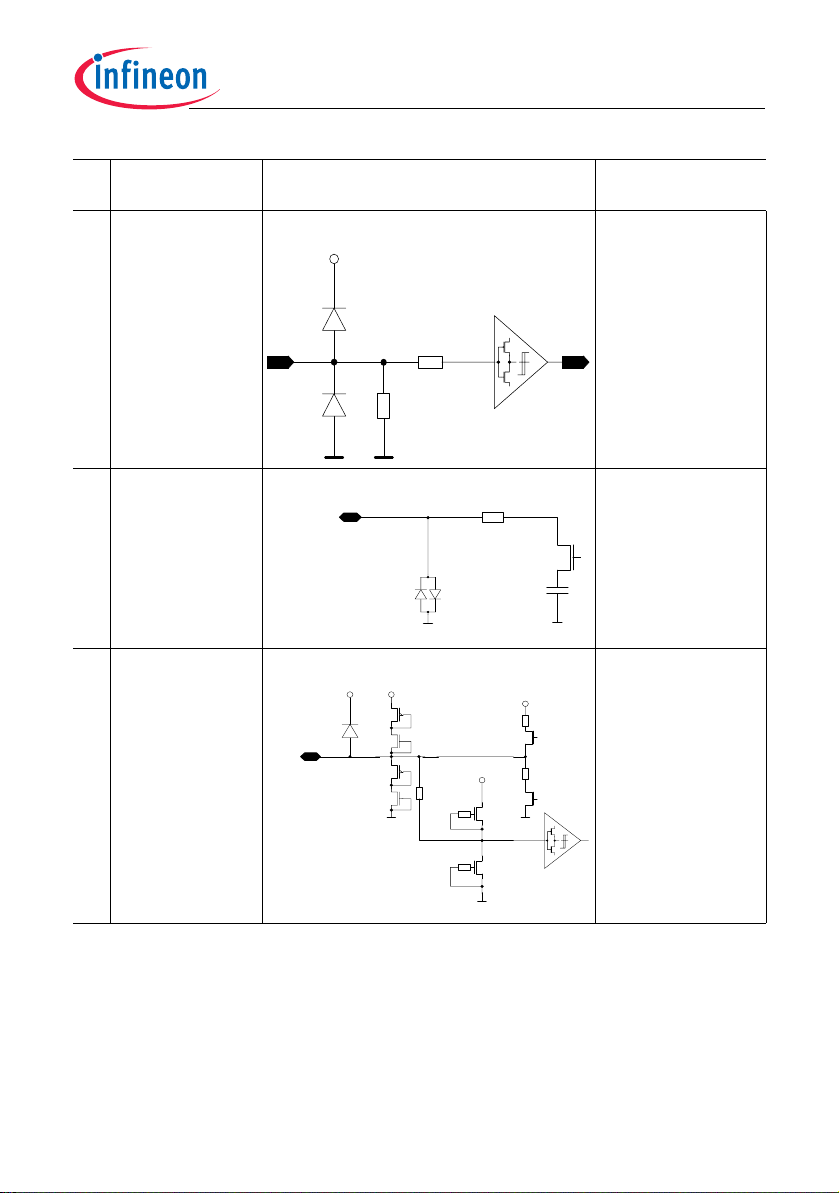

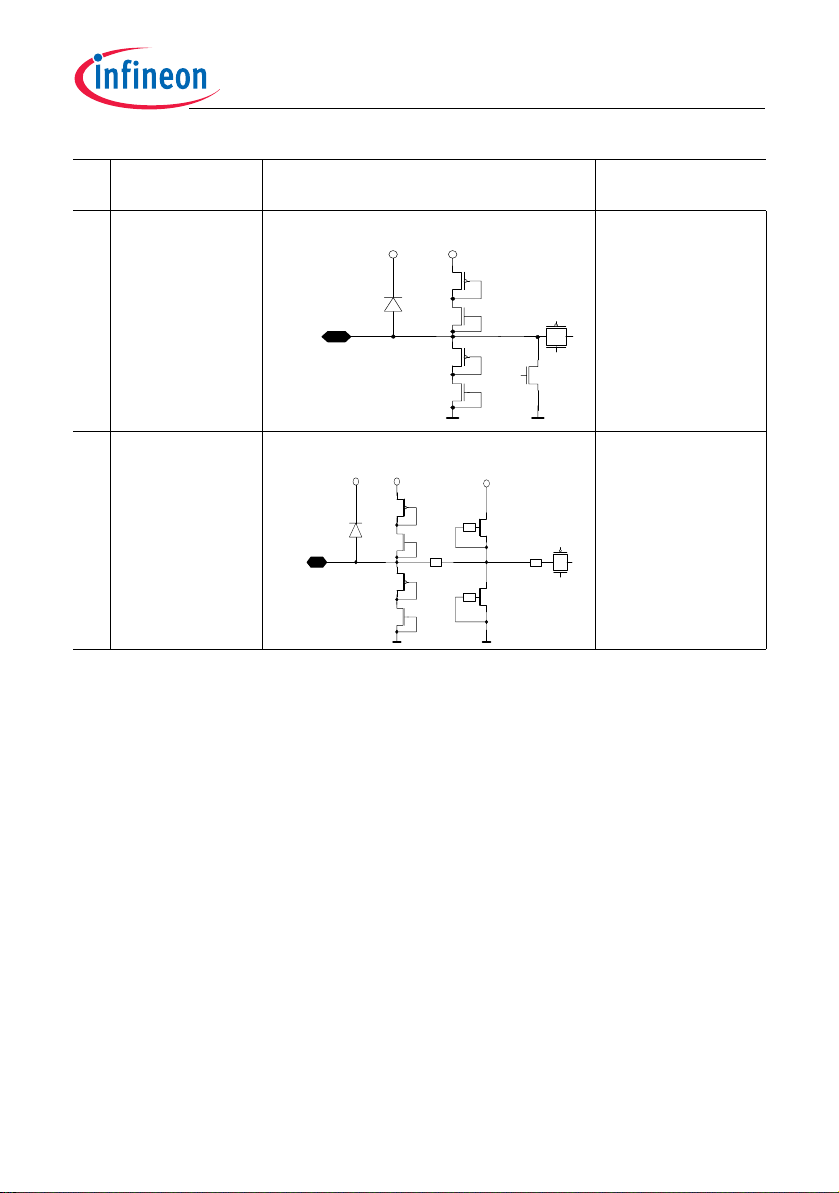

PMA7110

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

23 TME Test Mode Enable

VBat

TME

500

TME_i

250k

24 XTALCAP Crystal oscillator

XTALCAP

10

XGN D XGND

output

25 XTAL/SCLK Crystal oscillator

VDDD

input

SCLK

XTAL

500

XGND

XGND

≈ 0.9Vdc

Bypass

Preliminary Data Sheet 23 V0.9, 2008-04-28

PMA7110

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

26 XGND Crystal oscillator

PGND

GND

XGND

27 AMUX1

Core

2k

GND

AMUX1

VDDA

500

GND

28 AMUX2 Additional

Core

2k

AMUX2

VDDA

500

ground

Additional

differential ADC

standard input1 for

0

external sensor

Analog Testsignal

1

Port

7

differential ADC

standard input2 for

0

external sensor,

1

Analog Testsignal

Port

,

7

GND

GND

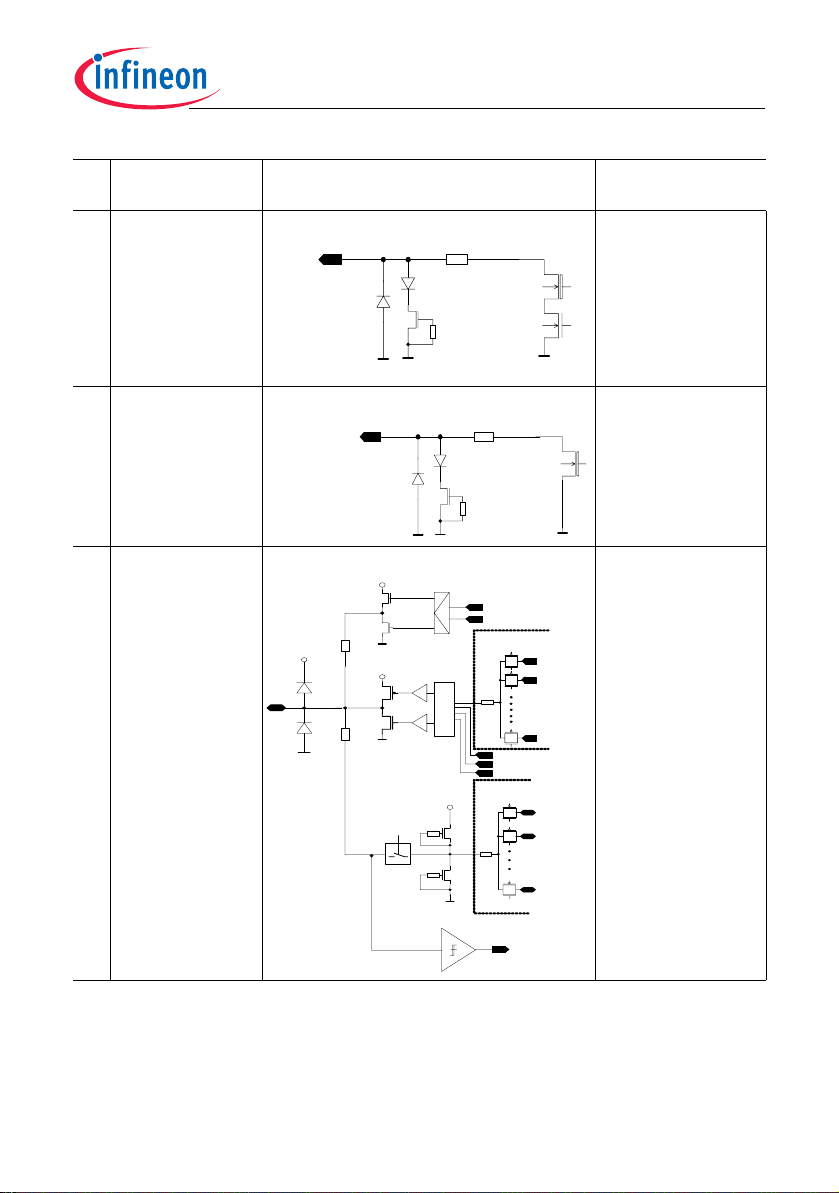

29 xLF Low Frequency

xLF

GND

50

xLF_i

15k

Preliminary Data Sheet 24 V0.9, 2008-04-28

Input

PMA7110

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

30 LF Low Frequency

Voltage

Regulator

Input

supply

LF

GND

50

15k

LF_i

31 VReg Regulated Power

VBat

VReg

GND

GND

32 VDDD Digital Supply

1.6 ...2.5 V

VDDD

Digi tal

core

GND

33 VDDA Analog Supply

VDDA

Ana log

core

GND

Preliminary Data Sheet 25 V0.9, 2008-04-28

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

34 GNDC Ground

PGND

GNDC

XGND

35 RD (sens.) Connect to

VDDA

diagnostic resister

on sensor bridge,

otherwise no

connection

RD

500

2k

100k

PMA7110

36 V2P (sens.) Channel 2

VDDA

V2P

500

Preliminary Data Sheet 26 V0.9, 2008-04-28

Positve Signal

2k

Functional Description

Pin

PAD name Equivalent I/O Schematic Function

No.

37 VM2 (sens.) Channel 2

VD DA

VM2

Negative Supply

38 V2N (sens.) Channel 2

VDDA

Negative Signal

PMA7110

V2N

500

2k

Preliminary Data Sheet 27 V0.9, 2008-04-28

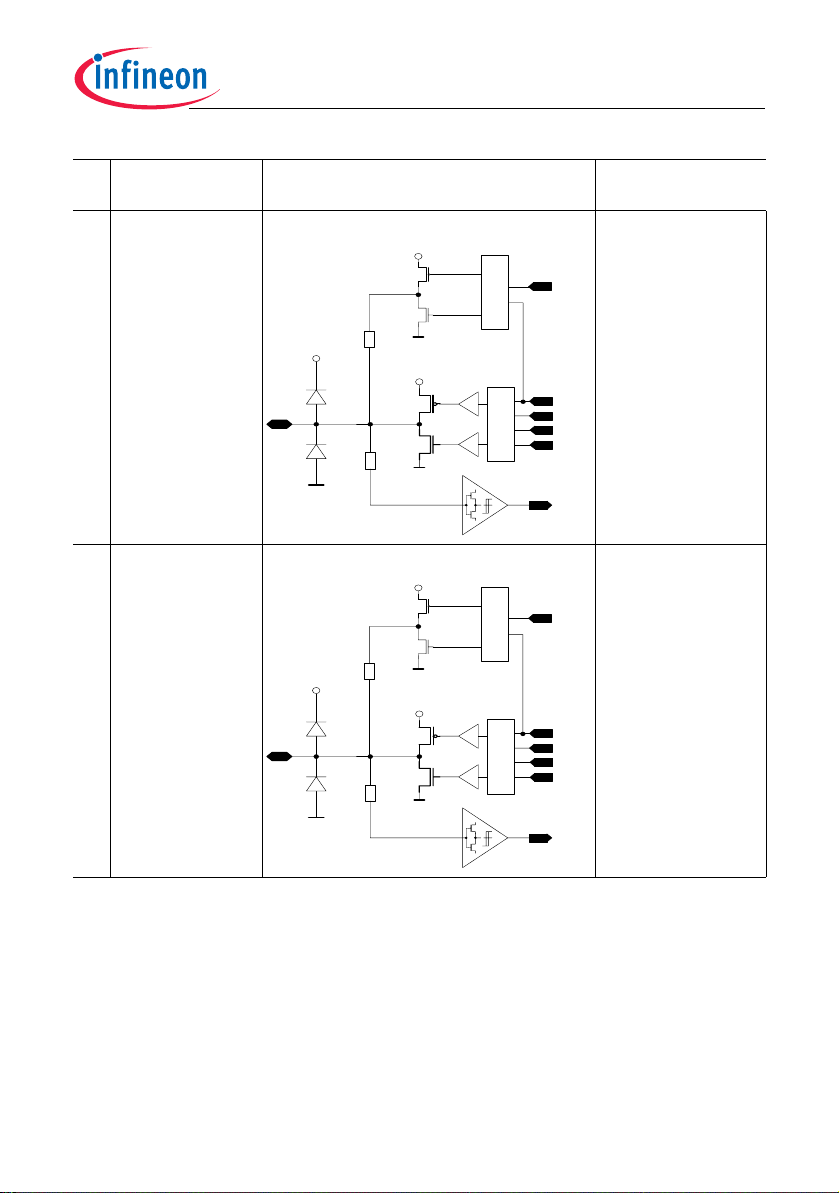

2.2 Functional Block Diagram

PMA7110

Functional Description

256 B

RAM

Diff . hig h sens itiv e inp ut1

12MHz RC

HF Os cillat or

V1P

V1N

Diff. high sensitiv e input2

V2P

V2N

Diff. standard input

AMUX1

AMUX2

Vmin

and

TMAX

detec tor

Voltage R egulat ors

Low

power

V-reg

Vbat

Vreg

Input multiplexer

B

ADC

T

Low

dropout

V-reg

VDDA

VD DD

Reference

volt age &

offset DAC

ADC state

machine

Bandgap and

PTAT

PRNG

GN D

ADC

Brownout

detect or

Interval timer

Figure 2 PMA7110 Block Diagram

6 kB

6 kB

Flash

Flash

Mic rocontroller

wit h 8051 core

Interrupt controller

Sys tem c ontrolle r

Reset

Cloc k cont roller

Timer calibration

2kHz RC

LP

Osci llator

12 kB

ROM

Wake U p

Test Controller

Power Mgm

Specia l

function

registers (SFR)

General Purpos e

Input/Output

(GPIO, I2C, SPI,

WU…)

RF transmitter

RF-PLL

Codes

modulat or

Manchester 101 Phase

LF rec eiver

Digi tal

Receiver

detec tor

CRC

generator

ASK

Carrier

Watch

dog

timer

...

Power

Amp

Crystal

Oscillator

FSK

modulat or

125kH z

Receiver

Timer

PP0

PP1

PP2

PP9

...

xReset

PA

PGND

XTAL

XTALCAP

XGND

LF

xLF

MSE TME

Preliminary Data Sheet 28 V0.9, 2008-04-28

Functional Description

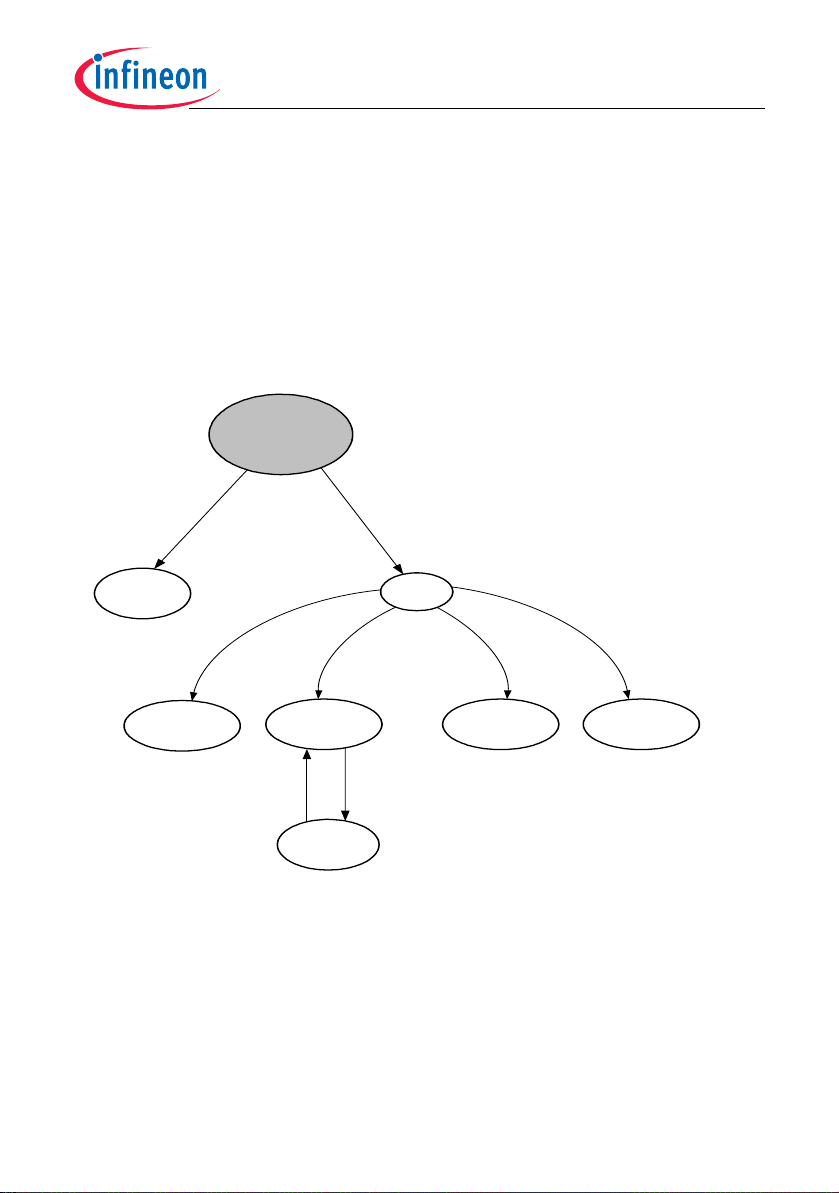

2.3 Operating Modes and States

The PMA7110 can be operated in four different operating modes.

•NORMALmode

•PROGRAMMINGmode

• DEBUG mode

• (internal production TEST mode)

2.3.1 Operating mode selection

SYSTEM RESET **

POR, xReset

Software reset

Brown-o ut event

PMA7110

TME = 1

SCAN Test

Mode

MSE = 1

PP0=0

PP1=1

Lockbyte II not set

PROGRA MMING

Mode

MSE = 1

PP0=0

PP1=0

TEST M ode 0 * DEBUG Mode

SFR CFG0.3=0

Functional

Test mode

TME = 0

Mode

Select

MSE = 1

PP0=1

PP1=0

Lockbyte II

not se t

NORMAL

L

o

S

c

F

k

R

b

y

C

t

e

F

G

I

I

0

n

.

3

o

*Note: If Lockbyte I and/or II is set, only a reduced

=

t

1

s

Test command set is ava ilable

e

t

**Note: Whenever TME is set to high the current

operation mode is left and SCAN Test mode is

entered, regardle ss if there was a reset event or not!

MSE = 0

or

MSE = 1

PP0=1|1|0

PP1=1|0|1

Lockbyte II set

or

MSE = 1

PP0=1

PP1=1

Lockbyte II

not set

Mode

Figure 3 Operating mode selection of the PMA7110 after Reset

The Mode Select is entered after the System Reset expires and SCAN Test mode is not

selected. The levels on the the I/O pins PP0 and PP1 are latched by the System

controller and read by the operating system to determine the mode of operation of the

device according to Table 3 "Operating mode selection after Reset" on Page 30.

Therefore also the status of MSE and Lockbyte II from the FLASH are checked. The

Preliminary Data Sheet 29 V0.9, 2008-04-28

PMA7110

Functional Description

MSE, PP0 and PP1 levels must not change after reset release during the whole t

MODE

period (see Figure 5 "Power On Reset - operating mode selection" on Page 32).

Table 3 Operating mode selection after Reset

TME MSE Lock

3.)

x x x x SCAN external Test

1

PP0 PP1 Operating

byte II

mode

Devicecontrol Hardware

restrictions

n.a.

machine

0 0 x x x NORMAL CPU executing

Flash write disabled

from 4000h

0 1 x 0 0 TEST TEST mode

None

handler

01not

0 1 set 0 1 NORMAL CPU executing

0 1 PROGRAMMING PROGRAM

set

None

mode handler

Flash write disabled

from 4000h

01not

0 1 set 1 0 NORMAL CPU executing

1 0 DEBUG DEBUG mode

set

Flash write disabled

handler

Flash write disabled

from 4000h

0 1 x 1 1 NORMAL CPU executing

Flash write disabled

from 4000h

1.) Flash protection is done by hardware. In these modes setting the SFR bits FCS.3 [PROG] and FCS.2 [ERASE]

is not possible.

2.) Flash programming and erasing is only possible via ROM Library functions.

3.) Whenever TME is set to high the current mode is left immediately and SCAN Test Mode is entered, regardless

if there is a reset or not.

2)

2.)

2.)

2.)

2.)

Preliminary Data Sheet 30 V0.9, 2008-04-28

PMA7110

e

Functional Description

.

MSE = 0

Mode

Select

or

MSE = 1

PP0=1|1|0

PP1=1|0|1

Lockb yte II set

or

MSE = 1

PP0=1

PP1=1

Lockb yte II

not set

WD

INIT

WD

WU

IFLG

IDLE

IDLE

RUN

RS

IRQRETI

PE

PDWN

Figure 4 NORMAL Mode - State transistion diagram

For low power consumption and safety reasons the PMA7110 supports different

operating states - RUN state, IDLE state and POWER DOWN mode and Thermal

shutdown state. The device operation in these states is described below.

Transitions between these states are either application software controlled or managed

automatically by the system controller.

- PDWN: Powerdown (CPU & Peripherrals stopped)

- IDLE: CPU clock stopped, peripherals are still running

States

TSHT - Thermal shutdown

PDWN - Powerdown

RUN - Run application

IDLE - CPU clock stopped

TE

TSHT

WU

Transitions

WU - Wakeup

PE - Powerdown enable

TE - Thermal shutdown enabl

WD - Watchdog

IFLG - Idle flag

RS - Resume

IRQ - Interrupt request

RETI- Return from interrupt

Preliminary Data Sheet 31 V0.9, 2008-04-28

Vreg

RESET

(internal)

PP0, PP1

V

V

PMA7110

Functional Description

THR

POR

t

POR

t

MODE

Figure 5 Power On Reset - operating mode selection

During the time t

, the levels of PP0, PP1 and MSE are read, and being determined

MODE

the operation mode of the device according to Table 3 "Operating mode selection

after Reset" on Page 30. The levels on these pins must be stable during the whole

period.

t

MODE

The PMA7110's Power On Reset circuit is activated if Vreg rises above V

internal blocks are held in Reset state until Vreg has risen above V

When this Reset state is released, a further time of t

on PP0, PP1 and MSE. After t

has elapsed, the device starts operation in the

MODE

is needed for reading the levels

MODE

THR

.

POR

. The

selected mode.

Note: See “Power On Reset” on Page 138 for details on Power On Reset

characteristics.

2.3.2 State Description

2.3.2.1 INIT State

This is a transient state which is entered when the settings of PP0, PP1, MSE, TSE and

the Lockbyte II lead to Normal Mode (please refer to Table 3 "Operating mode

selection after Reset" on Page 30). In this state, the SFRs which are not located in the

System controller get reset and the ROM routines initializes the system to its default

Preliminary Data Sheet 32 V0.9, 2008-04-28

PMA7110

Functional Description

values. Then the application Program in Flash is started at 4000h and the device enters

RUN state.

2.3.2.2 RUN State

In RUN state the CPU8051 executes programs stored in ROM or FLASH memory.

Peripherals are on or off according to the application program. The watchdog (WD) is

active and automatically cleared when entering RUN state on a Wakeup event. The CPU

clock frequency is selectable by software. All Wakeup events are ignored in RUN state

but the corresponding flags get set and can be read and cleared.

2.3.2.3 IDLE State

In IDLE state, the CPU8051 clock is disabled but Peripherals (Timers, ADC, RF-TX, SPI,

2

C Interface and Manchester/Biphase Coder) continues normal operation. If a resume

I

condition occurs the RUN state is reentered immediatelly. The watchdog (WD) is active

and reset automatically when entering IDLE state. All wakeups are ignored in IDLE state

but the corresponding flags are set if a wakeup occurs and can be evaluated once the

device returns to the RUN state.

In case of a Peripheral requests, an interrupt or an External Interrupt occurs the IDLE

state is left for RUN state, the Interrupt service routine is executed and on the next RETI

(return from interrupt) instruction the IDLE State is re-entered in case no Resume event

has occured in between.

Resume events:

The resume source can be identified by reading REF. Resume events may occur on

following events:

• RF transmitter buffer empty.

• RF transmission finished.

• LF receiver buffer full.

• Timer 2 underflow.

• A/D conversion finished.

• RC-LP-Oscillator calibration finished.

• Clock change from RC-HF-Oscillator to Crystal-Oscillator finished.

Interrupt requests:

Interrupts during IDLE state may be requested by embedded peripherals or external

events.

• External (Pin) Interrupt 0/1

• Timer 0/1/2/3

Preliminary Data Sheet 33 V0.9, 2008-04-28

PMA7110

Functional Description

• I2C Interface

• SPI Interface

•LF Receiver

•RF Encoder

2.3.2.4 POWER DOWN State

In POWER DOWN state the CPU8051 and its peripherals are powered down. The

system controller, its SFRs, the XData memory and optional the lower 128 byte internal

RAM are kept powered. The LF receiver will be switched on periodically if the LF on/off

timer is enabled. Wakeup flags are cleared automatically when going to POWER DOWN

or THERMAL SHUTDOWN.

Wakeup Events:

A wakeup event occurs when a peripheral or external source causes the system to

power up again. The wakeup source can be identified by reading SFRs WUF and

ExtWUF. Wakeup Events may occur on following events:

• At least one of the External Wakeup Pins changed its state to the configured one

• Interval Timer underflow occured

• LF receiver carrier detected

• LF receiver pattern matched

• LF receiver sync matched

• Watchdog timer elapsed

2.3.2.5 THERMAL SHUTDOWN state

In THERMAL SHUTDOWN state, only the TMAX circuit can provide a wakeup event. All

other wakeup sources are disabled. The device will remain in this state until the

temperature falls below the T

Page 41 for details).

Preliminary Data Sheet 34 V0.9, 2008-04-28

threshold (see “Functional Block Description” on

REL

PMA7110

Functional Description

2.3.2.6 State Transitions

With reference to Figure 4 "NORMAL Mode - State transistion diagram" on Page 31,

the following state transitions can occur:

Table 4 State Transitions in NORMAL mode

State transition Description

RUN state

=> IDLE state (IFLG)

IDLE state

=> RUN state (RS, IRQ)

IDLE state

=> INIT state (WD)

RUN state

=> INIT state (WD)

RUN state

=> THERMAL SHUDOWN state

(TE)

RUN state

=> POWER DOWN state

(PDWN)

The application program can set SFR bit CFG0.5[IDLE]1) to

enter IDLE state. Note that the next opcode should be a NOP

instruction.

(see Table 11 "SFR Address F8

Register 0" on Page 58)

Note: If no peripheral that can create a RESUME event is

active, IDLE state will not be entered and the application will

continue operation.

RS: A peripheral unit (Timer 2, ADC, RF transmitter,

LF receiver, System Clock source switch) creates a resume

event. The application continues with the instruction after the

Idle bit setting (see Table 20 "SFR Address D1

Resume Event Flag Register" on Page 67).

IRQ: An interrupt occurs. This interrupt allows the immediate

execution of the interrupt service routine. With the return from

interrupt instruction the device returns to IDLE state if no

resume event has been generated in between.

Overflow of the watchdog timer. The application will restart by

initialization of the SFRs that are located outside the SFR

Container. No Mode selection is possible, the Normal Mode is

not left. The watchdog wakeup may be identified by Table 18

"SFR Address C0H: WUF - Wakeup Flag Register" on

Page 65

The application should enter Thermal Shutdown state

whenever it detects that the specified operating temperature

maximum of 125°C has been overreached to avoid

malfunction of the device. This is done by setting the

CFG0.6 [TSHDWN]. Alternatively this can be done via ROM

library function.

Note: If the temperature is below the TMAX threshold the

device immediately generates a WU event and re-initializes

the system

Entering this state is always software controlled by setting

CFG0.7[PDWN]. The application program can call a

ROM Library function to enter POWER DOWN state

whenever needed.

: CFG0 - Configuration

H

: REF -

H

Preliminary Data Sheet 35 V0.9, 2008-04-28

PMA7110

Functional Description

State transition Description

THERMAL SHUTDOWN state

=> RUN state (WU)

POWERDOWNstate

=> RUN state (WU)

INIT state

=> RUN state

1)1) Note: It is mandatory that the instruction setting the CFG0.5[IDLE] is followed by a NOP instruction.

The TMAX circuit generates a wakeup event when the

temperature falls below TMAX threshold.

A wakeup event will restart the application and set the SFR

WUF resp. ExtWUF accordingly. The Watchdog timer is reinitialized (see Table 19 "SFR Address F1H: ExtWUF -

Wakeup Flag Register 2" on Page 65). Wakeup duration

from POWER DOWN mode to RUN state typically lasts 1410

µs. The time is the sum for the power supply to get stable

(100µs), the startup time of the oscillator (1150 µs) and the

time for the operating system to get initialized

(160µs @12MHz CPU8051 clock).

This state change is initiated automatically by the system

controller as soon as INIT state is finished.

Preliminary Data Sheet 36 V0.9, 2008-04-28

PMA7110

Functional Description

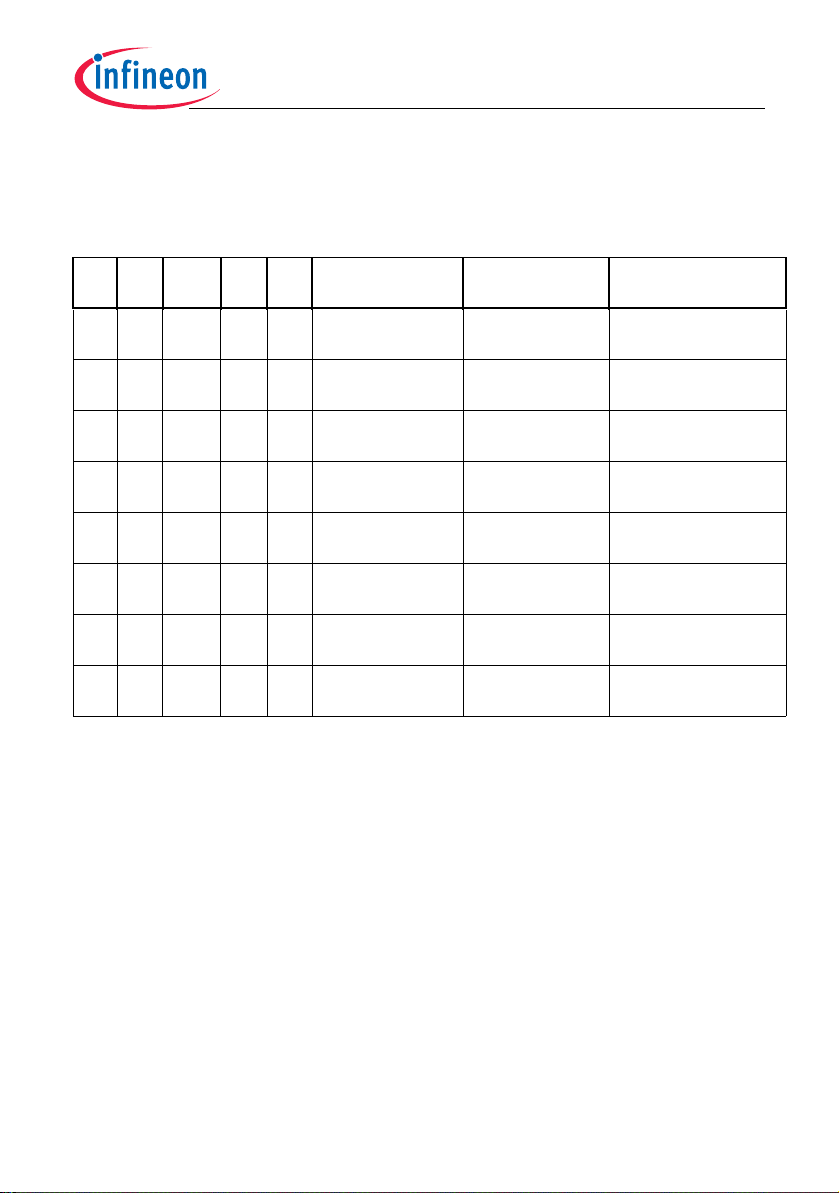

2.3.2.7 Status of PMA7110 Blocks in Different States

Depending of the actual state in NORMAL mode the internal blocks of the PMA7110 are

active, inactive or have no supply to reduce power consumption. The next table gives an

overview over the different blocks in the different device states.

Table 5 Status of important PMA7110 blocks in different states

Peripheral unit RUN state IDLE state POWER DOWN

state

Power on reset active active active active

Brown-out detector active active inactive

power down

Power supply - Low

drop voltage regulator

Low power voltage

supply

System controller active active active active

Wakeup Logic active active active active

CPU8051 active inactive no supply no supply

Non-volatile SFRs

(System Controller)

Peripheral core

SFR’s

Manchester/Biphase

Coder, Timer

Pheripheral modules CRC, MFLSR

Peripheral modules

-I2C, SPI, ADC

Watchdog active active no supply no supply

active active inactive

power down

(Remark:

can be enabled

by LF-RX)

active active active active

active inactive

content not

lost

active inactive

content not

lost

software

selectable

software

selectable

software

selectable

software

selectable

inactive no supply no supply

software

selectable

inactive

content not lost

no supply content lost

no supply no supply

no supply no supply

THERMAL

SHUTDOWN state

inactive

power down

inactive

power down

inactive

content not lost

no supply - content

lost

Preliminary Data Sheet 37 V0.9, 2008-04-28

PMA7110

Functional Description

Peripheral unit RUN state IDLE state POWER DOWN

state

RAM Lower 128Bytes active inactive

content not

lost

selectable

power down

(content lost) or

inactive

THERMAL

SHUTDOWN state

selectable power

down (content lost)

or inactive (content

not lost)

(content not lost)

RAM Upper 128Bytes active inactive

content not

no supply content lost

no supply - content

lost

lost

XData 16 bytes active inactive

content not

inactive

content not lost

inactive content not

lost

lost

FLASH memory active inactive

content not

no supply

content not lost

no supply

content not lost

lost

ROM active inactive no supply

content not lost

Crystal oscillator software

selectable

software

selectable

inactive

power down

no supply

content not lost

inactive

power down

2kHz RC-Oscillator active active active inactive

power down

12MHz

RC-HF-Oscillator

software

selectable

software

selectable

power down

(Remark:

power down

can be enabled

by LF-RX)

Interval timer active active active inactive

LF Receiver software

selectable

RF Transmitter software

selectable

software

selectable

software

selectable

software

selectable

inactive

power down

inactive

power down

inactive

power down

Preliminary Data Sheet 38 V0.9, 2008-04-28

PMA7110

Functional Description

Peripheral unit RUN state IDLE state POWER DOWN

state

Vmin Detector software

selectable

software

selectable

no supply inactive

THERMAL

SHUTDOWN state

power down

Note: active: block is powered, is active and keeps its register contents. Power

consumption is high

inactive: block is powered, cannot be used, but keeps its register contents.

Power consumtion is low

no supply: block is not powered, connot be used and all register content is lost.

Power consumption is zero

Preliminary Data Sheet 39 V0.9, 2008-04-28

PMA7110

Functional Description

2.4 Fault protection

The PMA7110 features multiple fault protections which prevent the application from

unexpected behavior and deadlocks. This chapter gives a brief overview of the available

fault protections. Detailed explanation of the usage can be found later in this document

and in [1] “Reference SFR Registers” on Page 144.

2.4.1 Watchdog Timer

For operation security a watchdog timer is available to avoid application deadlocks. The

watchdog timer must be reset periodically by the microcontroller, otherwise the timer

generates a software reset and forces a restart of PMA7110 program execution.

The watchdog timer duration is fixed to nominal 1 second. The accuracy depends on the

accuracy of the 2 kHz RC LP Oscillator which is used to clock the watchdog timer.

Setting SFR bit CFG2.1[WDRES] resets the watchdog timer (see Table 13 "SFR

Address D8

: CFG2 - Configuration Register 2" on Page 60).

H

2.4.2 VMIN Detector

This circuit will detect if the supply voltage is below the minimum value required to

guarantee the measurement accuracy. The ROM library functions which perform

measurements will return the VMIN status in a statusbyte with the measurement result.

2.4.3 FLASH Memory Checksum

A CRC checksum is stored in the FLASH memory, and can be recalculated and checked

by the application program for verification of program code if needed.

Flash bit FCSP.7[ECCErr]: If a single bit error in the Flash memory occurs it is corrected

by the Flash internal Error Correction Coder, as an indication the FCSP.7[ECCErr] bit is

set. (see Table 101 "SFR Address E9

: FCSP- Flash Control Register - Sector

H

Protection Control" on Page 146 in “Reference SFR Registers” on Page 144)

2.4.4 ADC Measurement Overflow & Underflow

The ROM Library functions which perform measurements will return the over/underflow

status in a statusbyte with the measurement result.

2.4.5 TMAX Detector

The TMAX detector is used to wakeup the PMA7110 from

THERMAL SHUTDOWN state if the ambient temperature falls below the trigger level

T

.

REL

Entering THERMAL SHUTDOWN state can be initiated by a ROM Library function

described in [1] “Reference Documents” on Page 157.

Preliminary Data Sheet 40 V0.9, 2008-04-28

PMA7110

Functional Description

2.5 Functional Block Description

2.5.1 Sensor Interfaces and Data Acquisition

The PMA7110 has two internal sensors, two high sensitive differential analog interfaces

4 programmable gainfactors (from 76+-20%, 60+-20%, 50+-20% and 38+-20% ) and

one standard differential analog interface (gainfactor 1) to acquire environmental data:

• Temperature Sensor

• Battery Voltage Monitoring

• external data through analog interface

The analog data is aquired and digitalized by the internal 10 Bit ADC. Measurement

routines for acquiring data are available within the ROM library functions that are

described in [1] “Reference Documents” on Page 157.

2.5.1.1 Sensor Interface

SFR CFG2.3 PDADC

SFR CFG1 .3

SFR REF.5

SFR ADCM

SFR ADCS

SFR ADCC1

SFR ADCC0 STC[2:0]

SFR ADCC1

SFR ADCOFF

SFR ADCDH

SFR ADCDL

SFR ADCM

ADCEn

READC

SARSATL

SARSATH

CL000

CG3FF

SAMPLE

BUSY

GAIN[1:0]

FCnSC

SUBC[2: 0]

TVC[2:0]

GAIN[1:0]

OFF[5:0]

Data[9:8]

Data[7:0]

RV[2:0]

CS[2:0]

EOC

Sensor Interface

MUX

Channel 0

CSI

Logi c

Control

Channel 1

Channel 2

Channel 3

Channel 4

A

D

C

Channel 5

Channel 6

Ch5p,Ch5n

Ch6p,Ch6n

Ch0p,Ch0 n

Ch1p,Ch1n

Ch2p,Ch2n

Ch3p,Ch3n

Ch4p,Ch4n

Battery Sensor

Temper ature

Sensor

Sta ndard

Sens or Int erfac e

Bandga p

Reference

VRe g Sensor

External

Sensor

Interface

AMUX1

AMUX2

VDD (sens.)

VDD (sens.)

V1P (sen s.)

V1N (sens.)

VM1 (sens.)

Channel 7

Ch7p,Ch7n

V2P (sens.)

V2N (sens.)

VM2 (sens.)

RD (sens.)

Figure 6 Block diagram Sensor Interface

The sensor interface connects to the external sensors and to the internal (on-chip)

temperature and battery voltage sensors.

Preliminary Data Sheet 41 V0.9, 2008-04-28

PMA7110

Functional Description

All signal channels can be configured for differential or single-ended operation.

Differential operation is only recommended for signals where the common-mode voltage

is stable, while the positive and negative signal voltages vary symmetrically around the

common-mode voltage.

The input multiplexer selects one channel for the input signal and one channel for the

reference voltage to the ADC. Any channel can be selected as reference, except

channels 6 and 7, which are specially adapted to the low level signals from external

sensors.

Preliminary Data Sheet 42 V0.9, 2008-04-28

PMA7110

Functional Description

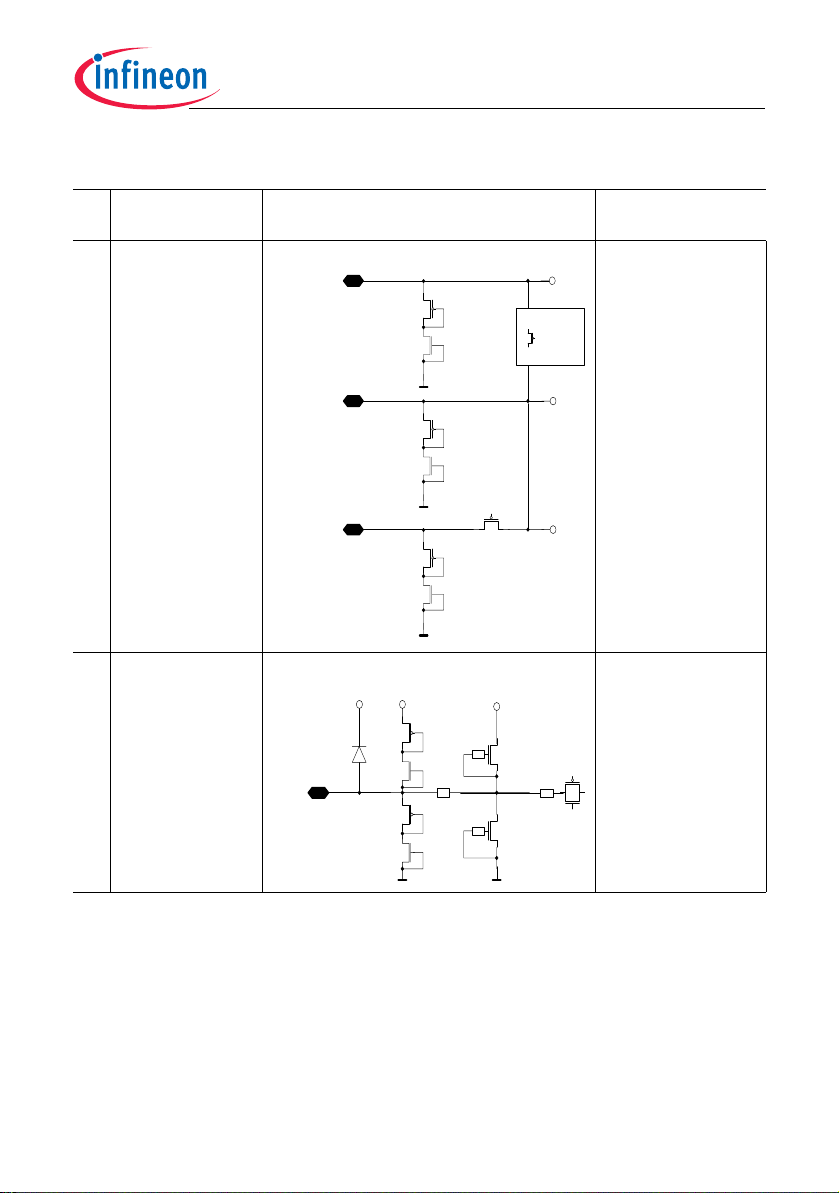

2.5.1.2 Two differential high sensitive interfaces to external Sensors

Differential high sensitive sensor interface 1( (Channel 6)

V1P/V1N is the positve/negative differential voltage inputs of the first sensor bridge.

Differential high sensitive sensor interface 2 (Channel 7)

V2P/V2N is the positve/negative differential voltage inputs of the second sensor bridge.

Channel gain selection

The SFR Bit ADCC1.5-4 [GAIN1-0] gain factor selection allows the selection of the

sensitivity of the analog input channels 6 and 7. The gain is one for all other input

channels (see Table 6 ).

Table 6 Selection of the gain factor

Gain factor

(gain)

76 +/- 20% 11X 0 0

60 +/- 20% 11X 0 1

50 +/- 20% 11X 1 0

38 +/- 20% 11X 1 1

1others00

1others01

1others10

1others11

Channel

ADCM.CS2-0

GAIN1 GAIN0

Sensor Excitation

The two sensor bridges have a common positive supply which is always connected.

When a sensor bridge is to be activated, its negative supply is pulled to ground by

pad VM1 or VM2 for VMP or VMA. Otherwise, it is disconnected. In this way the power

of a connected bridge can be supplied.

Preliminary Data Sheet 43 V0.9, 2008-04-28

PMA7110

Functional Description

These two sensor interfaces are very adapted piezoresistive Wheatstone bridge

sensors, whose output signal is differential and ratiometric (proportional to the bridge

excitation voltage). The electrical configuration is shown as a example in figure below..

V1P

VM1

V1N

VDD

V2P

VM2

RD

V2N

Figure 7 Wheatstone bridge sensor

2.5.1.3 Interface to other signals

Battery voltage Interface (Channel 0)

The positive input to the battery voltage signal is derived by dividing voltage V

by 3.5.

Bat

The negative input is connected to GND. The battery voltage is converted with a

resolution of approximately 4.1mV, using channel 3 as reference.

Temperature Sensor Interface (Channel 1)

The temperature signal to the ADC is a single ended signal, with the PTAT voltage

between 500 and 1100 mV. The temperature sensor signal is digitized with a resolution

of approximately 0.5°C, using channel 3 as reference.

Standard sensor Interface (Channel 2)

The positive input signal is available at AMUX1, and the negative input at AMUX2.

2.5.1.4 Reference voltages

When channel 6 or 7 is selected as input to the ADC, and the negative external sensor

supply is identical to the negative supply of ADC, this negative supply should be selected

by the multiplexer as reference voltage on channel 5.

Preliminary Data Sheet 44 V0.9, 2008-04-28

PMA7110

Functional Description

If the negative external sensor supply (which should be used as reference voltage to

external sensor) is not identical to the negative supply of ADC, it should be connected to

the Channel 2 so that it can be selected by multiplexer as reference voltage for channel

6 or 7. But the supply voltage of the external sensor must always be within the range

GND to V

BATT

ch2p

ch2n

PMA7110

External

Supply

+

-

Sensor

ch6p

ch6n

Voltage

Figure 8 External Sensor use channel 2 as reference voltage

Additional 3 channels on ADC input multiplexer carry voltages which are intended as

reference voltages for the converter:

BANDGAP Reference (Channel 3)

This reference is a nominal voltage of 1210 mV. It is intended as reference for the

temperature and V

VREG Reference (Channel 4)

This reference is the V

and is meant as reference for the test signal, to allow as large test signal as possible.

BRIDGE SUPPLY Reference (Channel 5)

When channel 6 or 7 is selected as input to the ADC, the reference voltage is the bridge

supply voltage. A multiplexer selects the appropriate negative bridge supply.

measurements.

Bat

voltage. This is the largest allowable input voltage to the ADC,

REG

Preliminary Data Sheet 45 V0.9, 2008-04-28

PMA7110

Functional Description

2.5.1.5 Temperature Sensor

Temperature measurement is performed by a dedicated ROM library function.

See “Temperature Sensor Characteristics” on Page 128 for the sensor specification.

2.5.1.6 Battery Voltage Monitor

Battery Voltage measurement is performed by a dedicated ROM library function.

See “Battery Sensor Characteristics” on Page 128 for the sensor specification.

Preliminary Data Sheet 46 V0.9, 2008-04-28

PMA7110

Functional Description

2.5.2 Memory Organization and Special Function Registers (SFR)

Nonvolati le

Code

memory

0xFFFF

0x5900

0x58FF

0x58C0

0x58BF

0x5880

0x587F

0x5800

0x57FF

0x5780

0x577F

0x4033

0x4000

0x3FFF

0x3003

0x3002

0x3000

0x2FFF

0x007F

0x0000

FLASH

6kB

ROM

12 kB

Not implemented

Reference c ells

64B

64B

128B

128B

6016B

Lockbyte 1

Flas h Configurat ion + ID

User Data Sector II

Lockbyte 3

User Data Sector I

CRC Sum + Loc kbyt e 2

Code

Vect ors

Not implemented

SFR mapped SRAM

Revision number, Checksum

Mode Handlers

Library Functions

Vect ors

Figure 9 Memory map

The following memory blocks are implemented:

RAM

256

byte

RAM

16

byte

Data

memory

Data

Optional battery buffered

Data RAM

Indirect

addressing

SFR

Direct

addressing

Xdata

memory

Battery buffered Data RAM

acce ssib le w i th

movx

0xFF

0x80

0x7F

0x00

0x0F

0x00

• 12 kByte ROM Memory

• 3 Byte SFR mapped Code Memory

• 6 kByte Flash Code Memory

• 2x128 Bytes FLASH User Data Memory

• 128 Bytes Flash Configuration, ID and Reference cells

• 2 x 128 Byte Data RAM / thereof 128 bytes battery buffered optionally

• 16 bytes battery buffered XData RAM

Preliminary Data Sheet 47 V0.9, 2008-04-28

PMA7110

Functional Description

2.5.2.1 ROM

A 12 kB ROM memory is located in address range 0000H to 2FFF

ROM library functions and Reset/Wakeup Handlers

The ROM contains the reset handler, the wakeup handler and the ROM Library functions

(see [1] “Reference SFR Registers” on Page 144).

A hardware mechanism is implemented to prevent direct jumping into the ROM area,

thus access to the ROM library functions is granted via a vector table at the bottom of

the ROM address space.

ROM protection

To protect the ROM code against readout a hardware mechanism is implemented, thus

a read operation from the ROM in the protected address area returns zero.

.

H

Preliminary Data Sheet 48 V0.9, 2008-04-28

PMA7110

Functional Description

2.5.2.2 FLASH

FLASH Organization

The FLASH is divided into five sectors. Each sector can be erased and written

individually (Bytewise erasing and writing is not possible).

• 4000H -- 577FH (6016 Bytes) code sector (sector 0): This sector contains the Code

sector for the application program.

• 5780

-- 587FH (2x128 Bytes) User Data sector I + User Data sector II (sector 1

H

+ sector 2): These two sectors contain the User Data Sector which can store

individual device configuration data. It also contains the crystal frequency which is

needed for the ROM Library functions.

• 5880H -- 58BFH (64 Bytes) configuration sector (sector 3): This sector contains

the FLASH configuration sector for FLASH driver parameters.

• 58C0

-- 58FFH (64 Bytes) reference cells sector (sector 4): This sector contains

H

the reference current generator cells for FLASH reading.

FLASH protection

Write and erase operations on the Flash Code Sector are only allowed in

PROGRAMMING mode. To protect the FLASH against unauthorized access three

lockbytes can be set:

• Lockbyte 1: Address 0x58FF (Top address of Flash Configuration + Reference Cells

Sector).

This is written in the end of production test. Whenever the Resethandler detects this

value the FCSP.0[ConfLock] gets set and the Reference Cells Sector, Flash

Configuration Sector are irreversibly switched to read-only.

• Lockbyte 2: Address 0x577F (Top address of the Code Sector).

This byte is written (also a ROM CRC) by the Programmer together with the Code

download. When the Resethandler detects this byte it sets the FCSP.1[CodeLCK]. In

addition the Debug Mode, Programming Mode and Test Mode are no longer

accessible. Their pin settings lead to Normal Mode and reduced TM wherein the CRC

can be checked (pass/fail) and the whole Flash can be erased to reset the chip to

shipping state. This Lockbyte has to be set during programming the Code Sector to

protect application code against undesired read-out.

• Lockbyte 3: Address 0x587F (Top address of the User Data Sector I and User Data

Sector II).

There is a ROM Library function for setting this byte. (Therefore the data in the User

Preliminary Data Sheet 49 V0.9, 2008-04-28

PMA7110

Functional Description

Data Sector have to be captured into RAM, the Lockbyte added, the whole sector

erased (Flash!) and re-written. Whenever the Resethandler detects this value

DSR.0[FlashLCK] gets set. When not written together with the Code Sector the User

Data Sector is planned to be written in Normal Mode (from the Customer) using ROM

Library functions. There is a HW mechanism that blocks access to the Flash

Registers when operating from the Flash (not ROM). In this way, the usage of ROM

Library functions is guaranteed, they ensure several important details not to damage

the chip. If Lockbyte 3 is set without setting Lockbyte 2, this byte shows no effect and

will result a unlocked FLASH. How to set Lockbyte 3 is described in “FLASH Set

Lockbyte 3” on Page 121.

Preliminary Data Sheet 50 V0.9, 2008-04-28

PMA7110

e

Functional Description

2.5.2.3 RAM

The RAM is available as data storage for the application program. ROM library functions

may use some RAM locations for passing parameters and internal calculations. The

RAM area which is used for the ROM library functions is specified in [1] “Reference

Documents” on Page 157.

The RAM is always powered in RUN state and IDLE state.

The upper 128 bytes of RAM are always switched off in POWER DOWN state and

THERMAL SHUTDOWN state and lose their contents in these states.

SFR bit CFG2.4[PDLMB] determines if the lower 128 bytes of RAM are powered during

POWER DOWN state and THERMAL SHUTDOWN state.

If not powered in these states, this RAM loses the content, otherwise it can be used as

battery buffered storage beyond a POWER DOWN period.

Note: The RAM is not reset at a System Reset. After a Brown Out Reset this feature can

be used to possibly recover data from RAM.

After Power On Reset the RAM is not initialized, thus it contains random data. The

application has to initialize the RAM if needed.

2.5.2.4 Special Function Registers

Special Function Registers are used to control and monitor the state of the PMA7110

and its peripherals. The following table shows the naming convention for the SFR

descriptions that are used throughout this document.

R/C/W - 0/0

Value after Power On Reset

Value after wakeup from POWER DOWN / THERMAL SHUTDOWN stat

x ... unknown

u ... unchanged

1 ... high

0 ... low

Access:

R ... Readable

C ... Cleared after Read / automatically cleared

W ... Writeable

Figure 10 Naming convention for Register descriptions

Note: If a single bit or the whole byte value is declared as unchanged, it keeps its state

even during POWER DOWN state or THERMAL SHUTDOWN state.

Table 7 "SFR Special Function Register Address Overview" on Page 53 shows all

available registers of the PMA7110.

Note: All SFRs that are listed in Table 7 "SFR Special Function Register Address

Overview" on Page 53 but not in Table 8 "Status of SFR Registers in

Preliminary Data Sheet 51 V0.9, 2008-04-28

PMA7110

Functional Description

POWER DOWN state" on Page 53 should not be changed by the application

since they could be damaged irreversibly. These are handled automatically by the

ROM Library functions if needed.

Preliminary Data Sheet 52 V0.9, 2008-04-28

PMA7110

Functional Description

Table 7 SFR Special Function Register Address Overview

Addr Regis ter A ddr Register Addr Register Addr Register Addr Register Addr Register Addr Register Addr Re gister

F8 CFG0 F 9 LFRXC FA FB FC FD F E FF

F0 B F1 EXTWUF F2 EXTWUM F3 SP IB F4 SPIC F5 SPID F6 SPIM F7 SPIS

E8 CFG1 E9 FCSP EA FCS EB P3DIR EC P3 IN ED P3SENS EE RFC EF LB D

E0 ACC E1 FCPP 0 E2 FCPP1 E3 FCSERM E4 FCTKAS E5 FCSS E6 RFS E7 RFENC

D8 CFG2 D9 DSR DA ADCOFF DB ADCC0 DC ADCC1 DD ADWBC DE RFVCO DF RFFSLD

D0 PSW D1 REF D2 ADCM D3 ADCS D4 ADCDL D5 ADCDH D6 OSCCONF D7 RFFSPLL

C8 TCON2 C9 TMOD2 CA T L3 CB TH3 CC TL2 CD TH2 CE LFP1L CF LFP1H

C0 WUF C1 WUM C2 XTCFG C3 XTAL1 C4 XTAL0 C5 LFOOTP C6 LFOOT C7 LFPCFG

B8IP B9 DIVIC BAITPL BBITPH BCITPR BDTMAX BELFPOL BF LFPOH

B0 P3Out B1 I2CB B2 LFCDFlt B3 LFDIV0 B4 LFDIV1 B5 LFCDM B6 LFRX1 B7 LFRX0

A8 IE A9 CRCC AA CRCD AB RNGD AC CRC0 AD CRC1 AE RFTX AF LFSYNCFG

A0 P2

(reserved)

98 SCON

(reserved)

90 P1OUT 91 P1DIR 92 P1IN 93 P1SENS 94 DBCL0 95 DBCH0 96 DBTL0 97 DBTH0

88 TCON 89 TMOD 8A TL0 8B TL1 8C TH0 8D TH1 8E RFD 8F IRQFR

80 P0

(reserved)

The following tabe shows which SFRs keep their content in POWER DOWN state and

THERMAL SHUTDOWN state and gives a reference to the page within this document

where a detailed description can be found.

A1 P2Dir

99 SBUF

81SP 82DPL 83DPH 84MMR0 85MMR1 86MMR2 87PCON

A2 I2CC A3 I2CM A4 LFRXS A5 LFRXD A6 LFSYN0 A7 LFSYN1

(reserved)

9A I2CD 9B I2CS 9C DBCL1 9D DBCH1 9E DBTL1 9F DBTH1

(reserved)

Table 8 Status of SFR Registers in POWER DOWN state

SFR (Abbr.) Addr Register description

ACC 0xE0 Accumulator n Page 57

ADCC0 0xDB ADC Configuration Register 0 n Page 144

ADCC1 0xDC ADC Configuration Register 1 n Page 144

ADCDL 0xD 4 ADC Result Register (low byte) n Page 151

ADCDH 0xD5 ADC Result Register (high byte) n Page 151.

ADCM 0xD 2 ADC Mode Register n Page 145.

ADCOFF 0xDA ADC Input Offset c-network configuration n Page 145.

ADCS 0xD 3 ADC Status Register n Page 146.

ADWBC 0xDD AD WBC Wire Bond Check n Page 146.

B 0xF0 Register B n Page 57.

CFG0 0xF8 Configuration Register 0 n Page 58

CFG1 0xE8 Configuration Register 1 n Page 59

CFG2 0xD8 Configuration Register 2 n Page 60

CRCC 0xA9 CRC Control Register n Page 87

CRCD 0xAA CRC Data Register n Page 151

CRC0 0xAC CRC Shift Register (low byte) n Page 151

CRC1 0xAD CRC Shift Register (high byte) n Page 152

POWER SUP PLY

VDDD VDDC Note:

Preliminary Data Sheet 53 V0.9, 2008-04-28

Description

Page

PMA7110

Functional Description

SFR (Abbr.) Addr Register description

DBCL0 0x9 4 CPU Debug Compare Register 0 (low) n Page 152

DBCH0 0x95 CPU Debug Compare Register 0 (high) n Page 152

DBTL0 0x96 CPU Debu g Target Register 0 (low) n Page 152

DBTH0 0x9 7 CPU Debug Target Register 0 (high) n Page 152

DBCL1 0x9 C CPU Debug Compare Register 1 (low) n Page 152

DBCH1 0x9D CPU Debug Compare Register 1 (high) n Page 152

DBTL1 0x9E CPU Debug Target Register 1 (low) n Page 153

DBTH1 0x9 F CPU Debug Target Register 1 (high) n Page 153

DIVIC 0xB9 Internal Clock Divider n Page 71

DPL 0x82 Data Pointer (low) n Page 57

DPH 0x83 Data Pointer (high ) n Page 57

DSR 0xD9 Diagnosis and Status Register n Page 60

ExtWUF 0xF1 Wakeup Flag Register 2 n Page 65

ExtWUM 0xF2 Wakeup Mask Register 2 n Page 65

FCSP 0xE9 Flash Control Register - Sector Protection Control n Page 146

FCS 0xEA Flash Control Register - Status Mode n Page 147.

FCPP0 0xE1 Flash Charge Pumps Power Control Register 0 n Page 147

FCPP1 0xE2 Flash Charge Pumps Power Control Register 1 n Page 147

FCSERM 0xE3 Flash Sector Erase and Read Margin Select Register n Page 148.

FCTKAS 0xE4 Flash Tkill and Analog Output Select Register n Page 153

FCSS 0xE5 Flash Control Register for Single-Step Mode n Page 154

I2CB 0xB1 I2C Baudrate Register n Page 112

I2CC 0xA2 I2C Control Register n Page 111

I2CD 0x9A I2C Data Register n Page 112

I2CM 0xA3 I2C Mode Register n Page 113

I2CS 0x9B I2C Status Register n Page 112

IE 0xA 8 Interrupt Enable Register n Page 76

IP 0xB 8 Interrupt Priority Register n Page 77

IRQFR 0x8F Interrupt Request Flag Register (for extended interrupts) n Page 77

ITPL 0xBA Interval Timer Precounter Register (Low Byte) n Page 69

ITPH 0xBB Interval Timer Precounter Register (High Byte) n Page 69

ITPR 0xBC Interval Timer Period Register n Page 68

LBD 0xEF Low Battery Detector Control n Page 154

LFCDFlt 0xB2 t.b.d n t.b.d

LFCDM 0xB 5 t.b.d n t.b.d

LFDIV0 0xB3 t.b.d n t.b.d

LFDIV1 0xB4 t.b.d n t.b.d

LFOOT 0xC 6 t.b.d n t.b.d

LFOOTP 0xC5 t.b.d n t.b.d

LFPCFG 0xC 7 t.b.d n t.b.d

LFP0L 0xBE t.b.d n t.b.d

LFP0H 0xBF t.b.d n t.b.d

LFP1L 0xCE t.b.d n t.b.d

POWER SUP PLY

VDDD VDDC Note:

Description

Page

Preliminary Data Sheet 54 V0.9, 2008-04-28

PMA7110

Functional Description

SFR (Abbr.) Addr Register description

LFP1H 0xCF t.b.d n t.b.d

LFRX0 0xB7 t.b.d n t.b.d

LFRX1 0xB6 t.b.d n t.b.d

LFRXC 0xF9 t.b.d n t.b.d.

LFRXD 0xA5 t.b.d n t.b.d

LFRXS 0xA4 t.b.d n t.b.d.

LFSYNCFG 0xAF t.b.d n t.b.d.

LFSYN0 0xA6 t.b.d n t.b.d

LFSYN1 0xA7 t.b.d n t.b.d

MMR0 0x84 Memory Mapped Register 0 n Page 148

MMR1 0x85 Memory Mapped Register 1 n Page 148

MMR2 0x86 Memory Mapped Register 2 n Page 150

OSCCONF 0xD 6 RC HF Oscillator Configuration Register n Page 155

P0 (reserved) 0x80 IO-Port 0 Data Register n.u.

P1DIR 0x91 IO-Port 1 Direction Register n Page 106

P1IN 0x92 IO-Port 1 Data IN Register n Page 107

P1OUT 0x90 IO-Port 1 Data OUT Register n Page 106

P1SENS 0x93 IO-Port 1 Sensitivity Register n Page 107

P3DIR 0xEB IO-Port 3 Direction Register n Page 106

P3IN 0xEC IO-Port 3 Data IN Register n Page 107

P3OUT 0xB0 IO-Port 3 Data OUT Register n Page 106.

P3SENS 0xED IO-Port 3 Sensitivity Register n Page 107

P2 (reserved) 0xA0 IO-Port 2 Data Register n.u.

P2Dir (reserved) 0xA1 IO-Port 2 Direction Register n.u.

PCON (reserved) 0x8 7 Power Control Register n.u.

PSW 0xD0 Program Status Word n Page 57

REF 0xD1 Resume Event Flag Register n Page 67

RFC 0xEE RF-Transmitter Co ntrol Register n Page 79

RFD 0x8 E RF-Encoder Tx Data Register n Page 82

RFENC 0xE7 R F-Encoder Tx Control Register n Page 82

RFFSPLL 0xD7 RF-Frequency Synthesizer PLL Configuration n Page 155.

RFS 0xE6 RF-Encoder Tx Status Register n Page 84

RFFSLD 0xDF RF-Frequency Synthesizer Lock Detector Configuration n Page 151

RFTX 0xAE RF-Transm itter Configuration Register n Page 79

RFVCO 0xD E RF-Frequency Synthesizer VCO Configuration n Page 151

RNGD 0xAB RNG Data Register n Page 89

SBUF (reserved) 0x99 Serial Interface Buffer n.u.

SCON (reserved) 0x98 Serial Interface Control Register n.u.

SP 0x81 Stack Pointer n Page 149.