Data Sheet, Preliminary, Nov. 2007

Control integrated Power

System (CIPOS™)

IKCS12F60AA

http://www.infineon.com/cipos

Power Management & Drives

Never stop thinking.

CIPOS™ IKCS12F60AA

Revision History: 2007-12 Rev.1.4

Previous Version: 1.3

Page Subjects (major changes since last revision)

8 max. bootstrap capacitor

Authors: O. Hellmund, W. Scholz, W. Frank

Edition 2007-07

Published by

Infineon Technologies AG

85579 Neubiberg, Germany

© Infineon Technologies AG 12/12/07.

All Rights Reserved.

Attention please!

The information given in this data sheet shall in no event be regarded as a guarantee of conditions or

characteristics (“Beschaffenheitsgarantie”). With respect to any examples or hints given herein, any typical

values stated herein and/or any information regarding the application of the device, Infineon Technologies

hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of

non-infringement of intellectual property rights of any third party.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office or representatives (http://www.infineon.com).

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types

in question please contact your nearest Infineon Technologies Office or representatives.

Infineon Technologies Components may only be used in life-support devices or systems with the express

written approval of Infineon Technologies, if a failure of such components can reasonably be expected to

cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or

system. Life support devices or systems are intended to be implanted in the human body, or to support

and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health

of the user or other persons may be endangered.

®

TrenchStop

CIPOS™, CoolMOS™, CoolSET™, DuoPack™, EmCon™ and thinQ!™ are trademarks of Infineon

Technologies AG.

is a registered trademark of Infineon Technologies AG.

Preliminary Data Sheet 2/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Table of Contents

CiPoS™ Control integrated Power System ..................................................................................................4

Features........................................................................................................................................................4

Target Applications.....................................................................................................................................4

Description...................................................................................................................................................4

System Configuration.................................................................................................................................4

Internal Electrical Schematic...........................................................................................................................5

Pin Assignment.................................................................................................................................................6

Pin Description............................................................................................................................................6

/HIN1,2,3 and /LIN1,2,3 (Low side and high side control pins, Pin 15 - 20) .............................................. 6

EN (enable, Pin 24) .................................................................................................................................... 7

ITRIP (Over-current detection function, Pin 21)......................................................................................... 7

VDD, VSS (control side supply and reference, Pin 22, 23)........................................................................7

VB1,2,3 and VS1,2,3 (High side supplies, Pin 1, 2, 4, 5, 7, 8)................................................................... 7

VRU, VRV, VRW (low side emitter, Pin 12, 13, 14) ................................................................................... 7

V+ (positive bus input voltage, Pin 10)....................................................................................................... 7

Absolute Maximum Ratings ............................................................................................................................8

Module Section............................................................................................................................................8

IGBT and Diode Section .............................................................................................................................8

Control Section............................................................................................................................................9

Recommended Operation Conditions............................................................................................................9

Static Parameters ...........................................................................................................................................10

Dynamic Parameters......................................................................................................................................11

Integrated Components.................................................................................................................................12

Circuit of a Typical Application.....................................................................................................................12

Test Circuits....................................................................................................................................................14

Preliminary Data Sheet 3/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

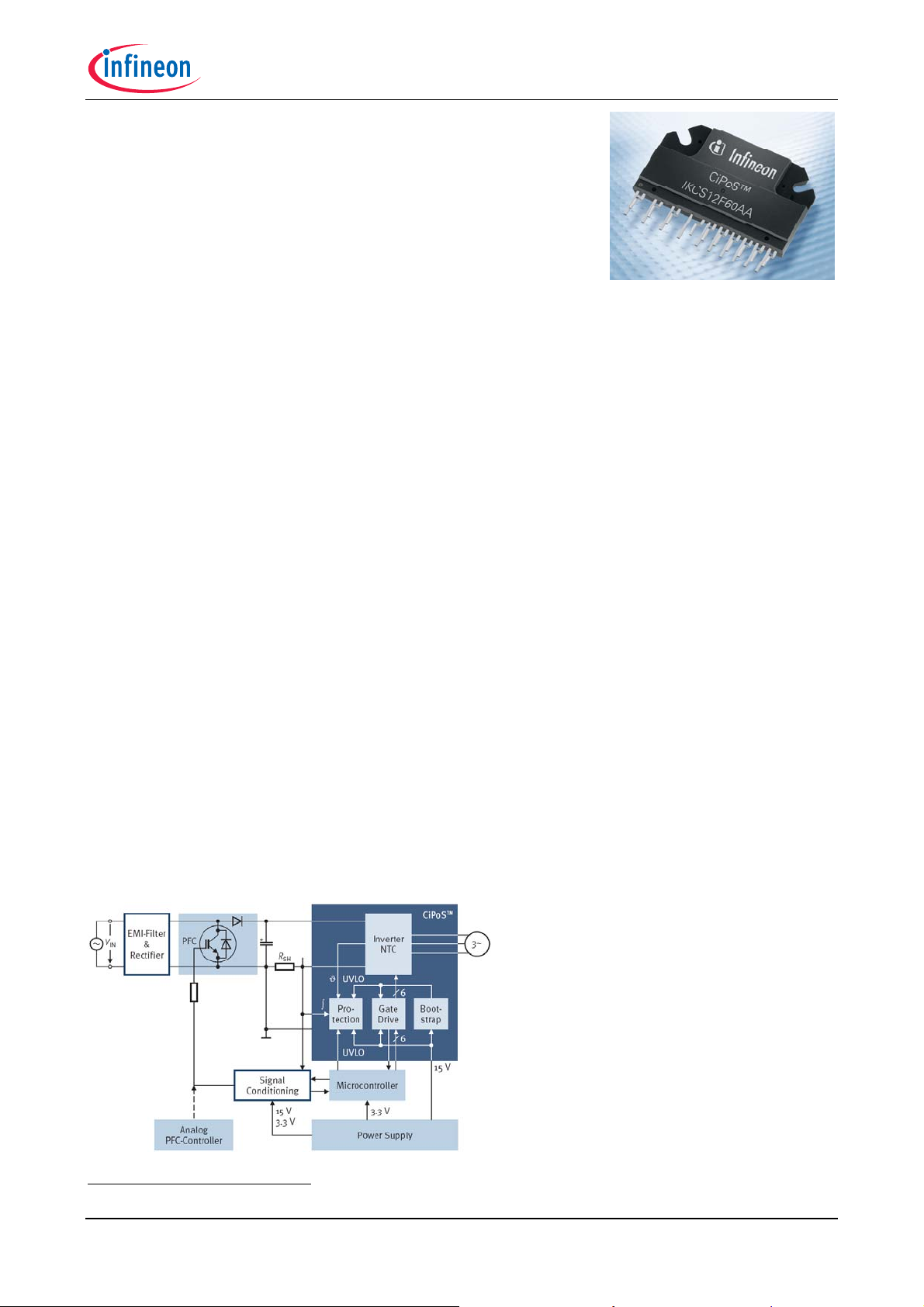

CIPOS™

Control integrated Power System

Single In-Line Intelligent Power Module

3Φ-bridge 600V / 12A @ 25°C

Features

• Fully isolated Single In-Line molded module

®

• TrenchStop

• Optimal adapted EmCon™ diode for low EMI

• Integrated bootstrap diode and capacitor

• Rugged SOI gate driver technology with

stability against transient and negative voltage

• Temperature monitor and over temperature

shutdown

• Overcurrent shutdown

• Undervoltage lockout at all channels

• Matched propagation delay for all channels

• Low side emitter pins accessible for all phase

current monitoring (open emitter)

• Cross-conduction prevention

• Lead-free terminal plating; RoHS compliant

• Qualified according to JEDEC

temperature stress tests for 500h) for target

applications

IGBTs with lowest V

CE(sat)

1

(high

Target Applications

• Washing machines

• Consumer Fans and Consumer Compressors

Description

The CiPoS™ module family offers the chance for

integrating various power and control components

to increase reliability, optimize PCB size and

system costs.

This SIL-IPM is designed to control AC motors in

variable speed drives for applications like air

conditioning, compressors and washing

machines. The package concept is specially

adapted to power applications, which need

extremely good thermal conduction and electrical

isolation, but also EMI-save control and overload

protection. The features of Infineon TrenchStop

IGBTs and EmCon™ diodes are combined with a

new optimized Infineon SOI gate driver for

excellent electrical performance.

®

System Configuration

• 3 halfbridges with TrenchStop® IGBT & FW-

EmCon™ diodes

• 3Φ SOI gate driver

• Bootstrap diodes for high side supply

• Integrated 100nF bootstrap capacitance

• Temperature sensor, passive components for

adaptions

• Isolated heatsink

• Creepage distance 3.1mm

1

J-STD-020 and JESD-022

Preliminary Data Sheet 4/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

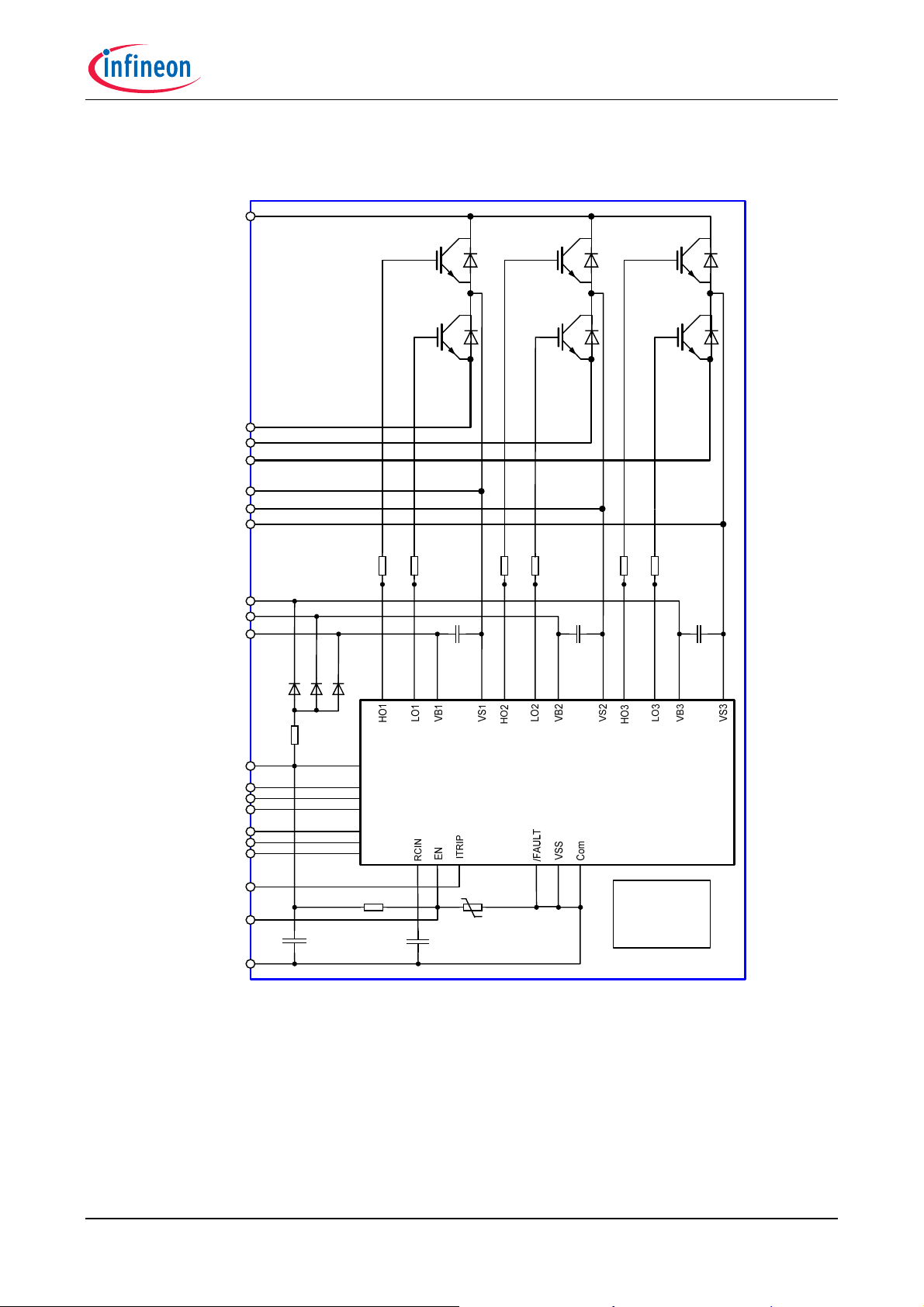

Internal Electrical Schematic

V+ (10)

Tr1, U-HS

D1

Tr3, V-HS

D3

Tr5, W-HS

D5

VRU (12)

VRV (13)

VRW (14)

U, VS1 (8)

V, VS2 (5)

W, VS3 (2)

VB3 (1)

VB2 (4)

VB1 (7)

Dbs1-

Dbs3

Rbs

Tr2, U-LS

D2

RH1 RL1 RL2RH2 RL3RH3

CbsH1 CbsH2 CbsH3

Tr4, V-LS

D4

Tr6, W-LS

D6

VDD (22)

/HIN1 (15)

/HIN2 (16)

/HIN3 (17)

/LIN1 (18)

/LIN2 (19)

/LIN3 (20)

ITRIP (21)

EN (24)

VSS (23)

Figure 1: Internal Schematic

VCC

/HIN1

/HIN2

/HIN3

/LIN1

/LIN2

/LIN3

R

Driver-IC

RTS

C2C1

For integrated

components see

Table

Preliminary Data Sheet 5/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Pin Assignment

Pin Number Pin Name Pin Description

1 VB3 high side floating IC supply voltage

2 W,VS3 motor output W, high side floating IC supply offset voltage

3 n.a. None

4 VB2 high side floating IC supply voltage

5 V,VS2 motor output V, high side floating IC supply offset voltage

6 n.a. None

7 VB1 high side floating IC supply voltage

8 U,VS1 motor output U, high side floating IC supply offset voltage

9 n.a. None

10 V+ positive bus input voltage

11 n.a. None

12 VRU low side emitter

13 VRV low side emitter

14 VRW low side emitter

15 /HIN1 input gate driver high side 1/U

16 /HIN2 input gate driver high side 2/V

17 /HIN3 input gate driver high side 3/W

18 /LIN1 input gate driver low side 1/U

19 /LIN2 input gate driver low side 2/V

20 /LIN3 input gate driver low side 3/W

21 ITRIP input overcurrent shutdown

22 VDD module control supply

23 VSS module negative supply

24 EN input logic enable, output temperature monitoring

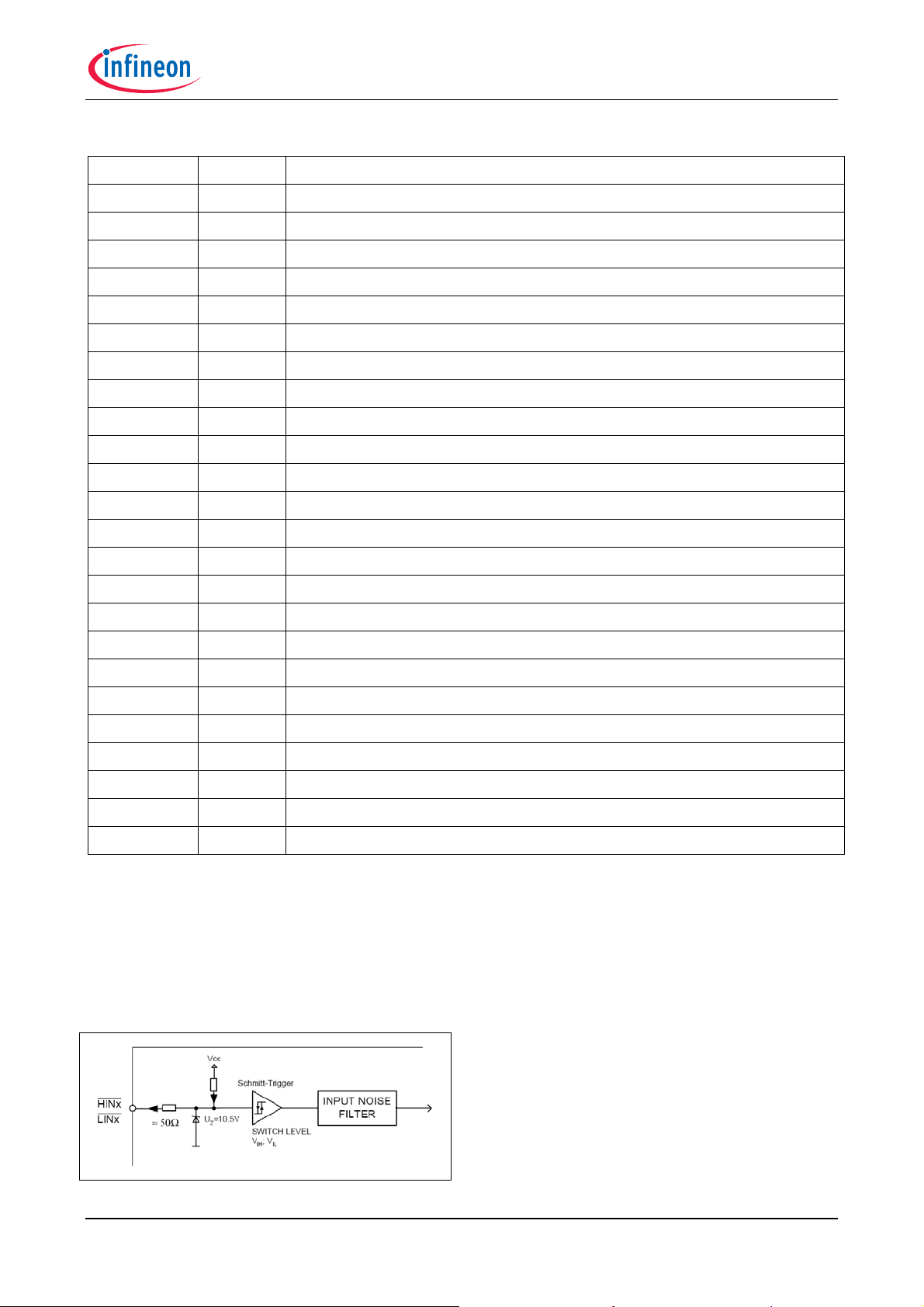

Pin Description

/HIN1,2,3 and /LIN1,2,3 (Low side and high

side control pins, Pin 15 - 20)

These pins are active low and they are

responsible for the control of the integrated IGBT

The Schmitt-trigger input threshold of them are

such to guarantee LSTTL and CMOS compatibility

down to 3.3V controller outputs. Pull-up resistor of

about 75 kOhm is internally provided to pre-bias

inputs during supply start-up and a zener clamp is

provided for pin protection purposes. Input

schmitt-trigger and noise filter provide beneficial

noise rejection to short input pulses.

It is recommended for proper work of CiPoS™ not

to provide input pulse-width lower than 1us.

The integrated gate drive provides additionally a

shoot through prevention capability which avoids

the simultaneous on-state of two gate drivers of

the same leg (i.e. HO1 and LO1, HO2 and LO2,

HO3 and LO3).

Figure 2: Input pin structure

Preliminary Data Sheet 6/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

A minimum deadtime insertion of typ 325ns is also

provided, in order to reduce cross-conduction of

the external power switches.

EN (enable, Pin 24)

The signal applied to pin EN controls directly the

output stages. All outputs are set to LOW, if EN is

at LOW logic level. The internal structure of the

pin is the same as Figure 1 made exception of the

switching levels of the Schmitt-Trigger, which are

here V

typical propagation delay time is t

= 2.1 V and V

EN,TH+

= 1.32 V. The

EN,TH-

= 700 ns.

EN

Figure 3: Internal Circuit at pin EN

This pin may also be used for reading out the

temperature close to the gate drive IC. Please

refer to section “Integrated Components” for the

specification of the integrated parts.

ITRIP (Over-current detection function, Pin 21)

CiPoS™ provides an over-current detection

function by connecting the ITRIP input with the

motor current feedback. The ITRIP comparator

threshold (typ 0.45V) is referenced to VSS

ground. A input noise filter (typ: t

ITRIPMIN

= 225ns)

prevents the driver to detect false over-current

events.

Over-current detection generates a hard shut

down of all outputs of the gate driver after the

shutdown propagation delay of typically 690ns.

The fault-clear time is set to typically to 2ms.

VDD, VSS (control side supply and reference,

Pin 22, 23)

VDD is the low side supply and it provides power

both to input logic and to low side output power

stage. Input logic is referenced to VSS ground as

well as the under-voltage detection circuit.

The under-voltage circuit enables the device to

operate at power on when a supply voltage of at

least a typical voltage of V

= 11.9 V is at

DDUV+

least present.

The IC shuts down all the gate drivers power

outputs, when the VCC supply voltage is below

= 10.3 V. This prevents the external power

V

DDUV-

switches from critically low gate voltage levels

during on-state and therefore from excessive

power dissipation.

VB1,2,3 and VS1,2,3 (High side supplies, Pin 1,

2, 4, 5, 7, 8)

VB to VS is the high side supply voltage. The high

side circuit can float with respect to VSS following

the external high side power device

emitter/source voltage.

Due to the low power consumption, the floating

driver stage is supplied by an integrated bootstrap

circuit connected to VDD. This includes also

Figure 4: Input filter timing diagram

integrated bootstrap capacitors of 100 nF at each

floating supply, which are located very close to the

gate drive circuit.

The under-voltage detection operates with a rising

supply threshold of typical V

falling threshold of V

= 10.3 V according to

DDUV-

= 11.9 V and a

BSUV+

Figure 4.

VS1,2,3 provide a high robustness against

negative voltage in respect of VSS of -50 V. This

ensures very stable designs even under rough

conditions.

VRU, VRV, VRW (low side emitter, Pin 12, 13,

14)

The low side emitters are available for current

measurements of each phase leg. It is

recommended to keep the connection to pin VSS

as short as possible in order to avoid unnecessary

inductive voltage drops.

V+ (positive bus input voltage, Pin 10)

The high side IGBT are connected to the bus

voltage. It is recommended, that the bus voltage

does not exceed 500 V.

Preliminary Data Sheet 7/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Absolute Maximum Ratings

(Tc = 25°C, if not stated otherwise)

Module Section

Description Condition Symbol

Storage temperature range

Operating temperature control PCB1

Solder temperature

Insulation test voltage

Mounting torque

Mounting pressure on surface

Creepage distance

External bootstrap capacitor

IGBT and Diode Section

Description Condition Symbol

Wave soldering,

1.6mm (0.063in.)

from case for 10s

RMS, f=50Hz, t

=1min

M3 screw and washer

Package flat on

mounting surface

single capacitor

charging, VDD = 20V

T

stg

T

PCB

T

sol

V

ISOL

MS

N

MC

dS

C

bs,ext

Value Unit

Min max

-40 125 °C

- 125 °C

- 260 °C

2500 - V

- 0.6 Nm

- 150 N/mm²

3.1 - mm

2 µF

Value Unit

Collector-Emitter breakdown voltage2 VGE=0V, IC = 0.25mA,

t

< 250ns

p

DC output current Tc = 25°C,T

vJ

<

V

(BR)CES

I

, Iv, Iw -12

u

150°C

= 80°C,T

T

c

vJ

<

150°C

Repetitive peak collector current tp limited by T

Short circuit withstand time3

VDD = 15V,VDC ≤ 400V,

T

j ≤ 150°C

Power dissipation per IGBT Tc = 25°C P

Operating junction temperature

range

IGBT

Diode

I

vJmax

, Iv, Iw -18 18 A

u

t

- 5 µs

sc

- 35 W

tot

T

vjI

T

vjD

1

Monitored by pin 24

2

For static operation with biased High-Side VS is reduced by 50V.

3

Allowed number of short circuits: <1000; time between short circuits: >1s.

min max

600 - V

-6

-40

-40

12

6

150

150

A

°C

Preliminary Data Sheet 8/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Description Condition Symbol

Value

Unit

min typ max

Single IGBT thermal resistance,

R

- - 3.0

thJC

K/W

junction-case

Single diode thermal resistance,

R

- - 4.2

thJCD

junction-case

Control Section

Description Condition Symbol

Value

Unit

min max

Module supply voltage VDD -1 20 V

High side floating supply voltage

V

-1 20

BS

(VB vs. VS)

High side floating IC supply offset

voltage

tp < 250ns

t

≥ 250ns

p

t

< 500ns

p

t

≥ 500ns

p

-

V

S1,2,3

VDD-VBS-50

VDD-VBS-6

600

-

550

V

-

-

Input voltage LIN, HIN, EN, ITRIP Vin -1 10 V

Operating junction temperature1 T

Max. switching frequency f

- 125

J,IC

- 20 kHz

PWM

Recommended Operation Conditions

All voltages are absolute voltages referenced to VSS -Potential unless otherwise specified.

Description Symbol

Value

min max

High side floating supply offset voltage VS -3 500

High side floating supply voltage (VB vs. VS) VBS 12.5 17.5

High side output voltage (VHO vs. VS) VHO 0 V

BS

Low side power supply VDD 12.5 17.5

Logic input voltages LIN,HIN,EN,ITRIP VIN 0 5

Unit

V

1

Monitored by pin 24

Preliminary Data Sheet 9/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Static Parameters

(Tc = 25°C, if not stated otherwise)

Description Condition Symbol

Value

Unit

min typ max

Collector-Emitter saturation voltage V

Diode forward voltage V

Zero gate voltage collector current1 V

Short circuit collector current1 V

= 15V, I

DD

out

25°C

150°C

DD

= 0V, I

= +/- 6A

out

25°C

150°C

= 600V, VGE = 0V

CE

t

< 250ns

p

T

= 25°C

j

T

= 150°C

j

= 15V, t

DD

V

= 300V, Tj ≤ 150°C

CC

SC

= +/- 6A

≤ 5µs

V

CE(sat)

-

-

VF

-

-

I

CES

-

-

1.7

1.9

1.6

1.6

-

-

2.15

2.05

40

1000

- 35 - A

I

C(SC)

V

V

µA

Logic "0" input voltage (LIN,HIN) VIH 1.7 2.1 2.4 V

Logic "1" input voltage (LIN,HIN) VIL 0.7 0.9 1.1 V

EN positive going threshold V

EN negative going threshold V

ITRIP positive going threshold V

ITRIP input hysteresis V

VDD and VBS supply undervoltage

V

positive going threshold

VDD and VBS supply undervoltage

V

negative going threshold

VCC and VBS supply undervoltage

V

lockout hysteresis

Input clamp voltage (/HIN, /LIN, EN,

V

1.9 2.1 2.3 V

EN,TH+

1.1 1.32 1.5 V

EN,TH-

360 450 540 mV

IT,TH+

60 85 - mV

IT,HYS

DDUV+

V

BSUV+

DDUV-

V

BSUV-

DDUVH

V

BSUVH

INCLAMP

11.0 12.0 12.8 V

9.5 10.3 11.0 V

1.2 1.6 - V

9.0 10.1 13.0 V

ITRIP)

Quiescent VB

supply current (VBx

x

V

= low IQB - 300 550 µA

IN

only)

Quiescent VDD supply current

V

= float I

IN

- 2.1 3.0 mA

QDD

(VDD only)

Input bias current V

Input bias current V

ITRIP Input bias current V

EN Input bias current VEN = 5V I

Leakage current of high side

= 5V I

IN

= 0V

IN

= 5V I

ITRIP

V

= 550V, T

S

= 125°C

j,IC

- 43 100 µA

IN+

I

IN-

- 62 120 µA

ITRIP+

- 62 120 µA

EN+

- 30 - µA

I

LVS

- 100 200 µA

1

Allowed number of short circuits: <1000; time between short circuits: >1s.

Preliminary Data Sheet 10/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Dynamic Parameters

(Tc = 25°C, if not stated otherwise)

Description Condition Symbol

Turn-on propagation delay

High side or low side

Turn-on rise time

High side or low side

Turn-off propagation delay

High side or low side

Turn-off fall time

High side or low side

Shutdown propagation delay

V

V

I

V

V

V

I

V

LIN,HIN

= 300V

DC

= 6A, V

out

LIN,HIN

LIN,HIN

= 300V

DC

= 6A, V

out

LIN,HIN

= 0V; I

DC

= 5V

= 5V; I

DC

= 0V

= 6A,

out

= 300V

= 6A,

out

= 300V

VEN = 0V, Iu, Iv, Iw = 6A tEN - 900 - ns

ENABLE

Shutdown propagation delay ITRIP V

Input filter time ITRIP V

Input filter time at LIN for turn on

= 1V, Iu, Iv, Iw = 6A t

ITRIP

= 1V t

ITRIP

V

= 0 V & 5V t

LIN,HIN

and off and input filter time at HIN

for turn on only

Input filter time at HIN for turn off V

Input filter time at HIN for turn off V

= 5V t

HIN

= 5 V t

HIN

Input filter time EN t

Fault clear time after ITRIP-fault V

Min. deadtime between low side

V

DT

LIN,HIN

ITRIP

= 0 V & 5V

= 0 V

and high side

Value

Unit

min typ max

- 617 - ns

t

d(on)

- 21 - ns

t

r

- 832 - ns

t

d(off)

- 29 - ns

t

f

- 900 - ns

ITRIP

155 225 380 ns

ITRIPmin

120 270 - ns

FILIN

- 200 - ns

FILIN1

- 350 - ns

FILIN2

300 430 - ns

FILEN

- 4 - ms

t

FLTCLR

1 - - µs

PWM

Deadtime of gate drive circuit DTIC 325 ns

IGBT Turn-on Energy (includes

reverse recovery of diode)

IGBT Turn-off Energy I

Diode recovery Energy I

I

= 6A, V

out

T

= 25°C

vj

= 150°C

T

vj

= 6A, V

out

T

= 25°C

vj

T

= 150°C

vj

= 6A, V

out

T

= 25°C

vj

T

= 150°C

vj

= 300V

DC

= 300V

DC

= 300V

DC

E

on

-

-

E

off

-

-

E

rec

-

-

145

195

122

160

31

81

µJ

-

-

µJ

-

-

µJ

-

-

Preliminary Data Sheet 11/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Integrated Components

Resistor (0.25 W)

Resistor

Resistor

B-Constant of NTC (Negative

Temperature Coefficient)

Bootstrap diode forward voltage

Capacitor

Capacitor

Bootstrap Capacitor

Circuit of a Typical Application

Value Description Condition Symbol1

min typ max

= 25°C

T

NTC

T

= 25°C B25 - 4250 - K

NTC

I

= 100mA

FDbs

Rbs

R

RTS

- 1.9 2.05 V

V

FDbs

C1

C2

CbsH

x

- 10 -

- 24

- 100 -

- 100 -

- 2.2 -

- 100 -

Unit

Ω

kΩ

nF

1

Symbols according to Figure 1

Preliminary Data Sheet 12/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Characteristics

1000ns

100ns

t, SWITCHING TIMES

10ns

0A 5A 10A 15A

IC, COLLECTOR CURRENT

Figure 5. Typical switching times as a

function of collector current

(inductive load, T

V

= 300V, V

CE

DD

= 15V

=150°C,

J

Dynamic test circuit in Figure A)

t

t

d(on)

r

t

t

f

d(off)

1000ns

100ns

t, SWITCHING TIMES

10ns

25°C 50°C 75°C 100°C 125°C

TvJ, JUNCTION TEMPERATURE

Figure 6. Typical switching times as a

function of junction temperature

(inductive load, V

V

= 0/15V, IC = 6A

GE

= 300V,

CE

Dynamic test circuit in Figure A)

t

d(off)

t

d(on)

t

f

t

r

1.25mJ

1.00mJ

0.75mJ

0.50mJ

E, SWITCHING ENERGY LOSSES

0.25mJ

0.00mJ

0A 5A 10A 15A

IC, COLLECTOR CURRENT

Figure 7. Typical switching energy losses

E

on

E

off

0.15mJ

0.10mJ

0.05mJ

E, SWITCHING ENERGY LOSSES

E

rec

0.00mJ

Figure 8. Typical switching energy losses

as a function of collector current

(inductive load, T

V

= 300V, V

CE

J

= 0/15V

GE

= 150°C,

Dynamic test circuit in Figure A)

25°C 50°C 75°C 100°C 125°C

TvJ, JUNCTION TEMPERATURE

as a function of junction

temperature

(inductive load, V

= 0/15V, IC = 6A

V

GE

= 300V,

CE

Dynamic test circuit in Figure A)

E

on

E

off

E

rec

Preliminary Data Sheet 13/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

F

12V

10V

8V

6V

4V

, VOLTAGE AT PIN EN

EN

V

Vdd = 10.3V

15V

2V

0V

25°C 50°C 75°C 100°C

20V

TC, CASE TEMPERATURE

Figure 9. Typical voltage at pin EN as a

15A

12A

9A

6A

, COLLECTOR CURRENT

C

I

3A

0A

Figure 10. Typical output characteristic of

function of case temperature

VGE=25°C

125°C

150°C

0V 1V 2V 3V

VCE, COLLECTOR EMITTER VOLTAGE

IGBT as a function of collector

emitter voltage (V

= 15V)

DD

15A

12A

9A

6A

, forward CURRENT

I

VGE=25°C

3A

0A

0V 1V 2V

125°C

150°C

VF, forward VOLTAGE

Figure 11. Typical diode forward current as

a function of forward voltage

Single Pulse

IGBT

Diode

0

10

K/W

-1

K/W

10

, TRANSIENT THERMAL RESISTANCE

thJC

Z

-2

10

K/W

100ns 1µs 10µs 100µs 1ms 10ms 100ms 1s

tP, PULSE WIDTH

Figure 24. Diode transient thermal

impedance as a function of pulse

width

/T)

(D=t

P

Preliminary Data Sheet 14/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Test Circuits and Parameter Definiton

Figure A: Dynamic test circuit

Leakage inductance L

Stray capacitance C

=180nH

σ

=39pF

σ

Figure B: Definition of diodes switching characteristics

t

Erec

⋅=

dtivErec

FD

∫

0

Figure C: Definition of Enable and ITIRP propagation delay

LIN1,2,3

HIN1,2,3

iCU, iCV, i

, v

CEU

CEV

CW

, v

CEW

2.1V

t

d(off)

90%

10%

0.9V

t

f

10%

t

Eoff

t

Eoff

⋅=

∫

0

2%

dtivEoff

CxCEx

Figure D: Switching times definition and switching energy definition

t

d(on)

t

r

90%

10%v

t

Eon

t

Eon

∫

0

2%

⋅=

dtivEon

CxCEx

Preliminary Data Sheet 15/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

LIN

LO

t

FILIN

high

t

FILIN

on

HIN

LIN

HO

LO

off on off

low

Figure E: Short Pulse suppression

Preliminary Data Sheet 16/17 Rev. 1.4, Dec. 2007

CIPOS™ IKCS12F60AA

Package Outline IKCS12F60AA

Description Condition Symbol

Value

Unit

min typ max

Weight

m

P

- 17 - g

Preliminary Data Sheet 17/17 Rev. 1.4, Dec. 2007

Loading...

Loading...