INFINEON HYB39S256400DT-6, HYB39S256400DT-7, HYB39S256400DT-7.5, HYB39S256400DT-8, HYB39S256800DT-6 User Manual

...

查询HYB39S256160DC-6供应商查询HYB39S256160DC-6供应商

Data Sheet, Rev. 1.02, Feb. 2004

HYB39S256400D[C/T](L)

HYB39S256800D[C/T](L)

HYB39S256160D[C/T](L)

256-MBit Synchronous DRAM

SDRAM

Memory Products

Never stop thinking.

Edition 2004-02

Published by Infineon Technologies AG,

St.-Martin-Strasse 53,

81669 München, Germany

© Infineon Technologies AG 2004.

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as a guarantee of

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim an y and all war ranties , including b ut not limited to w arranties of non -infringement, regarding

circuits, descriptions and charts stated herein.

Infineon Technologies is an appro ved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide

(www.infineon.com).

Warnings

Due to technical requirements components may contain dangerous substances. For in formation on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components ma y only be used in lif e-support devices or systems with the e xpress written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the

failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life

support devices or systems are intended to be implanted in the human body, or to support and/or maintain and

sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other

persons may be endangered.

Data Sheet, Rev. 1.02, Feb. 2004

Data Sheet, Rev. 1.02, Feb. 2004

HYB39S256400D[C/T](L)

HYB39S256800D[C/T](L)

HYB39S256160D[C/T](L)

256-MBit Synchronous DRAM

SDRAM

Memory Products

Memory Products

Never stop thinking.

HYB39S256[40/80/16]0D[C/T](L)

Revision History: Rev. 1.02 2004-02

Page Subjects (major changes since last revision)

17 Corrected Mode Register Definition in chapter 3

all Various layout and editorial changes

Previous Version: Rev. 1.01 2004-01

all Various layout and editorial changes

Previous Version: Rev. 1.0 2002-06

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this do cument) to:

techdoc.mp@infineon.com

Template: mp_a4_v2.0_2003-06-06.fm

HYB39S256[40/80/16]0D[C/T](L)

256-MBit Synchronous DRAM

Table of Contents Page

1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.2 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2 Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.1 Signal Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

2.2 Package P–TSOPII–54 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

2.3 Package P–TFBGA–54 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

2.4 Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.1 Operation Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.2 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3 Mode Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3.1 Burst Length . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.4 Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

3.5 Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.5.1 Read and Write . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.5.2 DQM Function . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.5.3 Suspend Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.5.4 Power Down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

4 Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.1 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

4.2 AC Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

5 Package Outlines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

Data Sheet 5 Rev. 1.02, 2004-02

HYB39S256[40/80/16]0D[C/T](L)

256-MBit Synchronous DRAM

1Overview

1.1 Features

• Fully Synchronous to Positive Clock Edge

• 0 to 70 °C operating temperature

• Four Banks controlled by BA0 & BA1

• Programmable CAS

• Programmable Wrap Sequence: Sequential or Interleave

• Programmable Burst Length: 1, 2, 4, 8 and full page

• Multiple Burst Read with Single Write Operation

• Automatic and Controlled Precharge Command

• Data Mask for Read / Write control (x4, x8)

• Data Mask for byte control (x16)

• Auto Refresh (CBR) and Self Refresh

• Power Down and Clock Suspend Mode

• 8192 refresh cycles / 64 ms (7,8 µs)

• Random Column Address every CLK (1-N Rule)

• Single 3.3 V

• LVTTL Interface versions

• Plastic Packages: P–TSOPII–54 400mil width (x4, x8, x16)

• Chipsize Packages: P–TFBGA–54 (12 mm x 8 mm)

± 0.3 V Power Supply

Latency: 2 & 3

Overview

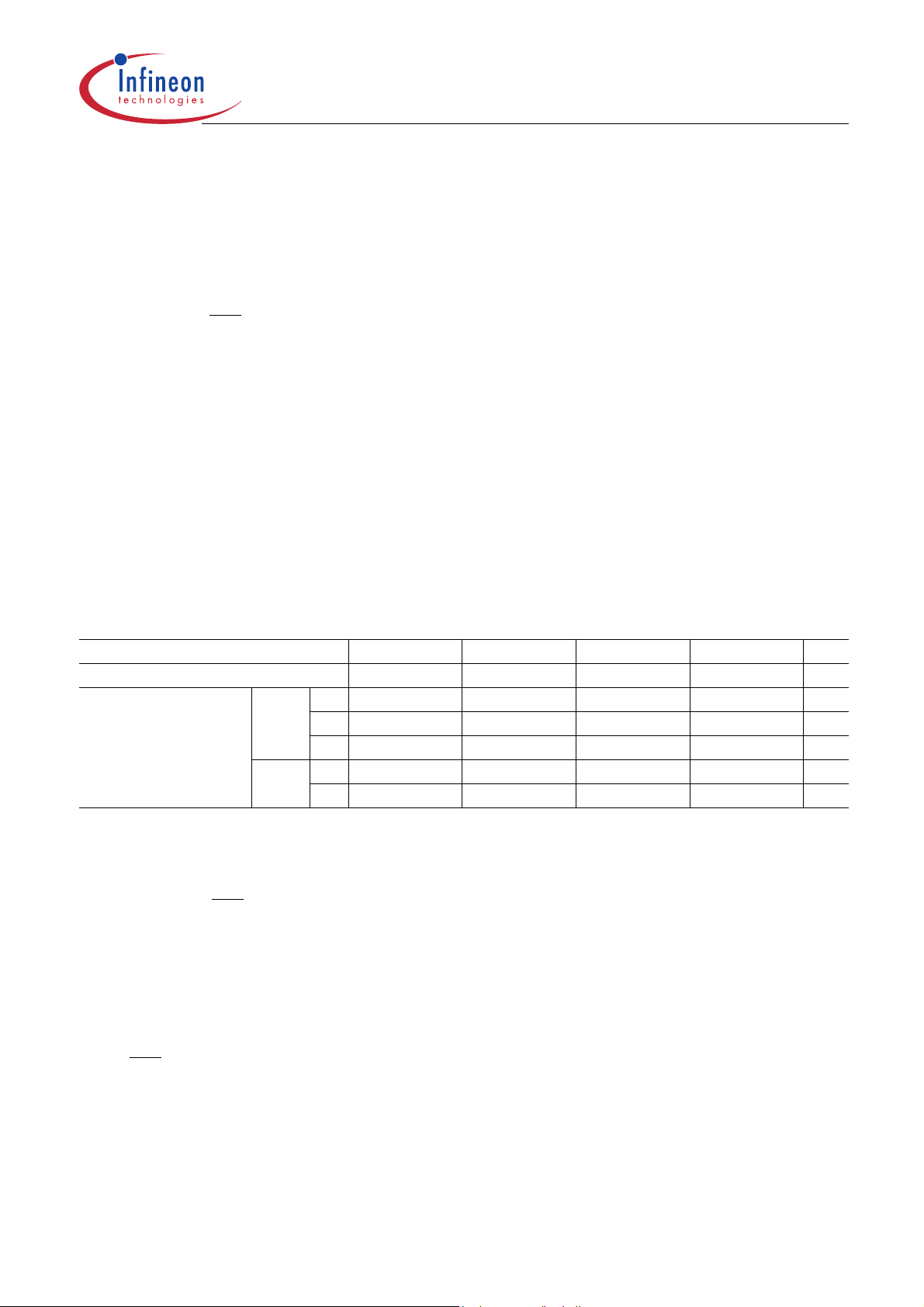

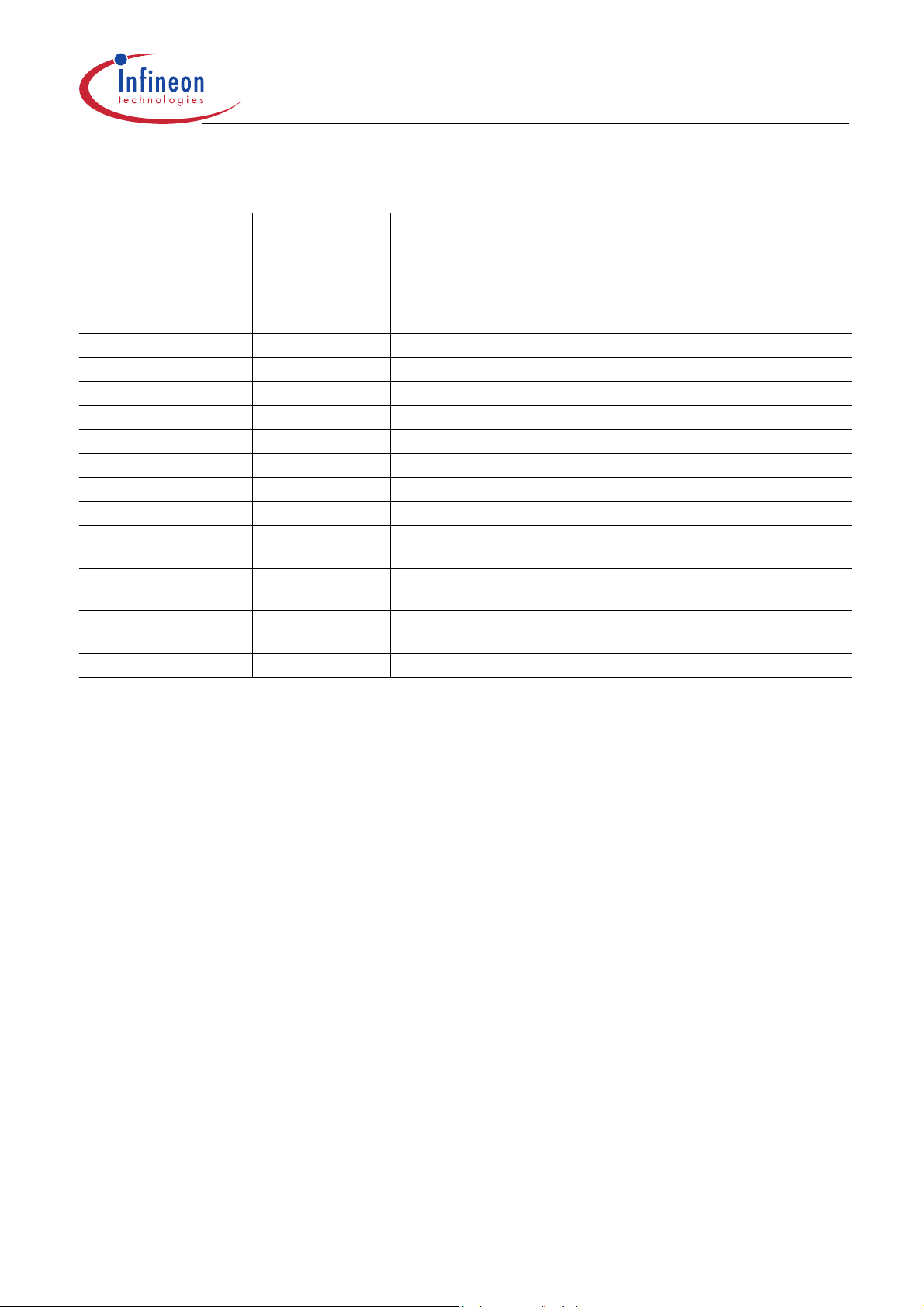

Table 1 Performance

Part Number Speed Code –6–7-7.5–8Unit

Speed Grade PC166 3–3–3 PC133 2–2–2 PC133 3–3–3 PC100 2–2–2 —

max. Clock Frequency @CL3

@CL2

f

166 143 133 125 MHz

CK3

t

677.58ns

CK3

t

5 5.4 5.4 6 ns

AC3

t

7.5 7.5 10 10 ns

CK2

t

5.4 5.4 6 6 ns

AC2

1.2 Description

The HYB39S256[40/80/16]0D[C/T](L) are four bank Synchronous DRAM’s organized as 4 banks x 16 MBit x4,

4 banks x 8 MBit x8 and 4 banks x 4 Mbit x16 respectively. These synchronous devices achieve high speed data

transfer rates for CAS

synchronizes the output data to a system clock. The chip is fabricated with INFINEON’s advanced 0.14 µm

256-MBit DRAM process technology.

The device is designed to comply with all industry standards set for synchronous DRAM products, both e lectrically

and mechanically. All of the contro l, address, data input and output circuits are synchronized with the positive edge

of an externally supplied clock.

Operating the four memory banks in an interleave fashion allows random access operation to occur at a higher

rate than is possible with standard DRAMs. A sequential and gapless data rate is possible depending on burst

length, CAS

Auto Refresh (CBR) and Self Refresh opera tion are supporte d. These d evices opera te with a single 3.3V

power supply. All 256-Mbit components are available in P–TSOPII–54 and P–TFBGA–54 packages.

latency and speed grade of the device.

-latencies by employing a chip architecture that prefetches multiple bits and then

± 0.3 V

Data Sheet 6 Rev. 1.02, 2004-02

10072003-13LE-FGQQ

HYB39S256[40/80/16]0D[C/T](L)

256-MBit Synchronous DRAM

Table 2 Ordering Information

Type Speed Grade Package Description

HYB 39S256400DT-6 PC166-333-520 P-TSOP-54-2 (400mil) 166MHz 4B x 16M x 4 SDRAM

HYB 39S256400DT-7 PC133-222-520 P-TSOP-54-2 (400mil) 143MHz 4B x 16M x 4 SDRAM

HYB 39S256400DT-7.5 PC133-333-520 P-TSOP-54-2 (400mil) 133MHz 4B x 16M x 4 SDRAM

HYB 39S256400DT-8 PC100-222-620 P-TSOP-54-2 (400mil) 125MHz 4B x 16M x 4 SDRAM

HYB 39S256800DT-6 PC166-333-520 P-TSOP-54-2 (400mil) 166MHz 4B x 8M x 8 SDRAM

HYB 39S256800DT-7 PC133-222-520 P-TSOP-54-2 (400mil) 143MHz 4B x 8M x 8 SDRAM

HYB 39S256800DT-7.5 PC133-333-520 P-TSOP-54-2 (400mil) 133MHz 4B x 8M x 8 SDRAM

HYB 39S256800DT-8 PC100-222-620 P-TSOP-54-2 (400mil) 125MHz 4B x 8M x 8 SDRAM

HYB 39S256160DT-6 PC166-333-520 P-TSOP-54-2 (400mil) 166MHz 4B x 4M x 16 SDRAM

HYB 39S256160DT-7 PC133-222-520 P-TSOP-54-2 (400mil) 143MHz 4B x 4M x 16 SDRAM

HYB 39S256160DT-7.5 PC133-333-520 P-TSOP-54-2 (400mil) 133MHz 4B x 4M x 16 SDRAM

HYB 39S256160DT-8 PC100-222-620 P-TSOP-54-2 (400mil) 125MHz 4B x 4M x 16 SDRAM

HYB39S256400DTL-x – P-TSOP-54-2 (400mil) 4B x 16M x 4 SDRAM Low Power

Versions (on request)

HYB39S256800DTL-x – P-TSOP-54-2 (400mil) 4B x 8M x 8 SDRAM Low Power

Versions (on request)

HYB39S256160DTL-x – P-TSOP-54-2 (400mil) 4B x 4M x 16 SDRAM Low Power

Versions (on request)

HYB39S256xx0DC(L)-x – P-TFBGA-54 (on request)

Overview

Data Sheet 7 Rev. 1.02, 2004-02

10072003-13LE-FGQQ

HYB39S256[40/80/16]0D[C/T](L)

256-MBit Synchronous DRAM

2 Pin Configuration

2.1 Signal Pin Description

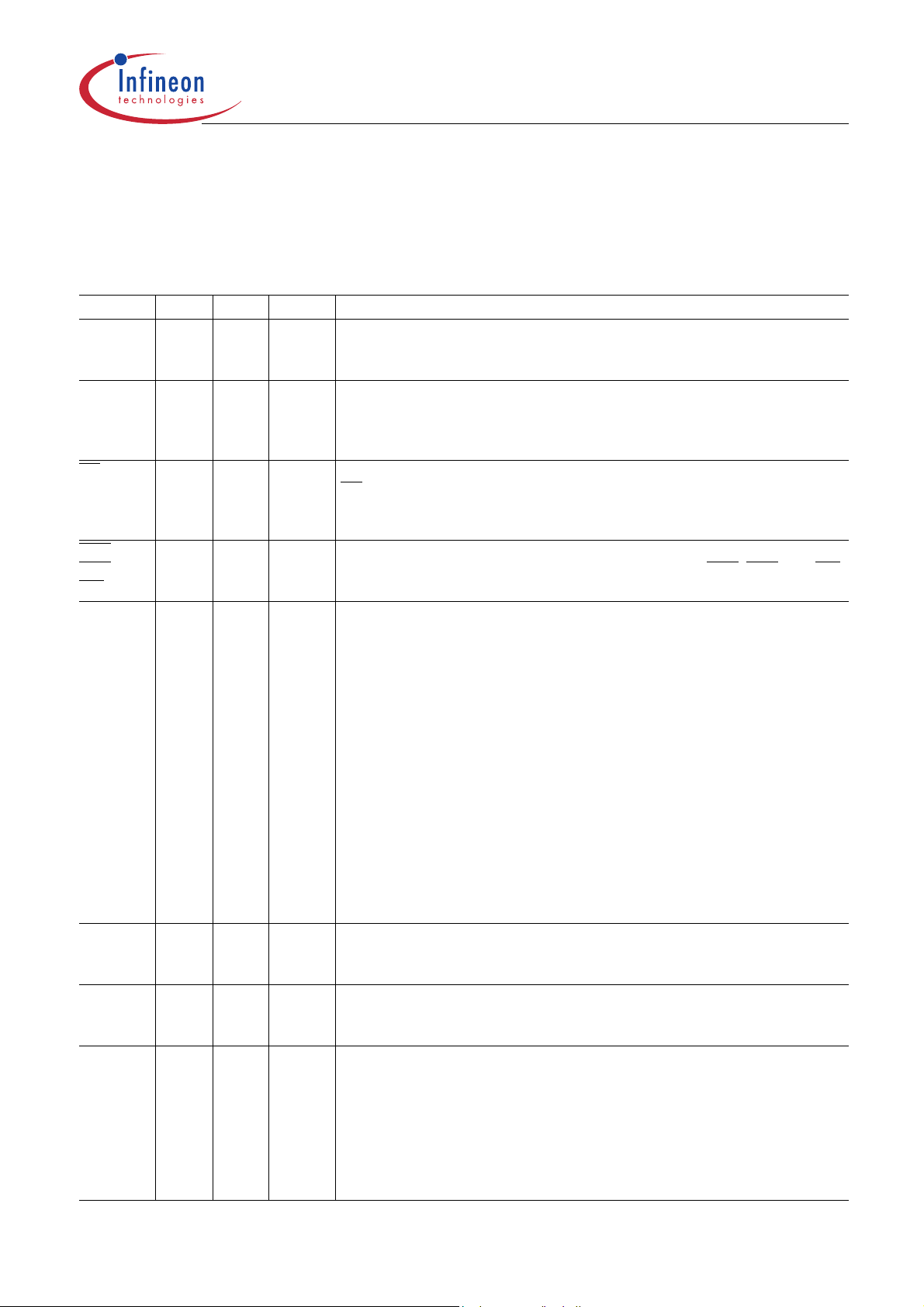

Table 3 Signal Pin Description

Pin Type Signal Polarity Function

CLK Input Pulse Positive

Edge

CKE Input Level Active

High

CS

RAS

CAS

WE

A0 - A12 Input Level – Address Inputs

BA0, BA1 Input Level – Bank Select

DQx Input

DQM

LDQM

UDQM

Input Pulse Active

Low

Input Pulse Active

Low

Level – Data Input/Output

Output

Input Pulse Active

High

Clock Input

The system clock input. All of the SDRAM inputs are sampled on the rising

edge of the clock.

Clock Enable

Activates the CLK signal when high and deactivates the CLK signal when

low, thereby initiating either the Powe r Down mode, Suspend mode, or the

Self Refresh mode.

Chip Select

CS

enables the command decoder when low and disables the command

decoder when high. When the command decoder is disabled, new

commands are ignored but previous operations continue.

Command Signals

When sampled at the positive rising edge of the clock, CAS

define the command to be executed by the SDRAM.

During a Bank Activate command cycle, A0-A12 define the row address

(RA0-RA12) when sampled at the rising clock edge.

During a Read or Write command cycle, A0-An define the column address

(CA0-CAn) when sampled at the rising clock edge. CAn depends upon the

SDRAM organization:

64M x4 SDRAM CAn = CA9, CA11 (Page Length = 2048 bits)

32M x8 SDRAM CAn = CA9 (Page Length = 1024 bits)

16M x16 SDRAM CAn = CA8 (Page Length = 512 bits)

In addition to the column address, A10 (= AP) is used to invoke the

autoprecharge operation at the end of the b urst read or write cycle . If A10

is high, autoprecharge is selected and BA0, BA1 defines the bank to be

precharged. If A10 is low, autoprecharge is disabled.

During a Precharge command cycle, A10 (= AP) is used in conjunction

with BA0 and BA1 to control which bank(s) to pr echarge. If A10 is h igh, all

four banks will be precharged regardless of the state of BA0 and BA1. If

A10 is low, then BA0 and BA1 are used to define which bank to precharge.

Bank Select Inputs. Bank address inputs selects which of the four banks a

command applies to.

Data Input/Output pins operate in the same manner as on EDO or FPM

DRAMs.

Data Mask

The Data Input/Output mask places the DQ buffers in a high impedance

state when sampled high. In Read mode, DQM has a latency of two clock

cycles and controls the output buffers like an output enable. In Write mo de,

DQM has a latency of zero and operates as a word mask by allowing input

data to be written if it is low but blocks the write operation if DQM is high.

One DQM input is present in x4 and x8 SDRAMs, LDQM and UDQM

controls the lower and upper bytes in x16 SDRAMs.

Pin Configuration

, RAS, and WE

Data Sheet 8 Rev. 1.02, 2004-02

10072003-13LE-FGQQ

HYB39S256[40/80/16]0D[C/T](L)

256-MBit Synchronous DRAM

Table 3 Signal Pin Description

Pin Type Signal Polarity Function

V

DD VSS

Supply – – Power and Ground

Power and ground for the input buffers and the core logic (3 .3 V)

V

DDQ VSSQ

Supply – – Power and Ground for DQs

Isolated power supply and ground for the output buffers to provide

improved noise immunity.

NC – – – Not Connected

No internal electrical connection is present.

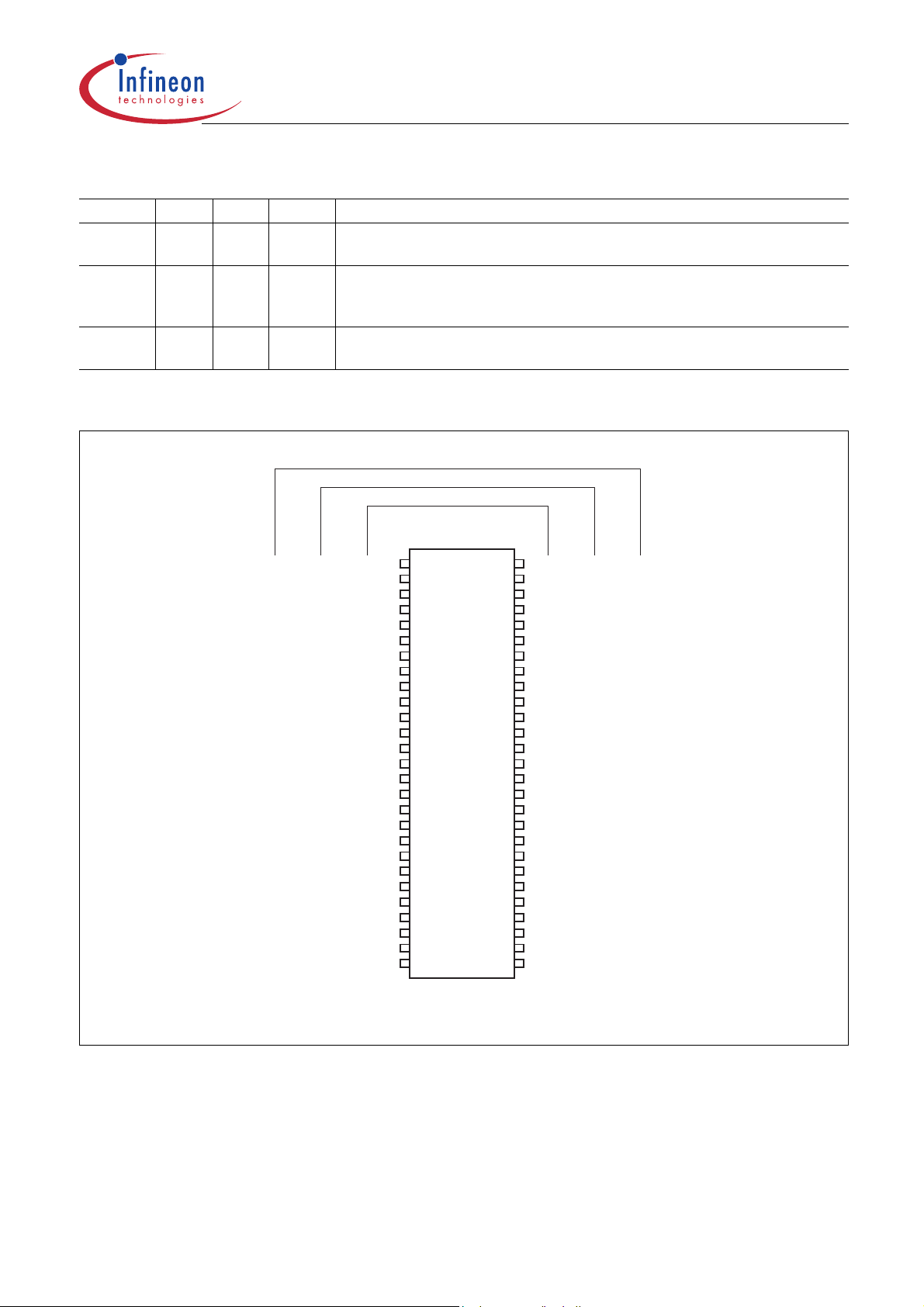

2.2 Package P–TSOPII–54

16 M x 16

32 M x 8

64 M x 4

V

V

DD

DD

DQ0

DQ0

V

V

DDQ

SSQ

DDQ

SSQ

DD

DD

DDQ

N.C.

DQ1

V

SSQ

N.C.

DQ2

V

DDQ

N.C.

DQ3

V

SSQ

N.C.

V

DD

N.C.

WE

CAS

RAS

CS

BA0

A10/AP

A0

A1

A2

A3

V

DD

DQ1

DQ2

V

DQ3

DQ4

V

DQ5

DQ6

V

DQ7

V

LDQM

WE

CAS

RAS

CS

BA0

BA1 BA1

A10/AP

A0

A1

A2

A3

V

V

DD

N.C.

V

DDQ

N.C.

DQ0

V

SSQ

N.C.

N.C.

V

DDQ

N.C.

DQ1

V

SSQ

N.C.

V

DD

N.C.

WE

CAS

RAS

CS

BA0

BA1

A10/AP

A0

A1

A2

A3

V

DD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

V

N.C.

V

N.C.

DQ3

V

N.C.

N.C.

V

N.C.

DQ2

V

N.C.

V

N.C.

DQM

CLK

CKE

A12

A11

A9 A9

A8

A7

A6

A5

A4

V

SS

SSQ

DDQ

SSQ

DDQ

SS

SS

V

DQ7

V

N.C.

DQ6

V

N.C.

DQ5

V

N.C.

DQ4

V

N.C.

V

N.C.

DQM

CLK

CKE

A12

A11

A8

A7

A6

A5

A4

V

SS

SSQ

DDQ

SSQ

DDQ

SS

SS

V

SS

DQ15

V

SSQ

DQ14

DQ13

V

DDQ

DQ12

DQ11

V

SSQ

DQ10

DQ9

V

DDQ

DQ8

V

SS

N.C.

UDQM

CLK

CKE

A12

A11

A9

A8

A7

A6

A5

A4

V

SS

Pin Configuration

TSOPII-54 (400 mil x 875 mil, 0.8 mm pitch)

SPP04126

Figure 1 Pinouts P–TSOPII–54

Data Sheet 9 Rev. 1.02, 2004-02

10072003-13LE-FGQQ

Loading...

Loading...