Page 1

DMA

Direct Memory Access

AURIX™ TC2xx Microcontroller Training

V1.0 2019-03

Please read the Important Notice and Warnings at the end of this document

Page 2

DMA

Direct Memory Access

Key Features Customer Benefits

Highlights

› The DMA moves data from source

locations to destination locations without

the intervention of the CPU or other on

chip devices.

› Up to 128 individually programmable

DMA channels

Flexible DMA channels requests

DMA double buffering

› Possible configuration of the request

type (SW, HW, Auto, ..) per DMA channel

› Transfer continuous data stream to two

destination buffers

› Perform multi DMA transactions from

non contiguous Memory regions

DMA Controller

Interrupt Router

DMARAM:

- DMA Channels

Transaction Control

Sets

Bus Master Interface

DMA

Request &

Arbitration

DMA Sub-block:

- Active DMA Channel

- DMA Move Engines

Bus Slave Interface

On Chip Bus

DMA linked list

2

2019-03-27 Copyright © Infineon Technologies AG 2019. All rights reserved.

Page 3

DMA

Flexible DMA channels requests

› The DMA Channel supports the following types of requests:

– DMA Software Request: initiated by CPU

– DMA Hardware Request: Any peripheral that can trigger an interrupt

can initiate a DMA transaction through the Interrupt Router

– DMA Daisy Chain Request: DMA transaction initiated by the next

higher priority DMA channel

– DMA Auto Start Request: initiated by the loading of the next

Transaction Control Set (TCS) during a DMA Linked List operation

3

2019-03-27 Copyright © Infineon Technologies AG 2019. All rights reserved.

Page 4

DMA

DMA double buffering

› Double buffer could be selected for source or destination buffering

› The application is able to freeze one of the destination buffers for cyclic

software tasks while the other buffer continues to be filled

DMA

DMA

Write Moves

On Chip bus

DMA

Read Moves

D5

D4

D3

D2

D1

D0

D0 D1 D2 D3 D4 D5

Continuous

Data Stream

Switch

Double Destination Buffering

4

2019-03-27 Copyright © Infineon Technologies AG 2019. All rights reserved.

Page 5

DMA

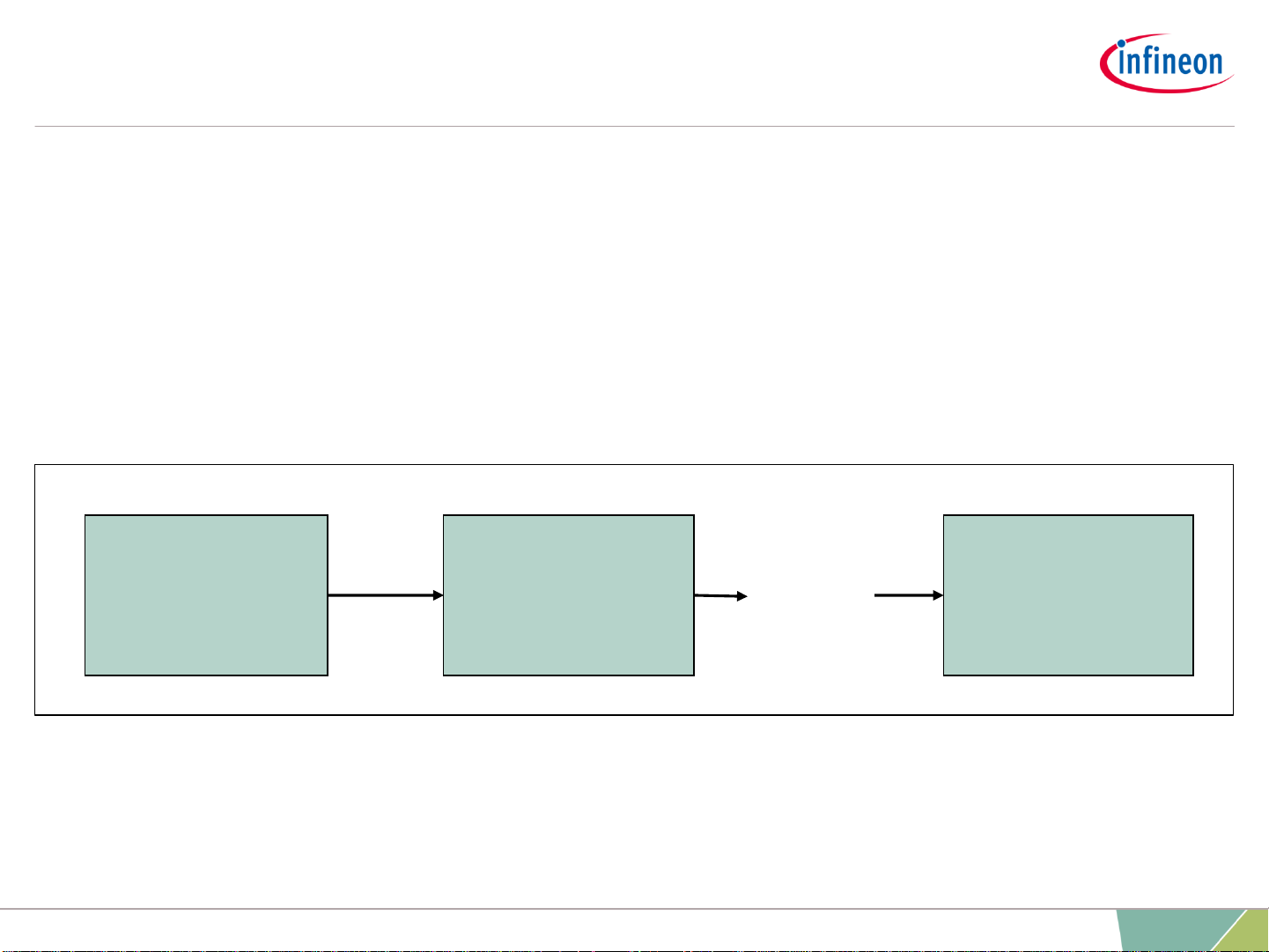

DMA linked list

› A linked list operation consists of a series of DMA transactions executed

by the same DMA channel. Each DMA transaction has an unique

configuration Set

› If the Auto start request is selected, a DMA transaction will be triggered

after the end of the previous one in the list no HW or SW trigger is

needed

› DMA linked are useful when user wants to transfer data from/to non

contiguous memory locations using one DMA channel and/or one

service request

DMA Transaction 1

• Source @1

• Destination @1

• Data Length 1

DMA Transaction 2

• Source @2

• Destination @2

• Data Length 2

DMA Transaction N

• Source @N

• Destination @N

• Data Length 1

Auto

Start

...

Auto

Start

Auto

Start

5

2019-03-27 Copyright © Infineon Technologies AG 2019. All rights reserved.

Page 6

DMA

System integration

› The DMA is connected to both SRI and SPB with master interfaces

› This enables the DMA to read and write data from/to any module

DMA

System Peripheral Bus

SRI Cross Bar Interconnect

Master

Interface

CPUs, RAM, Flash

Peripherals

Master

Interface

Slave

Interface

6

2019-03-27 Copyright © Infineon Technologies AG 2019. All rights reserved.

Page 7

Application example

DMA hardware requests

› In this example, data is transferred from the ADC output registers to

internal memory without any CPU intervention

DMA

ADC

Interrupt

Router

RAM

1

2

3

1. End of ADC conversion interrupt

2. Trigger a DMA channel transfer

3. Read ADC result register

4. Write data to RAM

4

7

2019-03-27 Copyright © Infineon Technologies AG 2019. All rights reserved.

Page 8

IMPORTANT NOTICE

The information given in this document shall in no

event be regarded as a guarantee of conditions or

characteristics (“Beschaffenheitsgarantie”).

With respect to any examples, hints or any typical

values stated herein and/or any information

regarding the application of the product, Infineon

Technologies hereby disclaims any and all

warranties and liabilities of any kind, including

without limitation warranties of non-infringement

of intellectual property rightsof any third party.

In addition, any information given in this

document is subject to customer’s compliance

with its obligations stated in this document and

any applicable legal requirements, norms and

standards concerning customer’s products and

any use of the product of Infineon Technologies in

customer’s applications.

The data contained in this document is exclusively

intended for technically trained staff. It is the

responsibility of customer’s technical

departments to evaluate the suitability of the

product for the intended application and the

completeness of the product information given in

this document with respectto such application.

For further information on the product,

technology, delivery terms and conditions and

prices please contact your nearest Infineon

Technologies office (www.infineon.com).

WARNINGS

Due to technical requirements products may

contain dangerous substances. For information

on the types in question please contact your

nearest Infineon Technologies office.

Except as otherwise explicitly approved by

Infineon Technologies in a written document

signed by authorized representatives of Infineon

Technologies, Infineon Technologies’ products

may not be used in any applications where a

failure of the product or any consequences of the

use thereof can reasonably be expected to result

in personal injury.

Edition 2019-03

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2019 Infineon Technologies AG.

All Rights Reserved.

Do you have a question about this

document?

Email: erratum@infineon.com

Document reference

AURIX_Training_1_

Direct_Memory_Access

Trademarks

All referenced product or service names andtrademarks are the property of their respectiveowners.

Loading...

Loading...