Page 1

UG_1801_PL16_1802_225559

Full-bridge converter for UPS

D2PAK/D2PAK-7 kit

About this document

This user guide describes the Infineon full-bridge demo board for UPS. The current design considers only the

power section including drivers and power devices with D2packages. D27-pin packages can also be used in this

demo board, which enables users to evaluate the performance of power MOSFETs and their drivers.

Scope and purpose

This document is intended to describe the functionalities of UPS converting DC to AC voltages. Users can then

evaluate the performance of power MOSFETs with gate driver ICs. With Infineon low-R

board can help reduce system cost and time-to-market.

Intended audience

This document addresses the market for UPS manufacturers with the goal of providing a high-performance

system solution at low cost.

MOSFETs the demo

DS(on)

Table of contents

About this document ............................................................................................................................1

Table of contents..................................................................................................................................1

1 Full-bridge converter for UPS with D2PAK/D2PAK-7 kit .......................................................... 2

1.1 Overview ............................................................................................................................................2

1.1.1 Key features ..................................................................................................................................3

1.2 Schematic ..........................................................................................................................................4

1.3 Layout ................................................................................................................................................4

1.4 Power-up procedure...........................................................................................................................6

1.4.1 PWM signal selections...................................................................................................................6

1.5 Performance evaluations....................................................................................................................6

1.5.1 Performance with heatsink at the front .........................................................................................6

1.5.2 Performance with heatsink at the back .......................................................................................10

1.6 Power loss estimations of MOSFETs and CS resistor ........................................................................11

1.7 Bill of Materials (BOM) .....................................................................................................................13

1.8 Additional results with D2PAK-7 (IRFS7430-7P).................................................................................14

1.8.1 Performance with heatsink at the back with 420 W load .............................................................14

1.8.2 Performance with heatsink at the back with 500 W.....................................................................15

1.8.3 Performance with heatsink at the front with 500 W..................................................................... 17

Revision history..................................................................................................................................19

User Guide Please read the Important Notice and Warnings at the end of this document Revision 1.0

www.infineon.com 2018-03-01

Page 2

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

D2PAK/ D2PAK-7 kit

1 Full-bridge converter for UPS with D2PAK/D2PAK-7 kit

1.1 Overview

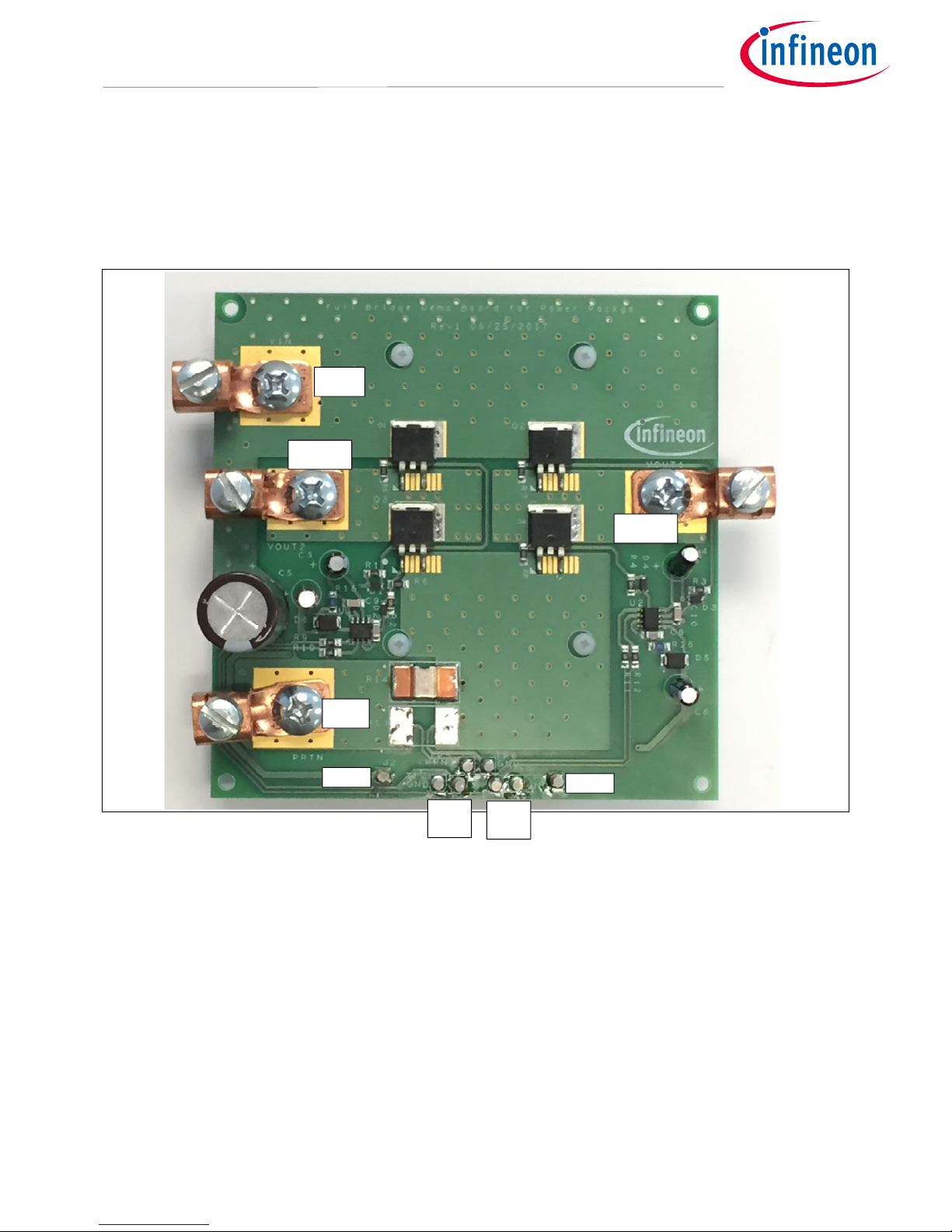

The full-bridge converter kit is a demo board for UPS applications. It contains two sections of half-bridge drivers

and power devices, as shown in Figure 1.

V

in+

V

out2

V

out1

V

in-

V

bias+

- +

PWM1

+ -

PWM2

V

bias-

Figure 1 Full-bridge converter demo board (120 mm × 120 mm)

The demo board needs two power supplies to provide an input voltage and a bias voltage. The voltages of both

power supplies are typically 12 V, which can be changed based on an application. The outputs can be connected

to a transformer. In this user guide, a transformer is used to get an AC voltage of 220 V with the input voltage of

12 V. In order to power up the demo board, two synchronized PWM signals are needed to control switching of

four power MOSFETs.

User Guide 2 Revision 1.0

2018-03-01

Page 3

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

D2PAK/ D2PAK-7 kit

1.1.1 Key features

The capabilities of the full-bridge converter for UPS with D2/D27-pin kit are as follows:

• D2/D27-pin kit for MOSFETs

• Separate Vinand bias voltages (12 V is used in this user guide)

• 600 V gate driver IC with +/- 4 A peak drive current (IRS2186)

• Current Sense (CS) information

• A heatsink can be mounted with four screws, which can be placed at the back or at the front

Figure 2 Heatsink (4 × 2.5 × 0.5 inches) mounted at the front or back with thermal pad

(Heatsink: ACCEL Thermal 914; Thermal pad: Berguist Gap Pad 5000S35, 20 mils)

User Guide 3 Revision 1.0

2018-03-01

Page 4

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

D2PAK/ D2PAK-7 kit

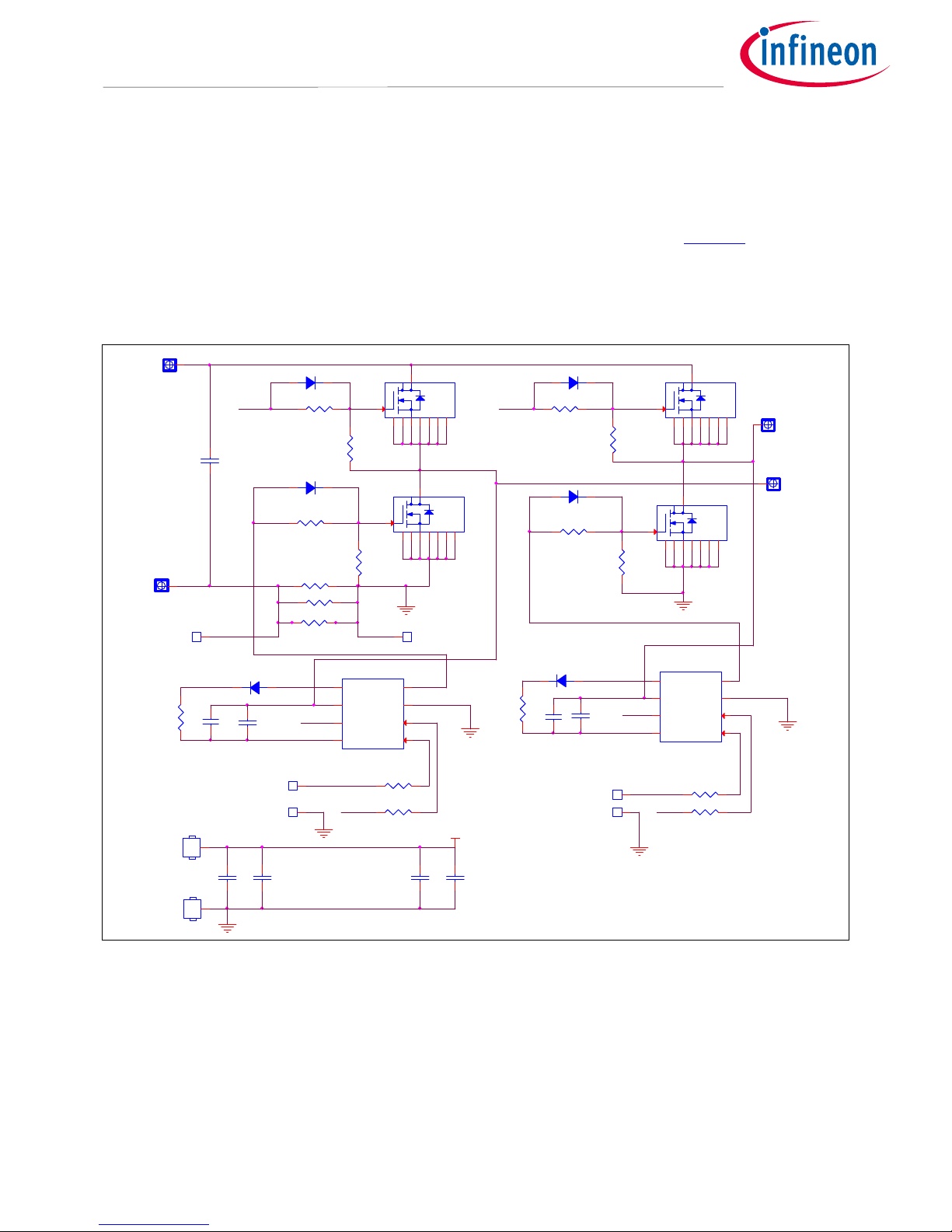

1.2 Schematic

A schematic of the demo board is shown in Figure 3. In the demo board, four MOSFETs (IRFS7430) are used. D27pin packages can be used if they are desired for evaluation. Two IRS2186 drivers are used to drive four MOSFETs.

Only two PWM signals are needed to control timing of the switching of the four MOSFETs. D1~4 four diodes are

used to have a slow turn-off to avoid high Vdsspike during turn-off.

PowerIN

2700uFx50V

PRTN

PRNT

R15

1.2

J2

BIAS +15V

GND

TP5

0.1uF 50V

0.1uF 50V

J3

PowerIN

1 2

1 2

R2

R14

12

BIAS +15V

TP4

C5

47 uF, 35V

R1

R13

R17

VbU1

D1

47

D2

47

1mOhm

open

open

HOV1

PWM2

HOV1

C1

+

PRTN

PRTN

D6

C9

C7

+

47uF, 50V

BIAS+15V

C3

TP3

PWM2

+

GND

G_Q1

R5

10 K

G_Q3

U1

5

Vcc

6

Vs

7

HO

8

Vb

IRS2186SPBF

PWM1

1

1

R6

10 K

LO

COM

LIN

HIN

R9

R10

0.1uF 50V

5.1

5.1

C8

4239567

4239567

TP6

GND

4

3

2

1

Q1

8

IRFS7430

Q3

IRFS7430

8

BIAS +15V

+

Top_Q1_S

R16

C6

47 uF, 35V

1.2

R3 47

D5

C10

0.1uF 50V

1 2

D3

1 2

D4

R4

47

12

C4

+

47 uF, 50V

PWM1

TP1

TP2

GND

R7

10 K

G_Q4

BIAS +15V

HOV2

VbU2

G_Q2HOV2

R8

10 K

PWM1

1

1

U2

5

Vcc

6

Vs

7

HO

8

Vb

IRS2186SPBF

PWM2

4239567

Top_Q2_S

4239567

COM

R11

R12

Q4

IRFS7430

8

LO

LIN

HIN

5.1

5.1

Q2

IRFS7430

8

4

3

2

1

Vout1

Vout2

Figure 3 Schematic of the demo board

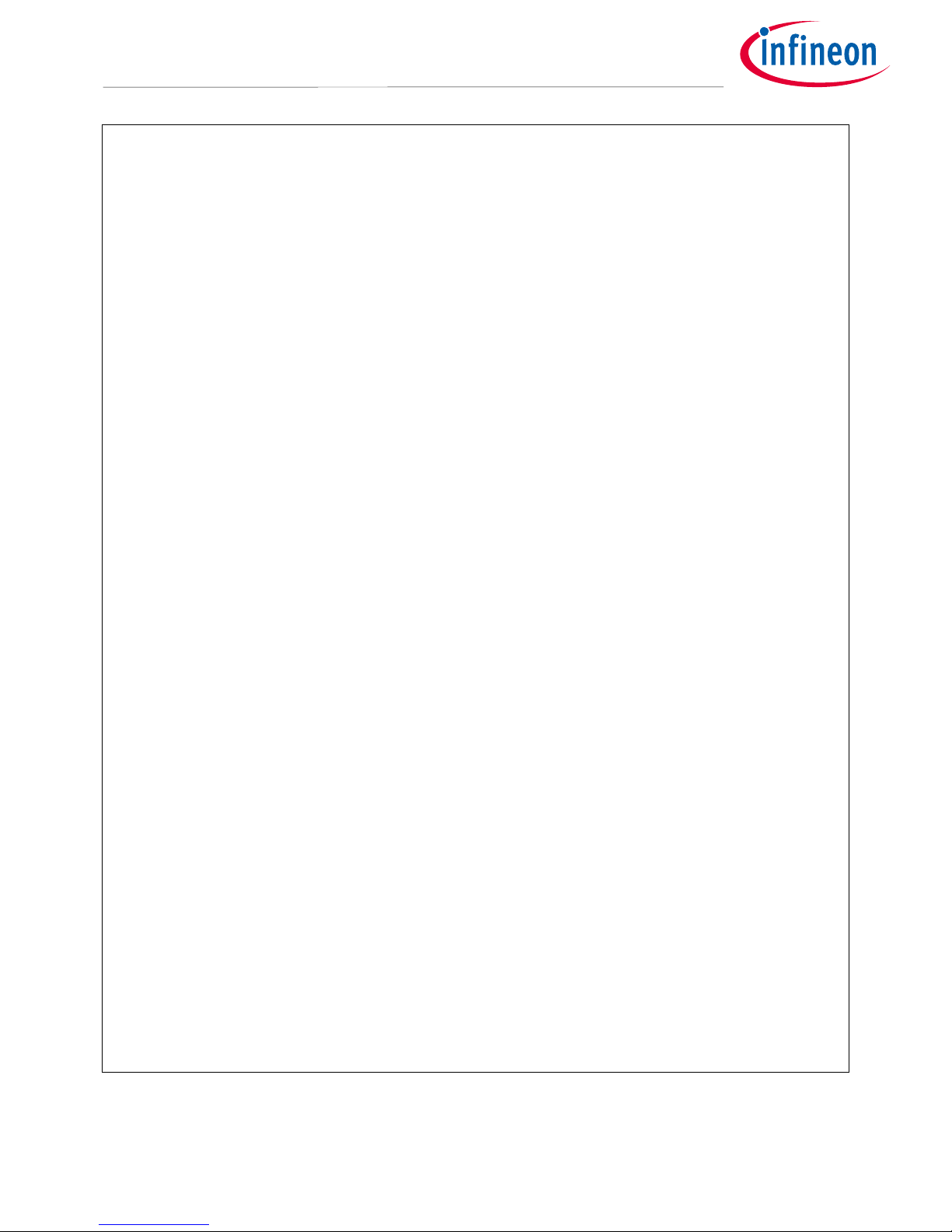

1.3 Layout

The demo board PCB has only two layers, as shown in Figure 4. Fabricated with FR4 material, both layers are 2

oz. copper with a board thickness of 62 mils (1.58 mm).

User Guide 4 Revision 1.0

2018-03-01

Page 5

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

D2PAK/ D2PAK-7 kit

Top

Bottom

Figure 4 PCB top and bottom layers

User Guide 5 Revision 1.0

2018-03-01

Page 6

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

D2PAK/ D2PAK-7 kit

1.4 Power-up procedure

Always connect the bias, two PWM signals and load first, then increase the input voltage from zero.

1.4.1 PWM signal selections

This user guide describes a set-up providing a 50 Hz square-wave AC output. Therefore, both PWM signals are

set with 50 Hz. The dead-time between the two legs has to be set high enough that the reset of the transformer

is completed. A shorter dead-time increases total turn-on time, which may saturate the transformer. A value of

0.9 ms was selected to do the tests. Both PWM signals have an amplitude of 10 V.

1.5 Performance evaluations

Test conditions:

Vin: 12 V

V

: 12 V

bias

PWM 1, 2: 50 Hz, 10 V, with 10 ms delay between them plus 0.7 ms dead-time

Load: Transformer (primary connected to V

bulbs, load of 420 W)

Airflow: No

out1

and V

, secondary connected to incandescent light

out2

1.5.1 Performance with heatsink at the front

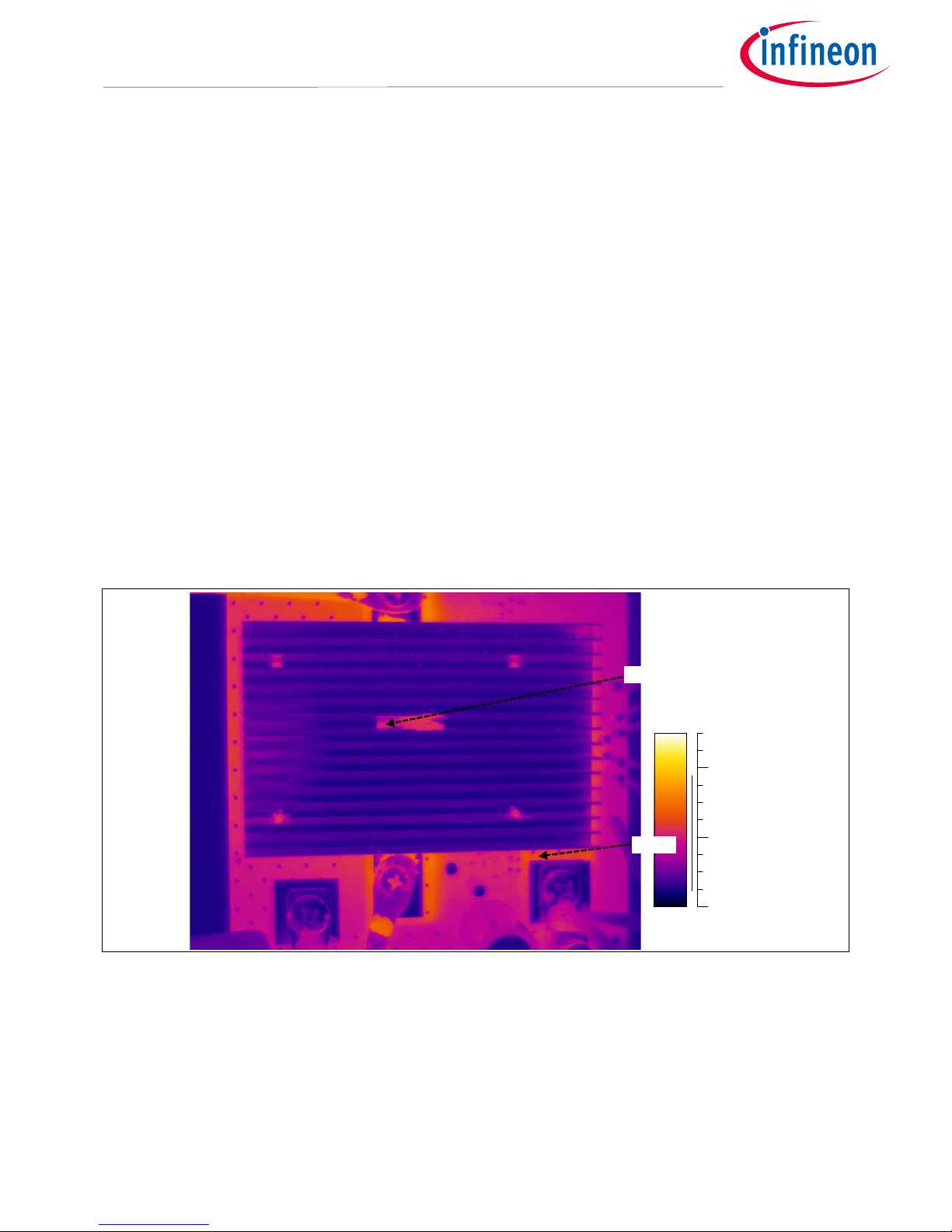

Figure 5 Front thermal image after 1 hour

43°C

A:45°C

70.0°C

60

40

20

20.0°C

User Guide 6 Revision 1.0

2018-03-01

Page 7

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

°

C

Resistor

D2PAK/ D2PAK-7 kit

B:45

70.0°C

60°C

60

Figure 6 Back thermal image after 1 hour

57°C

58°C

(FET)

68°C

40

20

20.0°C

70.0°C

60

40

Figure 7 Side thermal image after 1 hr

Comparing the temperature readings at points A and B between the front and back sides at the corner in Figures

6 and 7 shows that they are the same. Case temperatures of the MOSFETs are 1°C higher at the front than at the

back, as shown in Figures, 6, 7 and 8.

User Guide 7 Revision 1.0

20

20.0°C

2018-03-01

Page 8

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

Efficiency

1

96.5

2

96.5

3

96.5

4

96.7

5

96.6

6

96.7796.3

8

96.3

Ave

rage

96.5

Stdev

0.1

(10 V/div)

D2PAK/ D2PAK-7 kit

C1: Iout (20 A/div)

C2: V

C3: Iin(20 A/div)

C4: Vin(5 V/div)

out2

- V

out1

Figure 8 Typical input and output power measurement after 1 hour

Table 1 Efficiency after 1 hour

No.

(percent)

The average efficiency shown in Table 1 is 96.5 percent at 420 W load. The average total power loss is about 13

W. The reset time for the transformer is about 20 µs, as shown in Figure 9, which is much less than the dead-time

of 700 µs. The MOSFET turn-off waveforms are shown in Figure 10. Since Idswas measured by a Rogowski coil

current probe (C2), its zero level has an offset (I22 = -25 A), as shown in Figure 11. The turn-off switching power

loss can be calculated as:

f(Hz)×∫[()− 22] ∙ ()

= 50 Hz ×|(116 µJ – (25 × 16.7 µ))| = 15 mW.

The turn-off switching power loss for Q2, 3 and 4 is 16, 17 and 13 mW, respectively. Therefore, switching power

losses are negligible.

User Guide 8 Revision 1.0

= f(Hz) × [(F12 - F11 - I22.(F22 - F21)]

2018-03-01

Page 9

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

/div)

ds4

↔

2

0 µs(reset)

/div)

ds_Q1

27VC21=0.27 V (I21 = 27 A)

C22=-

0.25 V (I22 =

-

25 A)

F1:

Integral

of C4 x

C2

(power), F11 = 4.9 µJ, F12 = 121 µJ,

∆F1 = 116 µJ

F2: Integral of C4 (voltage), F21 = 0.19 µV.s, F22 = 16.9 µV.s,

∆F2 = 16.7 µV.s

D2PAK/ D2PAK-7 kit

C1: V

C2: I

C3: V

C4: V

- V

out1

(0.5 A/div)

Ioad

(5 V/div)

ds3

(5 V/div)

Figure 9 Waveforms during the dead-time

out2

(5 V

t1 t2

C1: Itr(20 A/div)

C2: I

C4: V

ds_Q1

(10 A

(5 V/div)

Figure 10 Turn-off waveforms

User Guide 9 Revision 1.0

2018-03-01

Page 10

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

(bottom)

D2PAK/ D2PAK-7 kit

1.5.2 Performance with heatsink at the back

D: 57°C

C:60°C

69°C

70.0°C

54°C

(top)

55°C

A: 46°C

40

20

20.0°C

Figure 11 Front thermal image after 1 hour

As shown in Figure 12, the corner temperature reading (A) is 1°C higher than that with the heatsink at the front in

Figure 6. The corner temperature reading (B) as shown in Figure 13 is 2°C higher than that with the heatsink at

the front in Figure 7. It indicates that the heatsink placed at the front is slightly more effective. Its average

efficiency is 96.4 percent, shown in Table 2, which is 0.1 percent lower than that shown in Table 1 with the

heatsink at the front. The higher efficiency is consistent with lower temperature readings at locations A and B,

shown in Figures 6, 7, 12 and 13.

The PCB temperature readings shown in Figure 12 at locations C and D show 3°C difference, which indicates that

source bond wires result in additional power loss.

60

Figure 12 Back thermal image after 1 hour

User Guide 10 Revision 1.0

B: 47°C

70.0°C

50°C

60

40

20

20.0°C

2018-03-01

Page 11

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

Efficiency

1

96.6

2

96.3

3

96.4

4

96.5

5

96.4

6

96.4

7

96.3

8

96.3

Ave

rage

96.4

Stdev

0.1

No.

R

DS(on)

(mΩ)

1

0.73

2

0.70

3

0.70

4

0.6950.7660.71

7

0.71

Ave

rage

0.72

Stdev

0.02

D2PAK/ D2PAK-7 kit

Table 2 Efficiency after 1 hour

No.

(percent)

1.6 Power loss estimations of MOSFETs and CS resistor

Table 3 shows the average R

is 39.2 A. Therefore, the conduction power loss for each MOSFET can be estimated as 39.22× 0.72/2 = 0.55 W,

which is much higher than the switching loss of 15 mW, shown in Figure 11. Based on the total power loss of 13

W, total MOSFET power loss is about 0.55 × 4/13 = 17 percent.

The power loss of the CS resistor can be estimated as 39.22× 1 = 1.5 W. This is about 12 percent of the total power

loss, which explains why it has the highest case temperature.

at 12 VGSis 0.72 mΩ. As shown in Figure 14, the RMS current for the transformer

DS(on)

Table 3 R

measurements at 12 V

DS(on)

GS

User Guide 11 Revision 1.0

2018-03-01

Page 12

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

A/div)

D2PAK/ D2PAK-7 kit

C1: Itr(20

Figure 13 Transformer RMS current measurement (39.2 A)

User Guide 12 Revision 1.0

2018-03-01

Page 13

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

D2PAK/ D2PAK-7 kit

1.7 Bill of Materials (BOM)

Item Quantity Part reference Part

description

1 1 C1 Electrolytic

Value Part

number

2700 µF, 35 V Nichicon

2700 µF 35 V

2 2 C3, C4, C5, C6 Electrolytic 5 ×

11mm

3 4 C7, C8, C9, C10 0.1 µF × 50 V

1206 C0G

4 4 D1, D2, D3, D4 Diode, 100 VM,

300 MA

47 µF, 35 V UVK1V470

MED

0.1 µF, 50 V CGA5L2C

OG1H104J

1N4148W 1N4148W-

7-F

5 2 D5, D6 Diode, 100 V, 2AMURS 210T3 MURS

210T3

6 8 J2, J3, TP1,

TP2, TP3, TP4,

Test point 218

mils, 90 mils

BIAS +15 V 1502-2 Keystone

TP5, TP6

Manufacture

r

Nichicon

TDK

Diodes Inc.

OnSemi

7 4 PRTN,

POWERIN,

VOUT1,

CONN TERM

RECT LUG 4/02AWG 5/16

VOUT2

8 4 Q1, Q2, Q3,

Q4

MOSFET 40 V,

0.75 mΩ, 305 nC

9 4 R1, R2, R3, R4 Resistor

1206, 1/4 W, 1

percent

10 4 R5, R6, R7, R8 Resistor

1206, 1/4 W, 1

percent

11 4 R9, R10, R11,

R12

Resistor

1206, 1/4 W, 1

percent

12 1 R13 Resistor

4 W

CX225-56HK-QYCXS70-14-CPanduit Corp

IRFS7430-

IRFS7430 Infineon

7PPBF

47 Ω RC1206FR-

Yageo

0747RL

10 k RK73H2BT

KOA

TE1002F

5.1 Ω MCR10EZ

Rohm

HJ5R1

2 mΩ EBWB-

Ohmite

N0020GET

User Guide 13 Revision 1.0

2018-03-01

Page 14

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

Efficiency

1

96.710.64

2

96.720.66396.630.64

(bottom)

D2PAK/ D2PAK-7 kit

13 2 R15, R16 Resistor

1206, 1/4 W, 1

1.2 Ω ESR18EZP

F1R20

Rohm

percent

14 1 R14, R17 - Not fitted Not fitted -

15 2 U1, U2 Hi/Lo gate

IRS2186SPBF IRS2186SPBFInfineon

driver

1.8 Additional results with D2PAK-7 (IRFS7430-7P)

1.8.1 Performance with heatsink at the back with 420 W load

Figure 15 shows temperature readings at the front side with a heatsink at the back. Compared with the readings

shown in Figure 12, the hottest point of the sense resistor is 5°C lower. The PCB reading at point A is 3°C lower,

both top and bottom MOSFETs are 4 to 5°C lower, and at location C the temperature reading is 7°C lower, which

shows that the source bond wires in the D27-pin package result in lower power dissipation. This is consistent with

the higher efficiencies shown in Table 4. Its average is 0.2 percent higher than the example shown in Table 2 with

the same load. Figure 16 also shows lower temperature readings with D27-pin MOSFETs. PCB location B shows

4°C lower temperature and the center 3°C lower than those shown in Figure 13. The lower power dissipation with

D27-pin parts is due to lower R

mΩ lower (11 percent).

, which is shown in Table 5 compared with Table 3. The average R

DS(on)

DS(on)

is 0.07

Figure 14 Front thermal image after 1 hour

Table 4 Efficiency after 1 hour Table 5 R

No.

User Guide 14 Revision 1.0

(percent)

measurement at 12 V

DS(on)

No. R

C: 53°C

64°C

49°C

(top)

51°C

A: 43°C

(mΩ)

DS(on)

70.0°C

60

40

20

20.0°C

GS

2018-03-01

Page 15

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

4

96.540.65

5

96.550.67

6

96.660.65

7

96.770.65

Stdev

0.1

°

C

D2PAK/ D2PAK-7 kit

8 96.6 Average

Average

96.6

Stdev

0.65

0.01

B: 43

47°C

70.0°C

60

40

20

20.0°C

Figure 15 Back thermal image after 1 hour

1.8.2 Performance with heatsink at the back with 500 W

As shown in Figure 17, both case temperature readings at the resistor (78°C) and PCB location A (49°C) are higher

than those (64°C and 44°C) with same parts at 420 W in Figure 15 and also higher than the (69°C and 46°C) with

D2at 420 W in Figure 12. The middle of the heatsink temperature reads 55°C, as shown in Figure 18, and is 5°C

higher than that with D2parts with 420 W, as shown in Figure 13. The average efficiency with D27-pin parts

shown in Table 6 is 97.0 percent, which is 0.4 percent higher than that with 420 W, shown in Table 4.

User Guide 15 Revision 1.0

2018-03-01

Page 16

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

D2PAK/ D2PAK-7 kit

Figure 16 Front thermal image after 1 hour with 500 W

C: 64°C

78°C

(resistor)

60°C

(top)

62°C

(bottom)

A: 49°C

Figure 17 Back thermal image after 1 hour with 500 W

B: 49°C

55°C

User Guide 16 Revision 1.0

2018-03-01

Page 17

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

1

97.1

2

97.0

3

97.1

4

96.9597.0697.1

7

97.0

8

97.1

Ave

rage

97.0

Stdev

0.1

Efficiency

1

96.9

2

96.9

3

97.1

4

97.1

5

97.1

6

96.9

7

97.0

8

96.9

Ave

rage

97.0

Stdev

0.1

D2PAK/ D2PAK-7 kit

Table 6 Efficiency after 1 hour

No.

Efficiency

(percent)

1.8.3 Performance with heatsink at the front with 500 W

As shown in Table 7, the average efficiency is 97 percent, which is 0.4 percent higher than that with the heatsink

at the back, shown in Table 4. The temperature readings at the middle (47°C) and location A (52°C) shown in

Figure 19 are both higher than those (43°C and 45°C) shown in Figure 6 due to the additional 80 W of load.

With the same load at 500 W, the temperature reading (52°C) at A shown in Figure 19 is higher than that (49°C) in

Figure 17, while the reading (48°C) at B in Figure 20 is lower than that (49°C) in Figure 18. This behavior is

different to that with D2MOSFETs. The reason is that with the D27-pin package more heat can be transferred to

the PCB, which makes the heatsink more effective when it is located at the back. This explains why the efficiency

with the heatsink at the front is the same as that with the heatsink at the back with D27-pin MOSFETs.

Table 7 Efficiency after 1 hour

No.

(percent)

User Guide 17 Revision 1.0

2018-03-01

Page 18

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

C

°

C

D2PAK/ D2PAK-7 kit

47°C

80.0°C

80

60

Figure 18 Front thermal image after 1 hour

A: 52°

B:48

69°C

65°C

40

20

20.0°C

80.0°C

80

60

40

Figure 19 Back thermal image after 1 hour

User Guide 18 Revision 1.0

20

20.0°C

2018-03-01

Page 19

Full-bridge converter for UPS

UG_1801_PL16_1802_225559

D2PAK/ D2PAK-7 kit

Revision history

Major changes since the last revision.

Page or reference Description of change

User Guide 19 Revision 1.0

2018-03-01

Page 20

Trademarks of Infineon Technologies AG

DrBlade™,

Infineon™,

ISOFACE™, IsoPACK™,

OptiMOS™, ORIGA™, POWERCODE™, PRIMARION™, PrimePACK™,

SPOC™,

AURIX™, C166™, CanPAK™, CIPOS™, CoolGaN™, CoolMOS™, CoolSET™, CoolSiC™, CORECONTROL™, CROSSAVE™, DAVE™, DI-POL™,

EasyPIM™, EconoBRIDGE™, EconoDUAL™, EconoPACK™, EconoPIM™, EiceDRIVER™, eupec™, FCOS™, HITFET™, HybridPACK™,

i-Wafer™, MIPAQ™, ModSTACK™, my-d™, NovalithIC™, OmniTune™, OPTIGA™,

PrimeSTACK™, PROFET™, PRO-SIL™, RASIC™, REAL3™, ReverSave™, SatRIC™, SIEGET™, SIPMOS™, SmartLEWIS™, SOLID FLASH™,

TEMPFET™, thinQ!™, TRENCHSTOP™, TriCore™.

Trademarks updated August 2015

Other Trademarks

All referenced product or service names and trademarks are the property of their respective owners.

IMPORTANT NOTICE

Edition 2018-03-01

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2018 Infineon Technologies AG.

All Rights Reserved.

Do you have a question about this

document?

Email: erratum@infineon.com

Document reference

UG_1801_PL16_1802_225559

The information contained in this application note is

given as a hint for the implementation of the

product only and shall in no event be regarded as a

description or warranty of a certain functionality,

condition or quality of the product. Before

implementation of the product, the recipient of this

application note must verify any function and other

technical information given herein in the real

application. Infineon Technologies hereby disclaims

any and all warranties and liabilities of any kind

(including without limitation warranties of noninfringement of intellectual property rights of any

third party) with respect to any and all information

given in this application note.

The data contained in this document is exclusively

intended for technically trained staff. It is the

responsibility of customer’s technical departments

to evaluate the suitability of the product for the

intended application and the completeness of the

product information given in this document with

respect to such application.

For further information on the product, technology,

delivery terms and conditions and prices please

contact your nearest Infineon Technologies office

(www.infineon.com).

WARNINGS

Due to technical requirements products may contain

dangerous substances. For information on the types

in question please contact your nearest Infineon

Technologies office.

Except as otherwise explicitly approved by Infineon

Technologies in a written document signed by

authorized representatives of Infineon

Technologies, Infineon Technologies’ products may

not be used in any applications where a failure of the

product or any consequences of the use thereof can

reasonably be expected to result in personal injury.

Loading...

Loading...