Data Sheet, V2.2, Aug. 2001

C167CS-4R

C167CS-L

16-Bit Single-Chip Microcontroller

Microcontrollers

Never stop thinking.

Edition 2001-08

Published by Infineon Technologies AG,

St.-Martin-Strasse 53,

D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

Attention please!

The information herein is given to describe certain components and shall not be considered as warranted

characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding

circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

Information

For further information on technology, delivery terms and conditions and prices please contact your nearest

Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide.

Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in

question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written

approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure

of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support

devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may

be endangered.

Data Sheet, V2.2, Aug. 2001

C167CS-4R

C167CS-L

16-Bit Single-Chip Microcontroller

Microcontrollers

Never stop thinking.

C167CS

Revision History: 2001-08 V2.2

Previous Version: 2000-12 V2.1 (Intermediate version)

2000-06 V2.0

1999-06

1999-03 (Advance Information)

Page Subjects (major changes from V2.1, 2000-12 to V2.2, 2001-08)

4Figure2 corrected (pins 98, 99)

25, 27 Figure 5 and Figure 6 updated

50ff Output voltage/current specification improved

52f Limit values for

IDO

and I

increased due to the usage of a standard

PDR

I

oscillator

54 Figure 10 corrected

57 Figure 12 updated for 40 MHz

59 Clock parameters adjusted

60 TUE note includes P1H

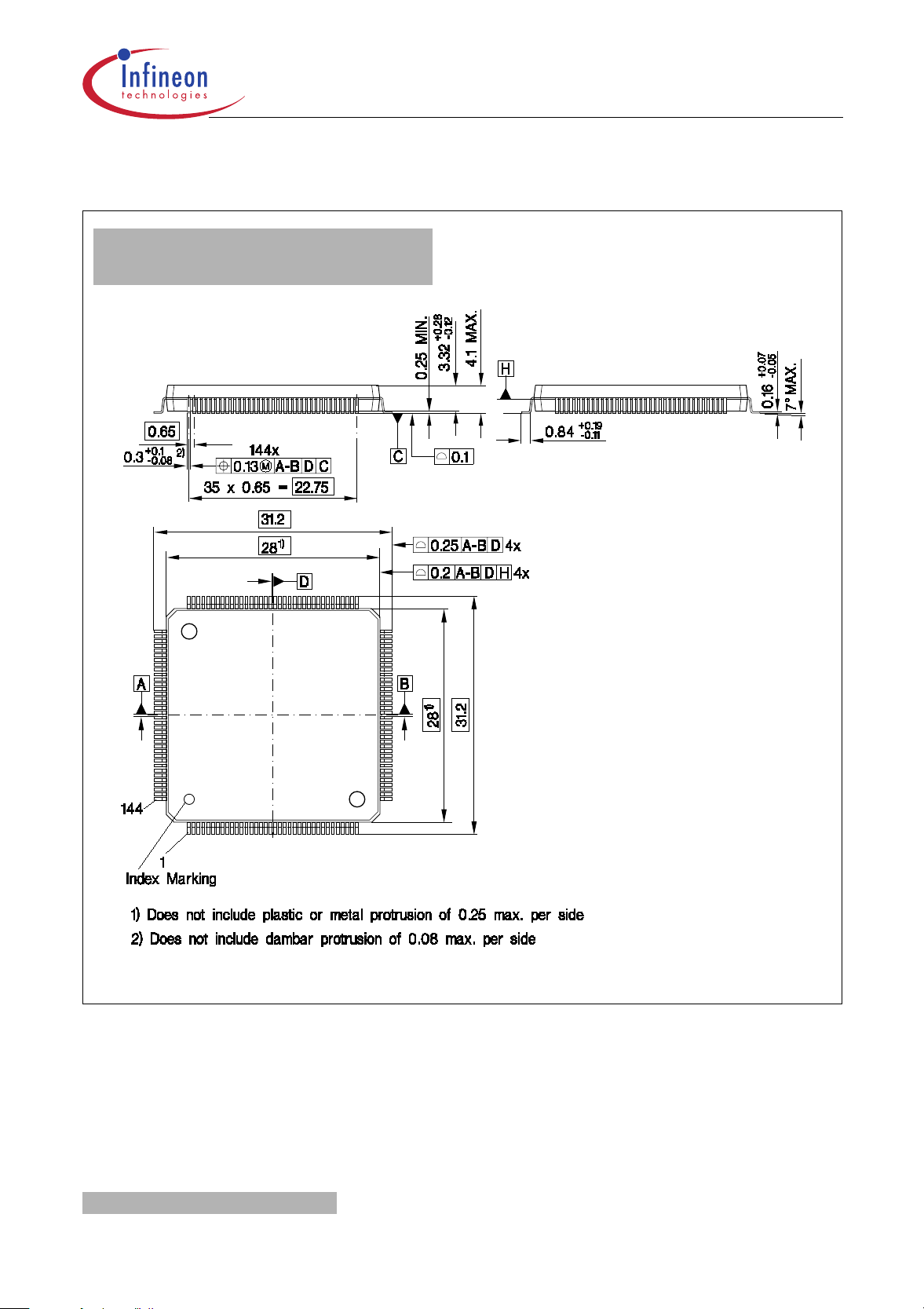

76 Package drawing updated

1)

Page Subjects (major changes from V2.0, 2000-06 to V2.1, 2000-12)

All Maximum operating frequency updated to 40 MHz

2 Derivative table updated

52 RSTIN

level for IDD corrected to VIL (was V

53 Current unit corrected to

µA

IL2

)

56 Input clock range adjusted

60f Note 5 detailed

tc

64 Parameters

, tc12, tc13, tc14, tc15, tc16, tc17, tc18, tc19 changed

10

65 Relative bus timing parameters added

tc

70 Parameter

changed, notes adapted

25

71 Notes adapted

72 Parameter tc

changed

28

t

75 Parameters

1)

New package due to new assembly line. MQFP-144-1 for current deliveries only, will be discontinued.

, t43, t44, t46, t47 changed

42

Controller Area Network (CAN): License of Robert Bosch GmbH

We Listen to Your Comments

Any information within this document that you feel is wrong, unclear or missing at all?

Your feedback will help us to continuously improve the quality of this document.

Please send your proposal (including a reference to this document) to:

mcdocu.comments@infineon.com

C167CS16-Bit Single-Chip Microcontroller

C166 Family

C167CS-4R, C167CS-L

• High Performance 16-bit CPU with 4-Stage Pipeline

– 80/60/50 ns Instruction Cycle Time at 25/33/40 MHz CPU Clock

– 400/303/250 ns Multiplication (16

– Enhanced Boolean Bit Manipulation Facilities

– Additional Instructions to Support HLL and Operating Systems

– Register-Based Design with Multiple Variable Register Banks

– Single-Cycle Context Switching Support

– 16 MBytes Total Linear Address Space for Code and Data

– 1024 Bytes On-Chip Special Function Register Area

• 16-Priority-Level Interrupt System with 56 Sources, Sample-Rate down to 40/30/25 ns

• 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via

Peripheral Event Controller (PEC)

• Clock Generation via on-chip PLL (factors 1:1.5/2/2.5/3/4/5),

via prescaler or via direct clock input

• On-Chip Memory Modules

– 3 KBytes On-Chip Internal RAM (IRAM)

– 8 KBytes On-Chip Extension RAM (XRAM)

– 32 KBytes On-Chip Program Mask ROM

• On-Chip Peripheral Modules

– 24-Channel 10-bit A/D Converter with Programmable Conversion Time

down to 7.8

– Two 16-Channel Capture/Compare Units

– 4-Channel PWM Unit

– Two Multi-Functional General Purpose Timer Units with 5 Timers

– Two Serial Channels (Synchronous/Asynchronous and High-Speed-Synchronous)

– Two On-Chip CAN Interfaces (Rev. 2.0B active) with 2

(Full CAN/Basic CAN), can work on one bus with 30 objects

– On-Chip Real Time Clock

• Up to 16 MBytes External Address Space for Code and Data

– Programmable External Bus Characteristics for Different Address Ranges

– Multiplexed or Demultiplexed External Address/Data Buses with 8-Bit or 16-Bit

Data Bus Width

– Five Programmable Chip-Select Signals

– Hold- and Hold-Acknowledge Bus Arbitration Support

• Idle, Sleep, and Power Down Modes with Flexible Power Management

• Programmable Watchdog Timer and Oscillator Watchdog

• Up to 111 General Purpose I/O Lines,

partly with Selectable Input Thresholds and Hysteresis

µs

× 16 bit), 800/606/500 ns Division (32-/16-bit)

× 15 Message Objects

Data Sheet 1 V2.2, 2001-08

C167CS-4R

C167CS-L

• Supported by a Large Range of Development Tools like C-Compilers,

Macro-Assembler Packages, Emulators, Evaluation Boards, HLL-Debuggers,

Simulators, Logic Analyzer Disassemblers, Programming Boards

• On-Chip Bootstrap Loader

• 144-Pin MQFP Package

This document describes several derivatives of the C167 group. Table 1 enumerates

these derivatives and summarizes the differences. As this document refers to all of these

derivatives, some descriptions may not apply to a specific product.

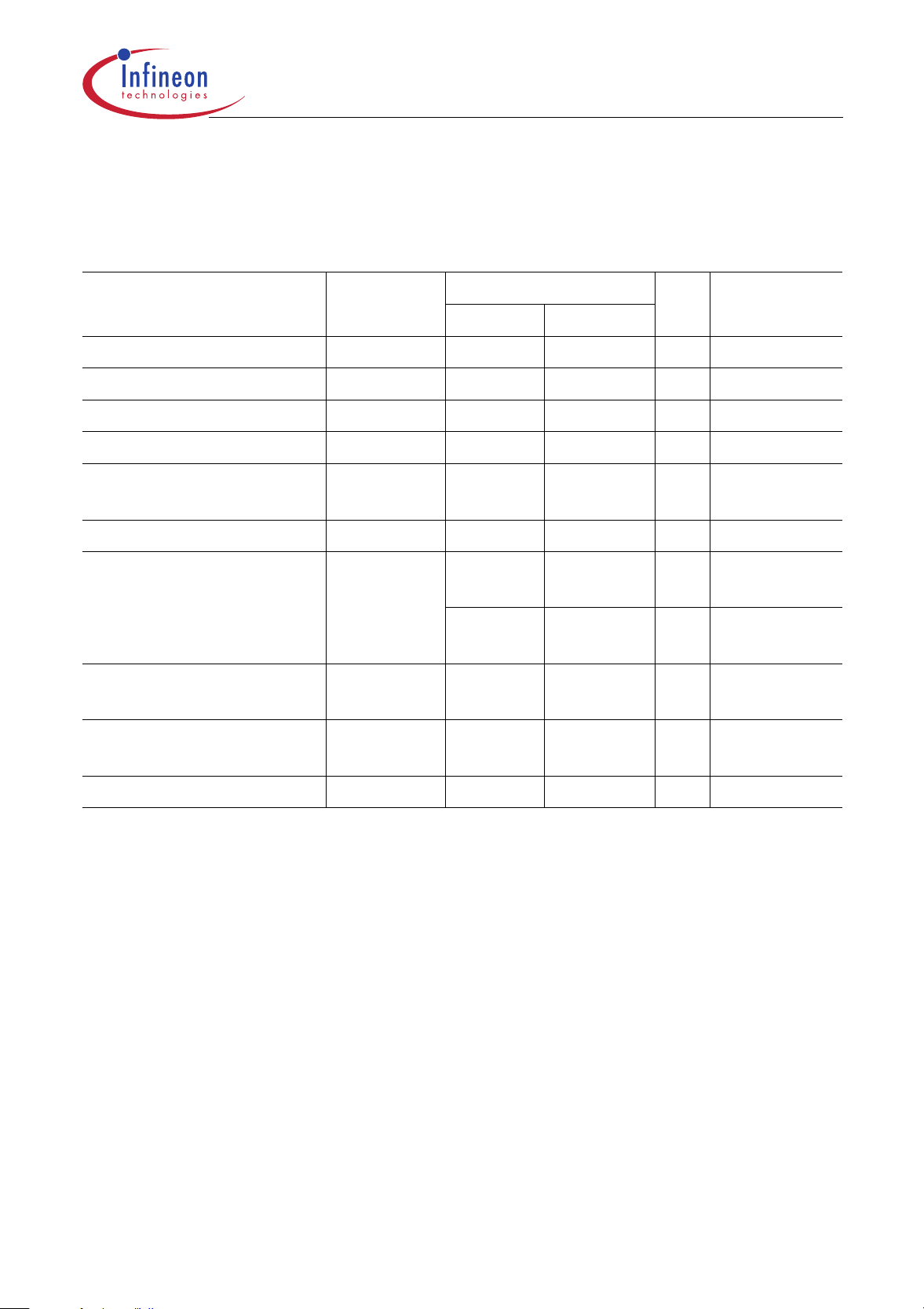

Table 1 C167CS Derivative Synopsis

Derivative

1)

Program Memory Operating Frequency

SAK-C167CS-LM

--- 25 MHz

SAB-C167CS-LM

SAK-C167CS-L33M

--- 33 MHz

SAB-C167CS-L33M

SAK-C167CS-L40M

--- 40 MHz

SAB-C167CS-L40M

SAK-C167CS-4RM

32 KByte ROM 25 MHz

SAB-C167CS-4RM

SAK-C167CS-4R33M

32 KByte ROM 33 MHz

SAB-C167CS-4R33M

SAK-C167CS-4R40M

32 KByte ROM 40 MHz

SAB-C167CS-4R40M

1)

This Data Sheet is valid for devices starting with and including design step BA.

For simplicity all versions are referred to by the term C167CS throughout this document.

Data Sheet 2 V2.2, 2001-08

C167CS-4R

C167CS-L

Ordering Information

The ordering code for Infineon microcontrollers provides an exact reference to the

required product. This ordering code identifies:

• the derivative itself, i.e. its function set, the temperature range, and the supply voltage

• the package and the type of delivery.

For the available ordering codes for the C167CS please refer to the “Product Catalog

Microcontrollers”, which summarizes all available microcontroller variants.

Note: The ordering codes for Mask-ROM versions are defined for each product after

verification of the respective ROM code.

Introduction

The C167CS derivatives are high performance derivatives of the Infineon C166 Family

of full featured single-chip CMOS microcontrollers. They combine high CPU

performance (up to 20 million instructions per second) with high peripheral functionality

and enhanced IO-capabilities. They also provide clock generation via PLL and various

on-chip memory modules such as program ROM, internal RAM, and extension RAM.

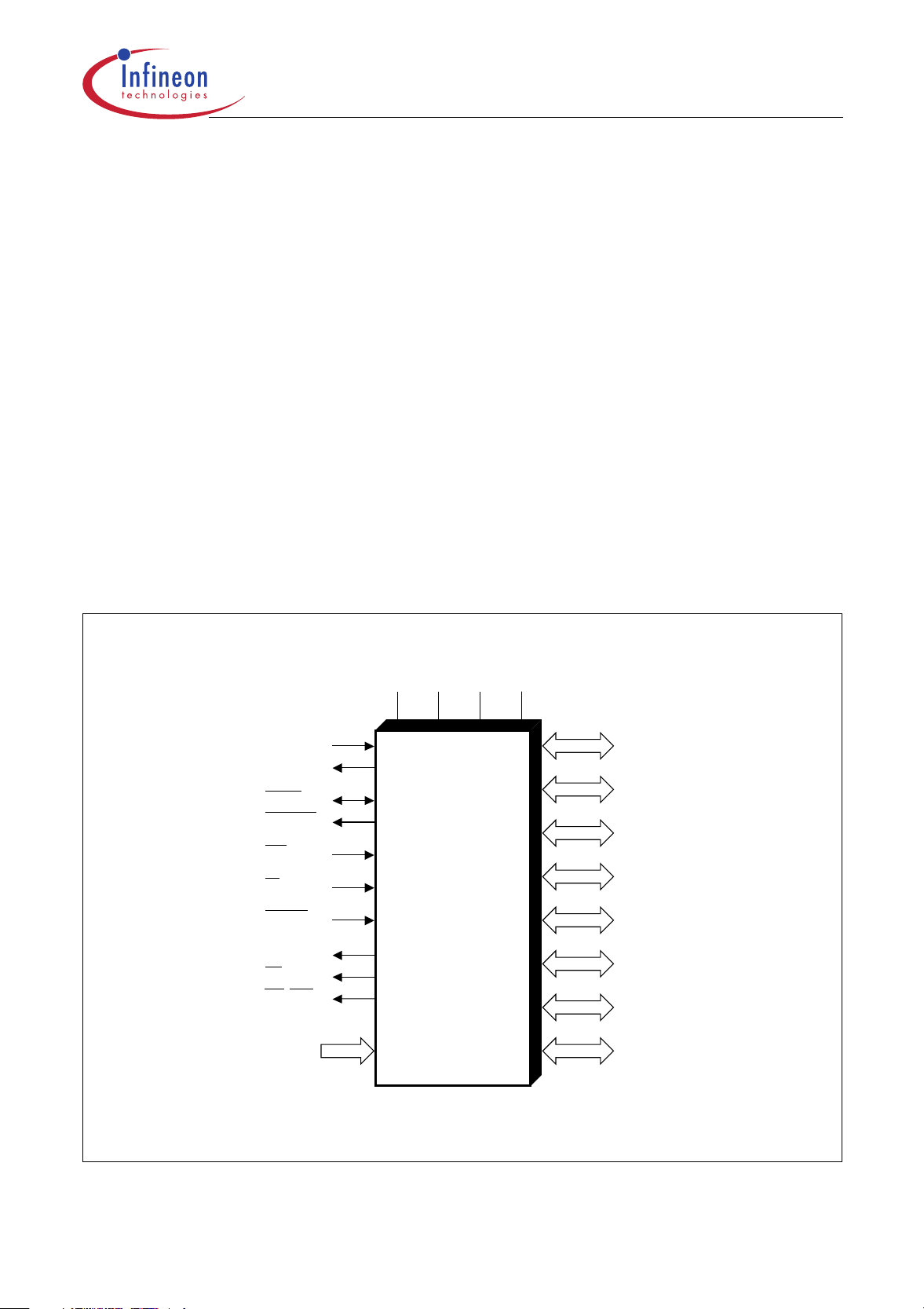

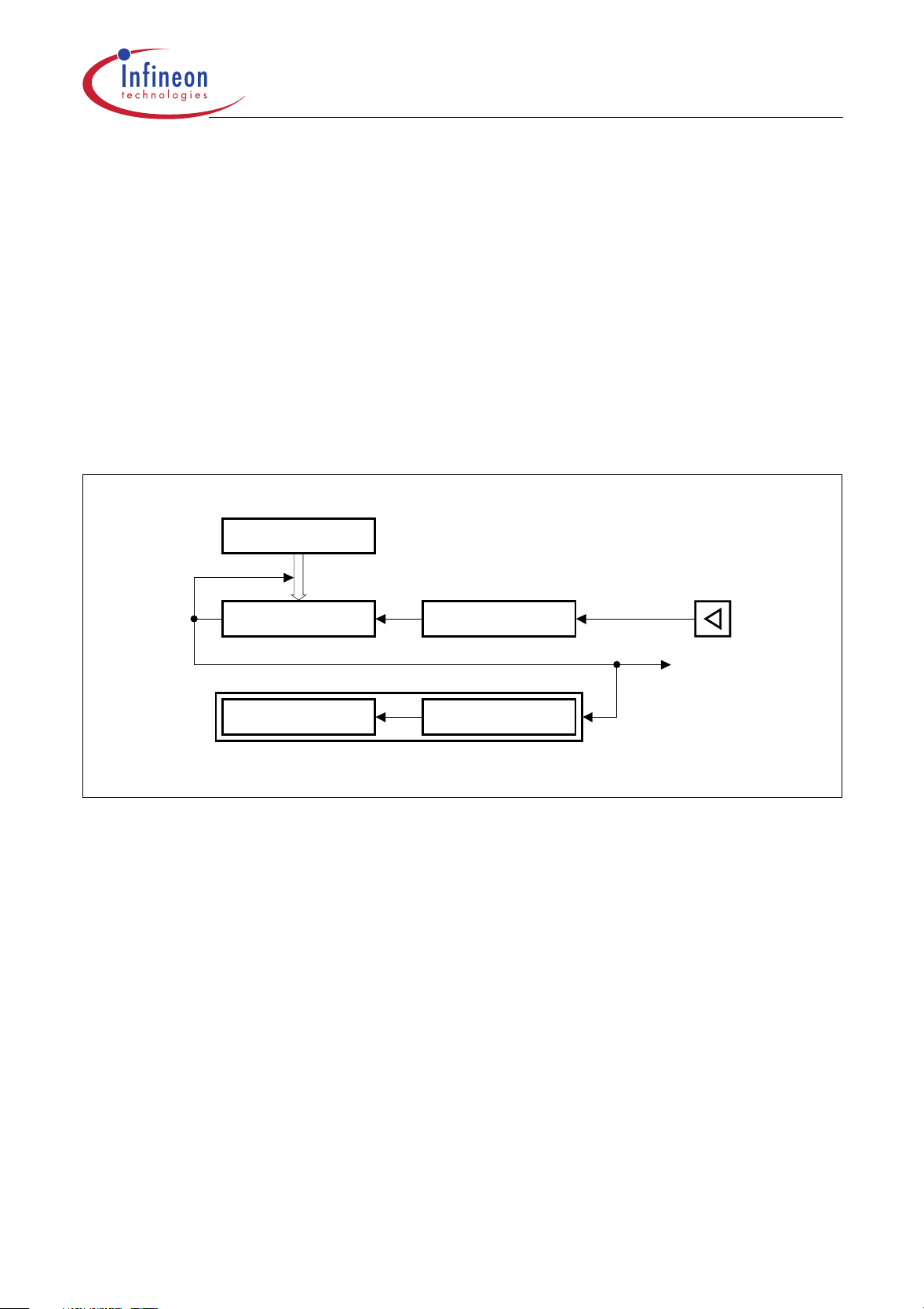

XTAL1

XTAL2

RSTIN

RSTOUT

NMI

EA

READY

ALE

RD

WR/WRL

Port 5

16 Bit

V

V

AREF AGND

C167CS

V

DDVSS

MCL04411

Port 0

16 Bit

Port 1

16 Bit

Port 2

16 Bit

Port 3

15 Bit

Port 4

8 Bit

Port 6

8 Bit

Port 7

8 Bit

Port 8

8 Bit

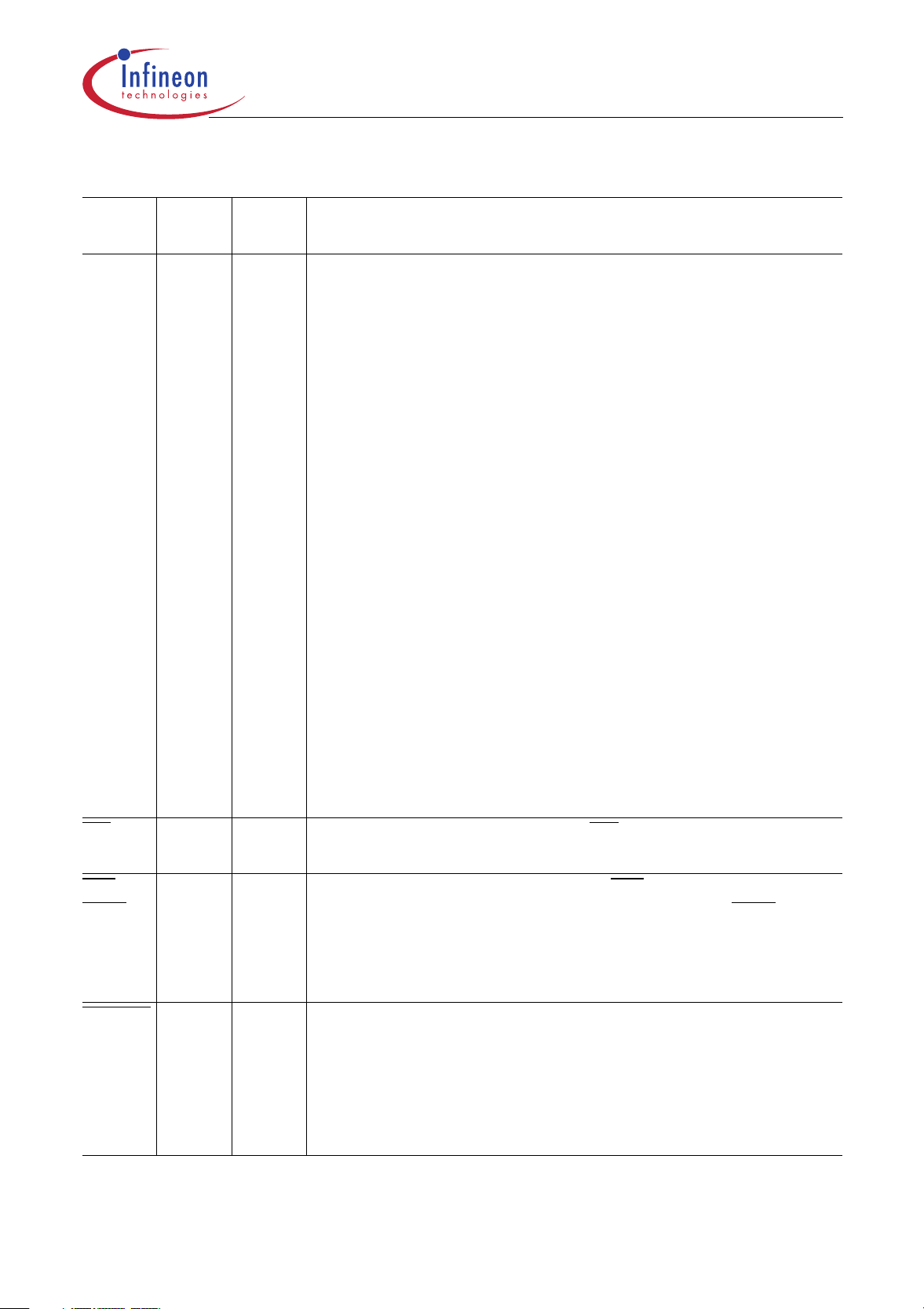

Figure 1 Logic Symbol

Data Sheet 3 V2.2, 2001-08

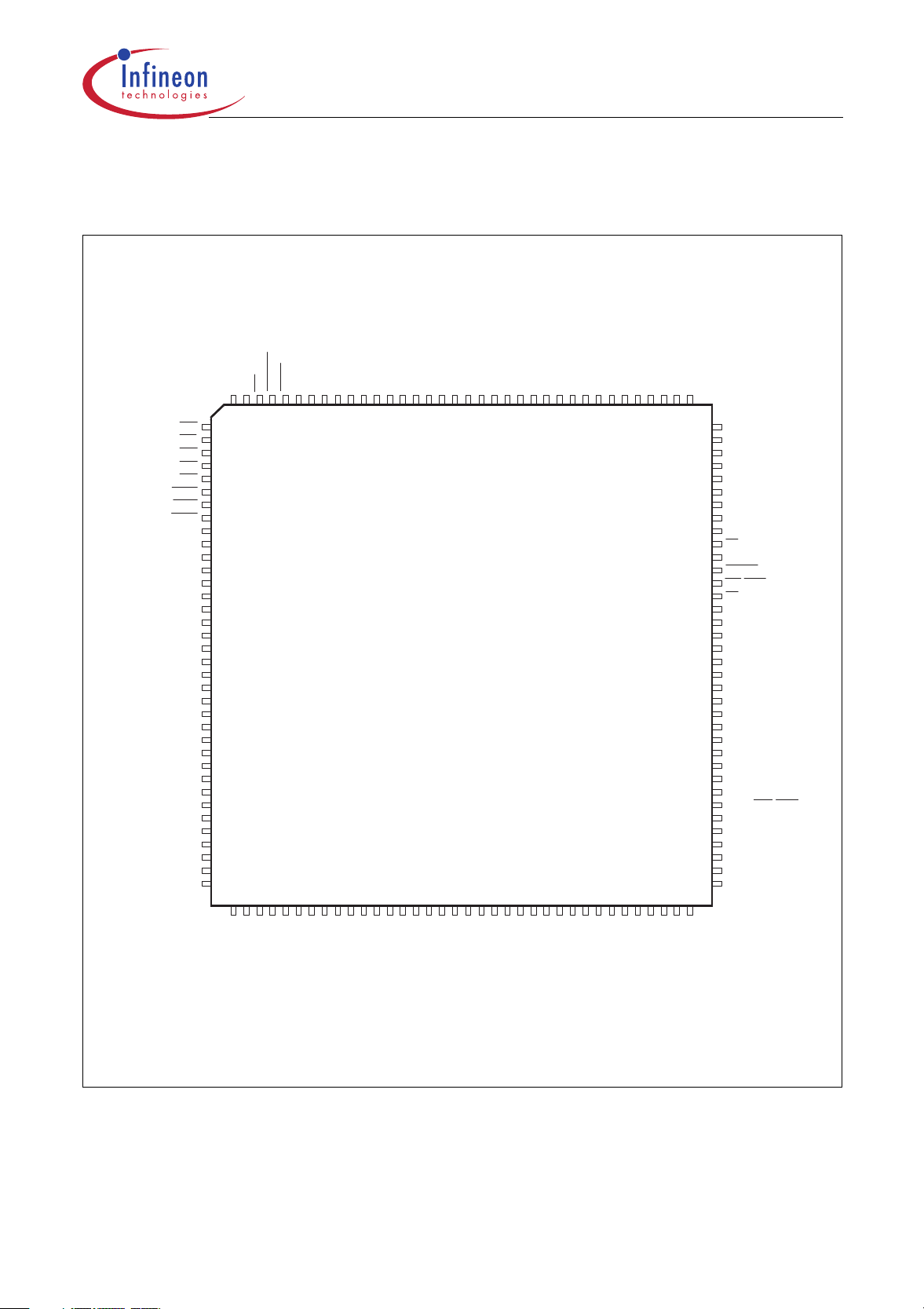

Pin Configuration

(top view)

C167CS-4R

C167CS-L

P6.0/CS0

P6.1/CS1

P6.2/CS2

P6.3/CS3

P6.4/CS4

P6.5/HOLD

P6.6/HLDA

P6.7/BREQ

*P8.0/CC16IO

*P8.1/CC17IO

*P8.2/CC18IO

*P8.3/CC19IO

P8.4/CC20IO

P8.5/CC21IO

P8.6/CC22IO

P8.7/CC23IO

V

V

P7.0/POUT0

P7.1/POUT1

P7.2/POUT2

P7.3/POUT3

P7.4/CC28IO

P7.5/CC29IO

P7.6/CC30IO

P7.7/CC31IO

P5.0/AN0

P5.1/AN1

P5.2/AN2

P5.3/AN3

P5.4/AN4

P5.5/AN5

P5.6/AN6

P5.7/AN7

P5.8/AN8

P5.9/AN9

D

S

D

S

V

V

NMI

RSTOUT

RSTIN

144

143

141

140

1

142

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

DD

18

SS

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

373839

404142

D

EF

N

R

G

A

A

V

V

P5.12/AN12/T6IN

P5.10/AN10/T6EUD

P5.11/AN11/T5EUD

D

S

S

D

V

XTAL1

V

P1H.7/A15/CC27IO

XTAL2

138

137

139

P5.13/AN13/T5IN

135

136

434445

464748

S

D

S

D

V

V

P5.14/AN14/T4EUD

P5.15/AN15/T2EUD

P1H.6/A14/CC26IO

P1H.5/A13/CC25IO

P1H.4/A12/CC24IO

P1H.3/A11

P1H.2/A10

P1H.1/A9

134

132

131

130

129

133

C167CS

495051

525354

P2.0/CC0IO

P2.1/CC1IO

P2.2/CC2IO

P2.3/CC3IO

P2.4/CC4IO

P2.5/CC5IO

D

S

S

D

V

V

P1H.0/A8

128

126

127

555657

S

S

V

P2.6/CC6IO

P2.7/CC7IO

P1L.7/A7/AN23

P1L.6/A6/AN22

P1L.5/A5/AN21

P1L.4/A4/AN20

P1L.3/A3/AN19

125

123

122

124

121

585960

D

D

V

P2.8/CC8IO/EX0IN

P2.9/CC9IO/EX1IN

P2.10/CC10IO/EX2IN

P2.11/CC11IO/EX3IN

P1L.2/A2/AN18

P1L.1/A1/AN17

P1L.0/A0/AN16

P0H.7/AD15

P0H.6/AD14

P0H.5/AD13

P0H.4/AD12

120

119

117

116

646566

P3.0/T0IN

114

115

676869

P3.2/CAPIN

P3.1/T6OUT

118

616263

P2.12/CC12IO/EX4IN

P2.13/CC13IO/EX5IN

P2.14/CC14IO/EX6IN

P2.15/CC15IO/EX7IN/T7IN

V

P0H.3/AD11

P0H.2/AD10

P0H.1/AD9

113

111

110

112

707172

V

P3.5/T4IN

P3.3/T3OUT

P3.4/T3EUD

D

S

S

D

V

109

108

107

106

105

104

103

102

101

100

S

D

S

D

V

P0H.0/AD8

P0L.7/AD7

P0L.6/AD6

P0L.5/AD5

P0L.4/AD4

P0L.3/AD3

P0L.2/AD2

P0L.1/AD1

P0L.0/AD0

99

EA

98

ALE

97

READY

96

WR/WRL

95

RD

94

V

93

V

P4.7/A23/*

92

91

P4.6/A22/*

90

P4.5/A21/*

89

P4.4/A20/*

88

P4.3/A19

87

P4.2/A18

86

P4.1/A17

85

P4.0/A16

84

N.C.

83

V

82

V

P3.15/CLKOUT/

81

FOUT

P3.13/SCLK

80

79

P3.12/BHE/WRH

78

P3.111/RxD0

77

P3.10/TxD0

76

P3.9/MTSR

75

P3.8/MRST

74

P3.7/T2IN

73

P3.6/T3IN

SS

DD

SS

DD

MCP04431

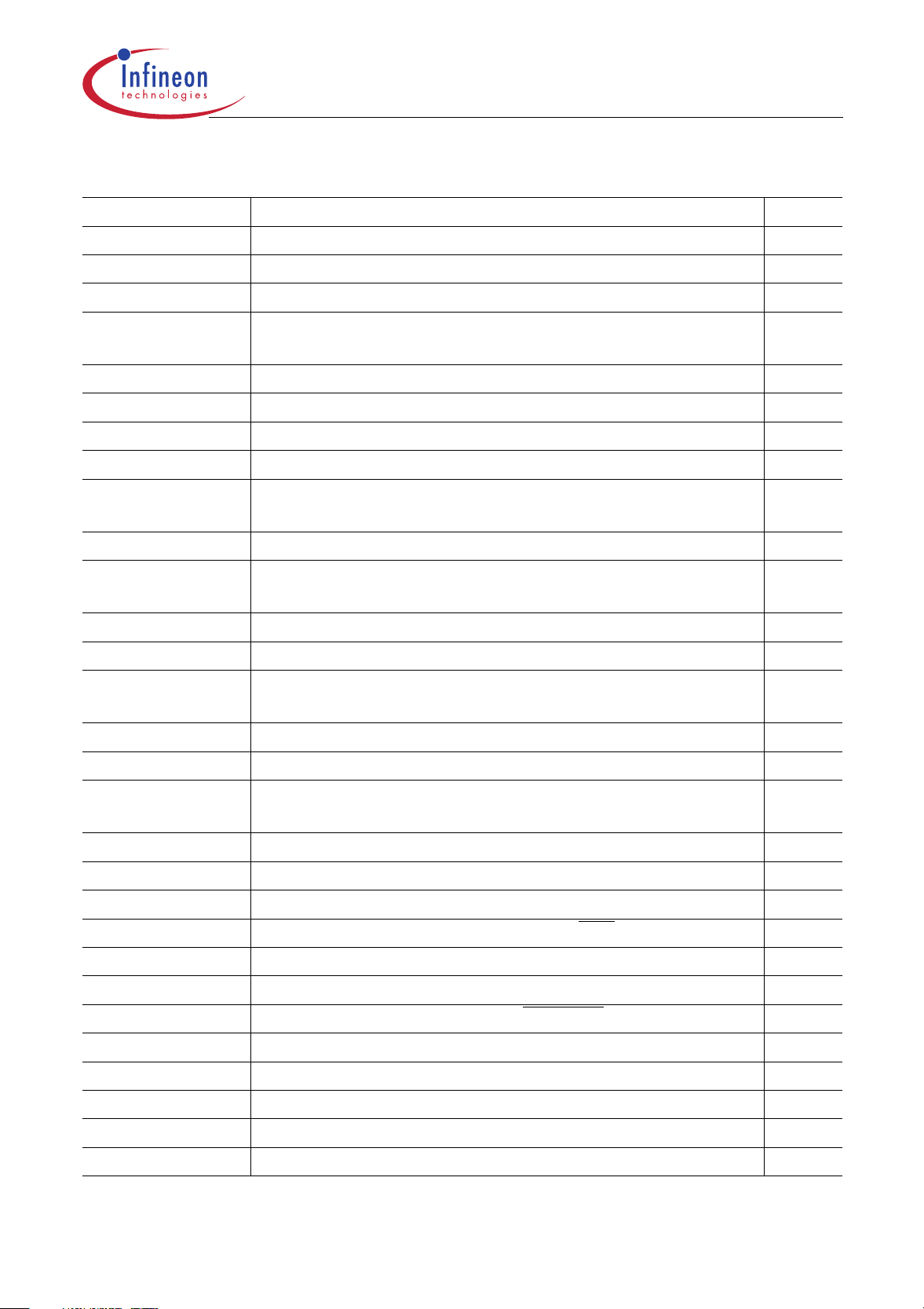

Figure 2

*) The marked pins of Port 4 and Port 8 can have CAN interface lines assigned to them.

Table 2 on the pages below lists the possible assignments.

Data Sheet 4 V2.2, 2001-08

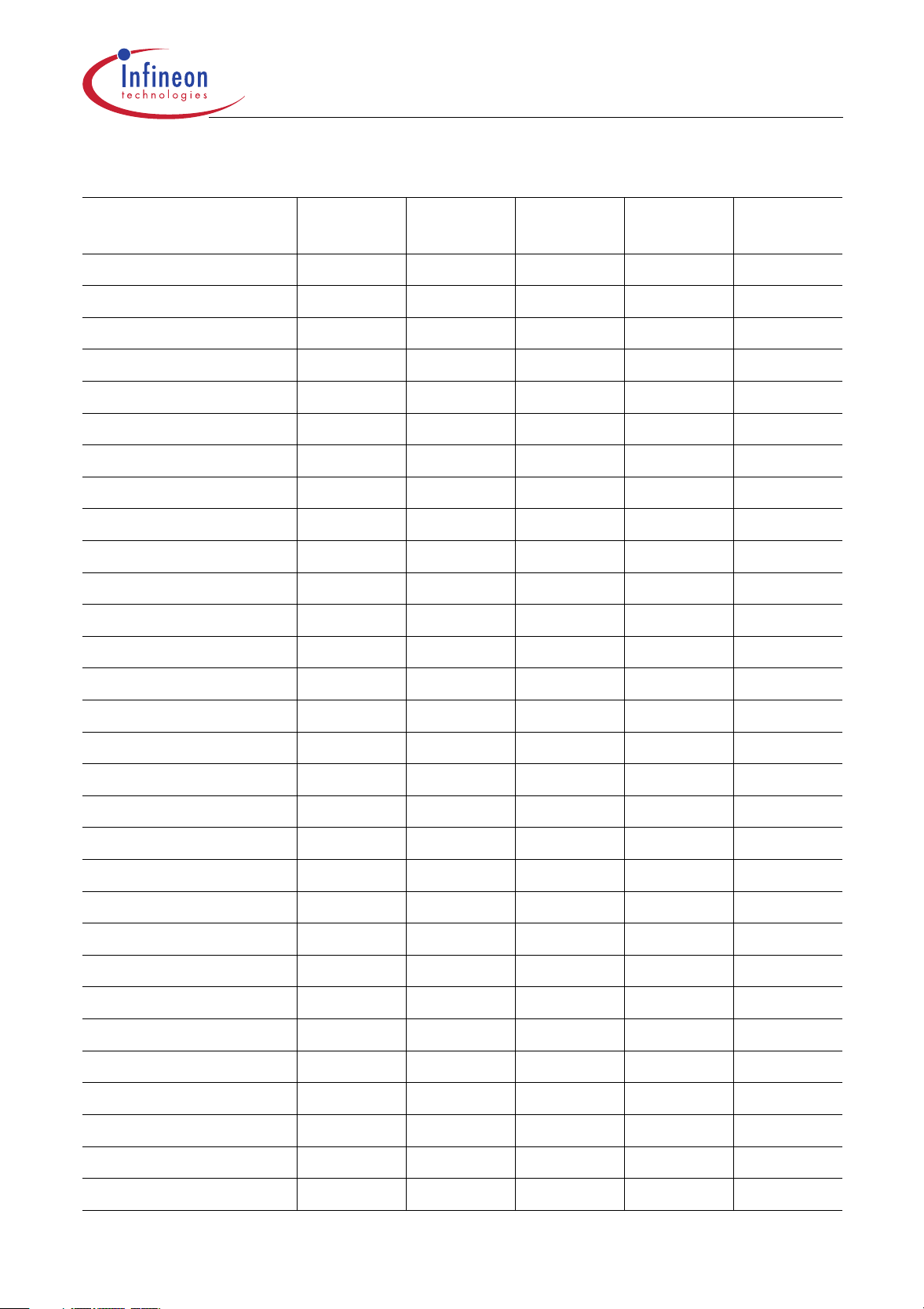

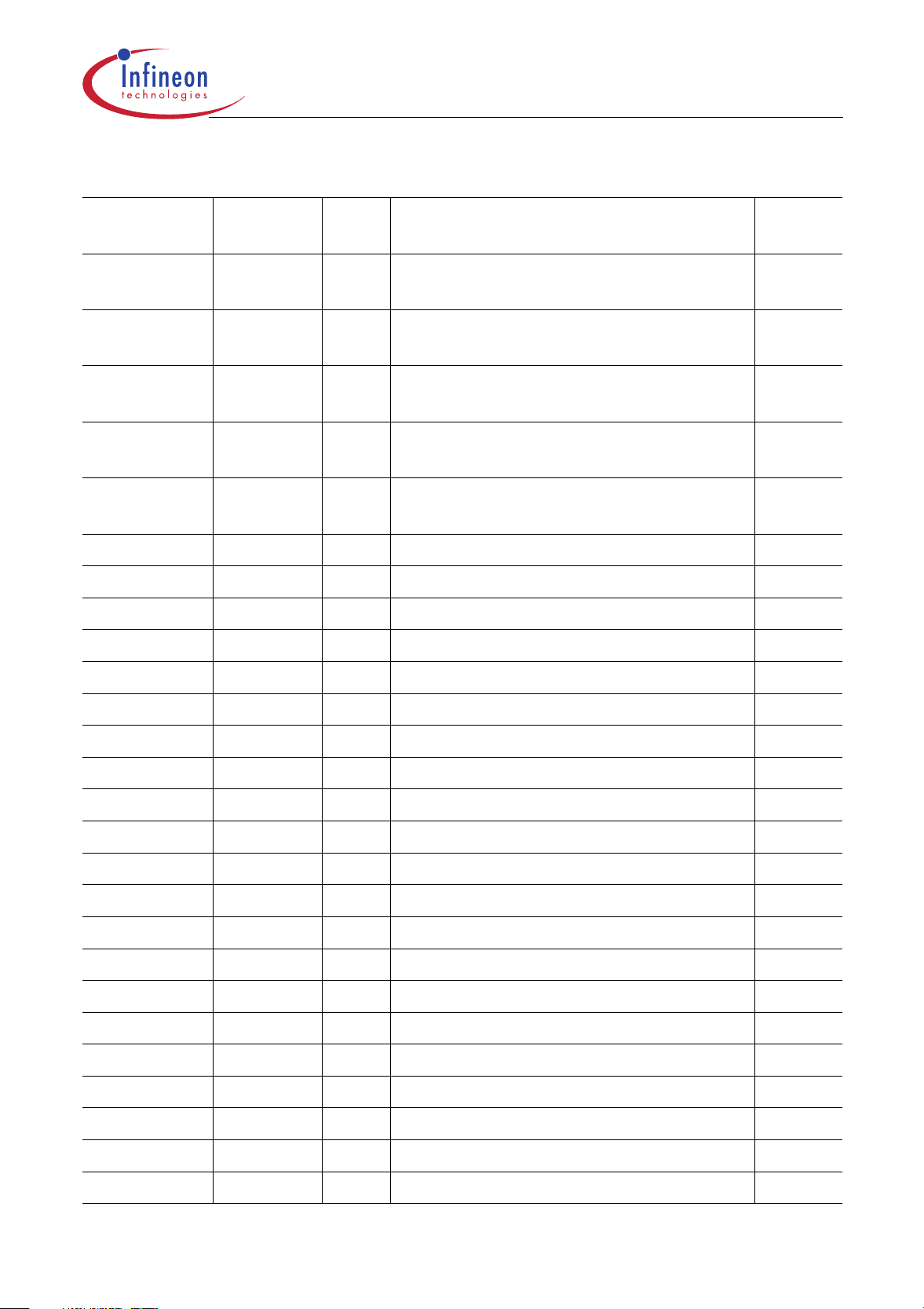

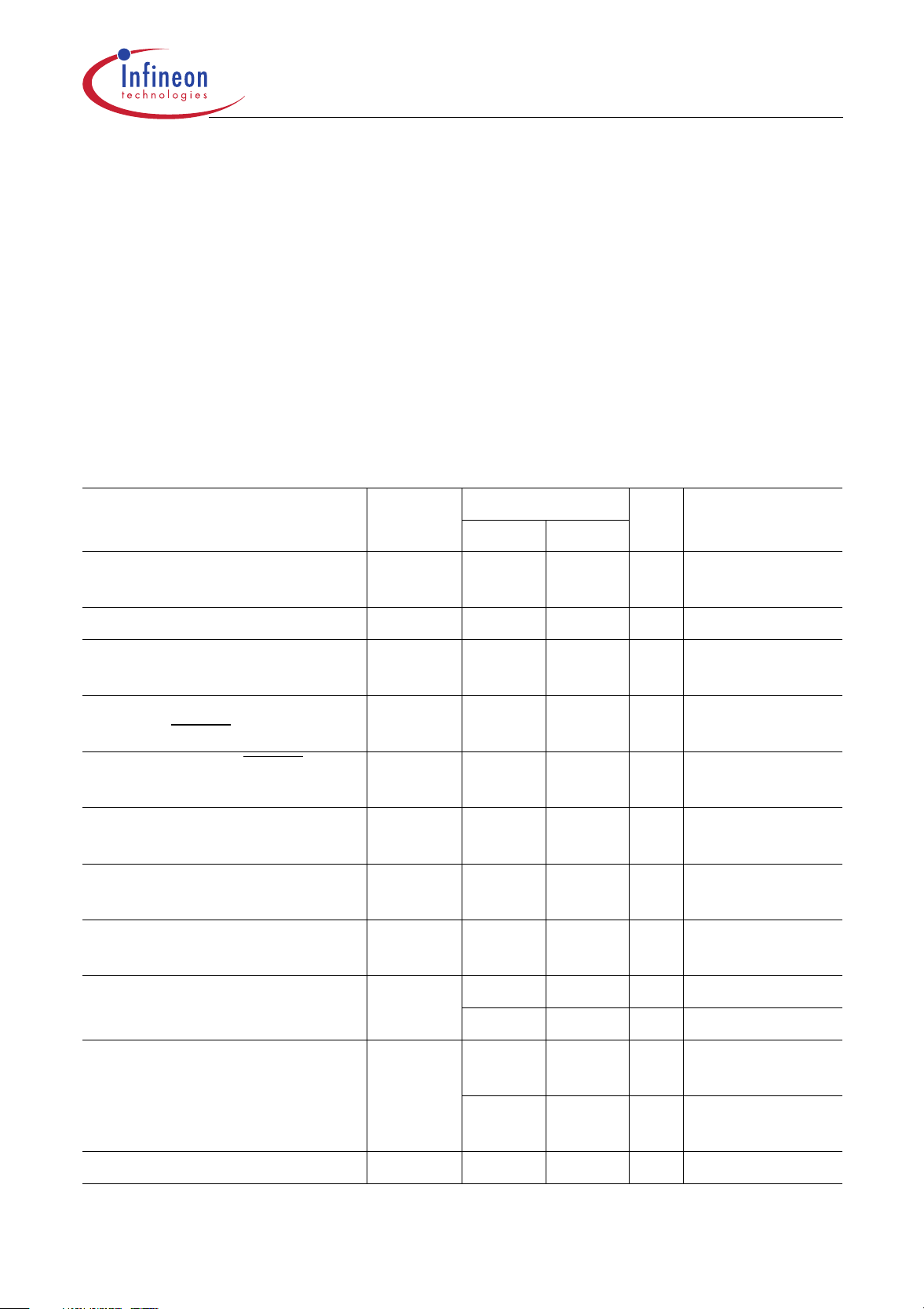

Table 2 Pin Definitions and Functions

C167CS-4R

C167CS-L

Symbol Pin

Num.

P6

P6.0

P6.1

P6.2

P6.3

P6.4

P6.5

P6.6

P6.7

1

2

3

4

5

6

7

8

P8

P8.0

P8.1

P8.2

P8.3

P8.4

P8.5

P8.6

P8.7

9

10

11

12

13

14

15

16

Input

Outp.

IO

O

O

O

O

O

I

I/O

O

IO

I/O

I

I

I/O

O

O

I/O

I

I

I/O

I

I

I/O

I/O

I/O

I/O

Function

Port 6 is an 8-bit bidirectional I/O port. It is bit-wise

programmable for input or output via direction bits. For a pin

configured as input, the output driver is put into highimpedance state. Port 6 outputs can be configured as push/

pull or open drain drivers.

The Port 6 pins also serve for alternate functions:

CS0

CS1

CS2

CS3

CS4

HOLD

HLDA

Chip Select 0 Output

Chip Select 1 Output

Chip Select 2 Output

Chip Select 3 Output

Chip Select 4 Output

External Master Hold Request Input

Hold Acknowledge Output (master mode)

or Input (slave mode)

BREQ

Bus Request Output

Port 8 is an 8-bit bidirectional I/O port. It is bit-wise

programmable for input or output via direction bits. For a pin

configured as input, the output driver is put into highimpedance state. Port 8 outputs can be configured as push/

pull or open drain drivers. The input threshold of Port 8 is

selectable (TTL or special). Port 8 pins provide inputs/

outputs for CAPCOM2 and serial interface lines.

1)

CC16IO CAPCOM2: CC16 Capture Inp./Compare Outp.,

CAN1_RxD CAN 1 Receive Data Input,

CAN2_RxD CAN 2 Receive Data Input

CC17IO CAPCOM2: CC17 Capture Inp./Compare Outp.,

CAN1_TxD CAN 1 Transmit Data Output,

CAN2_TxD CAN 2 Transmit Data Output

CC18IO CAPCOM2: CC18 Capture Inp./Compare Outp.,

CAN1_RxD CAN 1 Receive Data Input,

CAN2_RxD CAN 2 Receive Data Input

CC19IO CAPCOM2: CC19 Capture Inp./Compare Outp.,

CAN1_TxD CAN 1 Transmit Data Output,

CAN2_TxD CAN 2 Transmit Data Output

CC20IO CAPCOM2: CC20 Capture Inp./Compare Outp.

CC21IO CAPCOM2: CC21 Capture Inp./Compare Outp.

CC22IO CAPCOM2: CC22 Capture Inp./Compare Outp.

CC23IO CAPCOM2: CC23 Capture Inp./Compare Outp.

Data Sheet 5 V2.2, 2001-08

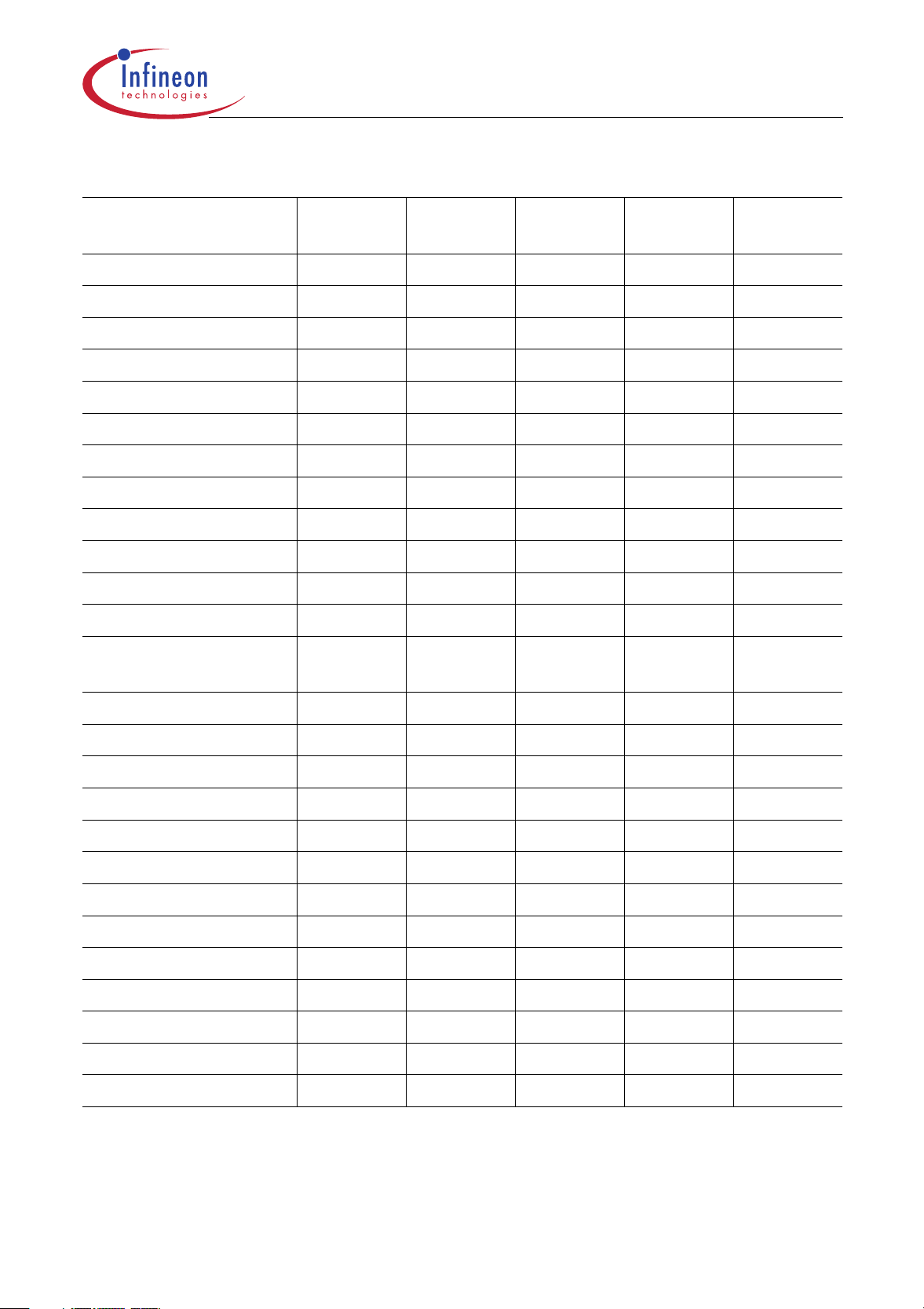

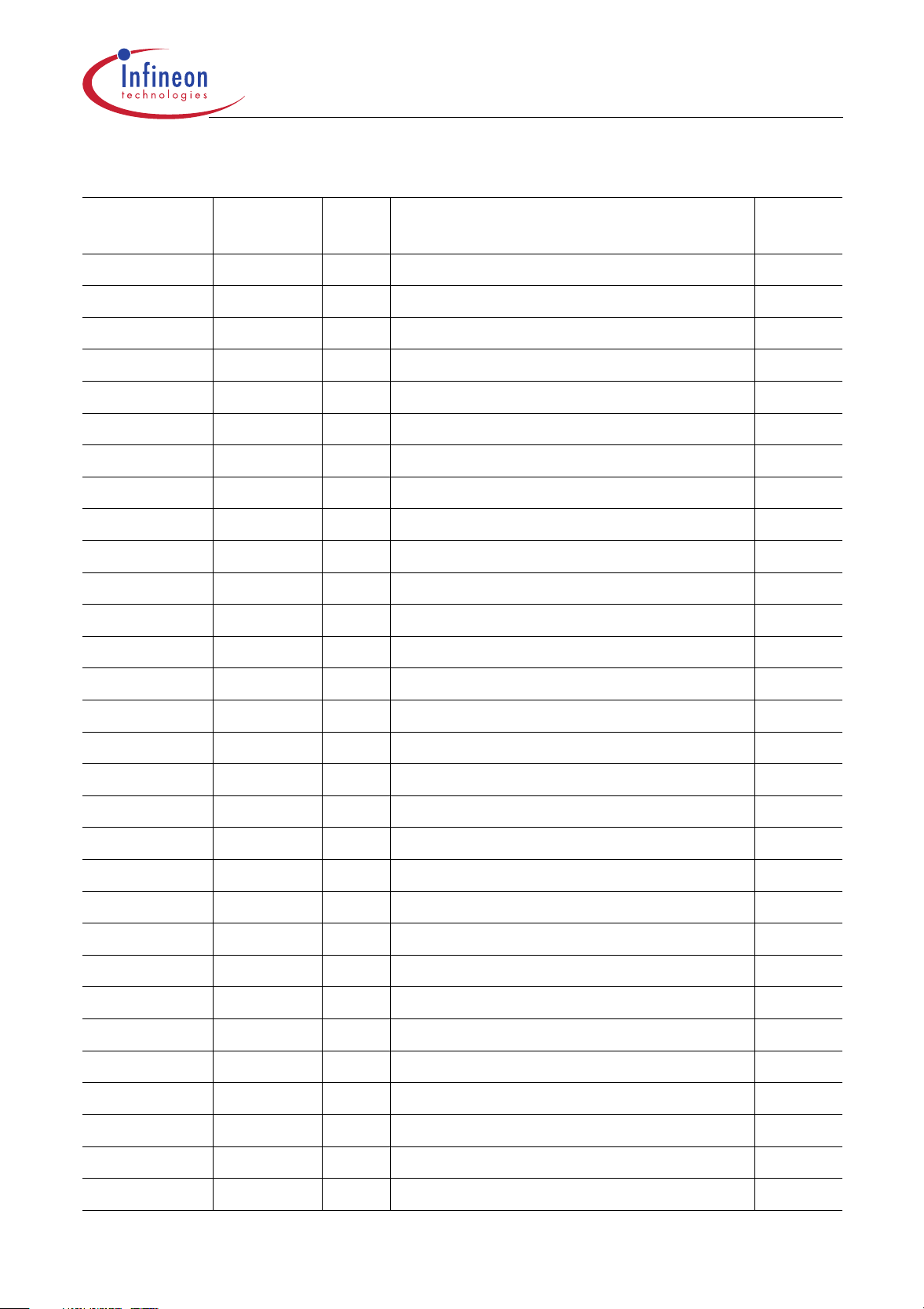

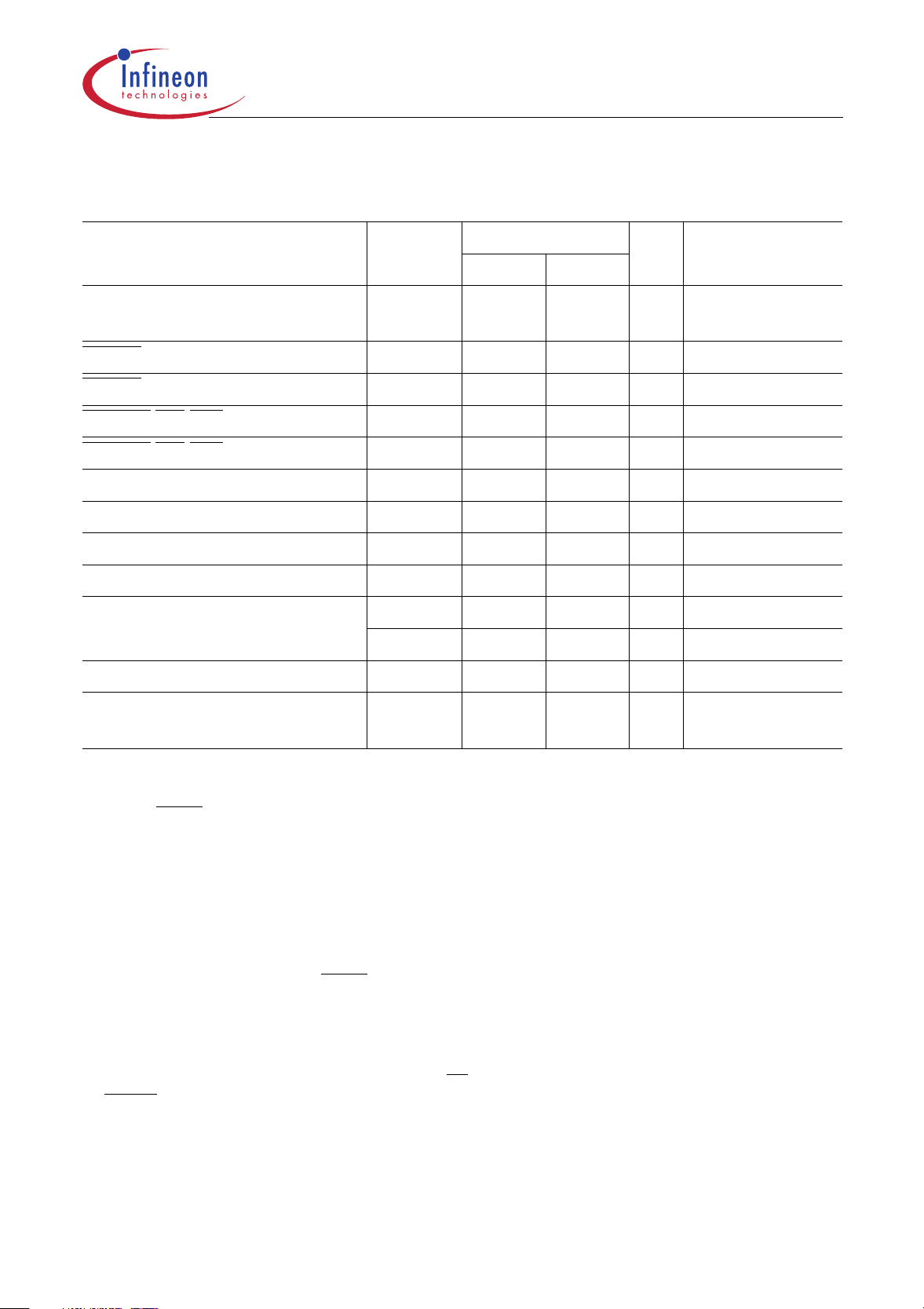

Table 2 Pin Definitions and Functions (cont’d)

C167CS-4R

C167CS-L

Symbol Pin

Num.

P7

P7.0

P7.1

P7.2

P7.3

P7.4

P7.5

P7.6

P7.7

P5

P5.0

P5.1

P5.2

P5.3

P5.4

P5.5

P5.6

P5.7

P5.8

P5.9

P5.10

P5.11

P5.12

P5.13

P5.14

P5.15

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

39

40

41

42

43

44

Input

Outp.

IO

O

O

O

O

I/O

I/O

I/O

I/O

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

Function

Port 7 is an 8-bit bidirectional I/O port. It is bit-wise

programmable for input or output via direction bits. For a pin

configured as input, the output driver is put into highimpedance state. Port 7 outputs can be configured as push/

pull or open drain drivers. The input threshold of Port 7 is

selectable (TTL or special).

The following Port 7 pins also serve for alternate functions:

POUT0 PWM Channel 0 Output

POUT1 PWM Channel 1 Output

POUT2 PWM Channel 2 Output

POUT3 PWM Channel 3 Output

CC28IO CAPCOM2: CC28 Capture Inp./Compare Outp.

CC29IO CAPCOM2: CC29 Capture Inp./Compare Outp.

CC30IO CAPCOM2: CC30 Capture Inp./Compare Outp.

CC31IO CAPCOM2: CC31 Capture Inp./Compare Outp.

Port 5 is a 16-bit input-only port with Schmitt-Trigger char.

The pins of Port 5 also serve as analog input channels for the

A/D converter, or they serve as timer inputs:

AN0

AN1

AN2

AN3

AN4

AN5

AN6

AN7

AN8

AN9

AN10, T6EUD GPT2 Timer T6 Ext. Up/Down Ctrl. Inp.

AN11, T5EUD GPT2 Timer T5 Ext. Up/Down Ctrl. Inp.

AN12, T6IN GPT2 Timer T6 Count Inp.

AN13, T5IN GPT2 Timer T5 Count Inp.

AN14, T4EUD GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.

AN15, T2EUD GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.

Data Sheet 6 V2.2, 2001-08

Table 2 Pin Definitions and Functions (cont’d)

C167CS-4R

C167CS-L

Symbol Pin

Num.

P2

P2.0

P2.1

P2.2

P2.3

P2.4

P2.5

P2.6

P2.7

P2.8

P2.9

P2.10

P2.11

P2.12

P2.13

P2.14

P2.15

47

48

49

50

51

52

53

54

57

58

59

60

61

62

63

64

Input

Outp.

IO

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I

Function

Port 2 is a 16-bit bidirectional I/O port. It is bit-wise

programmable for input or output via direction bits. For a pin

configured as input, the output driver is put into highimpedance state. Port 2 outputs can be configured as push/

pull or open drain drivers. The input threshold of Port 2 is

selectable (TTL or special).

The following Port 2 pins also serve for alternate functions:

CC0IO CAPCOM1: CC0 Capture Inp./Compare Output

CC1IO CAPCOM1: CC1 Capture Inp./Compare Output

CC2IO CAPCOM1: CC2 Capture Inp./Compare Output

CC3IO CAPCOM1: CC3 Capture Inp./Compare Output

CC4IO CAPCOM1: CC4 Capture Inp./Compare Output

CC5IO CAPCOM1: CC5 Capture Inp./Compare Output

CC6IO CAPCOM1: CC6 Capture Inp./Compare Output

CC7IO CAPCOM1: CC7 Capture Inp./Compare Output

CC8IO CAPCOM1: CC8 Capture Inp./Compare Output,

EX0IN Fast External Interrupt 0 Input

CC9IO CAPCOM1: CC9 Capture Inp./Compare Output,

EX1IN Fast External Interrupt 1 Input

CC10IO CAPCOM1: CC10 Capture Inp./Compare Outp.,

EX2IN Fast External Interrupt 2 Input

CC11IO CAPCOM1: CC11 Capture Inp./Compare Outp.,

EX3IN Fast External Interrupt 3 Input

CC12IO CAPCOM1: CC12 Capture Inp./Compare Outp.,

EX4IN Fast External Interrupt 4 Input

CC13IO CAPCOM1: CC13 Capture Inp./Compare Outp.,

EX5IN Fast External Interrupt 5 Input

CC14IO CAPCOM1: CC14 Capture Inp./Compare Outp.,

EX6IN Fast External Interrupt 6 Input

CC15IO CAPCOM1: CC15 Capture Inp./Compare Outp.,

EX7IN Fast External Interrupt 7 Input,

T7IN CAPCOM2: Timer T7 Count Input

Note: During Sleep Mode a spike filter on the EXnIN

interrupt inputs suppresses input pulses <10 ns.

Input pulses >100 ns safely pass the filter.

Data Sheet 7 V2.2, 2001-08

Table 2 Pin Definitions and Functions (cont’d)

C167CS-4R

C167CS-L

Symbol Pin

Num.

P3

P3.0

P3.1

P3.2

P3.3

P3.4

P3.5

P3.6

P3.7

P3.8

P3.9

P3.10

P3.11

P3.12

P3.13

P3.15

65

66

67

68

69

70

73

74

75

76

77

78

79

80

81

Input

Outp.

IO

I

O

I

O

I

I

I

I

I/O

I/O

O

I/O

O

O

I/O

O

O

Function

Port 3 is a 15-bit bidirectional I/O port. It is bit-wise

programmable for input or output via direction bits. For a pin

configured as input, the output driver is put into highimpedance state. Port 3 outputs can be configured as push/

pull or open drain drivers. The input threshold of Port 3 is

selectable (TTL or special).

The following Port 3 pins also serve for alternate functions:

T0IN CAPCOM1 Timer T0 Count Input

T6OUT GPT2 Timer T6 Toggle Latch Output

CAPIN GPT2 Register CAPREL Capture Input

T3OUT GPT1 Timer T3 Toggle Latch Output

T3EUD GPT1 Timer T3 External Up/Down Control Input

T4IN GPT1 Timer T4 Count/Gate/Reload/Capture Inp

T3IN GPT1 Timer T3 Count/Gate Input

T2IN GPT1 Timer T2 Count/Gate/Reload/Capture Inp

MRST SSC Master-Receive/Slave-Transmit Inp./Outp.

MTSR SSC Master-Transmit/Slave-Receive Outp./Inp.

T

×D0 ASC0 Clock/Data Output (Async./Sync.)

R

×D0 ASC0 Data Input (Async.) or Inp./Outp. (Sync.)

BHE

WRH

SCLK SSC Master Clock Output / Slave Clock Input.

CLKOUT System Clock Output (= CPU Clock)

FOUT Programmable Frequency Output

External Memory High Byte Enable Signal,

External Memory High Byte Write Strobe

N.C. 84 – This pin is not connected in the C167CS.

No connection to the PCB is required.

Data Sheet 8 V2.2, 2001-08

Table 2 Pin Definitions and Functions (cont’d)

C167CS-4R

C167CS-L

Symbol Pin

Num.

P4

P4.0

P4.1

P4.2

P4.3

P4.4

P4.5

P4.6

P4.7

85

86

87

88

89

90

91

92

Input

Outp.

IO

O

O

O

O

O

I

O

I

O

O

O

O

I

O

I

Function

Port 4 is an 8-bit bidirectional I/O port. It is bit-wise

programmable for input or output via direction bits. For a pin

configured as input, the output driver is put into highimpedance state. The Port 4 outputs can be configured as

push/pull or open drain drivers. The input threshold of Port 4

is selectable (TTL or special).

Port 4 can be used to output the segment address lines and

for serial interface lines:

1)

A16 Least Significant Segment Address Line

A17 Segment Address Line

A18 Segment Address Line

A19 Segment Address Line

A20 Segment Address Line,

CAN2_RxD CAN 2 Receive Data Input

A21 Segment Address Line,

CAN1_RxD CAN 1 Receive Data Input

A22 Segment Address Line,

CAN1_TxD CAN 1 Transmit Data Output,

CAN2_TxD CAN 2 Transmit Data Output

A23 Most Significant Segment Address Line,

CAN1_RxD CAN 1 Receive Data Input,

CAN2_TxD CAN 2 Transmit Data Output,

CAN2_RxD CAN 2 Receive Data Input

RD

95 O External Memory Read Strobe. RD is activated for every

external instruction or data read access.

WR

/

WRL

96 O External Memory Write Strobe. In WR-mode this pin is

activated for every external data write access. In WRL

-mode

this pin is activated for low byte data write accesses on a

16-bit bus, and for every data write access on an 8-bit bus.

See WRCFG in register SYSCON for mode selection.

READY 97 I Ready Input. When the Ready function is enabled, a high

level at this pin during an external memory access will force

the insertion of memory cycle time waitstates until the pin

returns to a low level.

An internal pullup device will hold this pin high when nothing

is driving it.

Data Sheet 9 V2.2, 2001-08

Table 2 Pin Definitions and Functions (cont’d)

C167CS-4R

C167CS-L

Symbol Pin

Num.

ALE 98 O Address Latch Enable Output. Can be used for latching the

EA

PORT0

P0L.0-7

P0H.0-7

99 I External Access Enable pin. A low level at this pin during and

100107

108,

111117

Input

Outp.

IO PORT0 consists of the two 8-bit bidirectional I/O ports P0L

Function

address into external memory or an address latch in the

multiplexed bus modes.

after Reset forces the C167CS to begin instruction execution

out of external memory. A high level forces execution out of

the internal program memory.

“ROMless” versions must have this pin tied to ‘0’.

and P0H. It is bit-wise programmable for input or output via

direction bits. For a pin configured as input, the output driver

is put into high-impedance state.

In case of an external bus configuration, PORT0 serves as

the address (A) and address/data (AD) bus in multiplexed

bus modes and as the data (D) bus in demultiplexed bus

modes.

Demultiplexed bus modes:

Data Path Width: 8-bit 16-bit

P0L.0 – P0L.7: D0 – D7 D0 – D7

P0H.0 – P0H.7: I/O D8 – D15

Multiplexed bus modes:

Data Path Width: 8-bit 16-bit

P0L.0 – P0L.7: AD0 – AD7 AD0 – AD7

P0H.0 – P0H.7: A8 – A15 AD8 – AD15

Data Sheet 10 V2.2, 2001-08

Table 2 Pin Definitions and Functions (cont’d)

C167CS-4R

C167CS-L

Symbol Pin

Num.

PORT1

P1L.0-7

P1H.0-7

P1L.0

P1L.1

P1L.2

P1L.3

P1L.4

P1L.5

P1L.6

P1L.7

P1H.4

P1H.5

P1H.6

P1H.7

118125

128135

118

119

120

121

122

123

124

125

132

133

134

135

Input

Outp.

IO

I

I

I

I

I

I

I

I

I/O

I/O

I/O

I/O

Function

PORT1 consists of the two 8-bit bidirectional I/O ports P1L

and P1H. It is bit-wise programmable for input or output via

direction bits. For a pin configured as input, the output driver

is put into high-impedance state. PORT1 is used as the

16-bit address bus (A) in demultiplexed bus modes and also

after switching from a demultiplexed bus mode to a

multiplexed bus mode.

The following PORT1 pins also serve for alternate functions:

AN16 Analog Input Channel 16

AN17 Analog Input Channel 17

AN18 Analog Input Channel 18

AN19 Analog Input Channel 19

AN20 Analog Input Channel 20

AN21 Analog Input Channel 21

AN22 Analog Input Channel 22

AN23 Analog Input Channel 23

CC24IO CAPCOM2: CC24 Capture Inp./Compare Outp.

CC25IO CAPCOM2: CC25 Capture Inp./Compare Outp.

CC26IO CAPCOM2: CC26 Capture Inp./Compare Outp.

CC27IO CAPCOM2: CC27 Capture Inp./Compare Outp.

XTAL2

XTAL1

137

138

O

I

XTAL2: Output of the oscillator amplifier circuit.

XTAL1: Input to the oscillator amplifier and input to

the internal clock generator

To clock the device from an external source, drive XTAL1,

while leaving XTAL2 unconnected. Minimum and maximum

high/low and rise/fall times specified in the AC

Characteristics must be observed.

Data Sheet 11 V2.2, 2001-08

Table 2 Pin Definitions and Functions (cont’d)

C167CS-4R

C167CS-L

Symbol Pin

Num.

Input

Outp.

Function

RSTIN 140 I/O Reset Input with Schmitt-Trigger characteristics. A low level

at this pin while the oscillator is running resets the C167CS.

An internal pullup resistor permits power-on reset using only

a capacitor connected to

V

SS

.

A spike filter suppresses input pulses <10 ns. Input pulses

>100 ns safely pass the filter. The minimum duration for a

safe recognition should be 100 ns + 2 CPU clock cycles.

In bidirectional reset mode (enabled by setting bit BDRSTEN

in register SYSCON) the RSTIN

line is internally pulled low

for the duration of the internal reset sequence upon any reset

(HW, SW, WDT). See note below this table.

Note: To let the reset configuration of PORT0 settle and to

let the PLL lock a reset duration of ca. 1 ms is

recommended.

RST

OUT

141 O Internal Reset Indication Output. This pin is set to a low level

when the part is executing either a hardware-, a software- or

a watchdog timer reset. RSTOUT

remains low until the EINIT

(end of initialization) instruction is executed.

NMI

V

AREF

V

AGND

142 I Non-Maskable Interrupt Input. A high to low transition at this

pin causes the CPU to vector to the NMI trap routine. When

the PWRDN (power down) instruction is executed, the NMI

pin must be low in order to force the C167CS to go into power

down mode. If NMI

is high, when PWRDN is executed, the

part will continue to run in normal mode.

If not used, pin NMI

should be pulled high externally.

37 – Reference voltage for the A/D converter.

38 – Reference ground for the A/D converter.

Data Sheet 12 V2.2, 2001-08

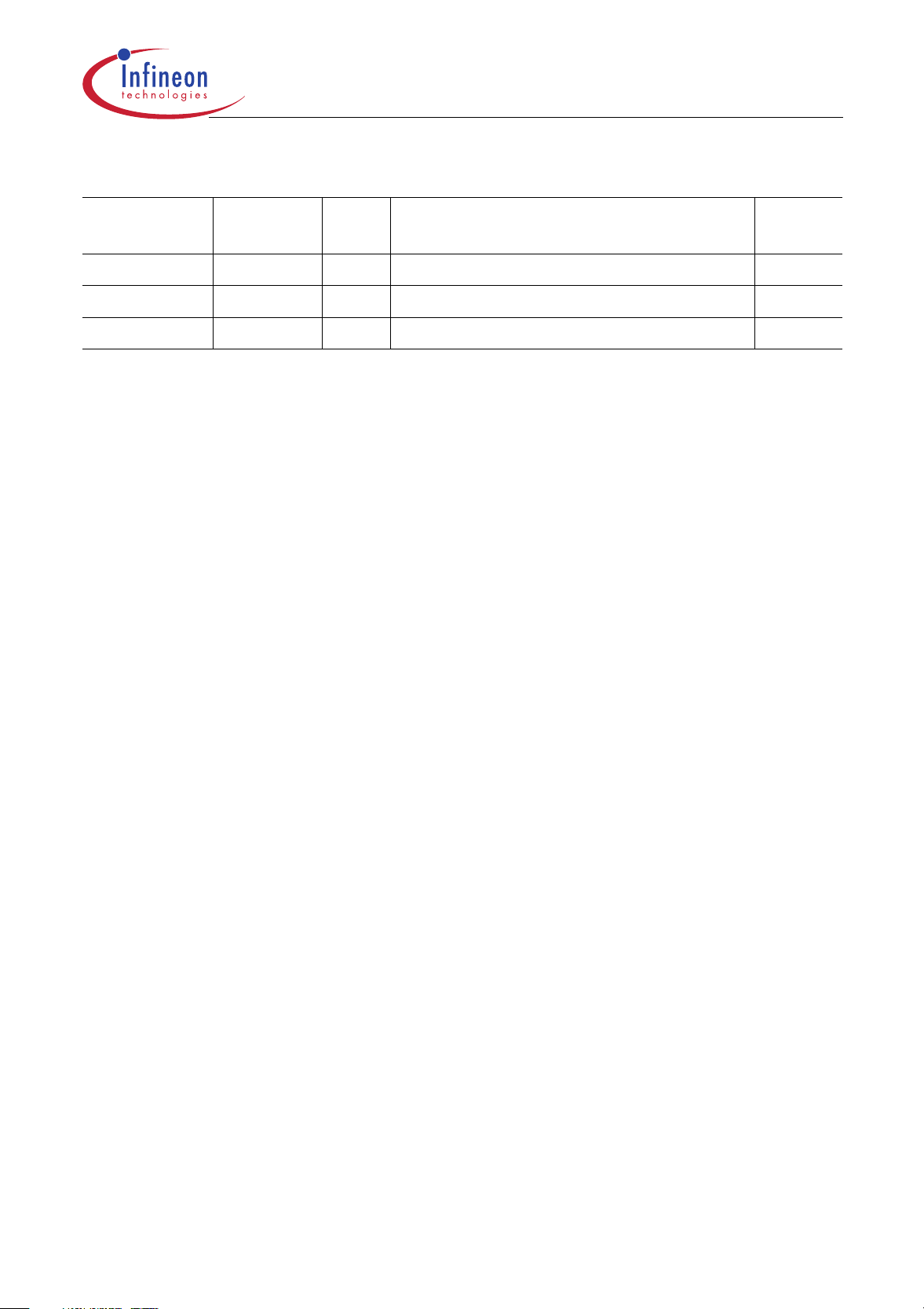

Table 2 Pin Definitions and Functions (cont’d)

C167CS-4R

C167CS-L

Symbol Pin

Num.

V

DD

17, 46,

56, 72,

82, 93,

Input

Function

Outp.

– Digital Supply Voltage:

+5 V during normal operation and idle mode.

≥2.5 V during power down mode.

109,

126,

136,

144

V

SS

18, 45,

– Digital Ground.

55, 71,

83, 94,

110,

127,

139,

143

1)

The CAN interface lines are assigned to ports P4 and P8 under software control. Within the CAN module

several assignments can be selected.

Note: The following behaviour differences must be observed when the bidirectional reset

is active:

• Bit BDRSTEN in register SYSCON cannot be changed after EINIT and is cleared

automatically after a reset.

• The reset indication flags always indicate a long hardware reset.

• The PORT0 configuration is treated like on a hardware reset. Especially the bootstrap

loader may be activated when P0L.4 is low.

• Pin RSTIN

may only be connected to external reset devices with an open drain output

driver.

• A short hardware reset is extended to the duration of the internal reset sequence.

Data Sheet 13 V2.2, 2001-08

C167CS-4R

C167CS-L

Functional Description

The architecture of the C167CS combines advantages of both RISC and CISC

processors and of advanced peripheral subsystems in a very well-balanced way. In

addition the on-chip memory blocks allow the design of compact systems with maximum

performance.

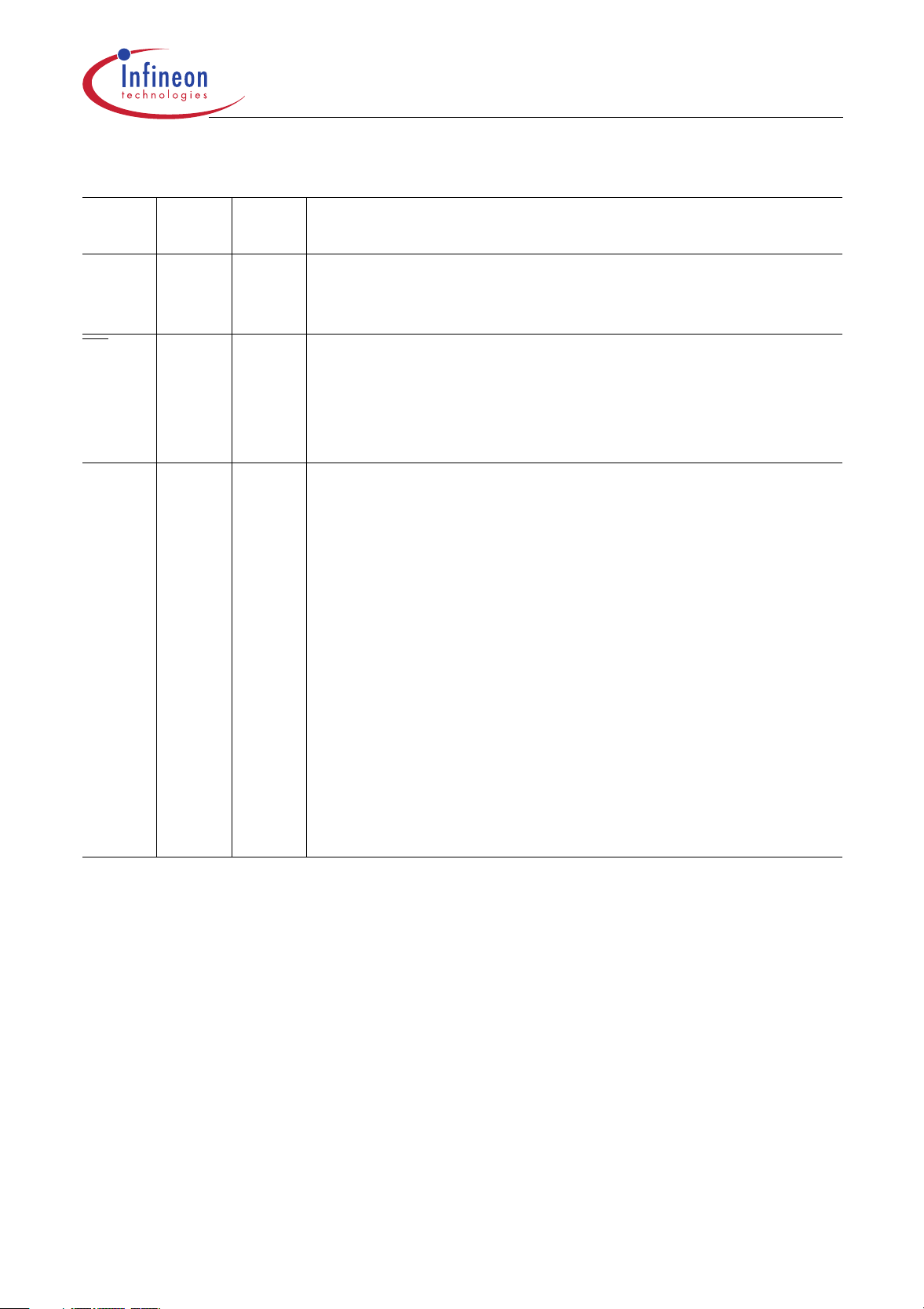

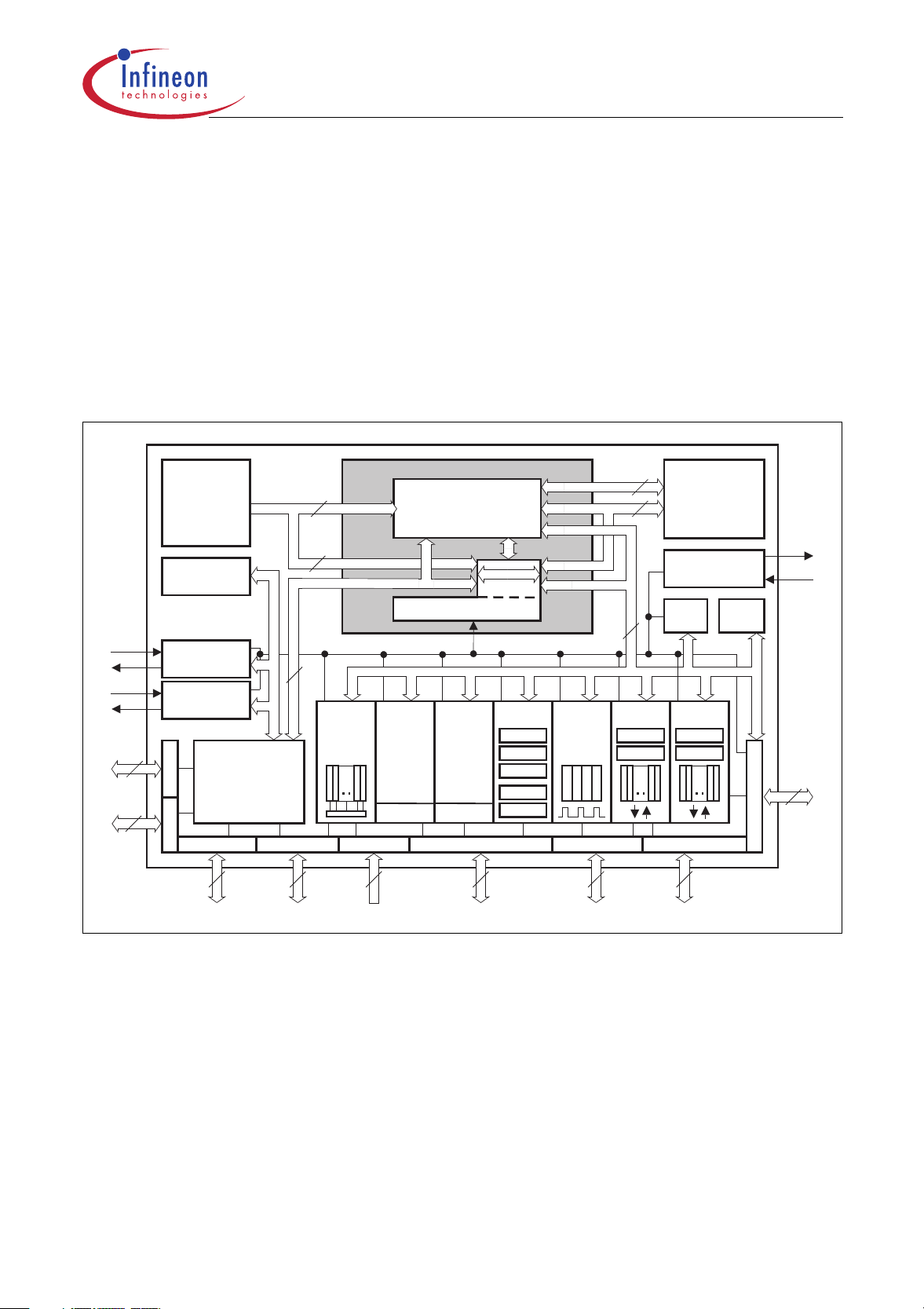

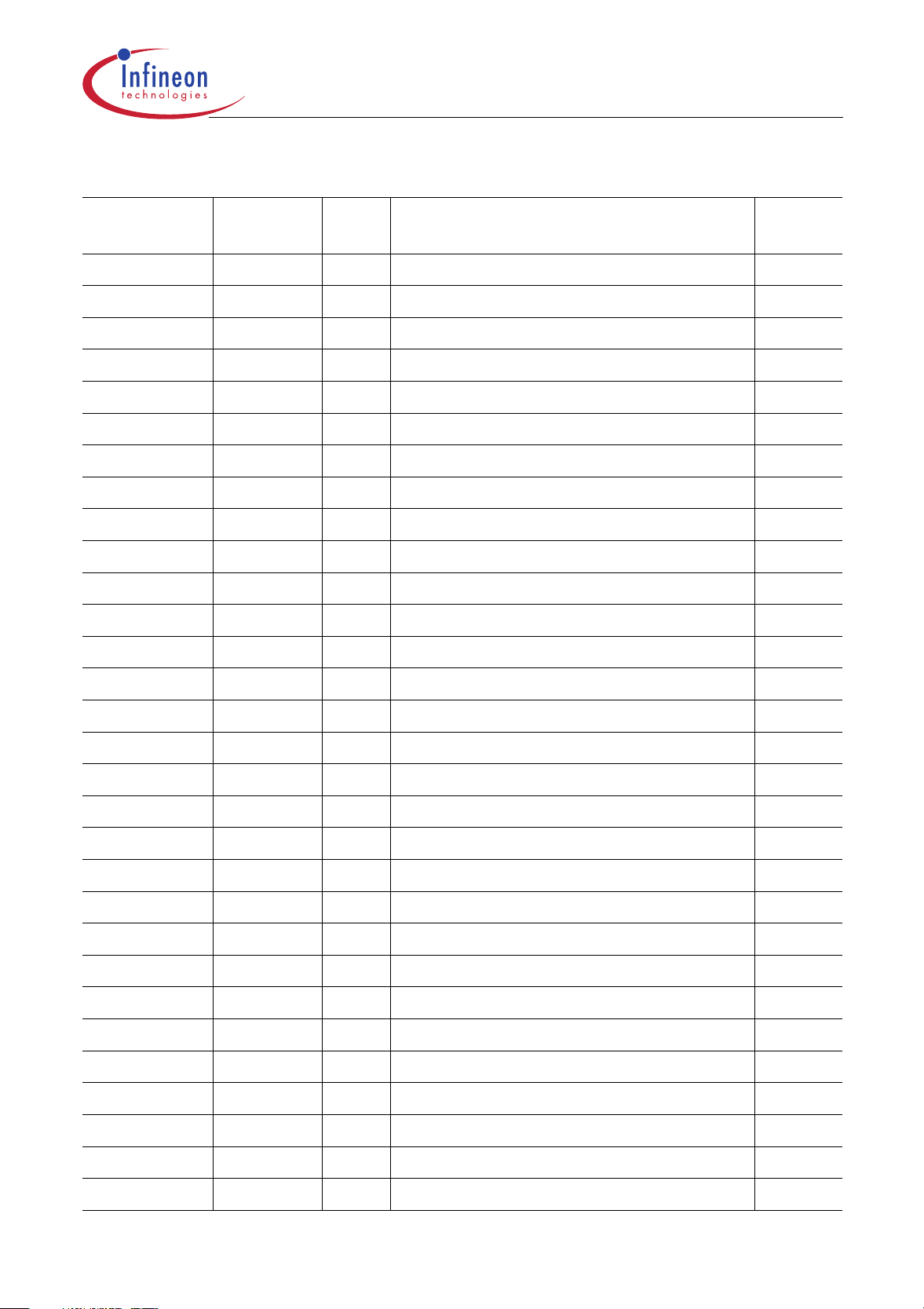

Figure 3 gives an overview of the different on-chip components and of the advanced,

high bandwidth internal bus structure of the C167CS.

Note: All time specifications refer to a CPU clock of 40 MHz

(see definition in the AC Characteristics section).

8

8

ProgMem

ROM

32 KByte

XRAM

6+2 KByte

CAN2

Rev 2.0B active

CAN1

Rev 2.0B active

XBUS Control

Port 4

External Bus

Control

Port 6

Port 0

16

EBC

Instr. / Data

)

x

u

m

e

it D

-B

6

(1

S

U

B

X

ip

h

-C

n

O

Port 1

32

16

16

16

External Instr. / Data

Interrupt Controller

ADC

10-Bit

16+8

Channels

ASC0

(USART)

BRGen

Port 5 Port 3

16

C166-Core

CPU

SSC

(SPI)

BRGen

PEC

16-Level

Priority

15

Interrupt Bus

GPT

T2

T3

T4

T5

T6

Data

Data

16

16

IRAM

Internal

Dual Port

3 KByte

RAM

Osc / PLL

RTC WDT

16

Peripheral Data Bus

PWM CCOM1

Port 7

CCOM2

8

T7

T8

T0

T1

Port 8

8

MCB04323_7CS

XTAL

16

Port 2

Figure 3 Block Diagram

The program memory, the internal RAM (IRAM) and the set of generic peripherals are

connected to the CPU via separate buses. A fourth bus, the XBUS, connects external

resources as well as additional on-chip resources, the X-Peripherals (see Figure 3).

The XBUS resources (XRAM, CAN) of the C167CS can be individually enabled or

disabled during initialization. Register XPERCON selects the required modules which

are then enabled by setting the general X-Peripheral enable bit XPEN (SYSCON.2).

Modules that are disabled consume neither address space nor port pins.

Note: The default value of register XPERCON after reset selects 2 KByte XRAM and

module CAN1, so the default XBUS resources are compatible with the C167CR.

Data Sheet 14 V2.2, 2001-08

C167CS-4R

C167CS-L

Memory Organization

The memory space of the C167CS is configured in a Von Neumann architecture which

means that code memory, data memory, registers and I/O ports are organized within the

same linear address space which includes 16 MBytes. The entire memory space can be

accessed bytewise or wordwise. Particular portions of the on-chip memory have

additionally been made directly bitaddressable.

The C167CS incorporates 32 KBytes of on-chip mask-programmable ROM (not in the

ROM-less derivative, of course) for code or constant data. The 32 KBytes of the on-chip

ROM can be mapped either to segment 0 or segment 1.

3 KBytes of on-chip Internal RAM (IRAM) are provided as a storage for user defined

variables, for the system stack, general purpose register banks and even for code. A

register bank can consist of up to 16 wordwide (R0 to R15) and/or bytewide (RL0, RH0,

…, RL7, RH7) so-called General Purpose Registers (GPRs).

1024 bytes (2

Register areas (SFR space and ESFR space). SFRs are wordwide registers which are

used for controlling and monitoring functions of the different on-chip units. Unused SFR

addresses are reserved for future members of the C166 Family.

8 KBytes of on-chip Extension RAM (XRAM), organized as two blocks of 2 KByte and

6 KByte, respectively, are provided to store user data, user stacks, or code. The XRAM

is accessed like external memory and therefore cannot be used for the system stack or

for register banks and is not bitaddressable. The XRAM permits 16-bit accesses with

maximum speed.

In order to meet the needs of designs where more memory is required than is provided

on chip, up to 16 MBytes of external RAM and/or ROM can be connected to the

microcontroller.

× 512 bytes) of the address space are reserved for the Special Function

Data Sheet 15 V2.2, 2001-08

C167CS-4R

C167CS-L

External Bus Controller

All of the external memory accesses are performed by a particular on-chip External Bus

Controller (EBC). It can be programmed either to Single Chip Mode when no external

memory is required, or to one of four different external memory access modes, which are

as follows:

– 16-/18-/20-/24-bit Addresses, 16-bit Data, Demultiplexed

– 16-/18-/20-/24-bit Addresses, 16-bit Data, Multiplexed

– 16-/18-/20-/24-bit Addresses, 8-bit Data, Multiplexed

– 16-/18-/20-/24-bit Addresses, 8-bit Data, Demultiplexed

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/

output on PORT0 or P0L, respectively. In the multiplexed bus modes both addresses

and data use PORT0 for input/output.

Important timing characteristics of the external bus interface (Memory Cycle Time,

Memory Tri-State Time, Length of ALE and Read Write Delay) have been made

programmable to allow the user the adaption of a wide range of different types of

memories and external peripherals.

In addition, up to 4 independent address windows may be defined (via register pairs

ADDRSELx / BUSCONx) which control the access to different resources with different

bus characteristics. These address windows are arranged hierarchically where

BUSCON4 overrides BUSCON3 and BUSCON2 overrides BUSCON1. All accesses to

locations not covered by these 4 address windows are controlled by BUSCON0.

Up to 5 external CS

external glue logic. The C167CS offers the possibility to switch the CS

unlatched mode. In this mode the internal filter logic is switched off and the CS

are directly generated from the address. The unlatched CS

CSCFG (SYSCON.6).

Access to very slow memories or memories with varying access times is supported via

a particular ‘Ready’ function.

A HOLD

resources with other bus masters. The bus arbitration is enabled by setting bit HLDEN

in register PSW. After setting HLDEN once, pins P6.7 … P6.5 (BREQ

are automatically controlled by the EBC. In Master Mode (default after reset) the HLDA

pin is an output. By setting bit DP6.7 to ‘1’ the Slave Mode is selected where pin HLDA

is switched to input. This allows to directly connect the slave controller to another master

controller without glue logic.

For applications which require less than 16 MBytes of external memory space, this

address space can be restricted to 1 MByte, 256 KByte, or to 64 KByte. In this case

Port 4 outputs four, two, or no address lines at all. It outputs all 8 address lines, if an

address space of 16 MBytes is used.

/HLDA protocol is available for bus arbitration and allows to share external

signals (4 windows plus default) can be generated in order to save

outputs to an

signals

mode is enabled by setting

, HLDA, HOLD)

Data Sheet 16 V2.2, 2001-08

C167CS-4R

C167CS-L

Note: When one or both of the on-chip CAN Modules are used with the interface lines

assigned to Port 4, the CAN lines override the segment address lines and the

segment address output on Port 4 is therefore limited to 6/4 bits i.e. address lines

A21/A19 … A16. CS

addressable external memory.

Central Processing Unit (CPU)

The main core of the CPU consists of a 4-stage instruction pipeline, a 16-bit arithmetic

and logic unit (ALU) and dedicated SFRs. Additional hardware has been spent for a

separate multiply and divide unit, a bit-mask generator and a barrel shifter.

Based on these hardware provisions, most of the C167CS’s instructions can be

executed in just one machine cycle which requires 50 ns at 40 MHz CPU clock. For

example, shift and rotate instructions are always processed during one machine cycle

independent of the number of bits to be shifted. All multiple-cycle instructions have been

optimized so that they can be executed very fast as well: branches in 2 cycles, a 16

16 bit multiplication in 5 cycles and a 32-/16-bit division in 10 cycles. Another pipeline

optimization, the so-called ‘Jump Cache’, allows reducing the execution time of

repeatedly performed jumps in a loop from 2 cycles to 1 cycle.

lines can be used to increase the total amount of

×

ROM

32

CPU

SP

STKOV

STKUN

Exec. Unit

Instr. Ptr.

Instr. Reg.

4-Stage

Pipeline

PSW

SYSCON

BUSCON 0

BUSCON 1

BUSCON 2

BUSCON 3

BUSCON 4 ADDRSEL 4

Data Page Ptr. Code Seg. Ptr.

MDH

MDL

Mul/Div-HW

Bit-Mask Gen

ALU

(16-bit)

Barrel - Shifter

Context Ptr.

ADDRSEL 1

ADDRSEL 2

ADDRSEL 3

R15

General

Purpose

Registers

R0

16

Internal

RAM

R15

R0

16

MCB02147

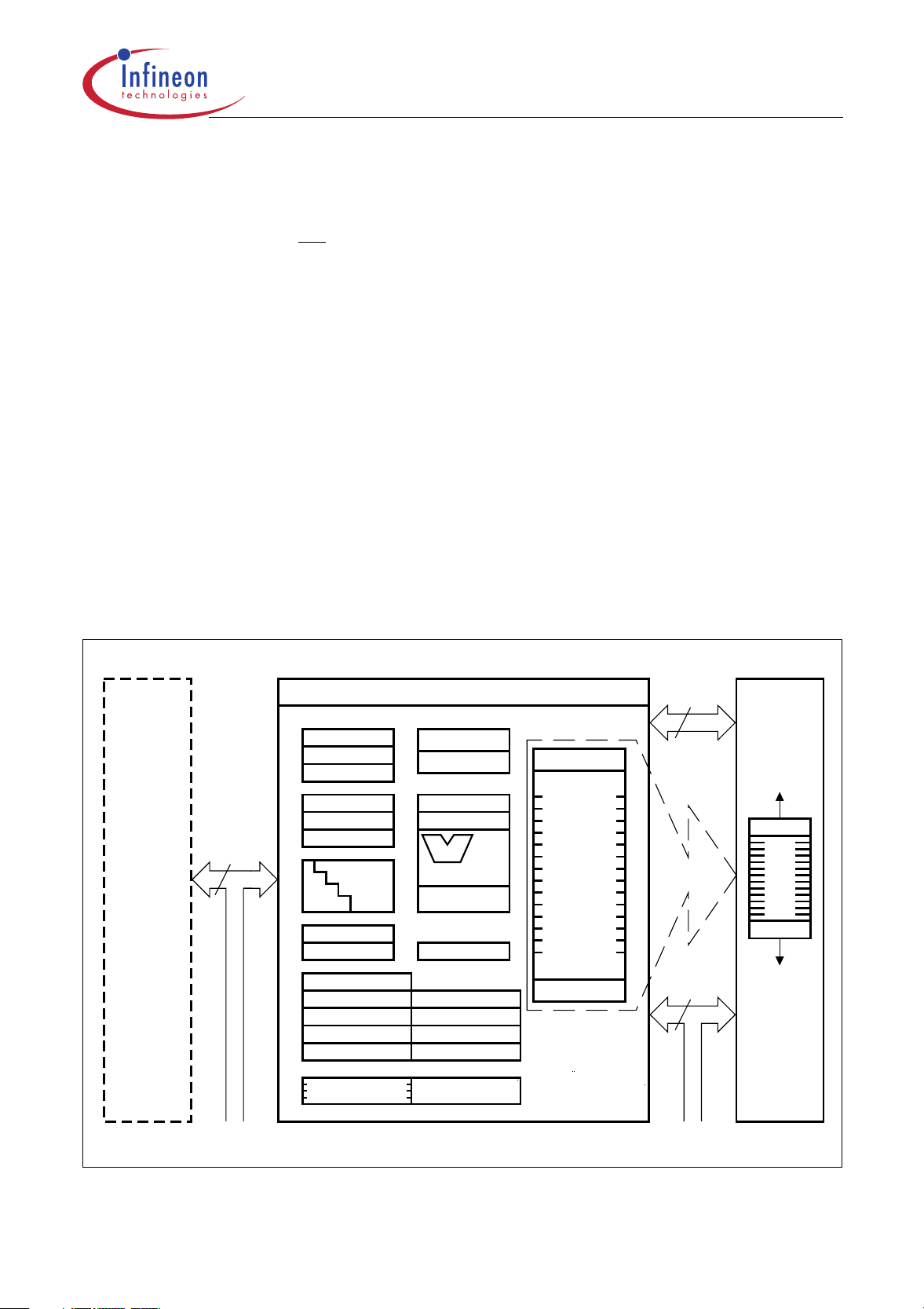

Figure 4 CPU Block Diagram

Data Sheet 17 V2.2, 2001-08

C167CS-4R

C167CS-L

The CPU has a register context consisting of up to 16 wordwide GPRs at its disposal.

These 16 GPRs are physically allocated within the on-chip RAM area. A Context Pointer

(CP) register determines the base address of the active register bank to be accessed by

the CPU at any time. The number of register banks is only restricted by the available

internal RAM space. For easy parameter passing, a register bank may overlap others.

A system stack of up to 1024 words is provided as a storage for temporary data. The

system stack is allocated in the on-chip RAM area, and it is accessed by the CPU via the

stack pointer (SP) register. Two separate SFRs, STKOV and STKUN, are implicitly

compared against the stack pointer value upon each stack access for the detection of a

stack overflow or underflow.

The high performance offered by the hardware implementation of the CPU can efficiently

be utilized by a programmer via the highly efficient C167CS instruction set which

includes the following instruction classes:

– Arithmetic Instructions

– Logical Instructions

– Boolean Bit Manipulation Instructions

– Compare and Loop Control Instructions

– Shift and Rotate Instructions

– Prioritize Instruction

– Data Movement Instructions

– System Stack Instructions

– Jump and Call Instructions

– Return Instructions

– System Control Instructions

– Miscellaneous Instructions

The basic instruction length is either 2 or 4 bytes. Possible operand types are bits, bytes

and words. A variety of direct, indirect or immediate addressing modes are provided to

specify the required operands.

Data Sheet 18 V2.2, 2001-08

C167CS-4R

C167CS-L

Interrupt System

With an interrupt response time within a range from just 5 to 12 CPU clocks (in case of

internal program execution), the C167CS is capable of reacting very fast to the

occurrence of non-deterministic events.

The architecture of the C167CS supports several mechanisms for fast and flexible

response to service requests that can be generated from various sources internal or

external to the microcontroller. Any of these interrupt requests can be programmed to

being serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

In contrast to a standard interrupt service where the current program execution is

suspended and a branch to the interrupt vector table is performed, just one cycle is

‘stolen’ from the current CPU activity to perform a PEC service. A PEC service implies a

single byte or word data transfer between any two memory locations with an additional

increment of either the PEC source or the destination pointer. An individual PEC transfer

counter is implicitly decremented for each PEC service except when performing in the

continuous transfer mode. When this counter reaches zero, a standard interrupt is

performed to the corresponding source related vector location. PEC services are very

well suited, for example, for supporting the transmission or reception of blocks of data.

The C167CS has 8 PEC channels each of which offers such fast interrupt-driven data

transfer capabilities.

A separate control register which contains an interrupt request flag, an interrupt enable

flag and an interrupt priority bitfield exists for each of the possible interrupt sources. Via

its related register, each source can be programmed to one of sixteen interrupt priority

levels. Once having been accepted by the CPU, an interrupt service can only be

interrupted by a higher prioritized service request. For the standard interrupt processing,

each of the possible interrupt sources has a dedicated vector location.

Fast external interrupt inputs are provided to service external interrupts with high

precision requirements. These fast interrupt inputs feature programmable edge

detection (rising edge, falling edge or both edges).

Software interrupts are supported by means of the ‘TRAP’ instruction in combination with

an individual trap (interrupt) number.

Table 3 shows all of the possible C167CS interrupt sources and the corresponding

hardware-related interrupt flags, vectors, vector locations and trap (interrupt) numbers.

Note: Interrupt nodes which are not used by associated peripherals, may be used to

generate software controlled interrupt requests by setting the respective interrupt

request bit (xIR).

Data Sheet 19 V2.2, 2001-08

Table 3 C167CS Interrupt Nodes

C167CS-4R

C167CS-L

Source of Interrupt or

PEC Service Request

Request

Flag

Enable

Flag

Interrupt

Vector

Vector

Location

CAPCOM Register 0 CC0IR CC0IE CC0INT 00’0040

CAPCOM Register 1 CC1IR CC1IE CC1INT 00’0044

CAPCOM Register 2 CC2IR CC2IE CC2INT 00’0048

CAPCOM Register 3 CC3IR CC3IE CC3INT 00’004C

CAPCOM Register 4 CC4IR CC4IE CC4INT 00’0050

CAPCOM Register 5 CC5IR CC5IE CC5INT 00’0054

CAPCOM Register 6 CC6IR CC6IE CC6INT 00’0058

CAPCOM Register 7 CC7IR CC7IE CC7INT 00’005C

CAPCOM Register 8 CC8IR CC8IE CC8INT 00’0060

CAPCOM Register 9 CC9IR CC9IE CC9INT 00’0064

CAPCOM Register 10 CC10IR CC10IE CC10INT 00’0068

CAPCOM Register 11 CC11IR CC11IE CC11INT 00’006C

CAPCOM Register 12 CC12IR CC12IE CC12INT 00’0070

H

H

H

H

H

H

H

H

H

H

H

H

H

Trap

Number

10

H

11

H

12

H

13

H

14

H

15

H

16

H

17

H

18

H

19

H

1A

H

1B

H

1C

H

CAPCOM Register 13 CC13IR CC13IE CC13INT 00’0074

CAPCOM Register 14 CC14IR CC14IE CC14INT 00’0078

CAPCOM Register 15 CC15IR CC15IE CC15INT 00’007C

CAPCOM Register 16 CC16IR CC16IE CC16INT 00’00C0

CAPCOM Register 17 CC17IR CC17IE CC17INT 00’00C4

CAPCOM Register 18 CC18IR CC18IE CC18INT 00’00C8

CAPCOM Register 19 CC19IR CC19IE CC19INT 00’00CC

CAPCOM Register 20 CC20IR CC20IE CC20INT 00’00D0

CAPCOM Register 21 CC21IR CC21IE CC21INT 00’00D4

CAPCOM Register 22 CC22IR CC22IE CC22INT 00’00D8

CAPCOM Register 23 CC23IR CC23IE CC23INT 00’00DC

CAPCOM Register 24 CC24IR CC24IE CC24INT 00’00E0

CAPCOM Register 25 CC25IR CC25IE CC25INT 00’00E4

CAPCOM Register 26 CC26IR CC26IE CC26INT 00’00E8

CAPCOM Register 27 CC27IR CC27IE CC27INT 00’00EC

1D

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

1E

1F

30

31

32

33

34

35

36

37

38

39

3A

3B

H

H

H

H

H

H

H

H

H

H

H

H

H

H

H

CAPCOM Register 28 CC28IR CC28IE CC28INT 00’00E0

CAPCOM Register 29 CC29IR CC29IE CC29INT 00’0110

Data Sheet 20 V2.2, 2001-08

3C

H

H

44

H

H

Table 3 C167CS Interrupt Nodes (cont’d)

C167CS-4R

C167CS-L

Source of Interrupt or

PEC Service Request

Request

Flag

Enable

Flag

Interrupt

Vector

Vector

Location

CAPCOM Register 30 CC30IR CC30IE CC30INT 00’0114

CAPCOM Register 31 CC31IR CC31IE CC31INT 00’0118

CAPCOM Timer 0 T0IR T0IE T0INT 00’0080

CAPCOM Timer 1 T1IR T1IE T1INT 00’0084

CAPCOM Timer 7 T7IR T7IE T7INT 00’00F4

CAPCOM Timer 8 T8IR T8IE T8INT 00’00F8

GPT1 Timer 2 T2IR T2IE T2INT 00’0088

GPT1 Timer 3 T3IR T3IE T3INT 00’008C

GPT1 Timer 4 T4IR T4IE T4INT 00’0090

GPT2 Timer 5 T5IR T5IE T5INT 00’0094

GPT2 Timer 6 T6IR T6IE T6INT 00’0098

GPT2 CAPREL Reg. CRIR CRIE CRINT 00’009C

A/D Conversion

ADCIR ADCIE ADCINT 00’00A0

Complete

H

H

H

H

H

H

H

H

H

H

H

H

H

Trap

Number

45

H

46

H

20

H

21

H

3D

H

3E

H

22

H

23

H

24

H

25

H

26

H

27

H

28

H

A/D Overrun Error ADEIR ADEIE ADEINT 00’00A4

ASC0 Transmit S0TIR S0TIE S0TINT 00’00A8

ASC0 Transmit Buffer S0TBIR S0TBIE S0TBINT 00’011C

ASC0 Receive S0RIR S0RIE S0RINT 00’00AC

ASC0 Error S0EIR S0EIE S0EINT 00’00B0

SSC Transmit SCTIR SCTIE SCTINT 00’00B4

SSC Receive SCRIR SCRIE SCRINT 00’00B8

SSC Error SCEIR SCEIE SCEINT 00’00BC

PWM Channel 0 … 3 PWMIR PWMIE PWMINT 00’00FC

CAN Interface 1 XP0IR XP0IE XP0INT 00’0100

CAN Interface 2 XP1IR XP1IE XP1INT 00’0104

Unassigned node XP2IR XP2IE XP2INT 00’0108

PLL/OWD and RTC XP3IR XP3IE XP3INT 00’010C

29

H

H

H

H

H

H

H

H

H

H

H

H

H

2A

47

2B

2C

2D

2E

2F

3F

40

41

42

43

H

H

H

H

H

H

H

H

H

H

H

H

H

Data Sheet 21 V2.2, 2001-08

C167CS-4R

C167CS-L

The C167CS also provides an excellent mechanism to identify and to process

exceptions or error conditions that arise during run-time, so-called ‘Hardware Traps’.

Hardware traps cause immediate non-maskable system reaction which is similar to a

standard interrupt service (branching to a dedicated vector table location). The

occurrence of a hardware trap is additionally signified by an individual bit in the trap flag

register (TFR). Except when another higher prioritized trap service is in progress, a

hardware trap will interrupt any actual program execution. In turn, hardware trap services

can normally not be interrupted by standard or PEC interrupts.

Table 4 shows all of the possible exceptions or error conditions that can arise during run-

time:

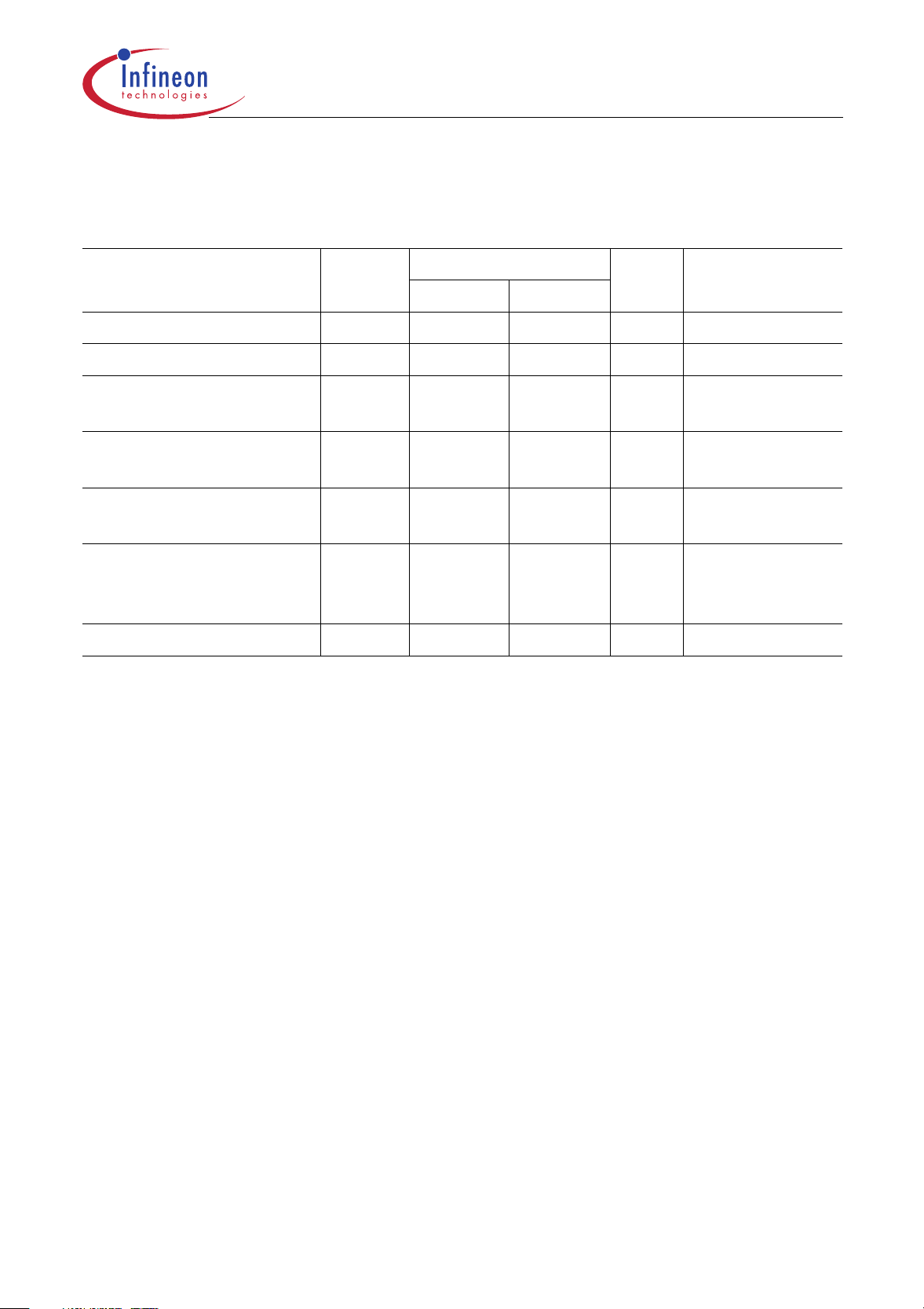

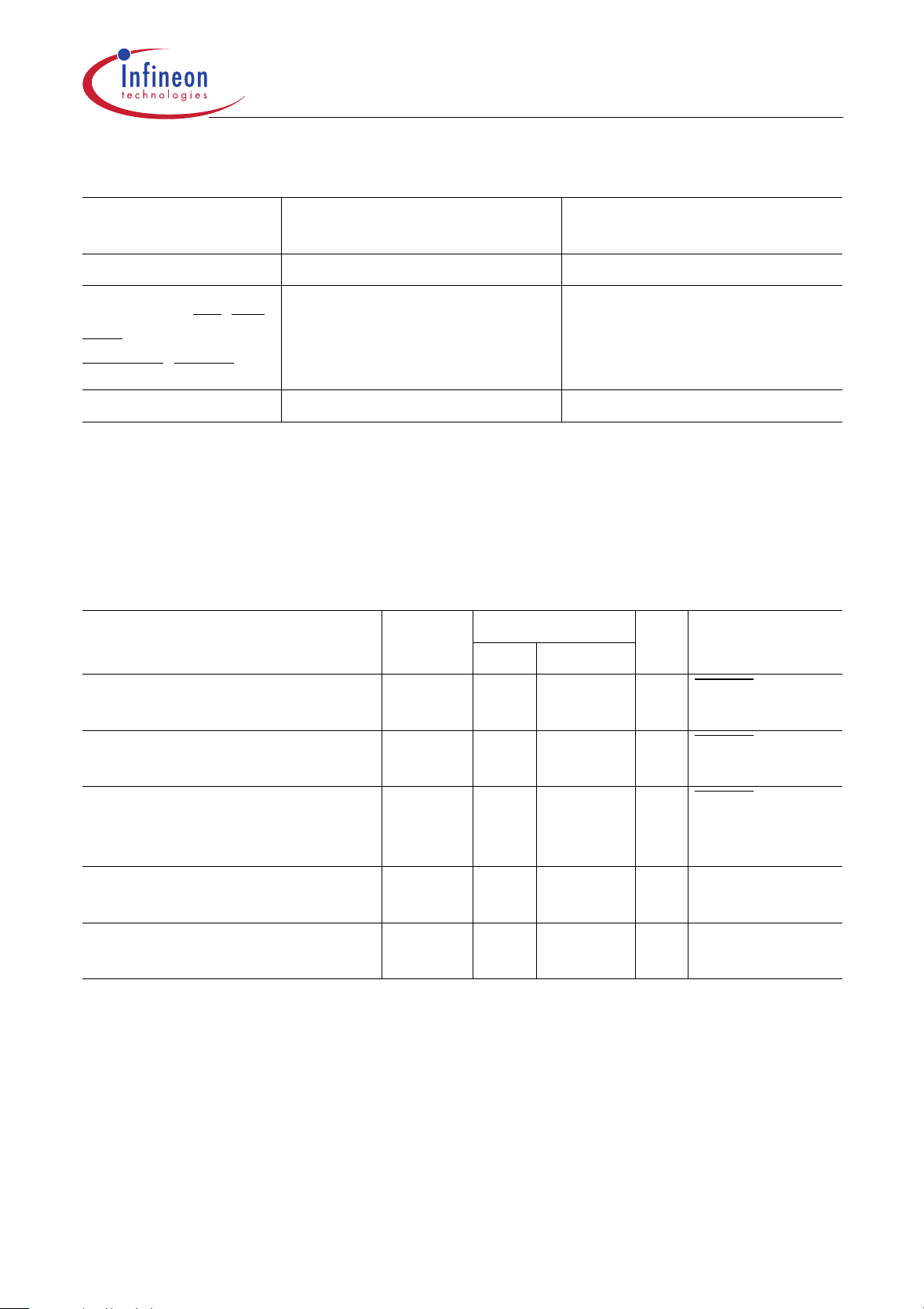

Table 4 Hardware Trap Summary

Exception Condition Trap

Flag

Reset Functions:

–

– Hardware Reset

– Software Reset

– W-dog Timer Overflow

Class A Hardware Traps:

– Non-Maskable Interrupt

– Stack Overflow

– Stack Underflow

NMI

STKOF

STKUF

Class B Hardware Traps:

– Undefined Opcode

– Protected Instruction

UNDOPC

PRTFLT

Fault

– Illegal Word Operand

ILLOPA

Access

– Illegal Instruction

ILLINA

Access

– Illegal External Bus

ILLBUS

Access

Trap

Vector

RESET

RESET

RESET

NMITRAP

STOTRAP

STUTRAP

BTRAP

BTRAP

BTRAP

BTRAP

BTRAP

Vector

Location

00’0000

00’0000

00’0000

00’0008

00’0010

00’0018

00’0028

00’0028

00’0028

00’0028

00’0028

H

H

H

H

H

H

H

H

H

H

H

Trap

Number

00

H

00

H

00

H

02

H

04

H

06

H

0A

H

0A

H

0A

H

0A

H

0A

H

Trap

Priority

III

III

III

II

II

II

I

I

I

I

I

Reserved –– [2C

Software Traps

–– Any

– TRAP Instruction

–

H

3C

]

H

[00’0000

00’01FC

–

[0B

H

0F

]

H

Any

–

H

]

H

[00

7F

–

H

]

H

–

Current

CPU

Priority

in steps

of 4

H

Data Sheet 22 V2.2, 2001-08

C167CS-4R

C167CS-L

Capture/Compare (CAPCOM) Units

The CAPCOM units support generation and control of timing sequences on up to

32 channels with a maximum resolution of 16 TCL. The CAPCOM units are typically

used to handle high speed I/O tasks such as pulse and waveform generation, pulse

width modulation (PMW), Digital to Analog (D/A) conversion, software timing, or time

recording relative to external events.

Four 16-bit timers (T0/T1, T7/T8) with reload registers provide two independent time

bases for the capture/compare register array.

The input clock for the timers is programmable to several prescaled values of the internal

system clock, or may be derived from an overflow/underflow of timer T6 in module GPT2.

This provides a wide range of variation for the timer period and resolution and allows

precise adjustments to the application specific requirements. In addition, external count

inputs for CAPCOM timers T0 and T7 allow event scheduling for the capture/compare

registers relative to external events.

Both of the two capture/compare register arrays contain 16 dual purpose capture/

compare registers, each of which may be individually allocated to either CAPCOM timer

T0 or T1 (T7 or T8, respectively), and programmed for capture or compare function.

Each register has one port pin associated with it which serves as an input pin for

triggering the capture function, or as an output pin to indicate the occurrence of a

compare event.

When a capture/compare register has been selected for capture mode, the current

contents of the allocated timer will be latched (‘capture’d) into the capture/compare

register in response to an external event at the port pin which is associated with this

register. In addition, a specific interrupt request for this capture/compare register is

generated. Either a positive, a negative, or both a positive and a negative external signal

transition at the pin can be selected as the triggering event. The contents of all registers

which have been selected for one of the five compare modes are continuously compared

with the contents of the allocated timers. When a match occurs between the timer value

and the value in a capture/compare register, specific actions will be taken based on the

selected compare mode.

Data Sheet 23 V2.2, 2001-08

C167CS-4R

C167CS-L

Table 5 Compare Modes (CAPCOM)

Compare Modes Function

Mode 0 Interrupt-only compare mode;

several compare interrupts per timer period are possible.

Mode 1 Pin toggles on each compare match;

several compare events per timer period are possible.

Mode 2 Interrupt-only compare mode;

only one compare interrupt per timer period is generated.

Mode 3 Pin set ‘1’ on match; pin reset ‘0’ on compare time overflow;

only one compare event per timer period is generated.

Double

Register Mode

Two registers operate on one pin;

pin toggles on each compare match;

several compare events per timer period are possible.

Data Sheet 24 V2.2, 2001-08

C167CS-4R

C167CS-L

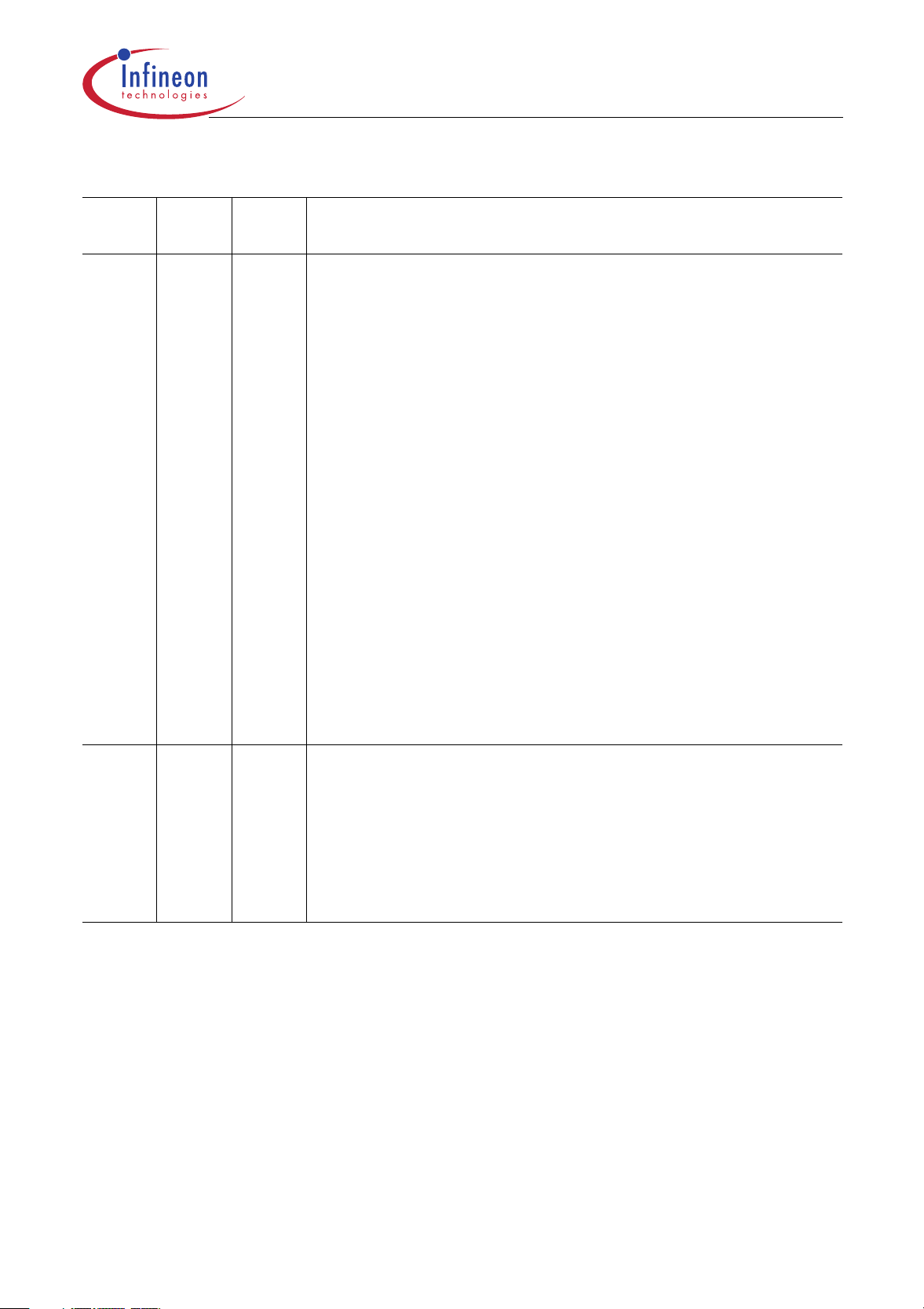

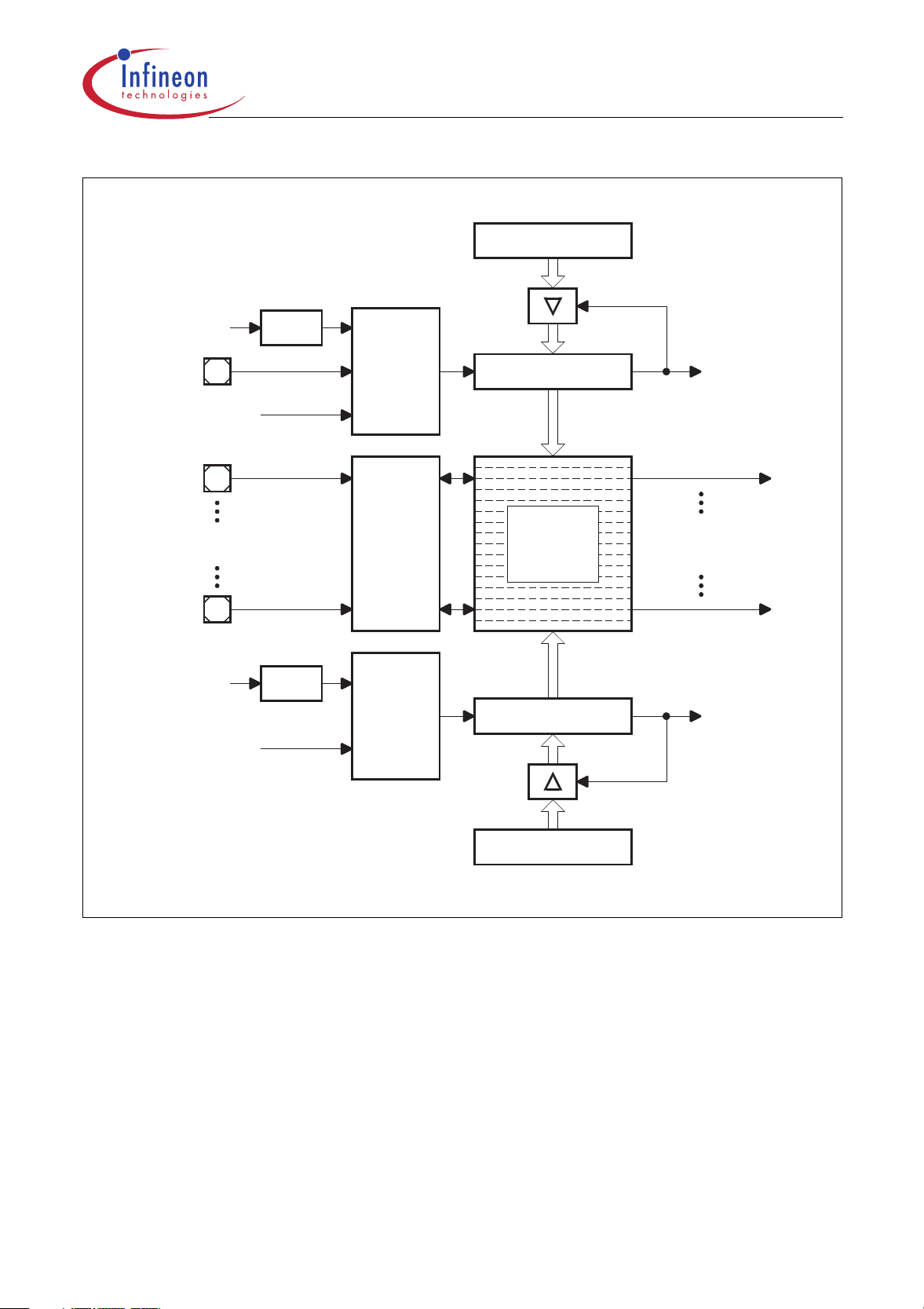

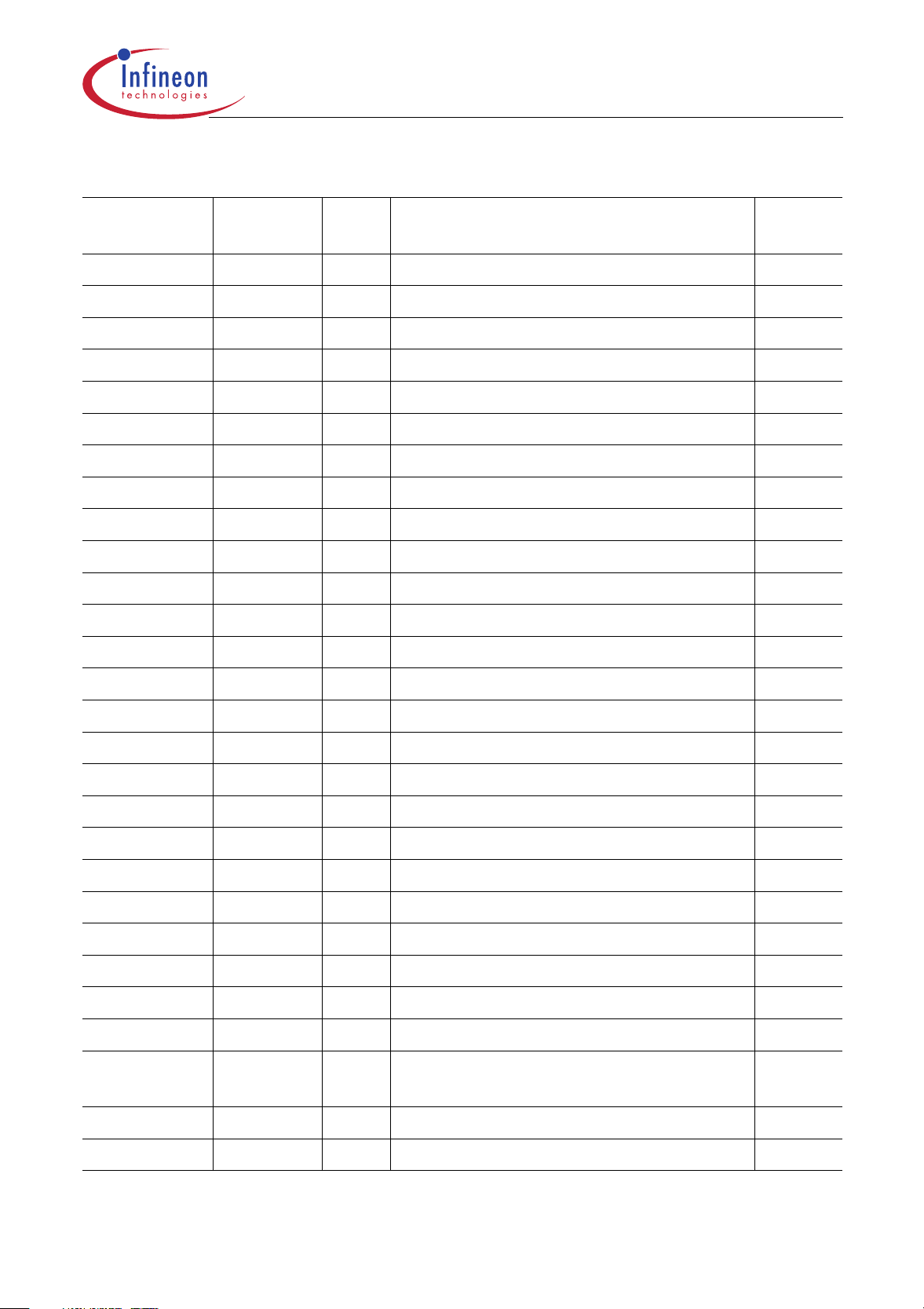

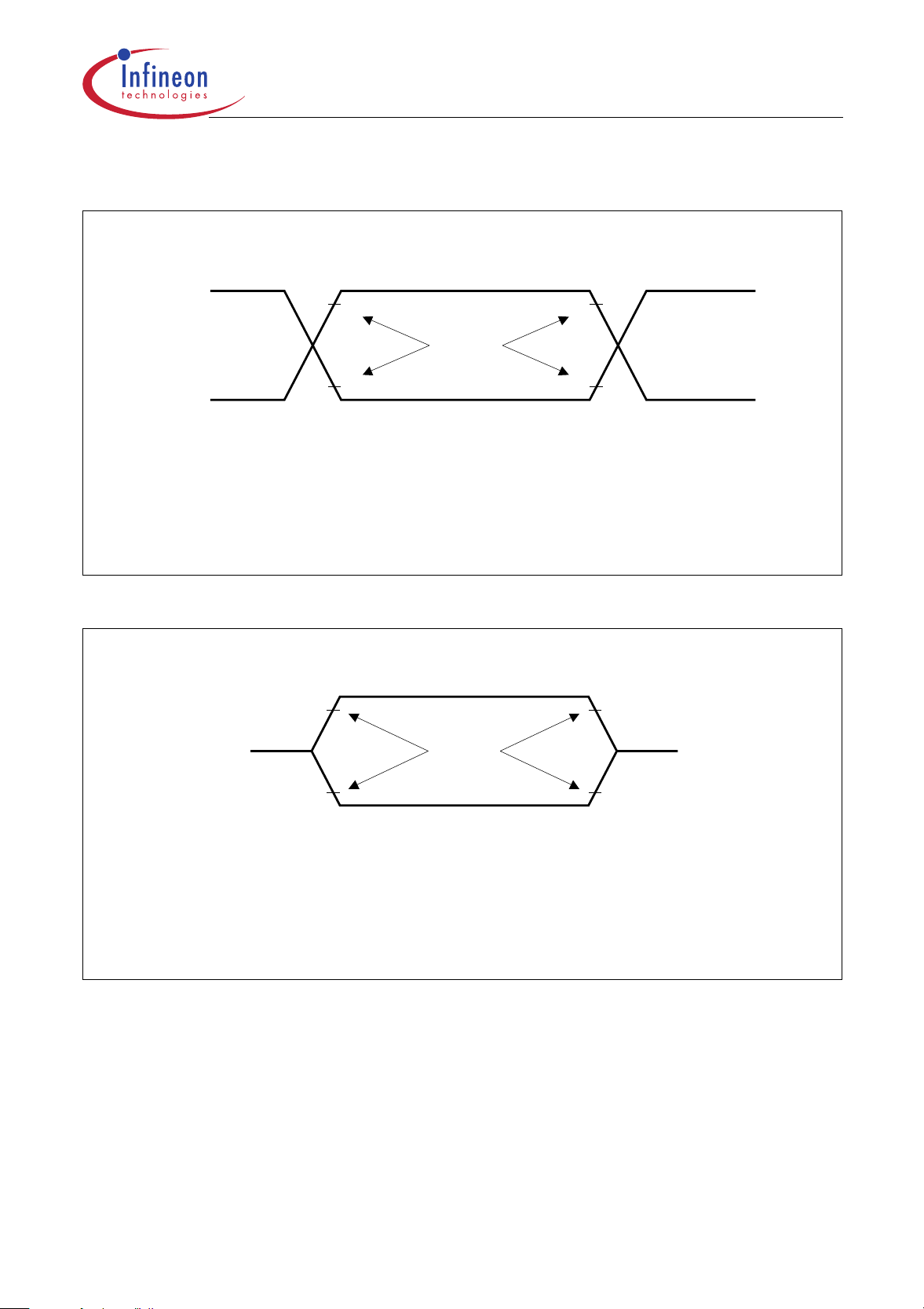

Reload Reg. TxREL

CPU

TxIN

GPT2 Timer T6

Over/Underflow

CCxIO

16 Capture Inputs

16 Compare Outputs

CCxIO

CPU

GPT2 Timer T6

Over/Underflow

2n : 1f

2n : 1f

Tx

Input

Control

Mode

Control

(Capture

or

Compare)

Ty

Input

Control

CAPCOM Timer Tx

16-Bit

Capture/

Compare

Registers

CAPCOM Timer Ty

Interrupt

Request

(TxIR)

16 Capture/Compare

Interrupt Request

Interrupt

Request

(TyIR)

x = 0, 7

y = 1, 8

n = 3 … 10

Reload Reg. TyREL

MCB02143B

Figure 5 CAPCOM Unit Block Diagram

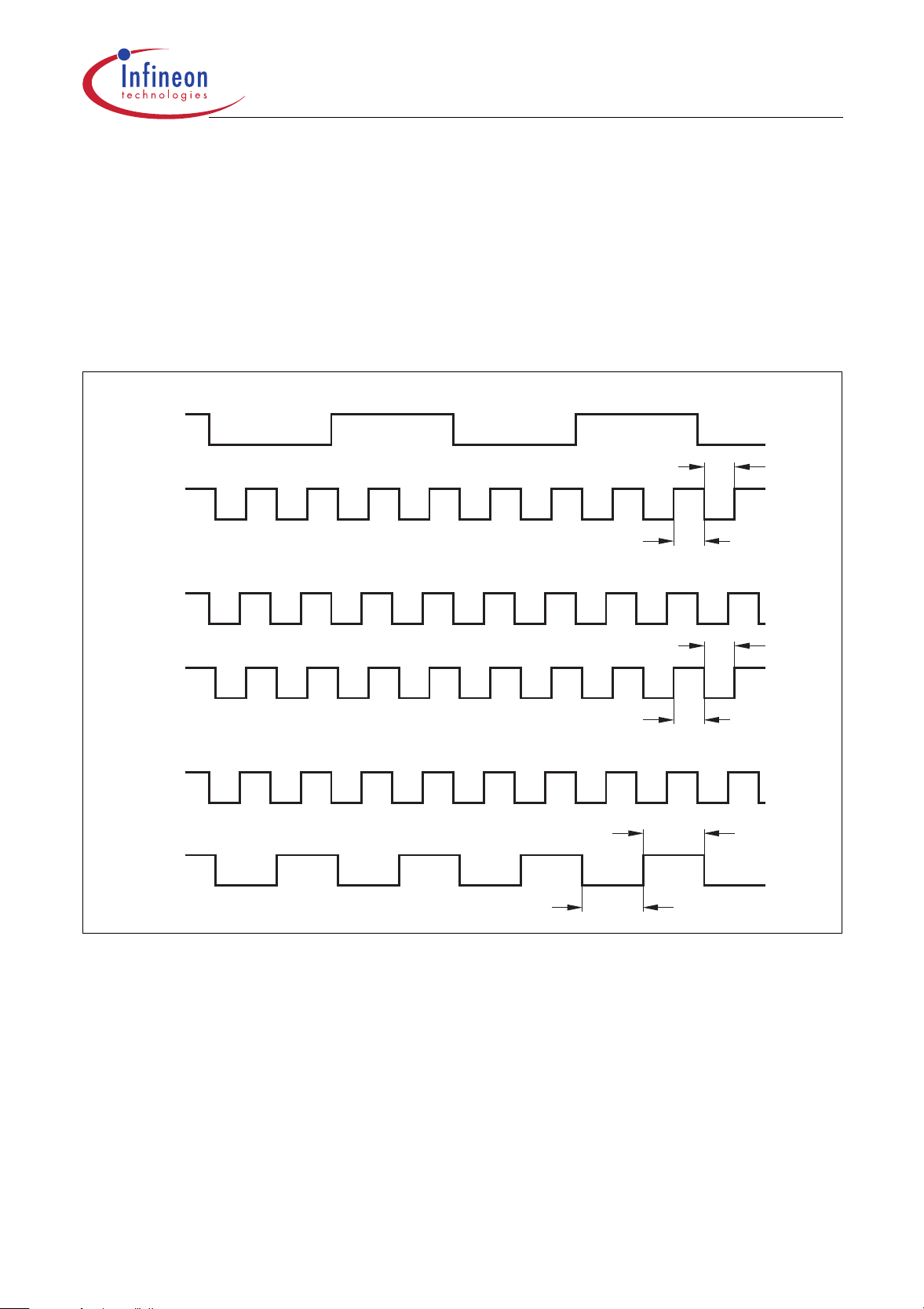

PWM Module

The Pulse Width Modulation Module can generate up to four PWM output signals using

edge-aligned or center-aligned PWM. In addition the PWM module can generate PWM

burst signals and single shot outputs. The frequency range of the PWM signals covers

5 Hz to 20 MHz (referred to a CPU clock of 40 MHz), depending on the resolution of the

PWM output signal. The level of the output signals is selectable and the PWM module

can generate interrupt requests.

Data Sheet 25 V2.2, 2001-08

C167CS-4R

C167CS-L

General Purpose Timer (GPT) Unit

The GPT unit represents a very flexible multifunctional timer/counter structure which

may be used for many different time related tasks such as event timing and counting,

pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT unit incorporates five 16-bit timers which are organized in two separate

modules, GPT1 and GPT2. Each timer in each module may operate independently in a

number of different modes, or may be concatenated with another timer of the same

module.

Each of the three timers T2, T3, T4 of module GPT1 can be configured individually for

one of four basic modes of operation, which are Timer, Gated Timer, Counter, and

Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from

the CPU clock, divided by a programmable prescaler, while Counter Mode allows a timer

to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the

operation of a timer is controlled by the ‘gate’ level on an external input pin. For these

purposes, each timer has one associated port pin (TxIN) which serves as gate or clock

input. The maximum resolution of the timers in module GPT1 is 16 TCL.

The count direction (up/down) for each timer is programmable by software or may

additionally be altered dynamically by an external signal on a port pin (TxEUD) to

facilitate e.g. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected

to the incremental position sensor signals A and B via their respective inputs TxIN and

TxEUD. Direction and count signals are internally derived from these two input signals,

so the contents of the respective timer Tx corresponds to the sensor position. The third

position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out

monitoring of external hardware components, or may be used internally to clock timers

T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload

or capture registers for timer T3. When used as capture or reload registers, timers T2

and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a

signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2

or T4 triggered either by an external signal or by a selectable state transition of its toggle

latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite

state transitions of T3OTL with the low and high times of a PWM signal, this signal can

be constantly generated without software intervention.

Data Sheet 26 V2.2, 2001-08

C167CS-4R

C167CS-L

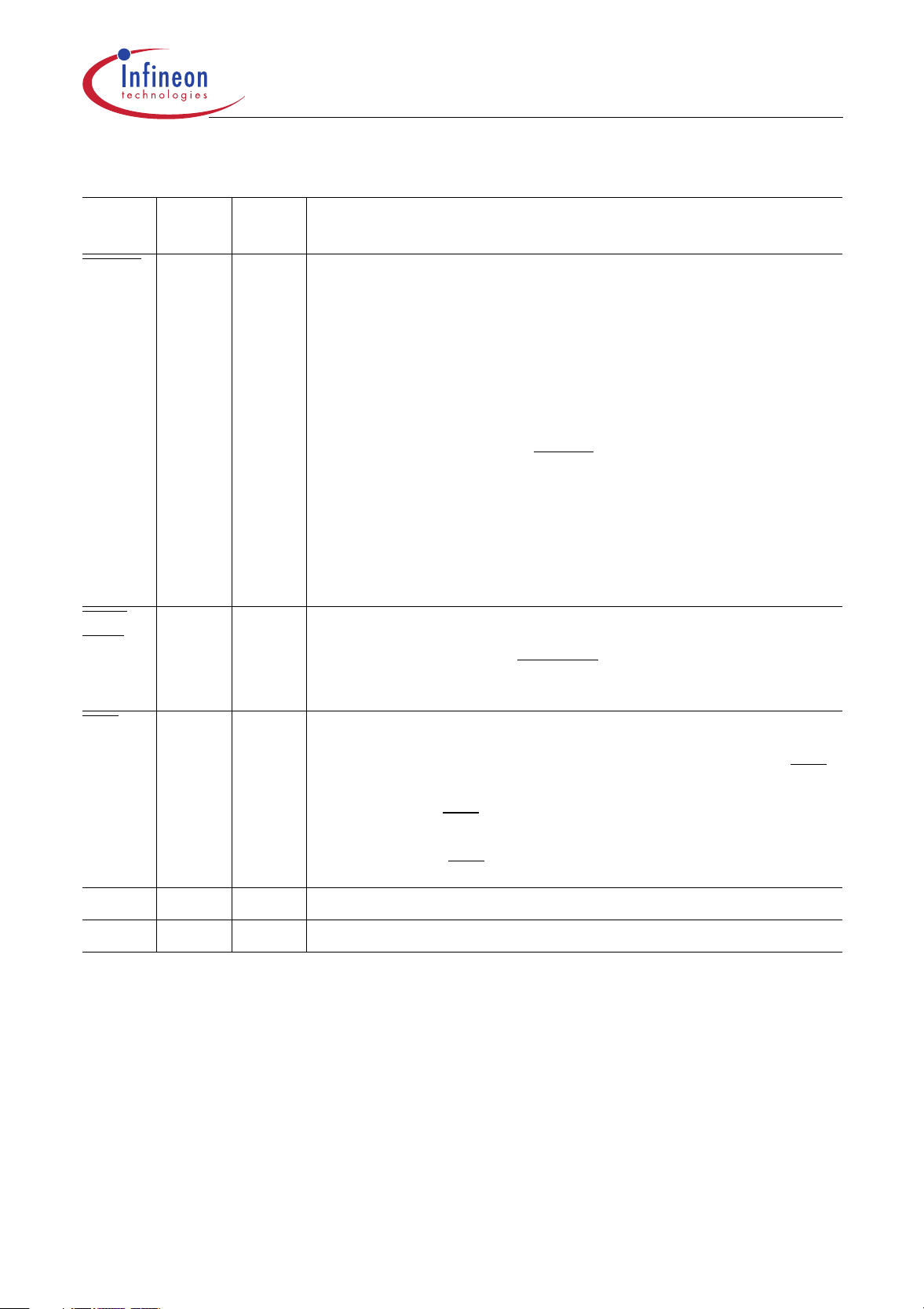

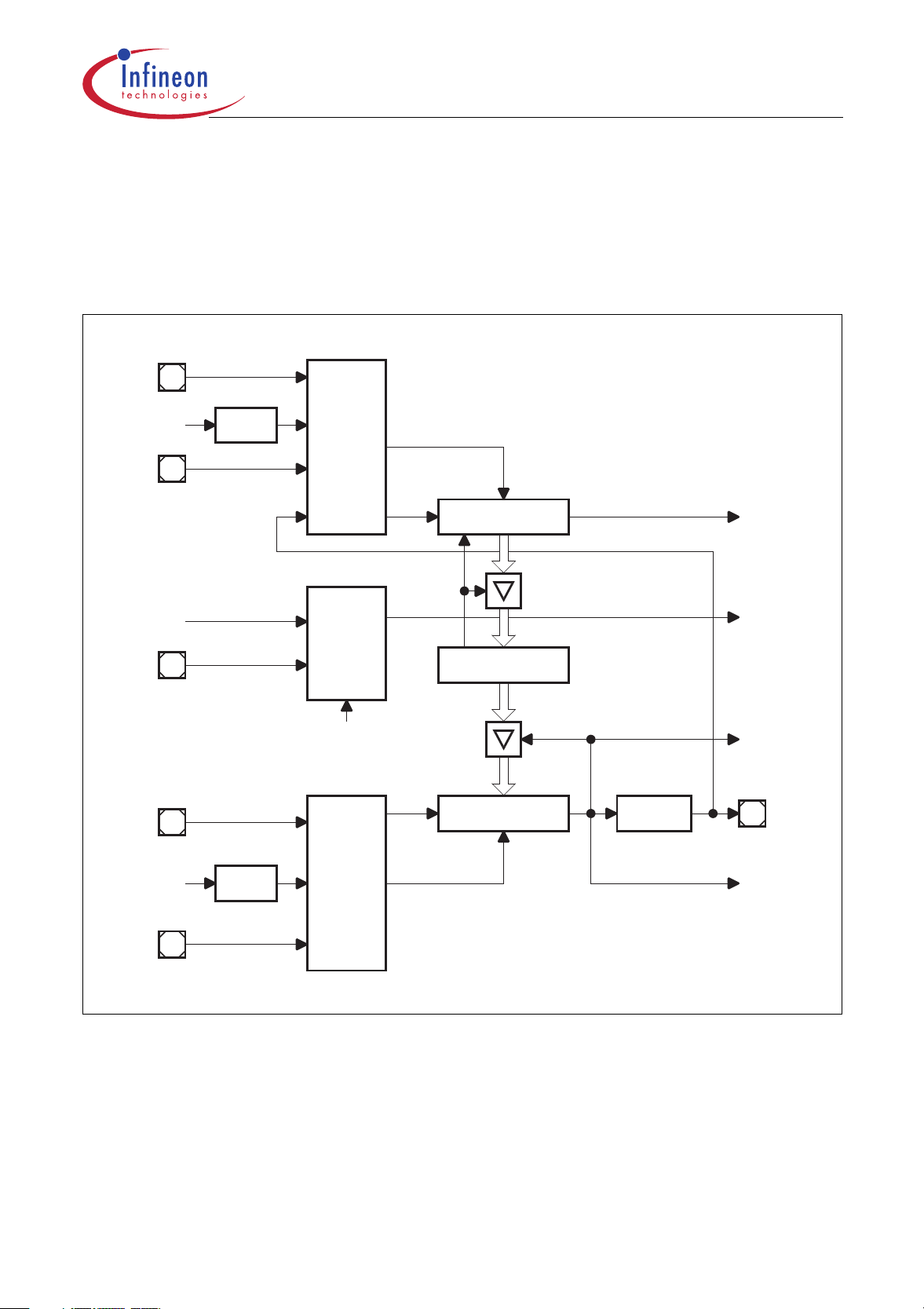

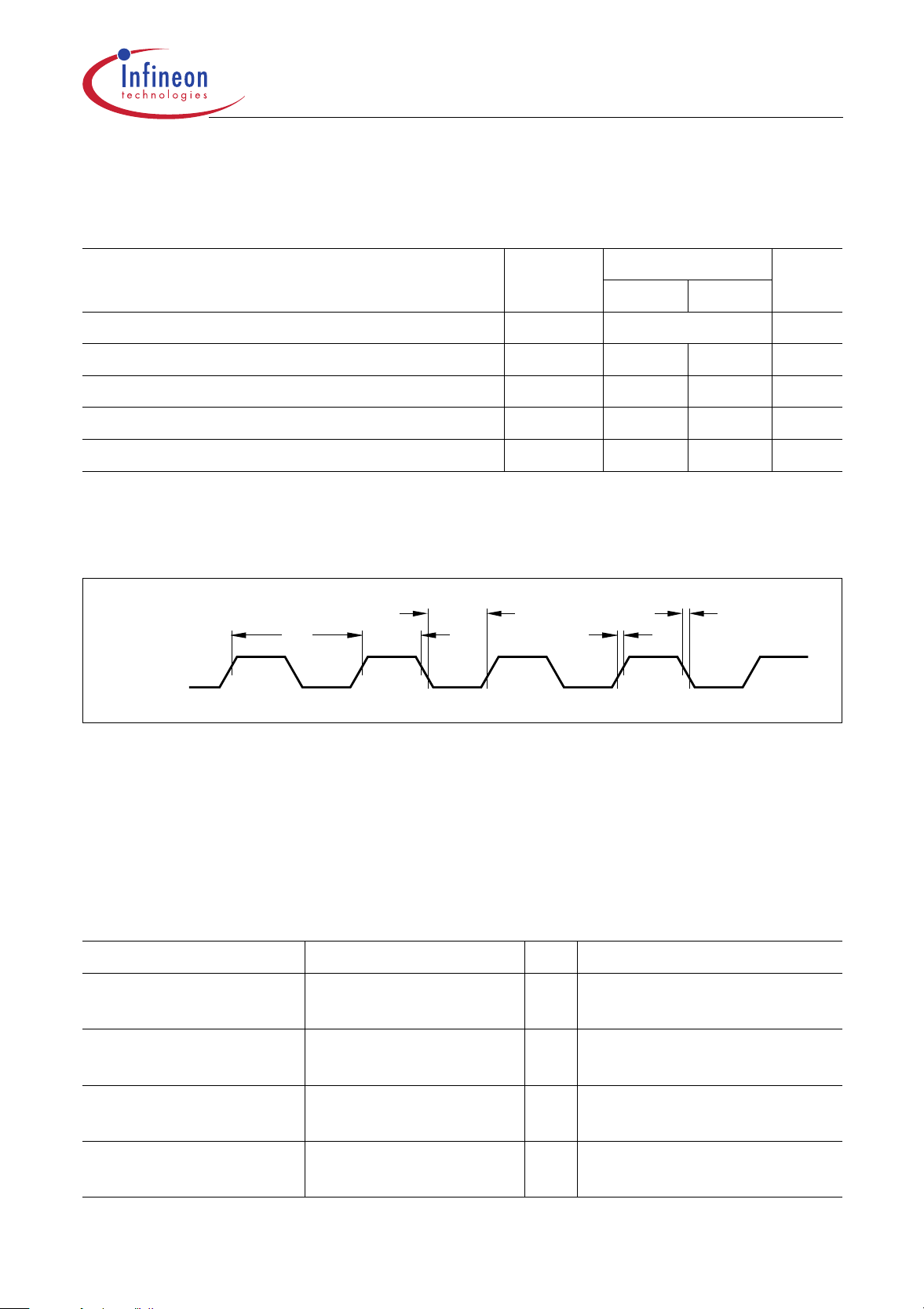

T2EUD

CPU

T2IN

CPU

T3IN

T3EUD

T4IN

CPU

T4EUD

n = 3 … 10

U/D

Interrupt

2n : 1f

2n : 1f

2n : 1f

T2

Mode

Control

T3

Mode

Control

T4

Mode

Control

GPT1 Timer T2

Reload

Capture

Toggle FF

GPT1 Timer T3 T3OTL

U/D

Capture

Reload

GPT1 Timer T4

U/D

Request

(T2IR)

Interrupt

Request

(T3IR)

T3OUT

Interrupt

Request

(T4IR)

MCT04825

Figure 6 Block Diagram of GPT1

With its maximum resolution of 8 TCL, the GPT2 module provides precise event control

and time measurement. It includes two timers (T5, T6) and a capture/reload register

(CAPREL). Both timers can be clocked with an input clock which is derived from the CPU

clock via a programmable prescaler or with external signals. The count direction (up/

down) for each timer is programmable by software or may additionally be altered

dynamically by an external signal on a port pin (TxEUD). Concatenation of the timers is

supported via the output toggle latch (T6OTL) of timer T6, which changes its state on

each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin

T6OUT. The overflows/underflows of timer T6 can additionally be used to clock the

CAPCOM timers T0 or T1, and to cause a reload from the CAPREL register. The

CAPREL register may capture the contents of timer T5 based on an external signal

transition on the corresponding port pin (CAPIN), and timer T5 may optionally be cleared

Data Sheet 27 V2.2, 2001-08

C167CS-4R

C167CS-L

after the capture procedure. This allows the C167CS to measure absolute time

differences or to perform pulse multiplication without software overhead.

The capture trigger (timer T5 to CAPREL) may also be generated upon transitions of

GPT1 timer T3’s inputs T3IN and/or T3EUD. This is especially advantageous when T3

operates in Incremental Interface Mode.

T5EUD

T5IN

CAPIN

T6IN

CPU

T3

CPU

2n : 1f

2n : 1f

T5

Mode

Control

MUX

CT3

T6

Mode

Control

Clear

Capture

U/D

GPT2 Timer T5

GPT2 CAPREL

GPT2 Timer T6

U/D

T6OTL

Interrupt

Request

Interrupt

Request

Interrupt

Request

T6OUT

Other

Timers

T6EUD

MCB03999

n = 2 … 9

Figure 7 Block Diagram of GPT2

Data Sheet 28 V2.2, 2001-08

C167CS-4R

C167CS-L

Real Time Clock

The Real Time Clock (RTC) module of the C167CS consists of a chain of 3 divider

blocks, a fixed 8:1 divider, the reloadable 16-bit timer T14, and the 32-bit RTC timer

(accessible via registers RTCH and RTCL). The RTC module is directly clocked with the

on-chip oscillator frequency divided by 32 via a separate clock driver (

and is therefore independent from the selected clock generation mode of the C167CS.

All timers count up.

The RTC module can be used for different purposes:

• System clock to determine the current time and date

• Cyclic time based interrupt

• 48-bit timer for long term measurements

f

RTC

= f

OSC

/32)

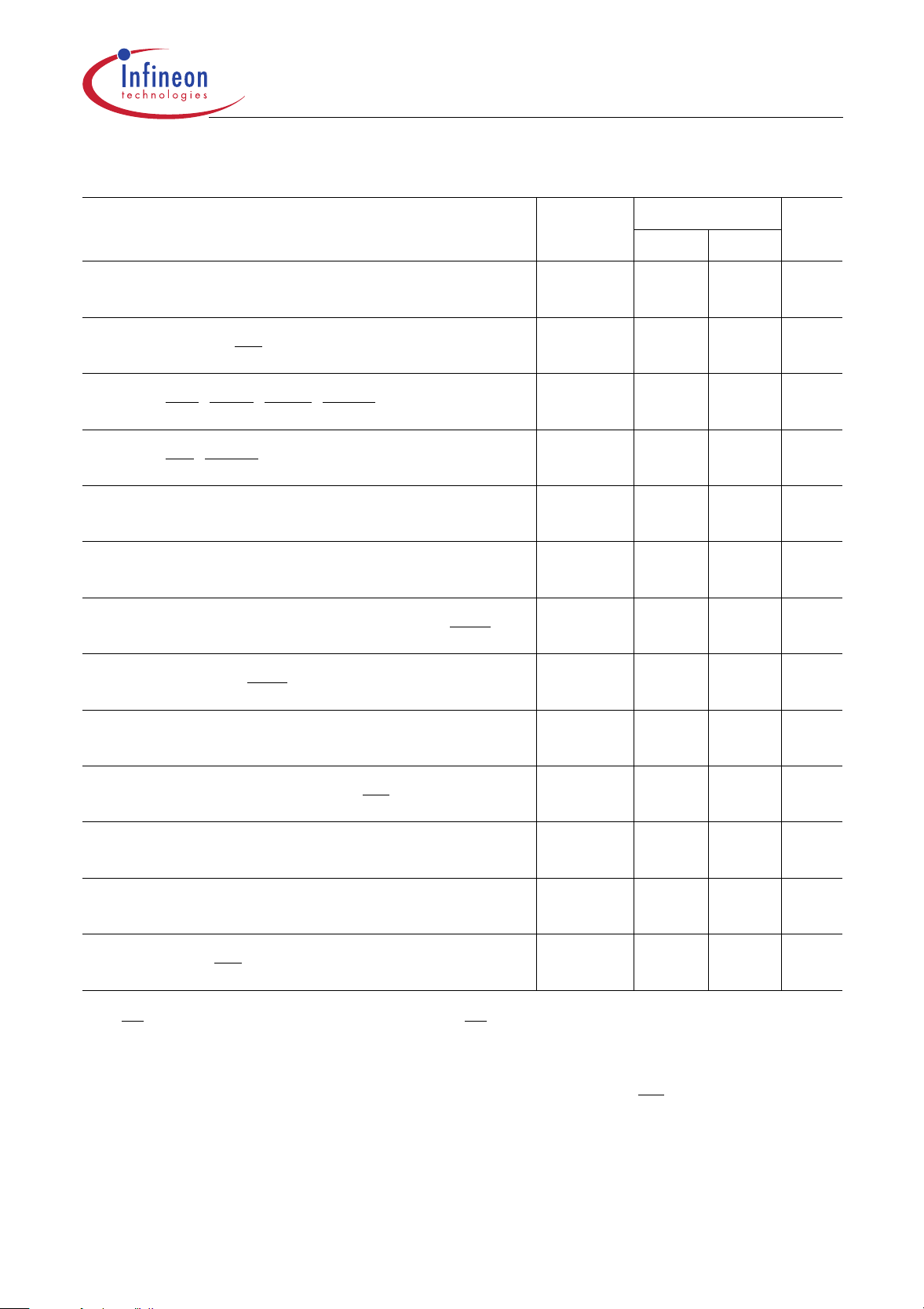

T14REL

Reload

f

T14 8:1

RTCLRTCH

RTC

Interrupt

Request

MCD04432

Figure 8 RTC Block Diagram

Note: The registers associated with the RTC are not affected by a reset in order to

maintain the correct system time even when intermediate resets are executed.

Data Sheet 29 V2.2, 2001-08

C167CS-4R

C167CS-L

A/D Converter

For analog signal measurement, a 10-bit A/D converter with 24 multiplexed input

channels (16 standard channels and 8 extension channels) and a sample and hold

circuit has been integrated on-chip. It uses the method of successive approximation. The

sample time (for loading the capacitors) and the conversion time is programmable and

can so be adjusted to the external circuitry.

Overrun error detection/protection is provided for the conversion result register

(ADDAT): either an interrupt request will be generated when the result of a previous

conversion has not been read from the result register at the time the next conversion is

complete, or the next conversion is suspended in such a case until the previous result

has been read.

For applications which require less than 24 analog input channels, the remaining

channel inputs can be used as digital input port pins.

The A/D converter of the C167CS supports four different conversion modes. In the

standard Single Channel conversion mode, the analog level on a specified channel is

sampled once and converted to a digital result. In the Single Channel Continuous mode,

the analog level on a specified channel is repeatedly sampled and converted without

software intervention. In the Auto Scan mode, the analog levels on a prespecified

number of channels (standard or extension) are sequentially sampled and converted. In

the Auto Scan Continuous mode, the number of prespecified channels is repeatedly

sampled and converted. In addition, the conversion of a specific channel can be inserted

(injected) into a running sequence without disturbing this sequence. This is called

Channel Injection Mode.

The Peripheral Event Controller (PEC) may be used to automatically store the

conversion results into a table in memory for later evaluation, without requiring the

overhead of entering and exiting interrupt routines for each data transfer.

After each reset and also during normal operation the ADC automatically performs

calibration cycles. This automatic self-calibration constantly adjusts the converter to

changing operating conditions (e.g. temperature) and compensates process variations.

These calibration cycles are part of the conversion cycle, so they do not affect the normal

operation of the A/D converter.

In order to decouple analog inputs from digital noise and to avoid input trigger noise

those pins used for analog input can be disconnected from the digital IO or input stages

under software control. This can be selected for each pin separately via registers

P5DIDIS (Port 5 Digital Input Disable) and P1DIDIS (PORT1 Digital Input Disable).

Data Sheet 30 V2.2, 2001-08

C167CS-4R

C167CS-L

Serial Channels

Serial communication with other microcontrollers, processors, terminals or external

peripheral components is provided by two serial interfaces with different functionality, an

Asynchronous/Synchronous Serial Channel (ASC0) and a High-Speed Synchronous

Serial Channel (SSC).

The ASC0 is upward compatible with the serial ports of the Infineon 8-bit microcontroller

families and supports full-duplex asynchronous communication at up to 781 Kbit/s/

1.03 Mbit/s/1.25 Mbit/s and half-duplex synchronous communication at up to 3.1/

4.1 Mbit/s/5.0 Mbit/s (@ 25/33/40 MHz CPU clock).

A dedicated baud rate generator allows to set up all standard baud rates without

oscillator tuning. For transmission, reception and error handling 4 separate interrupt

vectors are provided. In asynchronous mode, 8- or 9-bit data frames are transmitted or

received, preceded by a start bit and terminated by one or two stop bits. For

multiprocessor communication, a mechanism to distinguish address from data bytes has

been included (8-bit data plus wake up bit mode).

In synchronous mode, the ASC0 transmits or receives bytes (8 bits) synchronously to a

shift clock which is generated by the ASC0. The ASC0 always shifts the LSB first. A loop

back option is available for testing purposes.

A number of optional hardware error detection capabilities has been included to increase

the reliability of data transfers. A parity bit can automatically be generated on

transmission or be checked on reception. Framing error detection allows to recognize

data frames with missing stop bits. An overrun error will be generated, if the last

character received has not been read out of the receive buffer register at the time the

reception of a new character is complete.

The SSC supports full-duplex synchronous communication at up to 6.25/8.25/10 Mbit/s

(@ 25/33/40 MHz CPU clock). It may be configured so it interfaces with serially linked

peripheral components. A dedicated baud rate generator allows to set up all standard

baud rates without oscillator tuning. For transmission, reception and error handling

3 separate interrupt vectors are provided.

The SSC transmits or receives characters of 2 … 16 bits length synchronously to a shift

clock which can be generated by the SSC (master mode) or by an external master (slave

mode). The SSC can start shifting with the LSB or with the MSB and allows the selection

of shifting and latching clock edges as well as the clock polarity.

A number of optional hardware error detection capabilities has been included to increase

the reliability of data transfers. Transmit and receive error supervise the correct handling

of the data buffer. Phase and baudrate error detect incorrect serial data.

Data Sheet 31 V2.2, 2001-08

C167CS-4R

C167CS-L

CAN-Modules

The integrated CAN-Modules handle the completely autonomous transmission and

reception of CAN frames in accordance with the CAN specification V2.0 part B (active),

i.e. the on-chip CAN-Modules can receive and transmit standard frames with 11-bit

identifiers as well as extended frames with 29-bit identifiers.

The modules provide Full CAN functionality on up to 15 message objects each. Message

object 15 may be configured for Basic CAN functionality. Both modes provide separate

masks for acceptance filtering which allows to accept a number of identifiers in Full CAN

mode and also allows to disregard a number of identifiers in Basic CAN mode. All

message objects can be updated independent from the other objects and are equipped

for the maximum message length of 8 bytes.

The bit timing is derived from the XCLK and is programmable up to a data rate of 1 Mbit/

s. Each CAN-Module uses two pins of Port 4 or Port 8 to interface to an external bus

transceiver. The interface pins are assigned via software.

Module CAN2 is identical with the first one, except that it uses a separate address area

and a separate interrupt node.

The two CAN modules can be internally coupled by assigning their interface pins to the

same two port pins, or they can interface to separate CAN buses.

Note: When any CAN interface is assigned to Port 4, the respective segment address

lines on Port 4 cannot be used. This will limit the external address space.

Watchdog Timer

The Watchdog Timer represents one of the fail-safe mechanisms which have been

implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after a reset of the chip, and can only be

disabled in the time interval until the EINIT (end of initialization) instruction has been

executed. Thus, the chip’s start-up procedure is always monitored. The software has to

be designed to service the Watchdog Timer before it overflows. If, due to hardware or

software related failures, the software fails to do so, the Watchdog Timer overflows and

generates an internal hardware reset and pulls the RSTOUT

external hardware components to be reset.

The Watchdog Timer is a 16-bit timer, clocked with the system clock divided by 2/4/128/

256. The high byte of the Watchdog Timer register can be set to a prespecified reload

value (stored in WDTREL) in order to allow further variation of the monitored time

interval. Each time it is serviced by the application software, the high byte of the

Watchdog Timer is reloaded. Thus, time intervals between 12.8

monitored (@ 40 MHz).

The default Watchdog Timer interval after reset is 3.27 ms (@ 40 MHz).

pin low in order to allow

µs and 419 ms can be

Data Sheet 32 V2.2, 2001-08

C167CS-4R

C167CS-L

Parallel Ports

The C167CS provides up to 111 I/O lines which are organized into eight input/output

ports and one input port. All port lines are bit-addressable, and all input/output lines are

individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O

ports are true bidirectional ports which are switched to high impedance state when

configured as inputs. The output drivers of five I/O ports can be configured (pin by pin)

for push/pull operation or open-drain operation via control registers. During the internal

reset, all port pins are configured as inputs.

The input threshold of Port 2, Port 3, Port 7, and Port 8 is selectable (TTL or CMOS like),

where the special CMOS like input threshold reduces noise sensitivity due to the input

hysteresis. The input threshold may be selected individually for each byte of the

respective ports.

All port lines have programmable alternate input or output functions associated with

them. All port lines that are not used for these alternate functions may be used as general

purpose IO lines.

PORT0 and PORT1 may be used as address and data lines when accessing external

memory, while Port 4 outputs the additional segment address bits A23/19/17 … A16 in

systems where segmentation is enabled to access more than 64 KBytes of memory.

Port 2, Port 8 and Port 7 (and parts of PORT1) are associated with the capture inputs or

compare outputs of the CAPCOM units and/or with the outputs of the PWM module.

Port 6 provides optional bus arbitration signals (BREQ

signals.

Port 3 includes alternate functions of timers, serial interfaces, the optional bus control

signal BHE

frequency output FOUT).

Port 5 (and parts of PORT1) is used for the analog input channels to the A/D converter

or timer control signals.

The edge characteristics (transition time) and driver characteristics (output current) of

the C167CS’s port drivers can be selected via the Port Output Control registers

(POCONx).

/WRH, and the system clock output CLKOUT (or the programmable

, HLDA, HOLD) and chip select

Data Sheet 33 V2.2, 2001-08

C167CS-4R

C167CS-L

Oscillator Watchdog

The Oscillator Watchdog (OWD) monitors the clock signal generated by the on-chip

oscillator (either with a crystal or via external clock drive). For this operation the PLL

provides a clock signal which is used to supervise transitions on the oscillator clock. This

PLL clock is independent from the XTAL1 clock. When the expected oscillator clock

transitions are missing the OWD activates the PLL Unlock/OWD interrupt node and

supplies the CPU with the PLL clock signal. Under these circumstances the PLL will

oscillate with its basic frequency.

In direct drive mode the PLL base frequency is used directly (

In prescaler mode the PLL base frequency is divided by 2 (

f

= 2 … 5 MHz).

CPU

f

= 1 … 2.5 MHz).

CPU

Note: The CPU clock source is only switched back to the oscillator clock after a

hardware reset.

The oscillator watchdog can be disabled by setting bit OWDDIS in register SYSCON.

In this case (OWDDIS = ‘1’) the PLL remains idle and provides no clock signal, while the

CPU clock signal is derived directly from the oscillator clock or via prescaler or SDD. Also

no interrupt request will be generated in case of a missing oscillator clock.

Note: At the end of a reset bit OWDDIS reflects the inverted level of pin RD

at that time.

Thus the oscillator watchdog may also be disabled via hardware by (externally)

pulling the RD

line low upon a reset, similar to the standard reset configuration via

PORT0.

Data Sheet 34 V2.2, 2001-08

C167CS-4R

C167CS-L

Power Management

The C167CS provides several means to control the power it consumes either at a given