BSC035N04LS G

OptiMOS®3 Power-Transistor

Features

• Fast switching MOSFET for SMPS

• Optimized technology for DC/DC converters

• Qualified according to JEDEC

• N-channel

• Logic level

• Excellent gate charge x R

• Very low on-resistance R

• Superior thermal resistance

• 100% Avalanche tested

• Pb-free plating; RoHS compliant

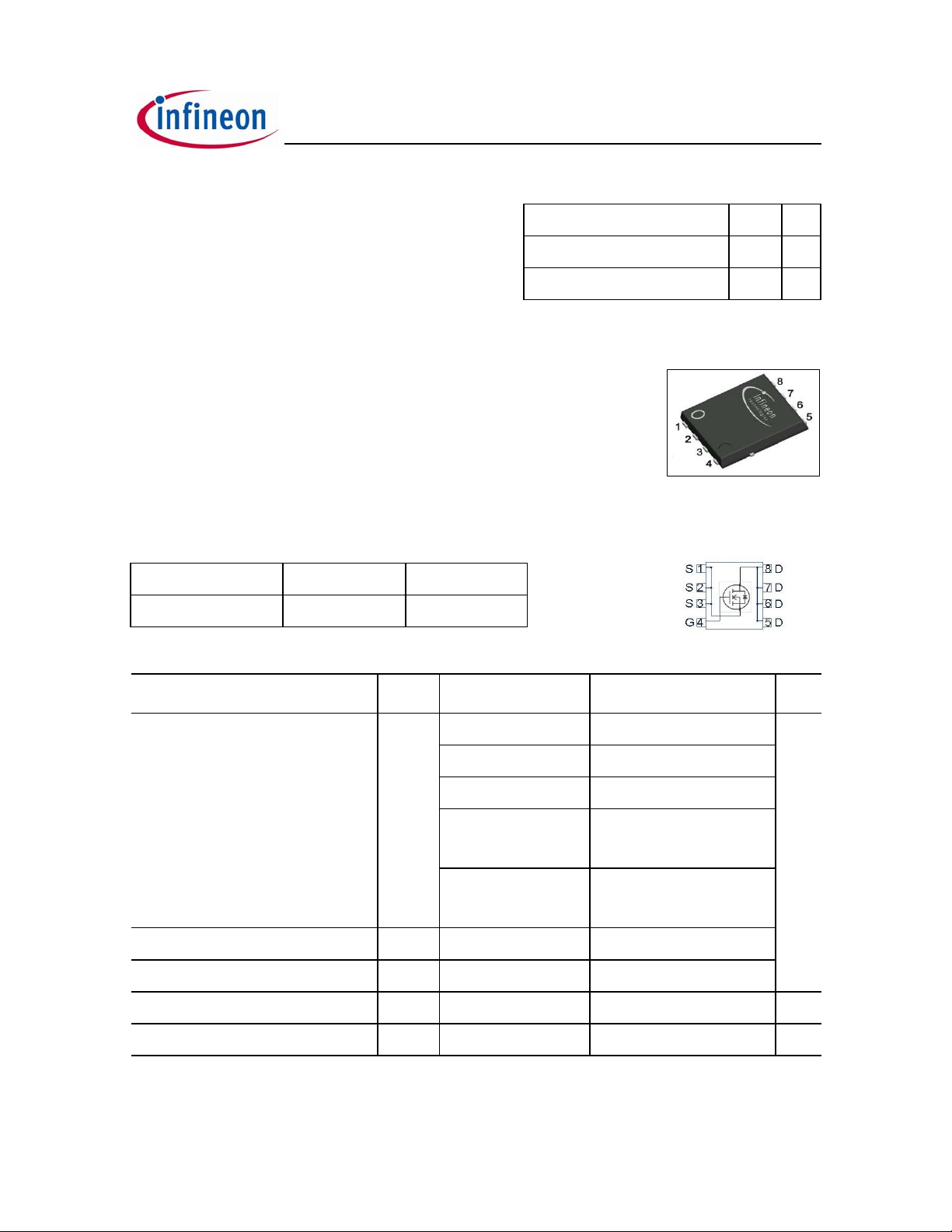

Type Package Marking

BSC035N04LS G PG-TDSON-8 035N04LS

1)

for target applications

product (FOM)

DS(on)

DS(on)

Product Summary

V

DS

R

DS(on),max

I

D

40 V

3.5

100 A

PG-TDSON-8

mΩ

Maximum ratings, at T

Parameter Symbol Conditions Unit

Continuous drain current

Pulsed drain current

Avalanche current, single pulse

Avalanche energy, single pulse

Gate source voltage

1)

J-STD20 and JESD22

=25 °C, unless otherwise specified

j

I

D

VGS=10 V, TC=25 °C

V

V

V

T

V

R

3)

4)

I

D,pulse

I

AS

E

AS

V

GS

TC=25 °C

TC=25 °C

ID=50 A, R

=10 V, TC=100 °C

GS

=4.5 V, TC=25 °C

GS

=4.5 V,

GS

=100 °C

C

=10 V, TA=25 °C,

GS

=50 K/W

thJA

GS

2)

=25 Ω

Value

100 A

71

92

58

21

400

50

65 mJ

±20 V

Rev. 1.01 page 1 2008-08-12

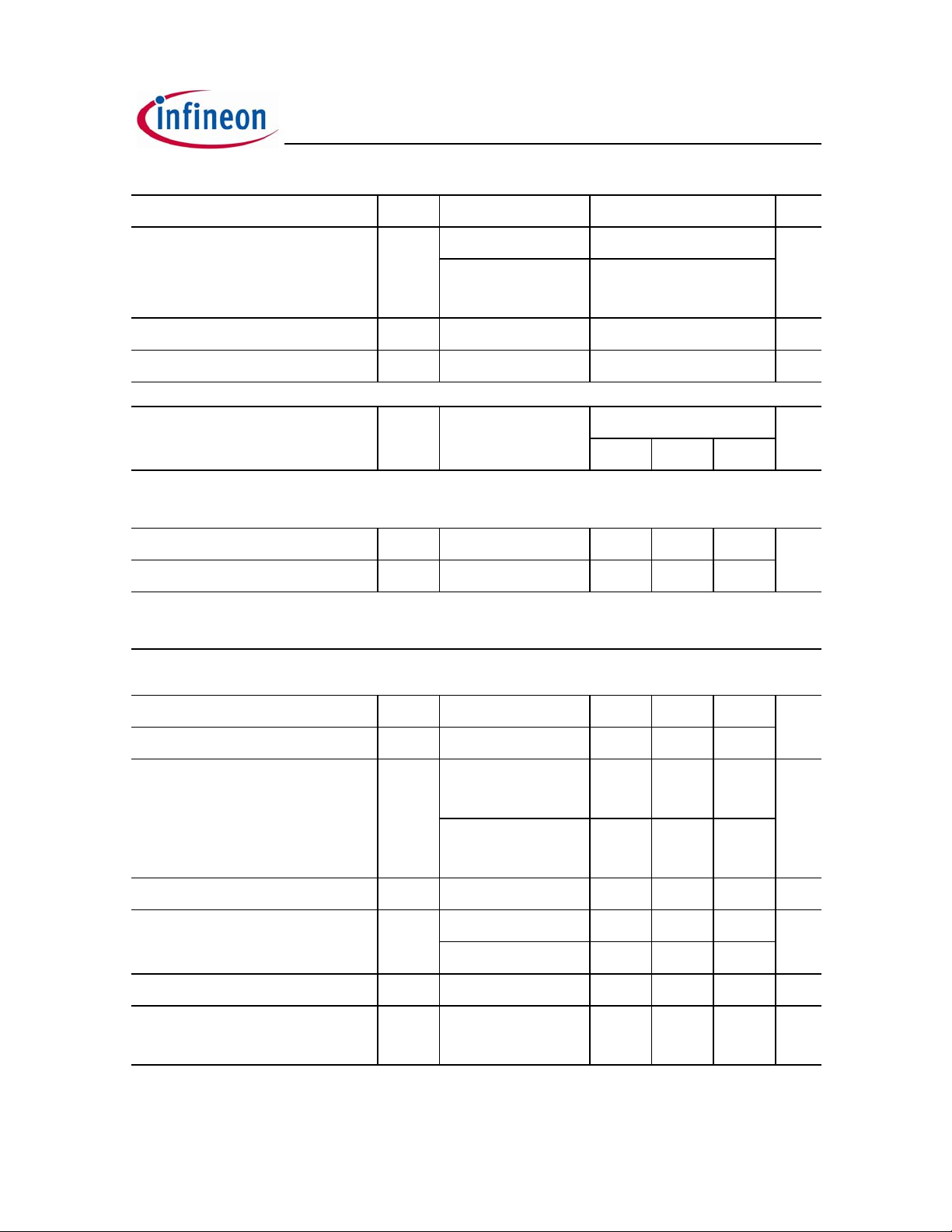

Maximum ratings, at Tj=25 °C, unless otherwise specified

BSC035N04LS G

Parameter Symbol Conditions Unit

stg

TC=25 °C

=25 °C,

T

A

R

=50 K/W

thJA

2)

Power dissipation

Operating and storage temperature

P

tot

, T

T

j

Value

69 W

2.5

-55 ... 150 °C

IEC climatic category; DIN IEC 68-1 55/150/56

Parameter Symbol Conditions Unit

Values

min. typ. max.

Thermal characteristics

Thermal resistance, junction - case

Device on PCB

Electrical characteristics, at T

=25 °C, unless otherwise specified

j

R

thJC

R

thJA

6 cm2 cooling area

2)

- - 1.8 K/W

--50

Static characteristics

Drain-source breakdown voltage

Gate threshold voltage

Zero gate voltage drain current

Gate-source leakage current

Drain-source on-state resistance

Gate resistance

Transconductance

2)

Device on 40 mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm2 (one layer, 70 µm thick) copper area for drain

connection. PCB is vertical in still air.

3)

See figure 3 for more detailed information

4)

See figure 13 for more detailed information

V

(BR)DSSVGS

V

GS(th)

I

DSS

I

GSS

R

DS(on)

R

G

g

fs

=0 V, ID=1 mA

VDS=VGS, ID=36 µA

VDS=40 V, VGS=0 V,

T

=25 °C

j

V

=40 V, VGS=0 V,

DS

T

=125 °C

j

VGS=20 V, VDS=0 V

VGS=4.5 V, ID=50 A

=10 V, ID=50 A

V

GS

|VDS|>2|ID|R

I

=50 A

D

DS(on)max

40 - - V

1.2 - 2

- 0.1 1 µA

- 10 100

- 10 100 nA

- 4.2 5.3

- 2.9 3.5

- 1.5 -

,

60 120 - S

mΩ

Ω

Rev. 1.01 page 2 2008-08-12

BSC035N04LS G

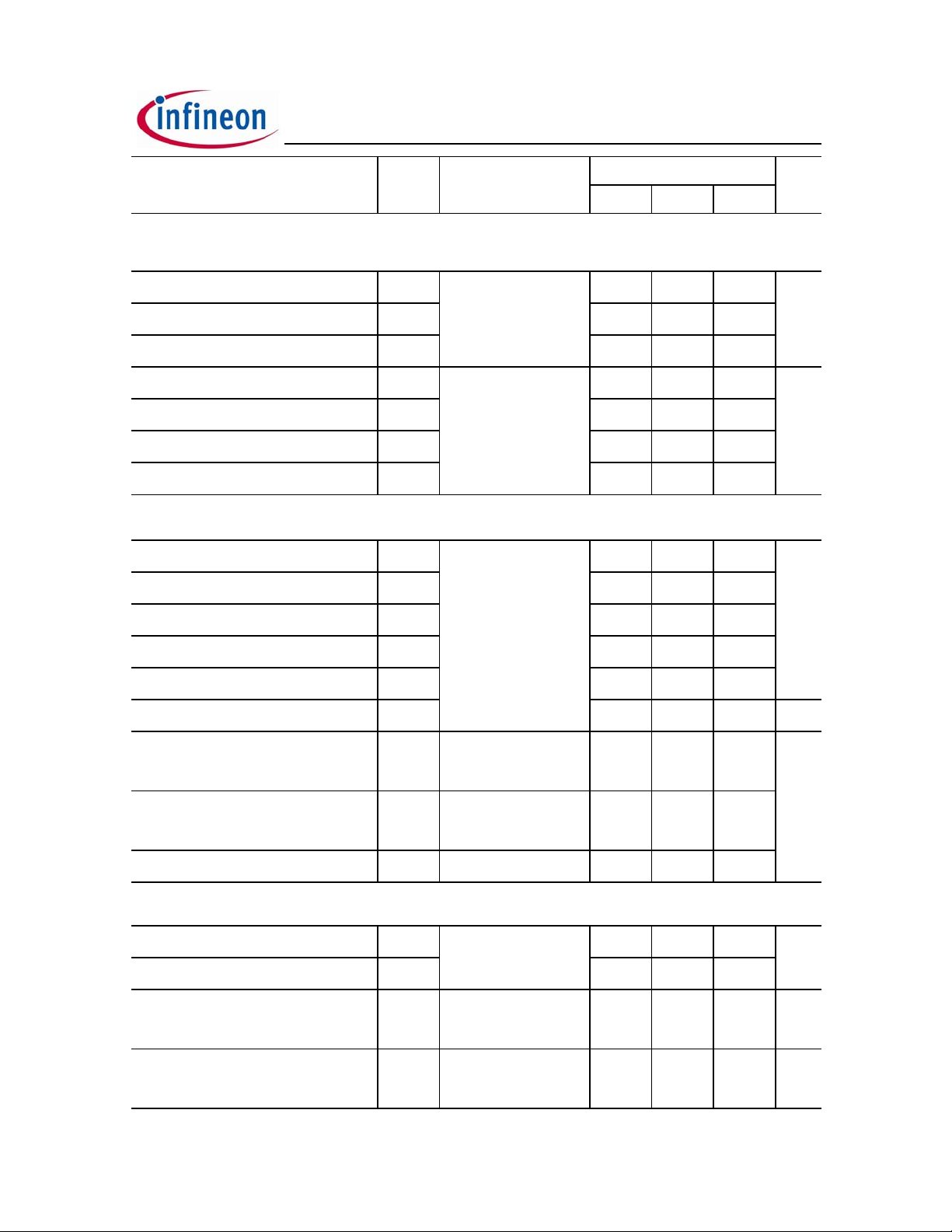

g

Parameter Symbol Conditions Unit

Values

min. typ. max.

Dynamic characteristics

Input capacitance

Output capacitance

Reverse transfer capacitance

Turn-on delay time

Rise time

Turn-off delay time

Fall time

Gate Char

e Characteristics

Gate to source charge

Gate charge at threshold

Gate to drain charge

Switching charge

C

iss

=0 V, VDS=20 V,

V

C

oss

C

rss

t

d(on)

t

r

t

d(off)

t

f

5)

Q

gs

Q

g(th)

Q

gd

Q

sw

GS

f =1 MHz

V

=20 V, VGS=10 V,

DD

=30 A, R

I

D

V

DD

V

GS

G

=20 V, ID=30 A,

=0 to 10 V

=1.6 Ω

- 3800 5100 pF

- 820 1100

-44-

- 7.9 - ns

- 4.6 -

-31-

- 5.0 -

-12-nC

- 6.1 -

- 5.0 -

-11-

Gate charge total

Gate plateau voltage

Gate charge total

Gate charge total, sync. FET

Output charge

Q

V

Q

Q

Q

g

plateau

g

g(sync)

oss

Reverse Diode

Diode continuous forward current

Diode pulse current

Diode forward voltage

Reverse recovery charge

5)

See figure 16 for gate charge parameter definition

I

S

I

S,pulse

V

SD

Q

rr

VDD=20 V, ID=30 A,

V

=0 to 4.5 V

GS

VDS=0.1 V,

V

=0 to 10 V

GS

VDD=20 V, VGS=0 V

TC=25 °C

VGS=0 V, IF=50 A,

T

=25 °C

j

VR=20 V, IF=IS,

di

/dt =400 A/µs

F

-4864

- 3.1 - V

-2331nC

-45-

-31-

- - 58 A

- - 400

- 0.84 1.2 V

-35-nC

Rev. 1.01 page 3 2008-08-12

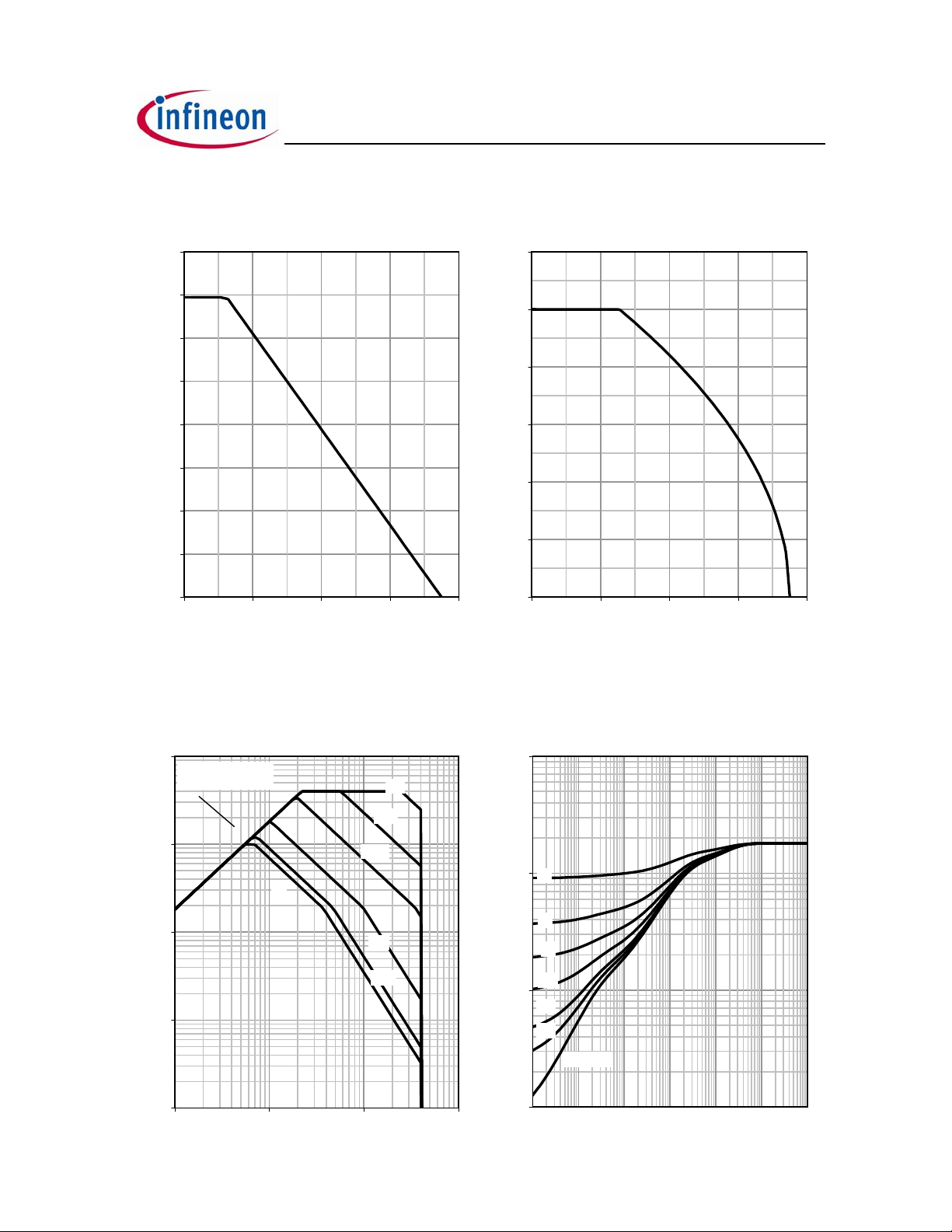

1 Power dissipation 2 Drain current

P

=f(TC) ID=f(TC); VGS≥10 V

tot

BSC035N04LS G

80

120

70

100

60

80

50

[W]

40

tot

P

[A]

D

I

60

30

40

20

20

10

0

0 40 80 120 160

TC [°C]

0

0 40 80 120 160

TC [°C]

3 Safe operating area 4 Max. transient thermal impedance

I

=f(VDS); TC=25 °C; D =0 Z

D

parameter: t

3

10

p

limited by on-state

resistance

1 µs

=f(tp)

thJC

parameter: D =tp/T

10

10 µs

2

10

10

10

10

[A]

D

I

-1

DC

1

0

10

-1

10

0

VDS [V]

100 µs

10

1 ms

10 ms

1

10

1

0.5

0.2

[K/W]

0.1

thJC

Z

0.05

0.1

0.02

0.01

single pulse

0000001

0.01

-1

-2

-3

-4

-5

2

10

-6

10

10

10

tp [s]

10

10

10

0

Rev. 1.01 page 4 2008-08-12

Loading...

Loading...