Page 1

EiceDRIVER™ 1ED38x0Mc12M Enhanced

1ED38x0Mc12M (1ED-X3 Digital)

Reference manual

Single-channel 5.7 kV (rms) isolated gate driver IC with I2C configurability for

DESAT, So-o, UVLO, Miller clamp and optional two-level turn-o

Features

• 650 V, 1200 V, 1700 V, 2300 V IGBTs, SiC, and Si MOSFETs

• 40 V absolute maximum output supply voltage

• ±3 A, ±6 A, and ±9 A typical sinking and sourcing peak output current

• Separate source and sink outputs for hard switching or optional two-level turn-o and with active Miller

clamp

• I2C bus for parameter configuration and status register readout

• Precise, adjustable, and temperature compensated V

• Adjustable IGBT so turn-o aer desaturation detection

• Operation at high ambient temperature up to 125 °C with over-temperature shut down at 160 °C (±10 °C)

• Tight IC-to-IC propagation delay matching (t

• Undervoltage lockout protection with hysteresis for input and output side with active shut-down

• Configurable feedback or fault-o behavior for comparator result of integrated ADC

• High common-mode transient immunity CMTI = 200 kV/µs

• Small space-saving DSO-16 fine-pitch package with large creepage distance (>8 mm)

• Safety certification

- UL 1577 recognized (File E311313) with V

- IEC 60747-17/VDE 0884-11 approval (pending) with V

• Refer to the product datasheet for electrical parameters and certification details

PDD,max

ISO,test

detection (DESAT) with fault output

CEsat

= 30 ns)

= 6840 V (rms) for 1 s, V

= 1767 V (peak, reinforced)

IORM

= 5700 V (rms) for 60 s

ISO

Potential applications

• Industrial motor drives - compact, standard, premium, servo drives

• Solar inverters

• UPS systems

• Welding

• Commercial and agricultural vehicles (CAV)

• Commercial air-conditioning (CAC)

• High-voltage isolated DC-DC converters

• Isolated switch mode power supplies (SMPS)

Product validation

Qualified for industrial applications according to the relevant tests of JEDEC47/20/22.

PG-DSO-16

Reference manual

www.infineon.com/gdisolated 2021-02-15

Please read the Important Notice and Warnings at the end of this document v2.1

Page 2

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

Device information

Device information

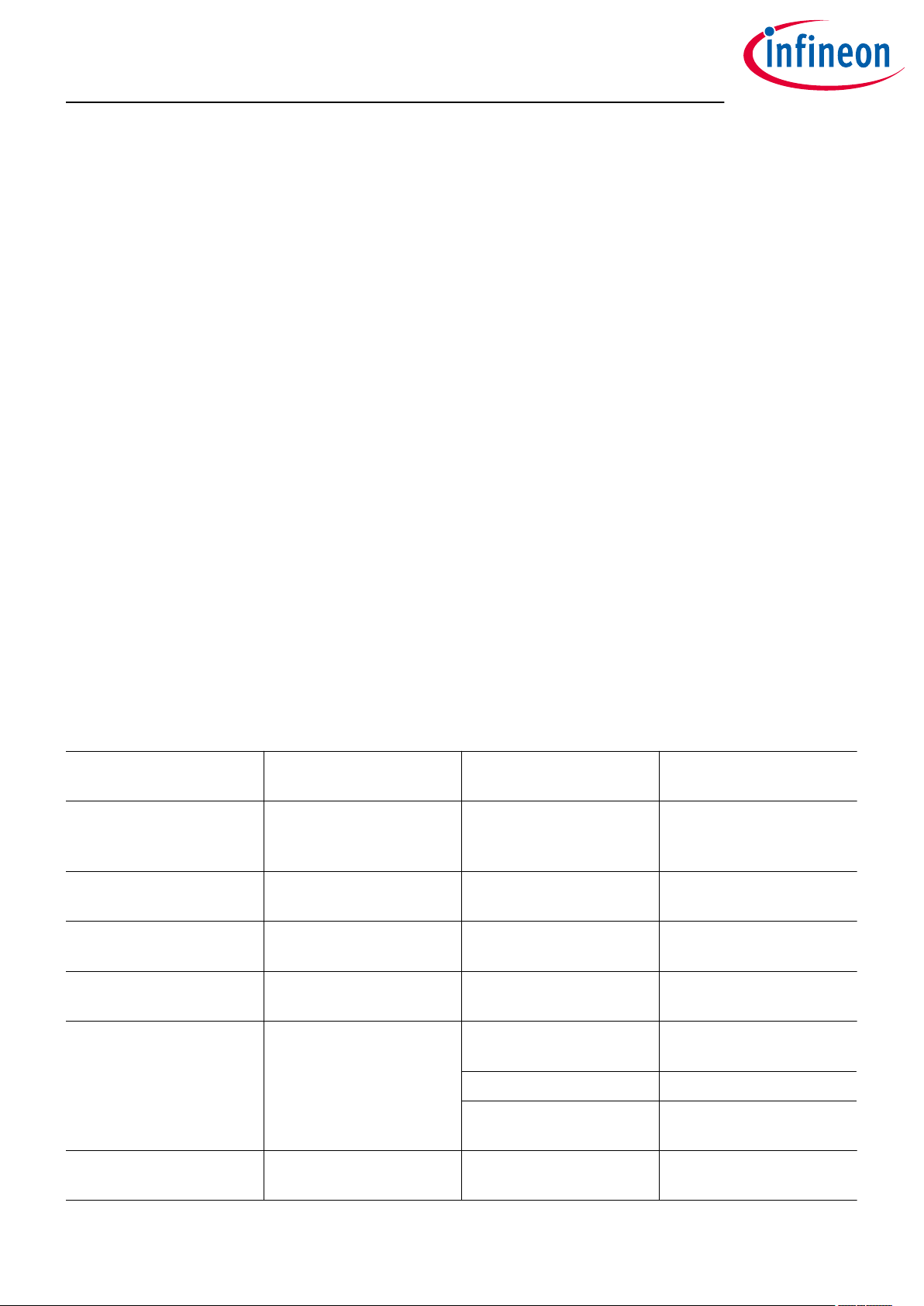

Product type Output current Isolation class Marking OPN

1ED3830MC12M 3 A (typ) reinforced 3830MC12 1ED3830MC12MXUMA1

1ED3860MC12M 6 A (typ) reinforced 3860MC12 1ED3860MC12MXUMA1

1ED3890MC12M 9 A (typ) reinforced 3890MC12 1ED3890MC12MXUMA1

1ED3830MU12M 3 A (typ) UL 1577 3830MU12 1ED3830MU12MXUMA1

1ED3860MU12M 6 A (typ) UL 1577 3860MU12 1ED3860MU12MXUMA1

1ED3890MU12M 9 A (typ) UL 1577 3890MU12 1ED3890MU12MXUMA1

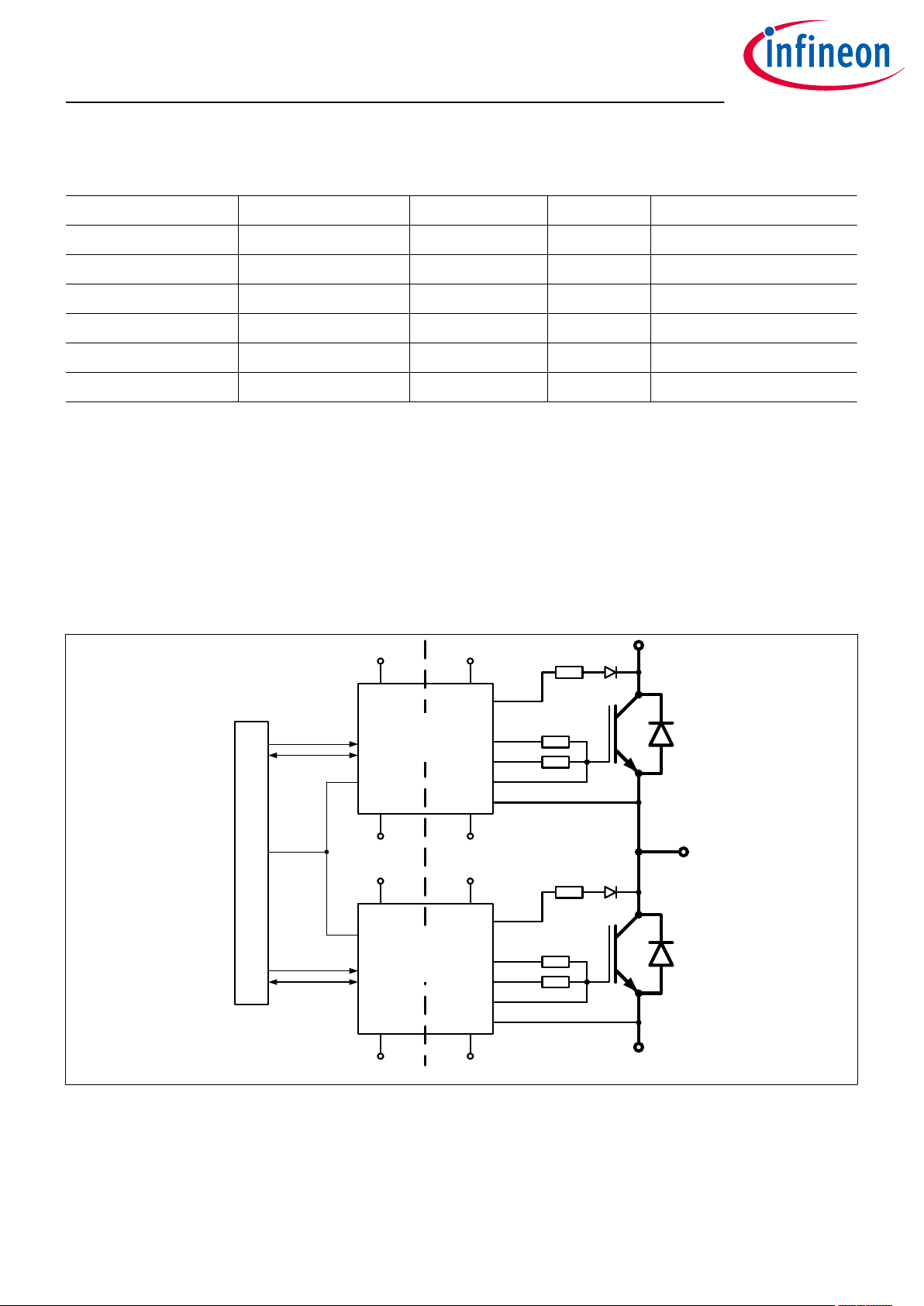

Description

The 1ED38x0Mc12M family (X3 Digital) consists of galvanically isolated single channel gate driver ICs in a small

PG-DSO-16 package with a large creepage and clearance of 8 mm. The gate driver ICs provide a typical peak

output current of 3 A, 6 A, and 9 A.

Adjustable control and protection functions are included to simplify the design of highly reliable systems. All

parameter adjustments are done from the input side via the I2C interface (pin SDA and SCL).

All logic I/O pins are supply voltage dependent 3.3 V or 5 V CMOS compatible and can be directly connected to a

microcontroller.

The data transfer across the galvanic isolation is realized by the integrated coreless transformer technology.

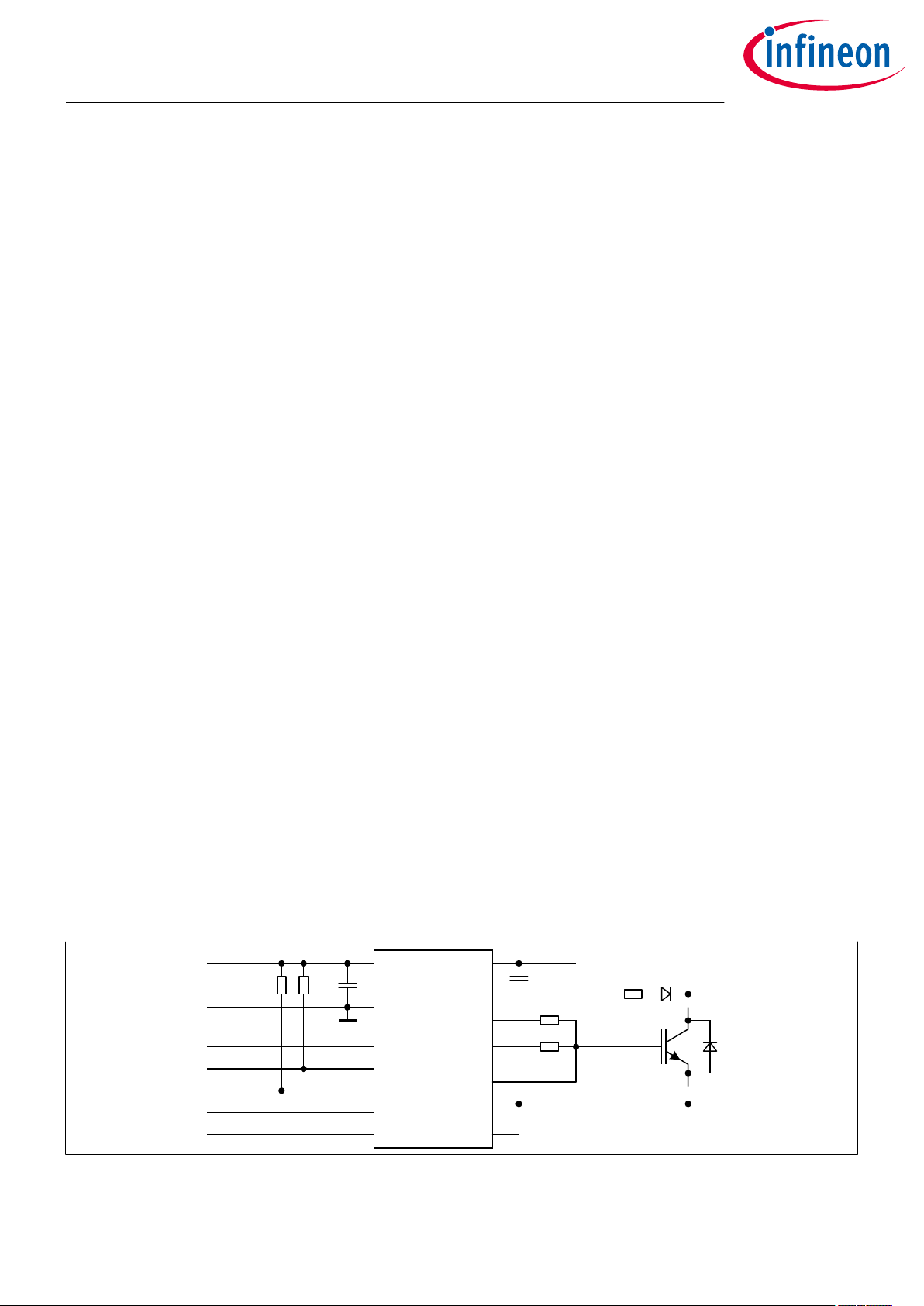

CPU

IN,H

RDYC, FLT_N

I2C

IN,L

RDYC, FLT_N

VCC1

GND1

VCC1

GND1

EiceDRIVER

with digital

interface

EiceDRIVER

with digital

interface

VCC2,H

DESAT,H

TM

ON,H

OFF,H

CLAMP,H

GND2,H

VEE2,H

VCC2,L

DESAT,L

TM

ON,L

OFF,L

CLAMP,L

GND2,L

VEE2,L

Figure 1 Typical application

Reference manual 2 v2.1

2021-02-15

Page 3

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

Table of contents

Table of contents

Table of contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

1 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

2 Related products . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

3 Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

3.1 Start-up and fault clearing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

3.2 Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

3.2.1 Input side undervoltage lockout, VCC1 UVLO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

3.2.2 Output side under-voltage lockout, VCC2 UVLO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

3.2.3 Output side undervoltage lockout, VEE2 UVLO . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12

3.3 Input side logic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

3.3.1 IN non-inverting driver input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

3.3.2 RDYC ready status output, fault-o and fault clear input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.3.2.1 Ready sources and configuration of not ready events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

3.3.2.2 RDYC fault-o input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.3.2.3 RDYC fault clear input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

3.3.3 FLT_N status output and fault-o input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

3.3.3.1 Fault sources and configuration of fault events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15

3.3.3.2 FLT_N fault-o input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.3.4 I2C bus . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

3.3.4.1 I2C bus byte format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17

3.3.4.2 I2C bus read/write operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

3.3.4.3 I2C bus address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

3.4 Operating states . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .21

3.4.1 OFF state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

3.4.2 Address configuration state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.4.3 Parameter configuration state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .22

3.4.4 Parameter transfer state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

3.4.5 Normal operation state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .23

3.4.6 Not ready state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.4.7 Fault state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3.4.8 So-reset, restore and recovery . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.4.8.1 So-reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.4.8.2 Automatic configuration restore from input side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .25

3.4.8.3 Automatic configuration recovery from output side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .26

3.5 Measurement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

3.6 Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .27

3.7 Desaturation protection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .29

3.7.1 DESAT behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

3.7.2 DESAT adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Reference manual 3 v2.1

2021-02-15

Page 4

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

Table of contents

3.7.2.1 DESAT1 adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

3.7.2.2 DESAT2 adjustment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .30

3.8 Gate driver output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .32

3.8.1 Turn-on behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3.8.2 Turn-o and fault turn-o behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .33

3.8.2.1 Hard switching turn-o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.8.2.2 Two-level turn-o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

3.8.2.2.1 Two-level turn-o behavior at normal operating conditions . . . . . . . . . . . . . . . . . . . . . . . . . . 35

3.8.2.2.2 Two-level turn-o behavior at overload condition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

3.8.2.2.3 Two-level turn-o short pulse behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

3.8.2.2.4 Two-level turn-o short pulse behavior with slow turn-on ramp speed . . . . . . . . . . . . . . . . 37

3.8.2.3 So turn-o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

3.8.2.4 Switch-o timeout until forced switch-o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .38

3.8.3 Active shut-down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.8.4 Active Miller clamp . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .39

3.8.4.1 CLAMP output types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

3.9 Short circuit clamping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

4 Register description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

4.1 Configuration registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

4.1.1 I2CADD: I2C address of gate driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .44

4.1.2 I2CGADD: I2C group address of gate driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

4.1.3 I2CCFGOK: I2C address configuration access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

4.1.4 PSUPR: Input pin filter times for IN, RDYC, FLT_N, and I2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4.1.5 FCLR: FLT_N clear behavior by RDYC or timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

4.1.6 RECOVER: Input and output configuration recovery modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

4.1.7 UVTLVL: UVLO threshold level for VCC2 and VEE2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

4.1.8 UVSVCC2C: VCC2 so UVLO enable and threshold level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

4.1.9 UVSVEE2C: VEE2 so UVLO enable and threshold level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .50

4.1.10 ADCCFG: ADC enable and compare polarity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

4.1.11 VEXTCFG: CLAMP pin voltage compare limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .53

4.1.12 OTWCFG: Over-temperature warning level and action . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

4.1.13 D1LVL: DESAT disable and DESAT1 voltage threshold level . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

4.1.14 D1FILT: DESAT1 filter time and type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

4.1.15 D2LVL: DESAT2 enable during TLTO, influence on fault o, and voltage threshold level . . . . . 56

4.1.16 D2FILT: DESAT2 filter time and type . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .58

4.1.17 D2CNTLIM: DESAT2 event counter limit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.1.18 D2CNTDEC: DESAT2 event count down . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .60

4.1.19 DLEBT: DESAT leading edge blanking time . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

4.1.20 F2ODLY: Delay from fault event to gate driver o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

4.1.21 DTECOR: DESAT temperature compensation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

4.1.22 DRVFOFF: Type of fault switch-o . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Reference manual 4 v2.1

2021-02-15

Page 5

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

Table of contents

4.1.23 DRVCFG: Type of normal switch-o and TLTO gate charge range . . . . . . . . . . . . . . . . . . . . . . . . . .65

4.1.24 TLTOC1: TLTO level and ramp A . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

4.1.25 TLTOC2: TLTO duration and ramp B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .67

4.1.26 CSSOFCFG: So turn-o current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .68

4.1.27 CLCFG: CLAMP and pin monitoring filter time and type, CLAMP output types and disable . . . . . 68

4.1.28 SOTOUT: Switch-o timeout time and fault signaling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .70

4.1.29 CFGOK: Register configuration lock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.1.30 CLEARREG: Clear event counter registers for DESAT2, VCC1 UVLO, VCC2 UVLO, event flags,

and so-reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

4.2 Status registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

4.2.1 Sticky bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .73

4.2.2 RDYSTAT: Status of input side, output side, and gate driver IC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

4.2.3 SECUVEVT: Output side UVLO events causing a not ready state (sticky bits) . . . . . . . . . . . . . . . . . 74

4.2.4 GFLTEVT: Indicator of active fault handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

4.2.5 FLTEVT: Fault status and events of input side and output side . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 76

4.2.6 PINSTAT: Status of pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

4.2.7 COMERRST: Status of input to output communication . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

4.2.8 CHIPSTAT: Logic status of gate driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.2.9 EVTSTICK: Event indicator (sticky bits) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

4.2.10 UV1FCNT: Counter of unfiltered VCC1 UVLO events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

4.2.11 UV2FCNT: Counter of unfiltered VCC2 UVLO events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

4.2.12 D2ECNT: Counter of DESAT2 events . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .83

4.2.13 ADCMVDIF: Filtered ADC calculation result of VCC2 to GND2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

4.2.14 ADCMGND2: Filtered ADC result of GND2 to VEE2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4.2.15 ADCMVCC2: Filtered ADC result of VCC2 to VEE2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

4.2.16 ADCMTEMP: Filtered ADC result of gate driver temperature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

4.2.17 ADCMVEXT: Filtered ADC result of CLAMP to VEE2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .85

5 Application notes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

5.1 Reference layout for thermal data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

5.2 Printed circuit board guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .88

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

Disclaimer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Reference manual 5 v2.1

2021-02-15

Page 6

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

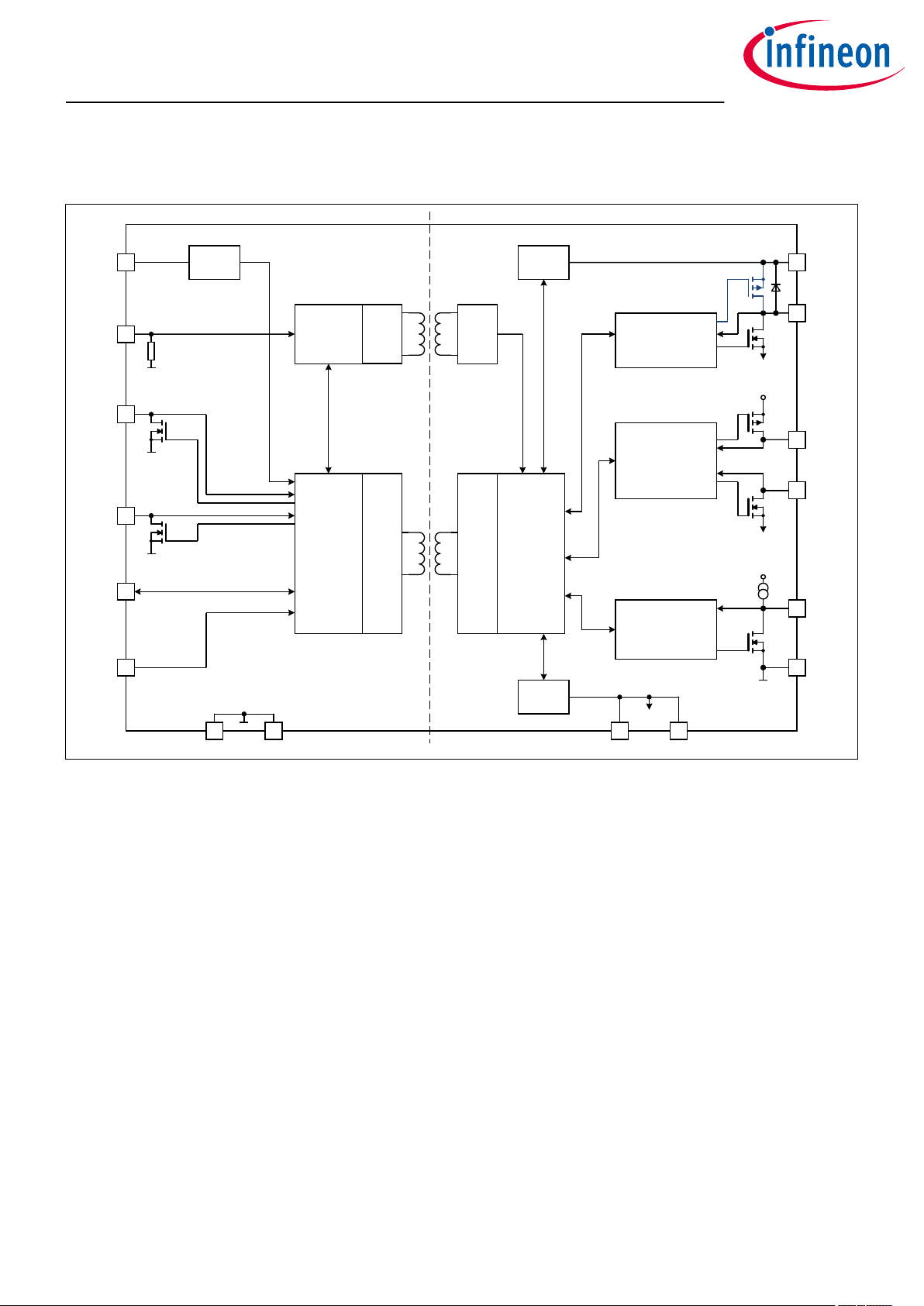

1 Block diagram

1 Block diagram

VCC1

FLT_N

RDYC

SDA

SCL

2

IN

7

UVLO1

PWM logic

1

TX

RX

UVLO2

CLAMP control,

monitoring, and

ADC input

opt.

VEE2

VCC2

14

10

VCC2

CLAMP

6

Output control

1

and monitoring

with hard-

12

ON

switching, TLTOff,

and SoftOff

11

OFF

5

VEE2

1

TRXLOGIC

TRX LOGIC

VCC2

4

DESAT

13

DESAT control

and monitoring

3

2

15

GND2

UVLO3

1

GND1

1

8 9 16

GND1

VEE2

VEE2 VEE2

Figure 2 Block diagram

Reference manual 6 v2.1

2021-02-15

Page 7

EiceDRIVER™ 1ED38x0Mc12M Enhanced

Reference manual

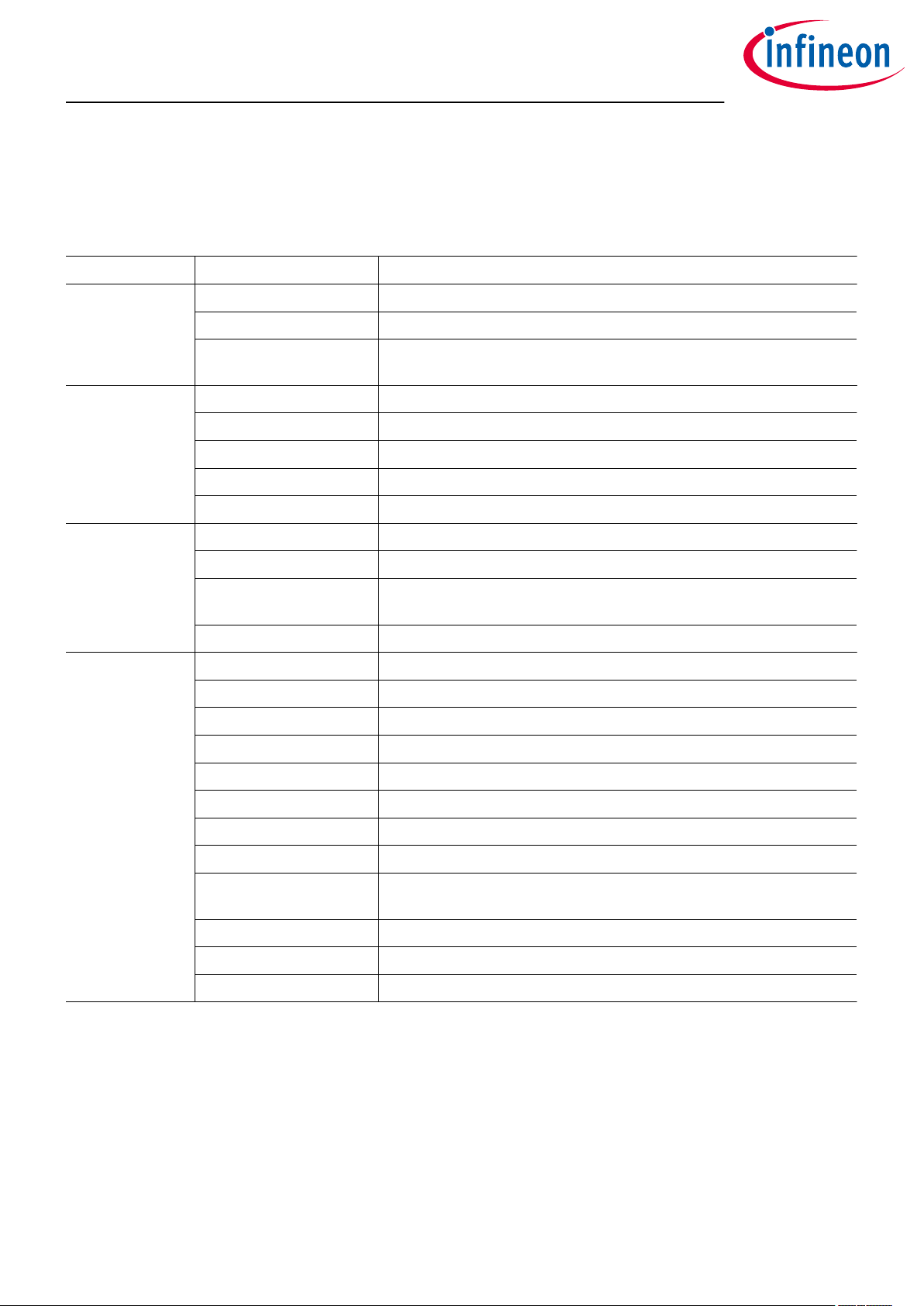

2 Related products

2 Related products

Note: Please consider the gate driver IC power dissipation and insulation requirements for the selected

power switch and operating condition.

Product group Product name Description

TRENCHSTOP

IGBT Discrete

™

IKQ75N120CS6 High Speed 1200 V, 75 A IGBT with anti-parallel diode in TO247-3

IKW15N120BH6 High Speed 1200 V, 15 A IGBT with anti-parallel diode in TO247

IHW40N120R5 Reverse conducting 1200 V, 40 A IH IGBT with integrated diode in

TO247

CoolSiC™ SiC

MOSFET Discrete

CoolSiC™ SiC

MOSFET Module

TRENCHSTOP

™

IGBT Modules

IMBF170R650M1 1700 V, 650 mΩ SiC MOSFET in TO263-7 package

IMW120R045M1 1200 V, 45 mΩ SiC MOSFET in TO247-3 package

IMZ120R350M1H 1200 V, 350 mΩ SiC MOSFET in TO247-4 package

IMZA65R027M1H 650 V, 27 mΩ SiC MOSFET in TO247-4 package

IMW65R107M1H 650 V, 107 mΩ SiC MOSFET in TO247-3 package

FS45MR12W1M1_B11 EasyPACK™ 1B 1200 V / 45 mΩ sixpack module

FF6MR12W2M1_B11 EasyDUAL™ 2B 1200 V, 6 mΩ half-bridge module

F3L11MR12W2M1_B74 EasyPACK™ 2B 1200 V, 11 mΩ 3-Level module in Advanced NPC

(ANPC) topology

F4-23MR12W1M1_B11 EasyPACK™ 1B 1200 V, 23 mΩ fourpack module

F4-200R17N3E4 EconoPACK™ 3 1700 V, 200 A fourpack IGBT module

FS150R17N3E4 EconoPACK™ 3 1700 V, 150 A sixpack IGBT module

FF650R17IE4 PrimePACK™ 3 1700 V, 650 A half-bridge dual IGBT module

FF1000R17IE4 PrimePACK™ 3 1700 V, 1000 A half-bridge dual IGBT module

FF1200R17IP5 PrimePACK™ 3+ 1700 V, 1200 A dual IGBT module

FF1500R17IP5 PrimePACK™ 3+ 1700 V, 1500 A dual IGBT module

FF1500R17IP5R PrimePACK™ 3 1700 V, 1500 A dual IGBT module

FF1800R17IP5 PrimePACK™ 3+ 1700 V, 1800 A dual IGBT module

FP10R12W1T7_B11 EasyPIM™ 1B 1200 V, 10 A three phase input rectifier PIM IGBT

module

FS100R12W2T7_B11 EasyPACK™ 2B 1200 V, 100 A sixpack IGBT module

FP150R12KT4_B11 EconoPIM™ 3 1200V three-phase PIM IGBT module

FS200R12KT4R_B11 EconoPACK™ 3 1200 V, 200 A sixpack IGBT module

Reference manual 7 v2.1

2021-02-15

Page 8

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

3 Functional description

The 1ED38x0Mc12M family (X3 Digital) consists of galvanically isolated single channel gate driver ICs with an

extensive digital adjustable feature parameter set. All adjustments are done from low voltage input side during

start up via I2C bus. The configuration is stored into registers.

To start-up the gate driver IC for normal operation both input and output sides of the gate driver IC need to be

powered.

The 1ED38x0Mc12M family (X3 Digital) is designed to support various supply configurations on the input and

output side. On the output side unipolar and bipolar supply is possible.

The output stage is realized as rail-to-rail. There the gate driver voltage follows the supply voltage without an

additional voltage drop. In addition it provides an easy clamping of the gate voltage during short circuit of an

external IGBT.

The RDYC status output reports correct operation of the gate driver IC like suicient voltage supply. The FLT_N

status output reports failures in the application like desaturation detection.

To ensure safe operation the gate driver IC is equipped with an input and output side under-voltage lockout

circuit. The UVLO levels are optimized for IGBTs and MOSFETs, and are adjustable.

The desaturation detection circuit protects the external IGBT from destruction at a short circuit. The gate driver

IC reacts on a DESAT fault by turning o the IGBT with one of the following configurable turn-o methods:

• two-level turn-o

• adjustable so-o

• hard switch-o

The two-level turn-o (TLTO) is a voltage controlled turn-o function.

The so turn-o function is used to switch-o the external IGBT in overcurrent conditions in a so-controlled

manner to protect the IGBT against collector emitter over-voltages.

An adjustable active Miller clamp function protects the IGBT from parasitic turn-on in fast switching

applications.

The 1ED38x0 family also oers several measurement and monitoring functions. The monitoring functions can

be divided into:

• hardware based functions and

• ADC measurement based functions.

3.1 Start-up and fault clearing

For normal operation both input and output sides of the gate driver IC need to be powered. A low level at the

FLT_N pin always indicates a fault condition. In this case the IC starts internal mechanisms for fault clearing.

Input side start-up

1. Voltage at VCC1 reaches the input UVLO threshold: input side of gate driver IC starts operating

2. FLT_N follows input supply voltage

3. Input side is ready to communicate across I2C bus, awaiting user gate driver parameter configuration

4. Records parameters received across the I2C bus

5. Waits until output side is powered

6. Initiates internal start-up: Transfers configured values to output side

7. Performs internal self-test

The complete start-up time t

Output side start-up

1. Voltage at VCC2 reaches the output UVLO threshold: output side of gate driver IC starts operating

2. Activates OFF gate driver output: connected gate stays discharged

3. Waits until input side is powered

Reference manual 8 v2.1

depends on the duration of the user parameter configuration.

START1

2021-02-15

Page 9

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

4. Initiates internal start-up: Receives configured values from input side

5. Performs internal self-test

The complete start-up time t

The gate driver IC releases RDYC to high to signal a successful start-up and its readiness to operate. The gate

driver IC will follow the status of the IN signal.

Clearing a fault with RDYC to low cycle

1. Set IN to low

2. Set RDYC to low for a duration longer than the fault clear time t

3. Release RDYC to high

a. If the source of the fault is no longer present, FLT_N is released to high

b. If another fault source is active, FLT_N stays low and the cycle needs to be repeated

4. Continue PWM operation

Clearing a fault by self clear timer

depends on the duration of the user parameter configuration.

START2

CLRMIN

1. Set IN to low

2. Self clear timer starts counting

3. Self clear timer reaches self clear time

a. If the source of the fault is no longer present, FLT_N is released to high

b. If another fault source is active, FLT_N stays low and the timer restarts

4. Continue PWM operation

3.2 Supply

The 1ED38x0Mc12M family (X3 Digital) is designed to support various supply configurations. The input side can

be used with a 3.3 V or 5 V supply.

The output side requires either an unipolar supply (VEE2 = GND2) or a bipolar supply.

• Individual supply voltages between VCC2 and GND2 or GND2 and VEE2 shall not exceed 25 V.

• The total supply voltage between VCC2 and VEE2 shall not exceed 35 V.

To ensure safe operation of the gate driver IC, it is equipped with an input and output side undervoltage lockout

circuit.

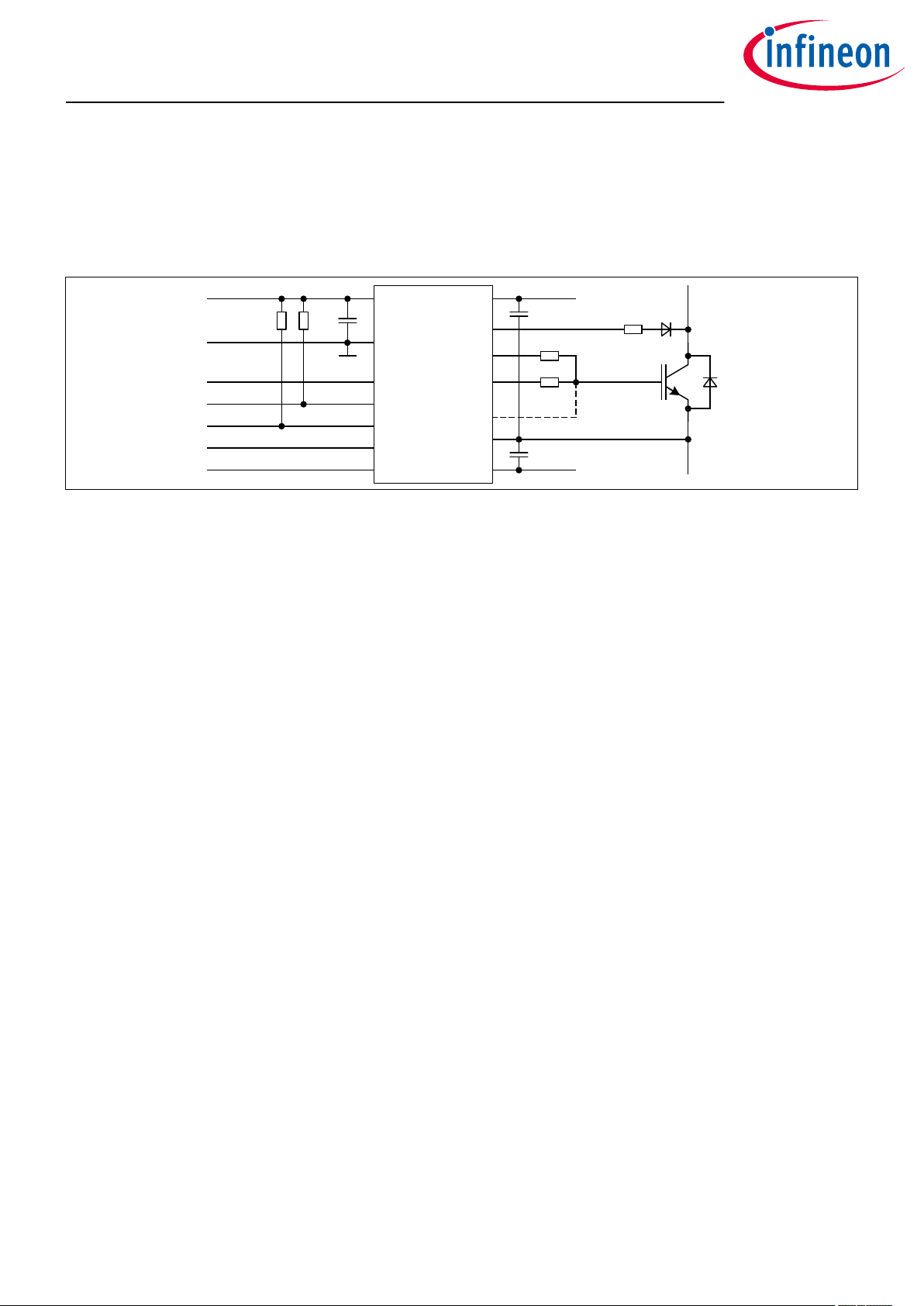

Unipolar supply

In unipolar supply configuration the gate driver IC is typically supplied with a positive voltage of 15 V at VCC2.

GND2 and VEE2 are connected together and this common potential is connected to the IGBT emitter.

+3V3

SGND

IN

RDYC

FLT_N

SCL

SDA

10k

10k

VCC1

GND1

IN

RDYC

FLT_N

SCL

SDA

VCC2

DESAT

ON

OFF

CLAMP

GND2

VEE2

+15V

1µ100n

1k

1R

1R

Figure 3 Application example with unipolar supply

Reference manual 9 v2.1

2021-02-15

Page 10

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

Bipolar supply

For bipolar supply the gate driver IC is typically supplied with a positive voltage of 15 V at VCC2 and a negative

voltage of -8 V or -15 V at VEE2 relative to GND2.

Between VCC2 and VEE2 the maximum potential dierence is 35 V.

+3V3

SGND

IN

RDYC

FLT_N

SCL

SDA

10k

10k

100n

VCC1

GND1

IN

RDYC

FLT_N

SCL

SDA

VCC2

DESAT

ON

OFF

CLAMP

GND2

VEE2

+15V

1µ

1µ

1k

1R

1R

-8V

Figure 4 Application example with bipolar supply

Negative supply prevents a parasitic turn-on due to the additional voltage margin to the gate turn-on threshold.

VEE2 over GND2 supply connection check

The gate driver IC has a built-in connection check for VEE2. A loss of VEE2 connection will be detected and

signaled via RDYC.

3.2.1 Input side undervoltage lockout, VCC1 UVLO

To ensure correct operation of the input side and safe operation of the application the gate driver IC is equipped

with an input supply undervoltage lockout for VCC1.

UVLO behavior during start-up:

1. The voltage at the supply terminal VCC1 reaches the V

2. The gate driver IC waits on the address and parameter configuration and synchronizes it with the output

side

3. The IC releases the RDYC output to high and is ready to operate.

The complete start-up time t

depends on the duration of the user parameter configuration.

START1

UVLO behavior during shut-down:

• If the supply voltage V

of the input side drops below V

VCC1

output will be switched o.

The fault signal FLT_N follows the input supply voltage.

UVLO1H

UVLO1L

threshold

the RDYC signal is switched to low and the

Reference manual 10 v2.1

2021-02-15

Page 11

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

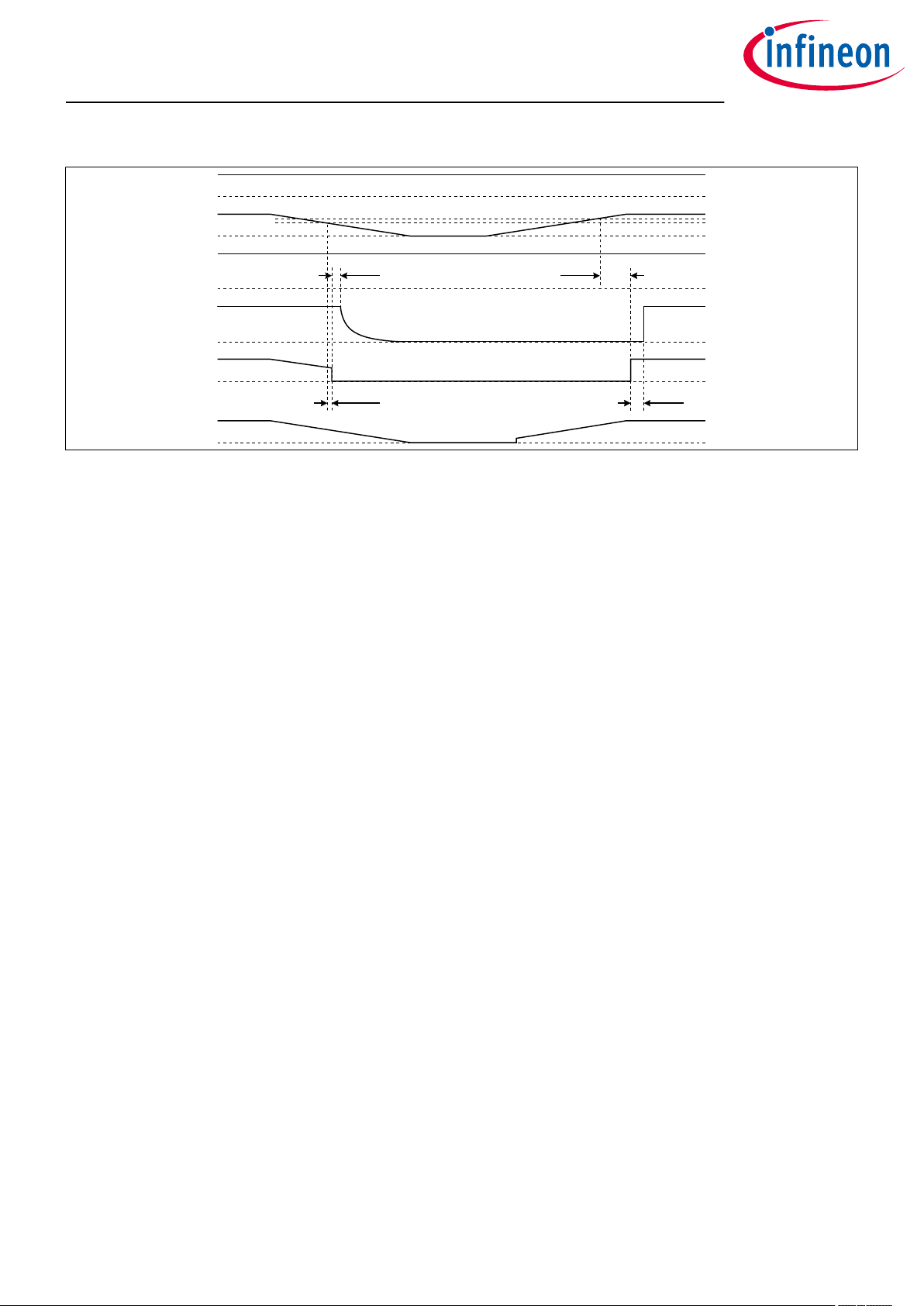

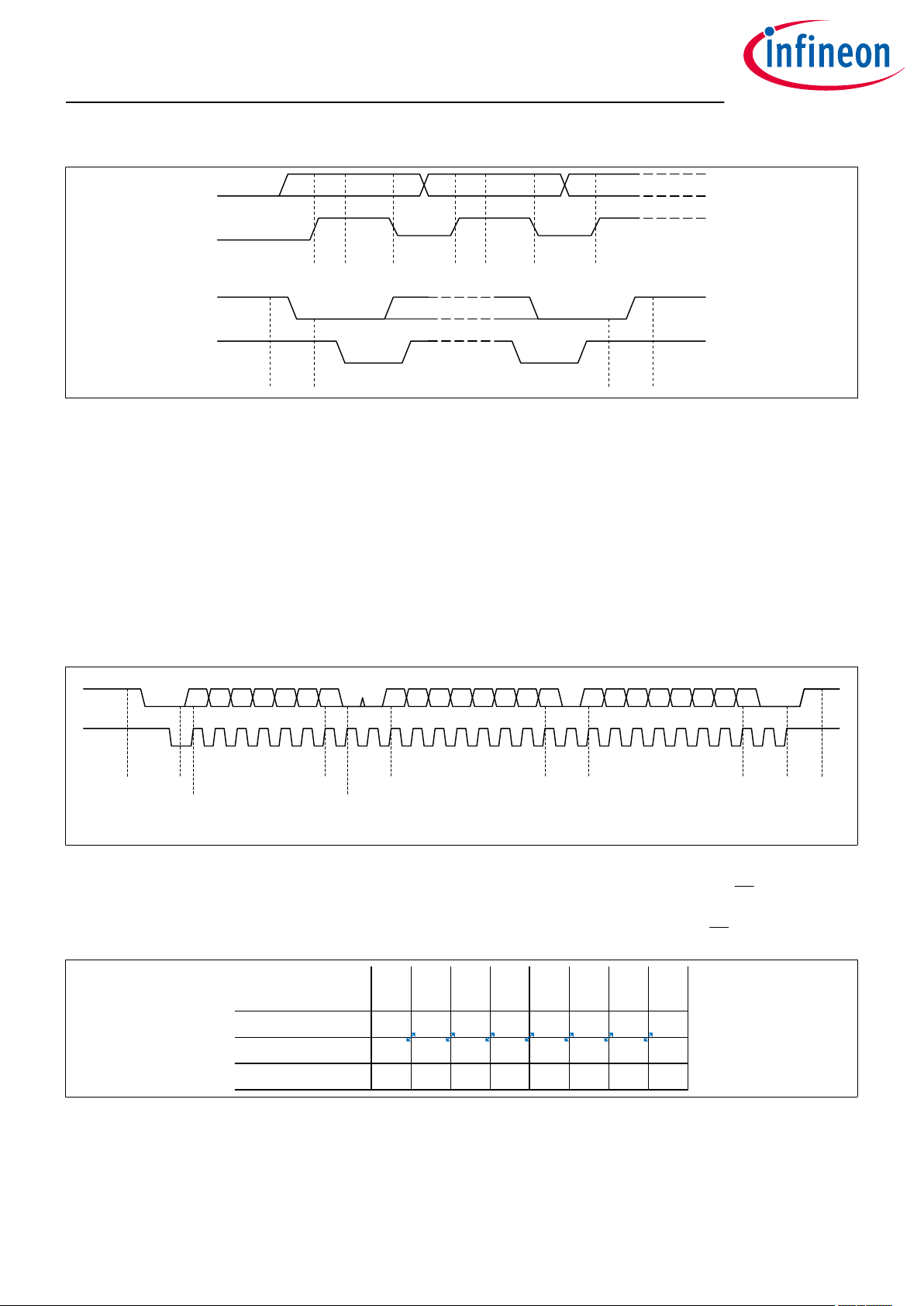

IN

VCC1

V

V

UVLO1H

UVLO1L

VCC2

ON+OFF

RDYC

FLT_N

t

t

UV1LRDYC

PDRDYC

t

START1

t

PDRDYC

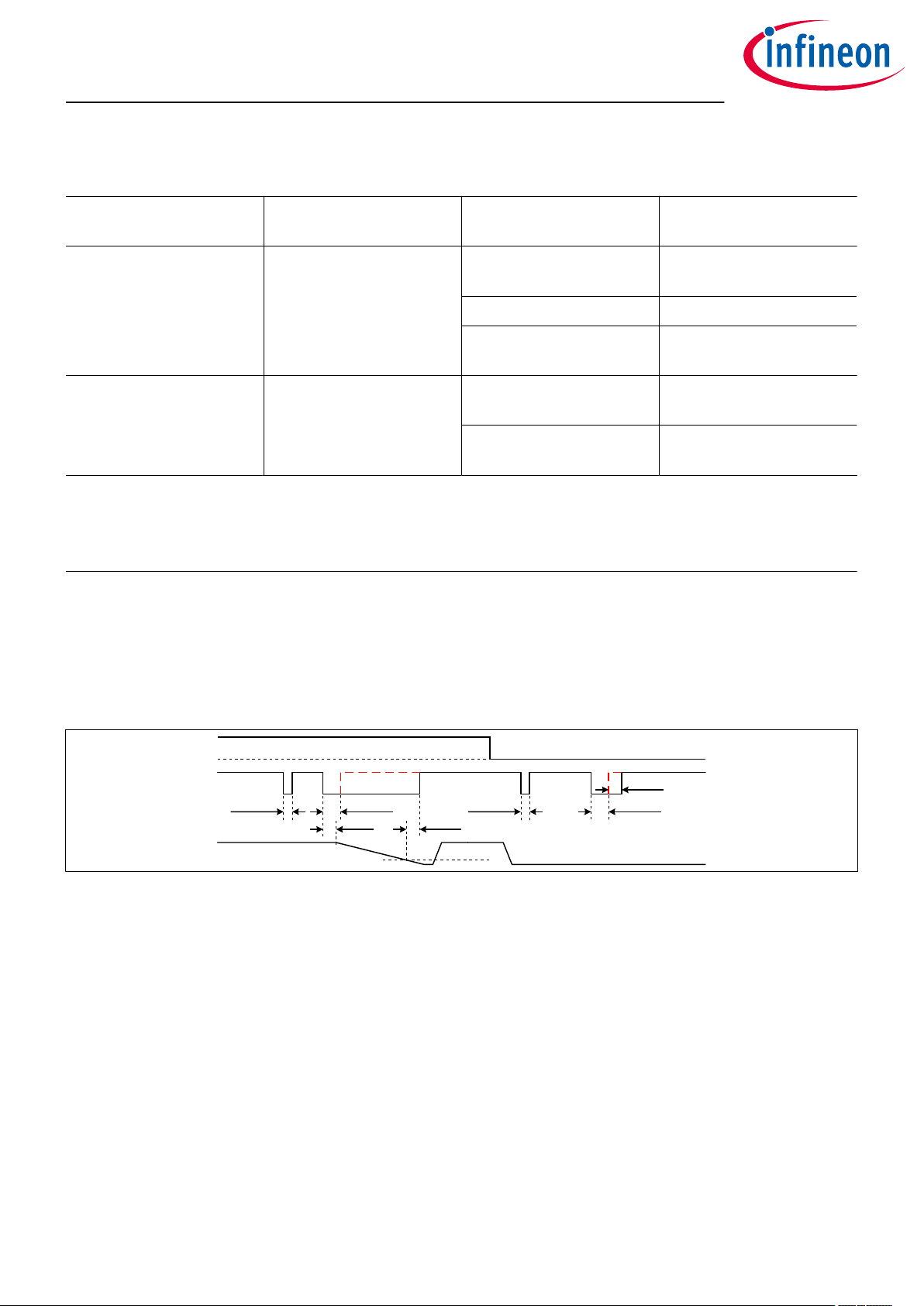

Figure 5 UVLO VCC1 behavior

The gate driver IC supports an alternative UVLO detection in order to provide the means of analyzing the quality

of the VCC1 power supply. The number of unfiltered UVLO comparator output transitions is stored in the register

UV1FCNT.UV1F_CNT and can be read out via I2C bus.

3.2.2 Output side under-voltage lockout, VCC2 UVLO

To ensure correct operation of the output side and safe operation of the IGBT in the application, the gate driver

IC is equipped with an output supply undervoltage lockout for VCC2 versus GND2.

UVLO behavior during start-up:

• If the voltage at the supply terminal VCC2 reaches the V

transfer the input side configuration to the output side before the RDYC output is released to high.

• The rising voltage at the output side triggers a so-reset at the input side unless

- a new set of parameters has been written while the output side was o or

- the RECOVER.RESTORE bit was already set to 1B.

In that cases, the gate driver transfers the configuration to the output side and releases the RDYC output to

high.

The complete start-up time t

depends on the duration of the user parameter configuration.

START2

UVLO behavior during shut-down:

• If the supply voltage V

of the output side drops below V

VCC2

output will be switched o.

threshold the gate driver first needs to

UVLO2H

the RDYC signal is switched to low and the

UVLO2L

Reference manual 11 v2.1

2021-02-15

Page 12

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

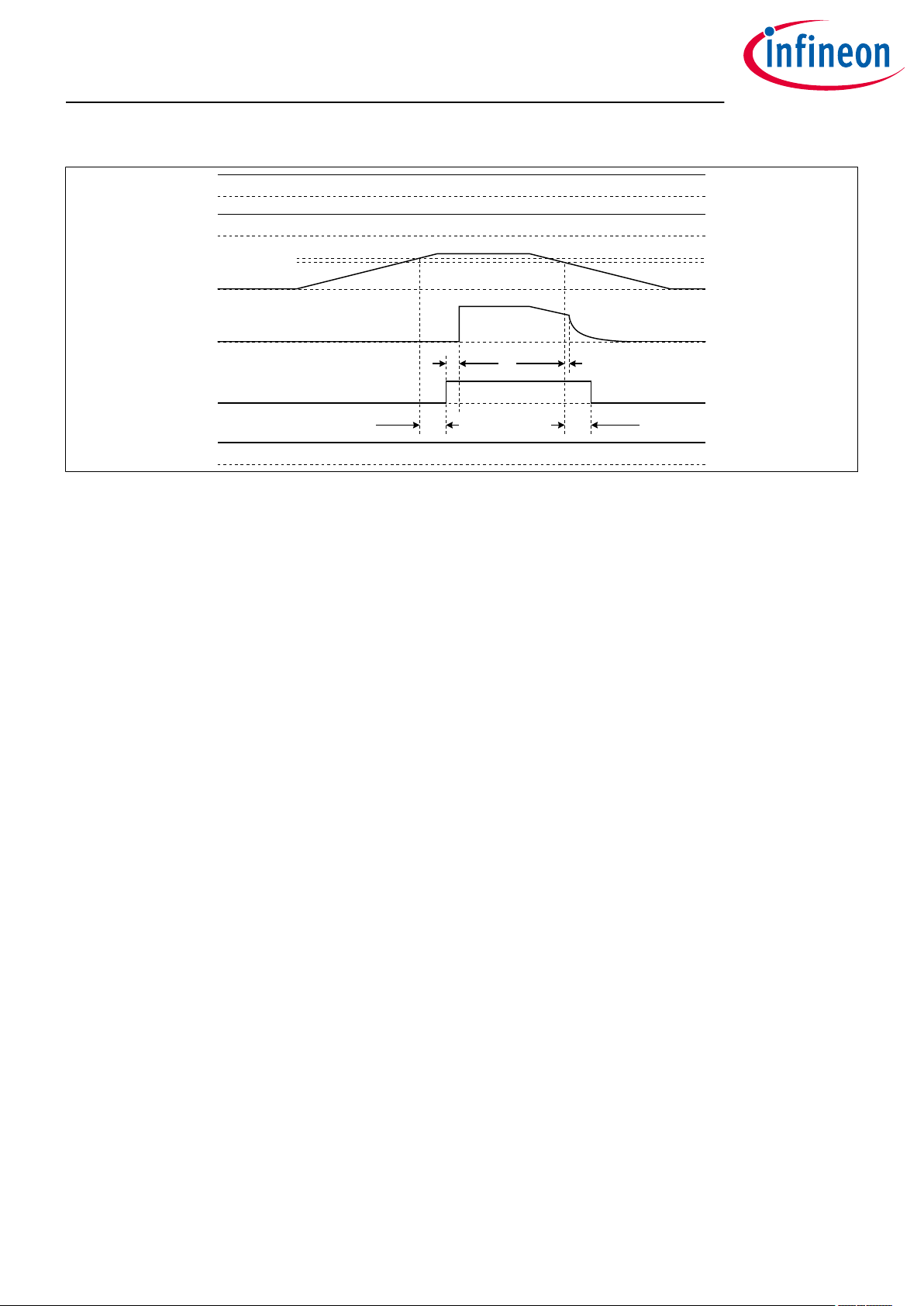

IN

VCC1

V

UVLO2H

V

UVLO2L

VCC2

ON+OFF

RDYC

FLT_N

Figure 6 UVLO VCC2 behavior

t

START2

t

PDRDYC

t

UV2LOFF

t

UV2LRDYC

Any V

event will lead to a fault-o and a RDYC low level. The actual UVLO threshold selection is done in

UVLO2L

register UVTLVL.UVVCC2TL. Going below this threshold will set the UVLO event register bit SECUVEVT.UV_VCC2.

If the supply voltage drops further the output side resets and needs a restart to configure its parameters again.

If the supply voltage recovers immediately without triggering a reset the gate driver IC will also release RDYC to

high.

The gate driver IC is supporting an alternative UVLO detection in order to provide the means of analyzing the

quality of the VCC2 power supply. The number of unfiltered UVLO2 comparator output transitions is stored in

the register UV2FCNT.UV2F_CNT and can be read out via I2C bus.

In addition the 1ED38x0 family oers the feature to measure, monitor and readout the VCC2 voltage through an

integrated ADC to tune the system behavior and adjust according to system/IGBT requirements.

3.2.3 Output side undervoltage lockout, VEE2 UVLO

The 1ED38x0 family oers three adjustable UVLO thresholds for the negative VEE2 supply rail tailored for the

typical operation conditions like -5 V or -8 V or -15 V supply versus GND2. Start up/shut down behavior is

identical to a VCC2 UVLO event assuming the VEE2 UVLO is configured.

VEE2 UVLO is handled in the undervoltage event register SECUVEVT.UV_VEE2, an V

fault o and a RDYC low level. Configure the negative UVLO level in register UVTLVL.UVVEE2TL. A 00B in this

register disables the VEE2 UVLO, e.g. for unipolar supply.

In addition the 1ED38x0 family oers the feature to measure, monitor, and readout the VEE2 voltage through an

integrated ADC to tune the system behavior and adjust according to system/IGBT requirements.

event will lead to a

UVLO3L

Reference manual 12 v2.1

2021-02-15

Page 13

EiceDRIVER™ 1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

3.3 Input side logic

The input threshold levels are always CMOS compliant. The threshold levels are 30% of VCC1 for low level and

70% of VCC1 for high level.

The pins IN and SCL are for input only, and the pins SDA, FLT_N, and RDYC are input/output pins.

3.3.1 IN non-inverting driver input

The input pin has a positive logic. To turn on the associated IGBT apply a logic high signal at the IN pin. The

1ED38x0 family oers the adjustment of the IN input filter time with two trimmed values of typical 103 ns and

183 ns, as described in register PSUPR. The selected filter time directly influences the propagation delay.

3.3.2 RDYC ready status output, fault-o and fault clear input

The RDYC pin is a logic input and open drain output and has three dierent functions:

• RDYC as ready status output of all ready sources

• RDYC as fault-o input

• RDYC as fault clear input

In a typical application the RDYC pins of all gate driver ICs in the inverter are connected together and form a

single wire RDYC signal.

An external pull-up resistor is required to ensure RDYC status output during operation.

3.3.2.1 Ready sources and configuration of not ready events

Not ready events are signaled at RDYC pin by switching the pin voltage to GND1. The gate driver oers

configurable and non configurable not ready events.

Table 1 Ready sources and configuration registers

Ready source Status register bit(s) Configuration register

bit(s)

Internal signal

transmission

VEE2 over GND2 n.a. - gate driver in reset n.a. non-configurable, always

VCC1 supply UVLO n.a. - gate driver in reset n.a. non-configurable, always

VCC2 supply UVLO

VCC2 supply so UVLO

1)

COMERRST .CRC_PRI, .CR

C_SEC, .PCT_COM, .CRC_C

OM, .DCT_COM

SECUVEVT.UV_VCC2 n.a. non-configurable, always

2)

SECUVEVT.UVSVCC2 UVSVCC2C.UVSVCC2E 1B enables so UVLO

n.a. non-configurable, always

UVSVCC2C.UVSVCC2L configures so UVLO level

Configuration

description

enabled

enabled

enabled

enabled

monitoring

ADCCFG.VINT_EN 1B enables ADC for

internal voltages

VEE2 supply UVLO

Reference manual 13 v2.1

1)

SECUVEVT.UV_VEE2 UVTLVL.UVVEE2TL >0D enables UVLO

monitoring

2021-02-15

Page 14

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

Table 1 Ready sources and configuration registers (continued)

Ready source Status register bit(s) Configuration register

bit(s)

VEE2 supply so UVLO

2)

SECUVEVT.UVSVEE2 UVSVEE2C.UVSVEE2E 1B enables so UVLO

Configuration

description

monitoring

UVSVEE2C.UVSVEE2L configures so UVLO level

ADCCFG.VINT_EN 1B enables ADC for

internal voltages

Gate driver configuration CHIPSTAT.CONFIG,

CHIPSTAT.ACTIVE

I2CCFGOK.I2CCFGOK 1B locks user address

configuration

CFGOK.USER_OK 1B locks user

configuration

1) A complete loss of secondary supply voltage followed by a power-up can result in a so-reset on the input

side requiring a parameter re-configuration.

2) If so UVLO is enabled, but ADC measurement is not enabled a so UVLO event will be signaled due to ADC

output value of 00H.

3.3.2.2 RDYC fault-o input

Pulling RDYC to low disables the operation of the gate driver IC. The gate driver IC ignores IN signals as long as

the RDYC pin stays low and the IC uses its fault-o function to switch-o the IGBT.

The defined minimum adjustable pulse width (PSUPR.IN_SUPR) makes the IC robust against glitches at RDYC.

The gate driver ignores pulses with a shorter duration.

IN

RDYC

<t

RDYCMIN

ON+OFF

RDYC ext.

>t

RDYCMIN

t

PDRDYC

t

SSIO

VEE2 + 2V

<t

RDYCMIN

>t

t

SSIO

RDYCMIN

Figure 7 RDYC short pulse behavior of external manipulation of the RDYC pin

Aer

an external RDYC low signal the IC is actively pulling RDYC to low until the voltage at ON pin falls below the

VEE2+2 V threshold.

The RDYC fault-o input is active low.

3.3.2.3 RDYC fault clear input

To use the RDYC as fault clear input, the register bit FCLR.FCLR_CFG needs to be 0B. Setting RDYC to low for

longer than the fault clear time t

Additionally the following conditions have to be met as well:

• PWM IN pin level needs to be low,

• voltage at ON pin has dropped below the VEE2+2 V threshold, and

• triggering fault condition is no longer present.

The typical fault clear time t

CLRMIN

will reset the stored fault signal at pin FLT_N with the rising edge of RDYC.

CLRMIN

is 1.0 µs.

Reference manual 14 v2.1

2021-02-15

Page 15

EiceDRIVER™ 1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

IN

FLT event

FLT_N

t

DESATFLT

t

DESATFLT

SSIO

>t

CLRMIN

VEE2 + 2V

>t

CLRMIN

t

SSIO

ON+OFF

t

RDYC

Figure 8 RDYC fault clear timing

V

RDYC

FLT_N

IH

Figure 9 RDYC fault clear rising edge to FLT_N

3.3.3 FLT_N status output and fault-o input

The FLT_N pin is a logic input and open drain output and has two dierent functions:

• FLT_N as fault-status output for fault sources

• FLT_N as fault-o input

In a typical application the FLT_N pins of all gate driver ICs in the inverter are connected together and form a

single wire FLT_N signal.

An external pull-up-resistor is required to ensure FLT_N status output during operation.

3.3.3.1 Fault sources and configuration of fault events

Fault events are signaled at FLT_N pin by switching the pin voltage level to GND1. The gate driver oers

configurable and non-configurable fault events.

Table 2 Fault sources and configuration registers

Fault source Status register bit(s) Configuration register

bit

Over temperature

FLTEVT .OTP_EVT n.a. non-configurable, always

protection

Over temperature warning FLTEVT.OTW_EVT OTWCFG.OTW_ACFG 0B disables OTW event

Desaturation detection of

FLTEVT .D1_EVT, .D2_EVT D1LVL.D_DIS 1B disables DESAT

IGBT

Secondary desaturation

FLTEVT.D2_EVT D2LVL.D2_ACFG 0B disables DESAT2 event

detection of IGBT

Switch-o timeout FLTEVT.SOTO_EVT SOTOUT.SOTOUT_F 0B disables timeout event

CLAMP pin voltage limit FLTEVT.VEXTFLT ADCCFG.VEXTL_EN 0B disables limit event

Reference manual 15 v2.1

Configuration

description

enabled

completely, no event

monitoring

2021-02-15

Page 16

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

The status register bits still highlight a possible fault event even if their configuration register disables the

triggering of FLT_N. The desaturation detection configuration with register bit D1LVL.D_DIS however disables

this part of the integrated circuit and therefore disables also both DESAT events.

3.3.3.2 FLT_N fault-o input

Pulling FLT_N to low disables the operation of the gate driver IC. The gate driver IC ignores IN signals as long as

the FLT_N pin stays low and the IC uses its fault-o function to switch-o the IGBT.

The defined minimum adjustable pulse width (PSUPR.IN_SUPR) makes the gate driver IC robust against glitches

at FLT_N.

Aer a low at the FLT_N pin either internally or externally applied, the fault event is latched until cleared.

The FLT_N fault-o input is active low.

IN

FLT_N

<t

FLT_NMIN

ON+OFF

FLT_N ext. FLT_N ext.

>t

FLT_NMIN

t

PDFLT_N

t

SSIO

+t

FSCLR

<t

FLT_NMIN

VEE2 + 2V

t

SSIO

>t

FLT_NMIN

+t

FSCLR

Figure 10 FLT_N short pulse behavior of external manipulation of the FLT_N pin with self clear

IN

FLT_N

<t

FLT_NMIN

FLT_N ext. FLT_N ext.

>t

FLT_NMIN

t

PDFLT_N

<t

FLT_NMIN

>t

FLT_NMIN

ON+OFF

RDYC

>t

CLRMIN

>t

CLRMIN

Figure 11 FLT_N short pulse behavior of external manipulation of the FLT_N pin cleared by RDYC

3.3.4 I2C bus

The 1ED38x0 family is equipped with a standard I2C bus interface to configure various parameters of the gate

driver IC and read out measurement and monitoring registers.

Key I2C features include:

• I2C bus slave device implementing all mandatory slave bus protocols for the specification UM10204 rev. 6

• 7 bit device addresses for individual and group addressing

• Initial I2C device address: 1AH (MSB aligned, bits 7:1)

• Signal voltage level compatible to 3.3 V and 5 V

• Supported bus speeds at gate driver data pin (SDA) and clock pin (SCL):

- standard-mode (Sm), with bit rates up to 100 kbit/s

- fast-mode (Fm), with bit rates up to 400 kbit/s

- fast-mode plus (FM+), with bit rates up to 1 Mbit/s

Reference manual 16 v2.1

2021-02-15

Page 17

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

SDA

SCL

SCL

filter

data valid data change data valid

time

SCL

filter

time

data change

SDA

SCL

S - start P - stop

Figure 12 Start, stop and data conditions

All I2C bus commands start with a start condition and stops with a stop condition. The data at the SDA pin gets

valid if SCL level is above the CMOS level threshold and the filter time has elapsed.

3.3.4.1 I2C bus byte format

All register addresses and data bytes of the 1ED38x0 family are 8 bit values. The serial data line (SDA) transmits

and receives with the most significant bit (MSB) first.

There are two register areas implemented:

• register addresses from 00H to 25H are used for configuration and

• register addresses from 26H to 37H are used as status registers.

MSB MSB MSBLSB LSB LSB

Wr

SDA

A6 A5 A4 A3 A2 A1 A0 R7 R6 R5 R4 R3 R2 R1 R0 Ack D7 D6 D5 D4 D3 D2 D1 D0 Ack

Ack

SCL

Start

Ack = Acknowledge

Wr = Write

Ax = Adress Bit

Rx = Register Bit

Dx = Data Bit

Slave address (7 bit)

Addressing byte (8 bit)

Register address (8 bit)

Data (8 bit) Stop

Figure 13 Write byte format (starting at register address)

The addressing byte is transmitted MSB first and includes the 7 bit I2C address followed by the Wr/Rd bit at

LSB position. Throughout this documentation, the hexadecimal device addresses are always written in this 8 bit

format. In the configuration registers the 7 bit I2C addresses are aligned to LSB without the

Bit

Address register byte

SDA addressing byte

Default address: 1A

MSB

7 6 5 4 3 2 1

res A6 A5 A4 A3 A2 A1 A0

A6 A5 A4 A3 A2 A1 A0 W/R

0 0 0 1 1 0 1 0

H

LSB

Wr/Rd bit.

0

Figure 14 I2C address alignment in register and during transmission

All registers have a data size of 8 bit, but not all bits are implemented in all registers. Not implemented data bits

read as 0B unless specified otherwise.

Reference manual 17 v2.1

2021-02-15

Page 18

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

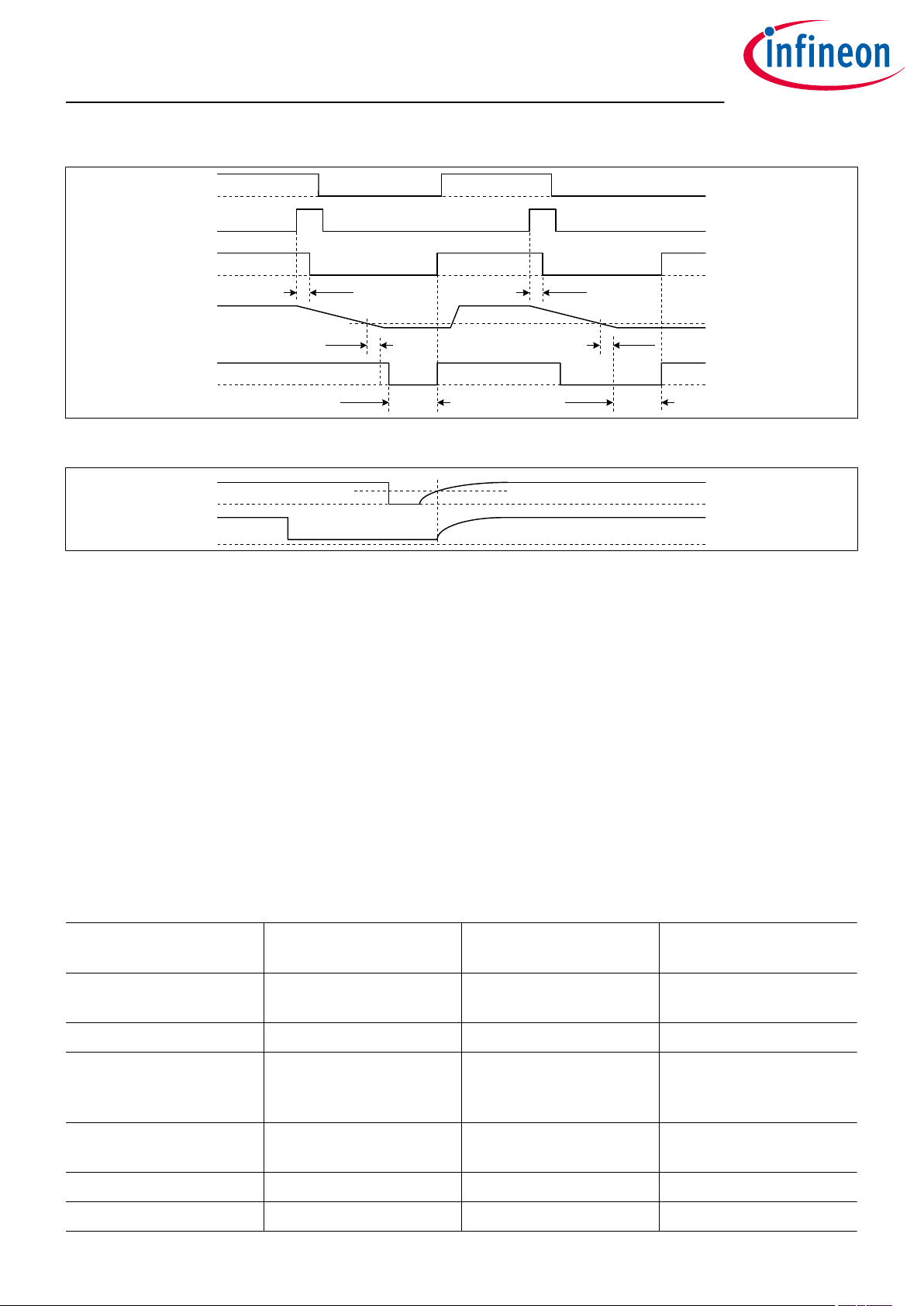

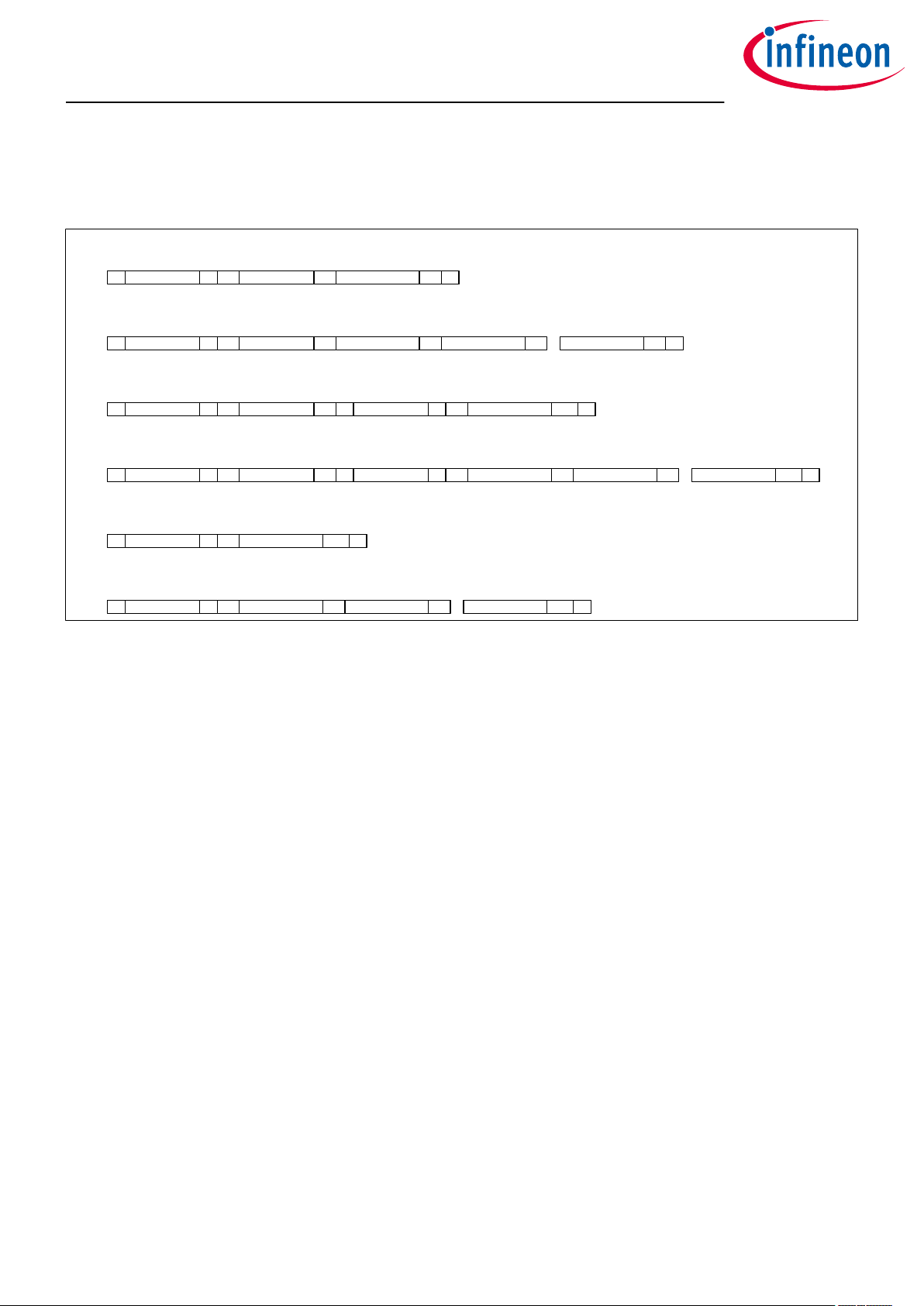

3.3.4.2 I2C bus read/write operation

Read and write operations are controlled by the I2C master (microcontroller).

Write byte (starting at specific register address)

1 7 1 1 8 1 8 1 1

S Slave address Wr Ack Register address Ack Data byte Ack P

Write n-bytes (starting at specific register address)

1 7 1 1 8 1 8 1

S Slave address Wr Ack Register address Ack Data byte (add.) Ack

Read byte (starting at specific register address)

1 7 1 1 8 1 7 1 11 8 1 1

S Slave address Wr Ack Register address Ack Data byte Nack PS Slave address AckRd

Read n-bytes (starting at specific register address)

1 7 1 1 8 1 7 1 11 8 1

S Slave address Wr Ack Register address Ack Data byte (add.) NackS Slave address AckRd

Data byte (add.+1)8Ack1Data byte (add.+n)8Ack

...

1

Ack

Data byte (add.+1)8Ack1Data byte (add.+n)

1

1

P

...

8

1

P

Read byte (starting at first status register)

1 7 1 1 8 1 1

S Slave address Rd Ack Data byte Nack P

Read n-bytes (starting at first status register)

1 7 1 1 8 1

S Slave address Rd Ack Data byte (add) Nack

1

Ack

Data byte (add+1)8Ack1Data byte (add+n)

...

8

1

P

Figure 15 Read/write operation

Write byte and write n-bytes to register

1. I2C master (microcontroller) to initiate write with start bit followed by 7 bit slave address (gate driver)

and write bit

2. Target gate driver answers with acknowledge (ACK)

3. Master to send 8 bit target register address

4. Target gate driver answers with ACK and sets internal register address

5. Master to send the data byte for current register

6. Target gate driver answers with ACK if target register is writable and increases internal register address by

1

H

7. Steps 5 and 6 can be repeated to send multiple bytes to consecutive registers

8. Master finalizes data write by sending a stop bit

Read byte and read n-bytes from specific register

1. I2C master (microcontroller) to initiate write with start bit followed by 7 bit slave address (gate driver)

and write bit

2. Target gate driver answers with acknowledge (ACK)

3. Master to send 8 bit target register address

4. Target gate driver answers with ACK and sets internal register address

5. Master begins new read session with start bit followed by 7 bit slave address (gate driver) and read bit

6. Target gate driver answers with acknowledge (ACK)

7. Target gate driver sends 8 bit data byte from current register and increases internal register address by 1

8. Master is responsible for ACK/NACK to control read of consecutive registers

a. When responding with ACK, the master is waiting for another data byte and the sequence

continues at number 7

b. When responding with NACK, the master terminates the read session

9. Master finalized data read by sending a stop bit

Reference manual 18 v2.1

2021-02-15

H

Page 19

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

Read byte and read n-bytes from status register

1. I2C master (microcontroller) to initiate read with start bit followed by 7 bit slave address (gate driver) and

read bit

2. Without a preceding register write the gate driver sets the internal register address to the first status

register

3. Target gate driver answers with acknowledge (ACK)

4. Target gate driver sends 8 bit data byte from current register and increases internal register address by 1

5. Master is responsible for ACK/NACK to control read of consecutive registers

a. When responding with ACK, the master is waiting for another data byte and the sequence

continues at number 4

b. When responding with NACK, the master terminates the read session

6. Master finalized data read by sending a stop bit

3.3.4.3 I2C bus address

H

The gate driver IC has two configurable 7 bit addresses:

• device address I2CADD, e.g. for dedicated read out or configuration

• group address I2CGADD to configure all gate driver ICs in the same group within one write cycle

Both addresses have to be set at start up. Configured addresses have to dier from the initial LSB aligned I2C

device address 0DH.

Address configuration aer power up

The gate driver IC is configured to start up with the initial I2C device address. To set the device addresses the

input side has to be powered up and VCC1 is stable above the turn-on undervoltage lockout level. At this point,

the gate driver IC is still in OFF state.

Address configuration steps:

1. Set RDYC to low to deactivate the gate driver IC

2. Set IN to high to select the gate driver IC (chip select, IC enters address configuration state)

3. Send an I2C write command with 4 data bytes to the initial MSB aligned I2C device address 1A

H

a. Data byte 1: Target device register address 00H (RegisterI2CADD)

b. Data bytes 2, 3: 7 bit device address and 7 bit group address aligned from bit 6 to bit 0

c. Data byte 4: value for I2CCFGOK = 01H , to accept and lock the address registers

4. All data bytes will be acknowledged by the gate driver IC to indicate successful transmission and address

acceptance, the gate driver IC enters parameter configuration state

5. Release IN and RDYC, the gate driver IC is now addressable using the addresses transferred

Address configuration during gate driver operation

To re-configure the I2C addresses while the gate driver IC is already in normal operation mode it needs to be

switched to the address configuration state by executing the following steps:

1. Set RDYC to low, entering not ready state

2. Send an I2C write command with 2 data bytes to the current device address

a. Data byte 1: Target device register address 1CH (Register CFGOK)

b. Data byte 2: Value 00H, to enter parameter configuration state

3. Send again an I2C write command with 2 data bytes to the current device address

a. Data byte 1: Target device register address 02H (Register I2CCFGOK)

b. Data byte 2: Value 00H, to enter address configuration state and unlock address registers

4. Follow the steps 2 to 5 of the address configuration aer power up to complete the address re-

configuration

Reference manual 19 v2.1

2021-02-15

Page 20

EiceDRIVER™ 1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

Address configuration notes

Attention: The gate driver IC does not acknowledge (NACK) a write of 01H to I2CCFGOK if the address

registers contain an invalid address.

Note: Reserved I2C bus addresses are not allowed but will be neither checked nor will the gate driver IC

send a NACK (not acknowledge) in response to such an address.

Reference manual 20 v2.1

2021-02-15

Page 21

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

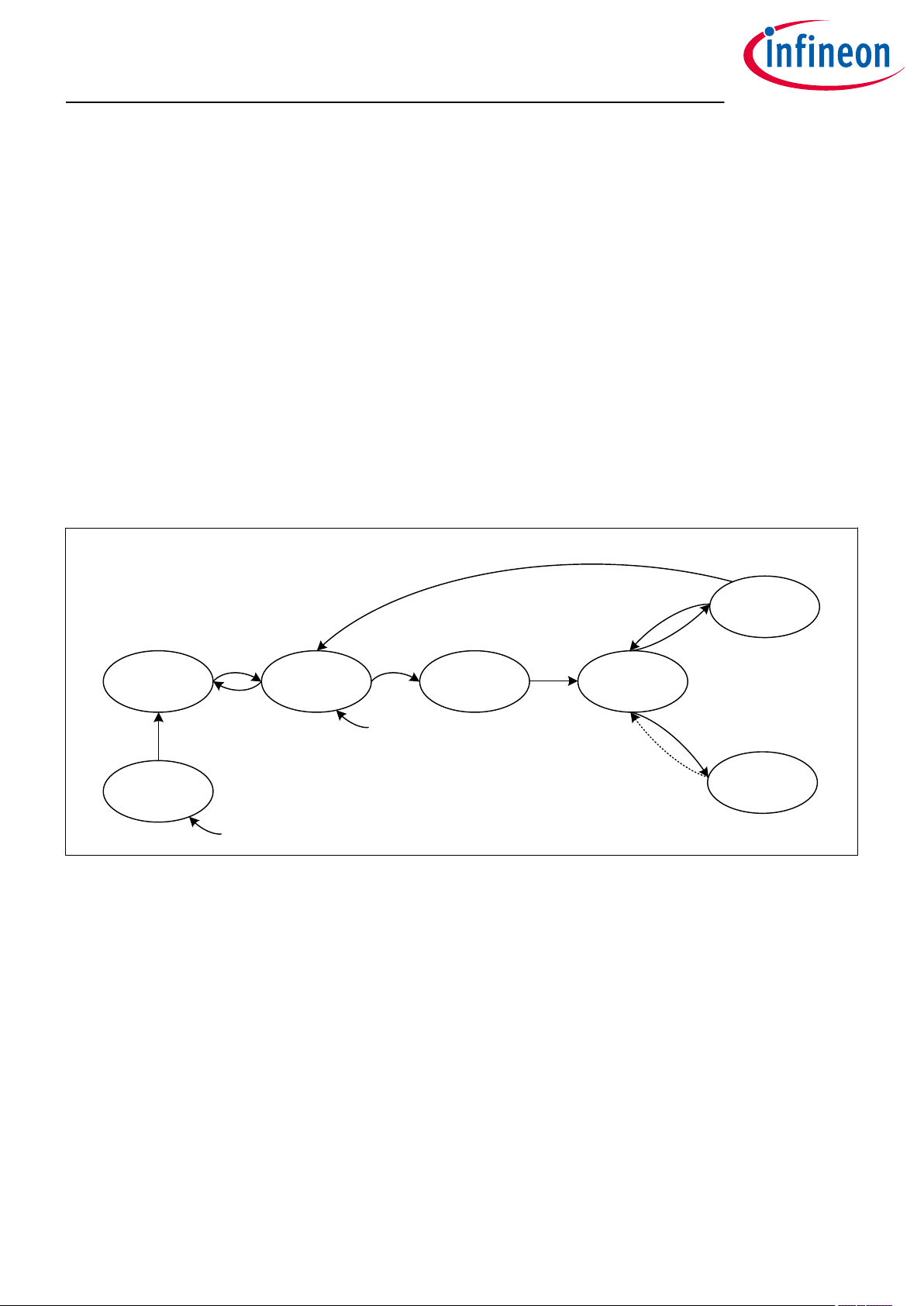

3.4 Operating states

The 1ED38x0 family of gate driver ICs can take the following states:

• OFF state, device not powered

• Address configuration state, the I2C addresses can be set, gate driver IC is not active

• Parameter configuration state, the gate driver parameters can be set and changed, gate driver IC is not

active

• Parameter transfer state, the gate driver IC is transferring the parameters from input side to output side,

gate driver IC is not active

• Normal operation, gate driver IC is active, ON and OFF outputs are following the IN signal, registers are read

only

• Not ready state, gate driver IC is switched o according to fault o settings, status signaled by a low at RDYC

pin

• Fault state, gate driver IC is switched o according to fault o settings, status signaled by a low at FLT_N pin

• See later section for additional sub states on fault clear, so-reset, recover, and restore of parameter

configuration aer power loss

CFGOK.USER_OK = 0

Not Ready

State

VCC1 ok

RDYC = 0

FLT_N = x

IN = x

Fault State

RDYC = 1

FLT_N = 0

IN = x

Address

Configuration

State

Power on

OFF State

VCC1 nok

VCC2 nok

VCC1 ok

RDYC = 0

FLT_N = 1

IN = 1

I2CCFGOK.

I2CCFGOK

= 1

= 0

Parameter

Configuration

State

VCC1 ok

RDYC = 0

FLT_N = x

IN = x

CFGOK.

USER_OK

Soft-reset

= 1

Parameter

Transfer

State

VCC1 ok

VCC2 ok

RDYC = 0

FLT_N = x

IN = x

RDYSTAT.

SEC_RDY

= 1

Operation

VCC1 ok

VCC2 ok

RDYC = 1

FLT_N = 1

IN = x

Normal

RDYC = 1

RDYC = 0

FLT_N = 0 or

.SEC_FLTN = 0

GFLTEVT

Fault clearing

Figure 16 Operating state diagram

• Pin names in uppercase italic letters, supply pin status listed as either okay (ok) or not okay (nok) and for

logic pins with low (0), high (1), or either (x)

• Register names in uppercase bold letters followed by the register bit name and value

• States in bubbles with transitions marked by arrows with conditions attached

3.4.1 OFF state

The OFF state is the default state of a non-powered gate driver IC. No operation is possible.

• Input side is not powered.

• Output side is o while powered or in active shut down while unpowered.

• All commands besides input chip power-up are ignored.

Signal condition to enter state:

• VCC1 power down

Reference manual 21 v2.1

2021-02-15

Page 22

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

Signal condition to leave state:

• to address configuration state: VCC1 power ok, VCC1 has passed upper UVLO1 threshold, IN is high

3.4.2 Address configuration state

The address configuration state is used to enter or change the I2C device address and is the first state aer the

OFF state. The gate driver IC is ready to receive the device addresses.

Register access in this state:

• I2CADD, I2C device address: read/write

• I2CGADD, group address: read/write

• I2CCFGOK, address configuration access lock register: read/write

Signal condition to enter state:

• from OFF state: VCC1 power ok, VCC1 is passing upper UVLO1 threshold, IN is high

• from parameter configuration state: register bit I2CCFGOK.I2CCFGOK set to 0

Signal condition to leave state:

• to parameter configuration state: registers I2CADD and I2CGADD set according to the I2C and gate driver IC

address requirements, register bit I2CCFGOK.I2CCFGOK set to 1

B

B

3.4.3 Parameter configuration state

The parameter configuration state is used to configure or change device function and parameter and is the

default state aer address configuration state.

Register access in this state:

• address registers: read only

• I2CCFGOK: read/write

• configuration registers: read/write

• status register: read only

Signal condition to enter state:

• from address configuration state: register bit I2CCFGOK.I2CCFGOK set to 1

• from not ready state: register bit CFGOK.USER_OK set to 0

B

B

• from a so-reset

Signal condition to leave state:

• to parameter transfer state: register bit CFGOK.USER_OK set to 1

• to address configuration state: register bit I2CCFGOK.I2CCFGOK set to 0

B

B

3.4.4 Parameter transfer state

The parameter transfer state is used to transfer the configuration registers from primary to secondary side.

Register access in this state:

• status, configuration and address registers: read only

Signal condition to enter state:

• from parameter configuration state: register bit CFGOK .USER_OK set to 1

Signal condition to leave state:

• to normal operation state: VCC2/VEE2 power okay and register bit RDYSTAT.SEC_RDY set to 1

B

B

Reference manual 22 v2.1

2021-02-15

Page 23

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

3.4.5 Normal operation state

The normal operation state is used for status register read and PWM operation.

Register access in this state:

• status, configuration and address registers: read only

Signal condition to enter state:

• from parameter transfer state: register bit RDYSTAT.SEC_RDY set to 1

• from fault state: intermediate states of fault clear flow

• from not ready state: RDYC signal released

Signal condition to leave state:

• to fault state: FLT_N signal externally pulled to low or register bit GFLTEVT.SEC_FLTN = 0B indicating a fault

source from output side

• to not ready state: RDYC signal pulled to low

B

3.4.6 Not ready state

The not ready state is used to indicate an inactive gate driver IC with PWM operation disabled.

Register access in this state:

• CFGOK register: read/write

• status, configuration and address registers: read only

Signal condition to enter state:

• from normal operation state: RDYC signal pulled to low

Signal condition to leave state:

• to normal operation state: RDYC signal released

• to parameter configuration state: CFGOK.USER_OK set to 0

B

3.4.7 Fault state

The fault state is used during and aer a fault turn o until the fault condition is cleared.

Register access in this state:

• status, configuration and address registers: read only

Signal condition to enter state:

• from normal operation state: FLT_N signal externally pulled to low or register bit GFLTEVT.SEC_FLTN = 0

indicating a fault source detected by the output side of the gate driver IC

Signal condition and flow to leave state:

B

Reference manual 23 v2.1

2021-02-15

Page 24

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

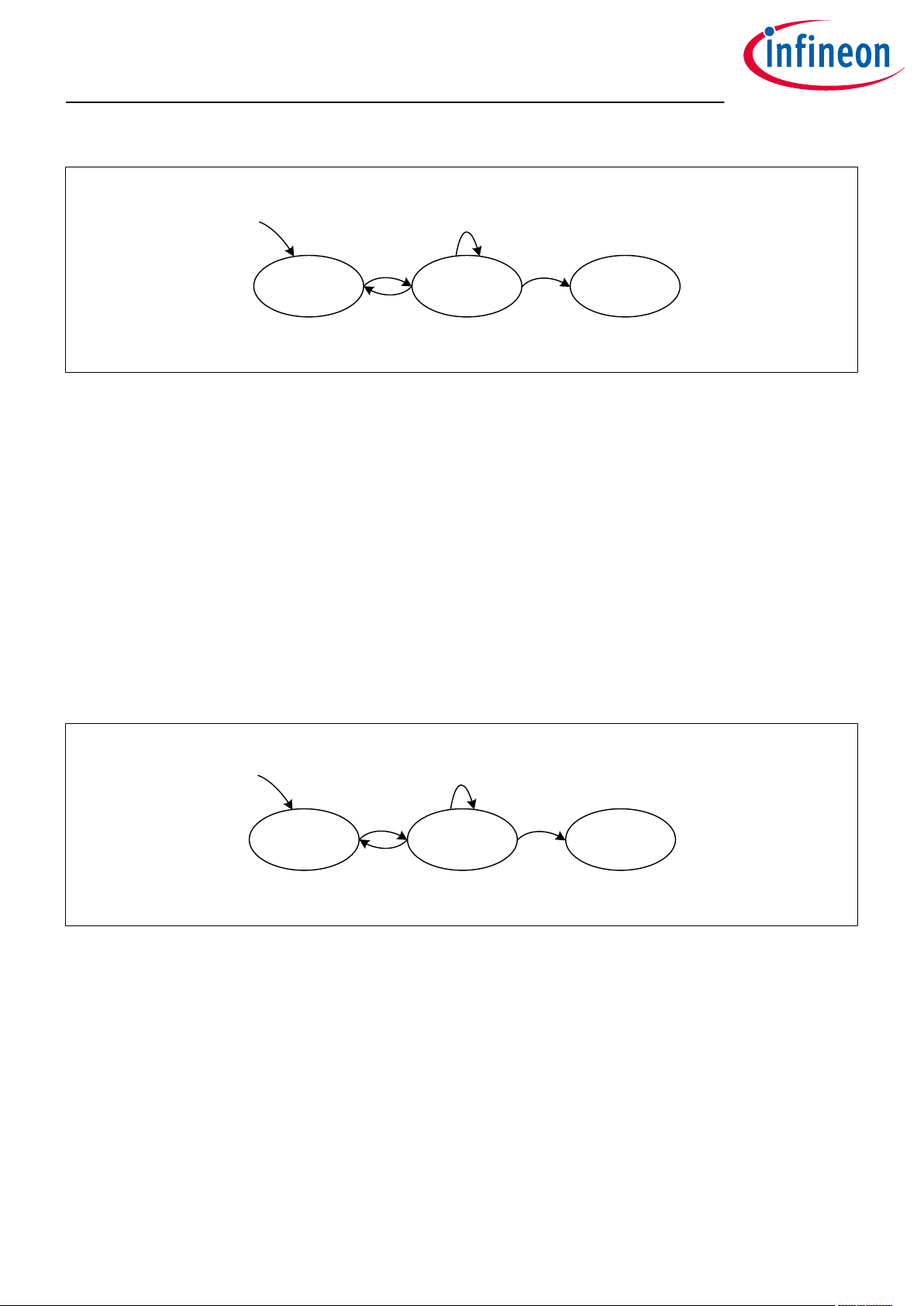

FLT_N = 0 or

.SEC_FLTN = 0

GFLTEVT

t ≤ FCLR.FSCLR_T

GFLTEVT.SEC_FLTN = 1 &

FLTEVT.VOUT_ST = 0 &

Fault State

RDYC = 1

FLT_N = 0

IN = x

FCLR.FCLR_CFG = 1

IN = 0

GFLTEVT

.SEC_FLTN = 0

Fault Clear

Pending

RDYC = x

FLT_N = 0

IN = x

Figure 17 Fault clear using self clear timer

• Pin names in uppercase italic letters, supply pin status listed as either okay (ok) or not okay (nok) and for

logic pins with low (0), high (1), or either (x)

• Register names in uppercase bold letters followed by the register bit name and value

• States in bubbles with transitions marked by arrows with conditions attached

t > FCLR.FSCLR_T

& FLT_N = 1

Normal

Operation

RDYC = 1

FLT_N = 1

Register bit FCLR.FCLR_CFG = 1B (Fault clear using self-clear timer)

1. register bit GFLTEVT.SEC_FLTN = 1B, indicating that the fault source is no longer triggering and the fault

o sequence is completed

2. register bit FLTEVT.VOUT_ST = 0B, indicating that the output switch-o is done

3. IN pin switched to low to enter the fault clear pending state

4. staying in fault clear pending for the duration of the configured self clear time FCLR.FSCLR_T without

having a new fault trigger GFLTEVT.SEC_FLTN = 0

B

5. aer fulfilling the above conditions the gate driver IC releases the FLT_N pin and returns to normal

operation state

FLT_N = 0 or

.SEC_FLTN = 0

GFLTEVT

GFLTEVT.SEC_FLTN = 1 &

FLTEVT.VOUT_ST = 0 &

Fault State

RDYC = x

FLT_N = 0

IN = x

FCLR.FCLR_CFG = 0

RDYC = 0 &

IN = 0

GFLTEVT

.SEC_FLTN = 0

&

t ≤ t

CLRMIN

RDYC = 0

Fault Clear

Pending

RDYC = 0

FLT_N = 0

IN = x

t > t

CLRMIN

RDYC = 1 &

FLT_N = 1

&

Normal

Operation

RDYC = 1

FLT_N = 1

Figure 18 Fault clear using RDYC pin

• Pin names in uppercase italic letters, supply pin status listed as either okay (ok) or not okay (nok) and for

logic pins with low (0), high (1), or either (x)

• Register names in uppercase bold letters followed by the register bit name and value

• States in bubbles with transitions marked by arrows with conditions attached

Register bit FCLR.FCLR_CFG = 0B (Fault clear using RDYC pin)

1. register bit GFLTEVT.SEC_FLTN = 1B, indicating that the fault source is no longer triggering and the fault

o sequence is completed

2. register bit FLTEVT.VOUT_ST = 0B, indicating that the output switch-o is done

3. IN pin switched to low

4. RDYC pin switched to low to enter the fault clear pending state

Reference manual 24 v2.1

2021-02-15

Page 25

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

5. staying in fault clear pending for the duration of the fault clear time t

trigger GFLTEVT.SEC_FLTN = 0

6. RDYC pin released to high

7. aer fulfilling the above conditions the gate driver releases the FLT_N pin and returns to normal

operation state

B

without having a new fault

CLRMIN

3.4.8 So-reset, restore and recovery

The 1ED38x0 family oers three configuration related modes:

• so-reset of all configuration registers to return to their reset values

• automatic restore of all output registers aer an output not ready event

• automatic recovery of all input registers aer an input not ready event

Both restore and recovery are independent and can be enabled at the same time. The automatic restore or

recovery can only work if one driver side stays supplied.

3.4.8.1 So-reset

The so-reset configuration register bit CLEARREG.SOFT_RST allows to clear all configuration registers. Unless

the automatic restore of output registers is configured, a so-reset will also be triggered aer a severe output

side UVLO event.

Aer a reset the registers will have their reset values and the gate driver IC returns to the parameter

configuration state. The I2C address registers I2CADD, I2CGADD, and I2CCFGOK will not be aected, only the

configuration registers need a new set of parameters.

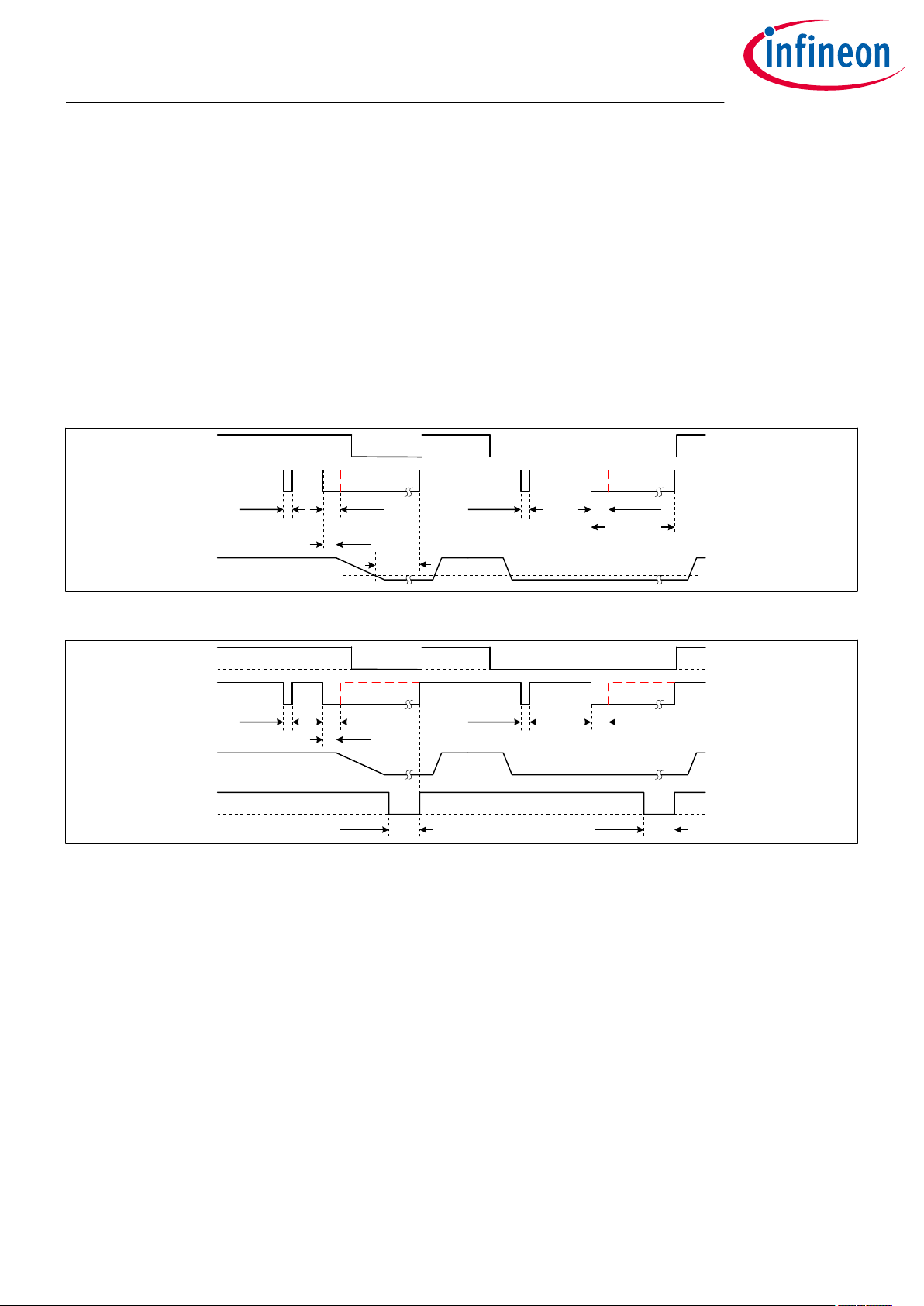

3.4.8.2 Automatic configuration restore from input side

The gate driver IC is equipped with an advanced configuration restore function. If the output side lost its

configuration (e.g. VCC2 UVLO triggered so-reset) the input side is trying to restore the data from the input side

to the output side as soon as the output side is ready again.

The function is configured in register bit RECOVER.RESTORE

• 0B = restore not active, the gate driver IC will

- perform a so-reset,

- clear parameter configuration bit CFGOK.USER_OK to 0B, and

- stay in parameter configuration state and wait for the user to re-configure the settings

• 1B = restore active, the gate driver IC will

- restore the output side and

- release RDYC and enter normal operation state

Reference manual 25 v2.1

2021-02-15

Page 26

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

Parameter

Configuration

State

VCC1 ok

RDYC = 0

FLT_N = x

IN = x

CFGOK.

USER_OK = 0

Output Side

Power Down

(not-ready)

State

VCC1 ok

VCC2 nok

RDYC = 0

I2CCFGOK.I2CCFGOK = 1

CFGOK.USER_OK = 1

RECOVER.RESTORE = 1

VCC2 -> ok

Parameter

Transfer

State

VCC1 ok

VCC2 ok

RDYC = 0

RDYSTAT.

SEC_RDY

= 1

Operation

VCC1 ok

VCC2 ok

RDYC = 1

FLT_N = 1

Normal

Figure 19 State diagram of output configuration restore from input side

• Pin names in uppercase italic letters, supply pin status listed as either okay (ok) or not okay (nok) and for

logic pins with low (0), high (1), or either (x)

• Register names in uppercase bold letters followed by the register bit name and value

• States in bubbles with transitions marked by arrows with conditions attached

The output side power down state is a not ready state where additional conditions apply. The regular path to

parameter configuration state is also possible. Otherwise the gate driver IC leaves this state to parameter

transfer state aer a successful output side power up. Aer the register transfer the status register bit

RDYSTAT.SEC_RDY will be set to 1B and the gate driver IC returns to normal operation state.

A successful restore will be signaled by the sticky bit in the register bit EVTSTICK.SRESTORE.

3.4.8.3 Automatic configuration recovery from output side

The gate driver IC is equipped with an advanced configuration recovery function. If the input side lost its

configuration (e.g. UVLO event at VCC1) the input side is trying to recover the data from the output side as soon

as the input side is ready again.

The function is configured in register RECOVER.RECOVER:

• 0B recover not active, gate driver IC will

- perform a so-reset,

- clear parameter configuration bit CFGOK.USER_OK and I2CCFGOK.I2CCFGOK to 0B, and

- returns to OFF state

• 1B recover active, gate driver IC will

- recover the configuration from the output side,

- release RDYC, and

- enter normal operation state

Input Side

Power Down

State

VCC1 nok

VCC2 ok

RDYC = 0

I2CCFGOK.I2CCFGOK = 1

CFGOK.USER_OK = 1

RECOVER.RECOVER = 1

VCC1 -> ok

Parameter

Transfer

State

VCC1 ok

VCC2 ok

RDYC = 0

RDYSTAT.

PRI_RDY

= 1

Operation

VCC1 ok

VCC2 ok

RDYC = 1

FLT_N = 1

Normal

Figure 20 State diagram of input configuration recover from output side

• Pin names in uppercase italic letters, supply pin status listed as either okay (ok) or not okay (nok) and for

logic pins with low (0), high (1), or either (x)

• Register names in uppercase bold letters followed by the register bit name and value

• States in bubbles with transitions marked by arrows with conditions attached

Reference manual 26 v2.1

2021-02-15

Page 27

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

The input side power down state is an extended o state. The gate driver IC leaves this state to

parameter transfer state aer a successful input side power up. Aer the register transfer the status register

RDYSTAT.PRI_RDY will be set to 1B and the gate driver IC returns to normal operation state.

A successful recover will be signaled by the sticky bit in the register EVTSTICK.SRECOVER.

3.5 Measurement

The 1ED38x0 family oers several measurement functions and uses a free running successive-approximationregister analog-to-digital converter (SAR-ADC). The SAR-ADC has a 8 bit resolution and the results are digitally

filtered with a three-point-two pass moving average filter.

Following internal and external parameter measurements are available:

• ADCMVCC2 Measurement VCC2 to VEE2

• ADCMVDIF Measurement and calculation VCC2 to GND2

• ADCMGND2 Measurement GND2 to VEE2

• ADCMTEMP Measurement junction temperature T

• ADCMVEXT Measurement external voltages, e.g. NTC

Measurement result registers will be updated sequentially depending on selected sample sources. The update

rate is typically below 100 µs.

The SAR-ADC configuration register ADCCFG is used to activate measurement channels and external voltage

compare behavior. Measurement of internal junction temperature is always active. Activated SAR-ADC

measurements also enable monitoring functions.

J

3.6 Monitoring

The 1ED38x0 family oers many monitoring functions. The monitoring functions can be divided into:

• Hardware based functions

The hardware based monitoring functions use dedicated hardware, e.g. fast UVLO.

• ADC-based functions

The ADC-based functions gather measured values of dierent parameters and compare them with limit

values. Enable ADC measurement to use related ADC-based monitoring functions.

Both groups contain non-configurable and configurable functions.

Non-configurable hardware monitoring:

• VEE2 over GND2, e.g. VEE2 connection failure

• Turn-o monitoring, VON > VEE2+2 V (FLTEVT.VOUT_ST = 1B)

• Gate voltage monitoring below VEE2+2 V (PINSTAT.ON_PIN = 1B)

• Gate voltage monitoring above VCC2-2 V (PINSTAT.OFF_PIN = 1B)

• Gate voltage monitoring above V

• Pin status monitoring of IN pin high (PINSTAT.PWM_IN = 1B)

• Pin status monitoring of RDYC pin high (PINSTAT.RDYC = 1B)

• Pin status monitoring of FLT_N pin high (PINSTAT.FLT_N = 1B)

• VCC1 supply voltage UVLO spike detection (UV1FCNT)

• VCC2 supply voltage UVLO spike detection (UV2FCNT)

Configurable hardware monitoring:

• Normal VCC2 supply UVLO event (SECUVEVT.UV_VCC2)

• Normal VEE2 supply UVLO event (SECUVEVT.UV_VEE2)

• Switch-o timeout, VON > VEE2+2 V and maximal switch-o timeout time elapsed (FLTEVT.SOTO_EVT)

(PINSTAT.TLTO_LVL = 1B)

TLTOFF

Reference manual 27 v2.1

2021-02-15

Page 28

EiceDRIVER

™

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

Non-configurable ADC-based monitoring:

• Over temperature protection event (FLTEVT.OTP_EVT)

Configurable ADC-based monitoring:

• VCC2 supply so UVLO event (SECUVEVT.UVSVCC2)

• VEE2 supply so UVLO event (SECUVEVT.UVSVEE2)

• External voltage compare event (FLTEVT.VEXTFLT)

• Over temperature warning event (FLTEVT.OTW_EVT)

Gate driver reaction to VEE2 over GND2 detected

A VEE2 over GND2 event triggers the following sequence:

1. IC detects VEE2 over GND2

2. IC initiates an output side reset, including

• Activation of active shutdown as a safety measure

• Resetting all configuration registers to their reset values

• Ignoring all PWM signals and reporting a not ready state

3. IC listens to its previously configured I2C address

• If RECOVER.RESTORE = 1B, the gate driver IC will restore the output side configuration from the input

side

• If RECOVER.RESTORE = 0B, the gate driver IC performs a so-reset and waits for a re-configuration via

I2C bus

4. Aer the configuration of the output side is valid again, the IC continues operation

Note: To avoid unintended VEE2 over GND2 detection, take extra care in power supply design, routing, and

capacitive blocking at these pins.

Reference manual 28 v2.1

2021-02-15

Page 29

™

EiceDRIVER

1ED38x0Mc12M Enhanced

Reference manual

3 Functional description

3.7 Desaturation protection

The desaturation detection circuit protects the external IGBT from destruction at a short circuit. The

desaturation protection follows the given sequence:

1. Voltage at DESAT pin reaches DESAT threshold level, e.g. 9.18 V, for a period of time exceeding the filter

time

2. Gate driver IC output switches the external IGBT o, using the defined fault o method

3. Gate driver IC switches FLT_N pin to low to indicate the fault to a connected microcontroller

4. Short circuit situation is resolved

• aer the voltage at the ON pin has dropped below the VEE2+2 V threshold,

• no other fault condition is present,

• the input has been turned o and

• the fault has been cleared using the defined fault clear method

VCC2

D

A

DESAT

LOGIC

FLT_off

OFF

GND2

+15V

C

VCC2

R

DESATDDESAT

R

G

Figure 21 DESAT circuit (only relevant pins shown)

The high-precision internal current source results in a minimum impact on the DESAT detection variation.

3.7.1 DESAT behavior

The DESAT function oers a leading edge blanking time and filters to optimize the DESAT detection for

application usage.

The leading edge blanking inhibits threshold detection during an IGBT turn on phase. The typical IGBT turn on

behavior starts with charging of the gate, commutation of the application load current and finally VCE voltage

decrease to V

blanking pauses the DESAT circuit until the time t

Following the leading edge blanking time, the gate driver IC forces the DESAT current into the external

DESAT circuit. The current typically flows through a protection resistor, a fast high voltage diode and the