Impala Linear Corporation ILC1832N, ILC1832M Datasheet

ILC1832

µP Supervisory Circuit

Impala Linear Cor poration

Impala Linear Corporation

1

(408) 574-3939

www.impalalinear.com

October 1999

ILC1832 1.1

The ILC1832 is a multifunction circuit which monitors microprocessor activity, external reset and power supplies in

microprocessor based systems. Ths circuit functions

include a watchdog timer, power supply monitor, microprocessor reset, and manual pushbutton reset input.

The power supply line is monitored with a comparator and

an internal voltage reference. RST is forced low when an

out-of-tolerance condition exists and remains asserted for

at least 250ms after V

CC

rises above the threshold voltage

(2.55V or 2.88V). The RST pin will remain logic low with

V

CC

as low as 1.4V.

The Watchdog input (ST) monitors µP activity and will assert

RST if no µP activity has occurred within the watchdog timeout period. The watchdog timeout period is selectable with

nominal periods of 150, 600, or 1200 milliseconds.

• Power OK/Reset Time Delay, 250ms min.

• Watchdog Timer, 150 ms, 600ms, or 1.2s Typical

• Precision Supply Voltage Monitor, Select Between 5%

or 10% of Supply Voltage

• 18µA Supply Current

• Debounced External Reset Input

• 8-Pin SOIC or DIP Package

• Computers

• Controllers

• Critical Microprocessor Power Monitoring

• Intelligent Instruments

• Portable Equipment

ILC1832

V

CC

Top View

PBRST

RST

TD

2

1 8

6

RST

GND

ST

TOL

4

3

5

7

ETC1832N - 8 Lead Plastic DIP Package

ETC1832M - 8 Lead Plastic SOIC Package

ILC1832

µµ

P

V

CC

V

CC

V

CC

ST

RESET

PBRST

RST

TD

GND

TOL

I/O

Part

Package

Temp. Range

ILC1832N

8-Lead PDIP

-40°C to +85°C

ILC1832M

8-Lead SOIC

-40°C to +85°C

General Description

Features

Applications

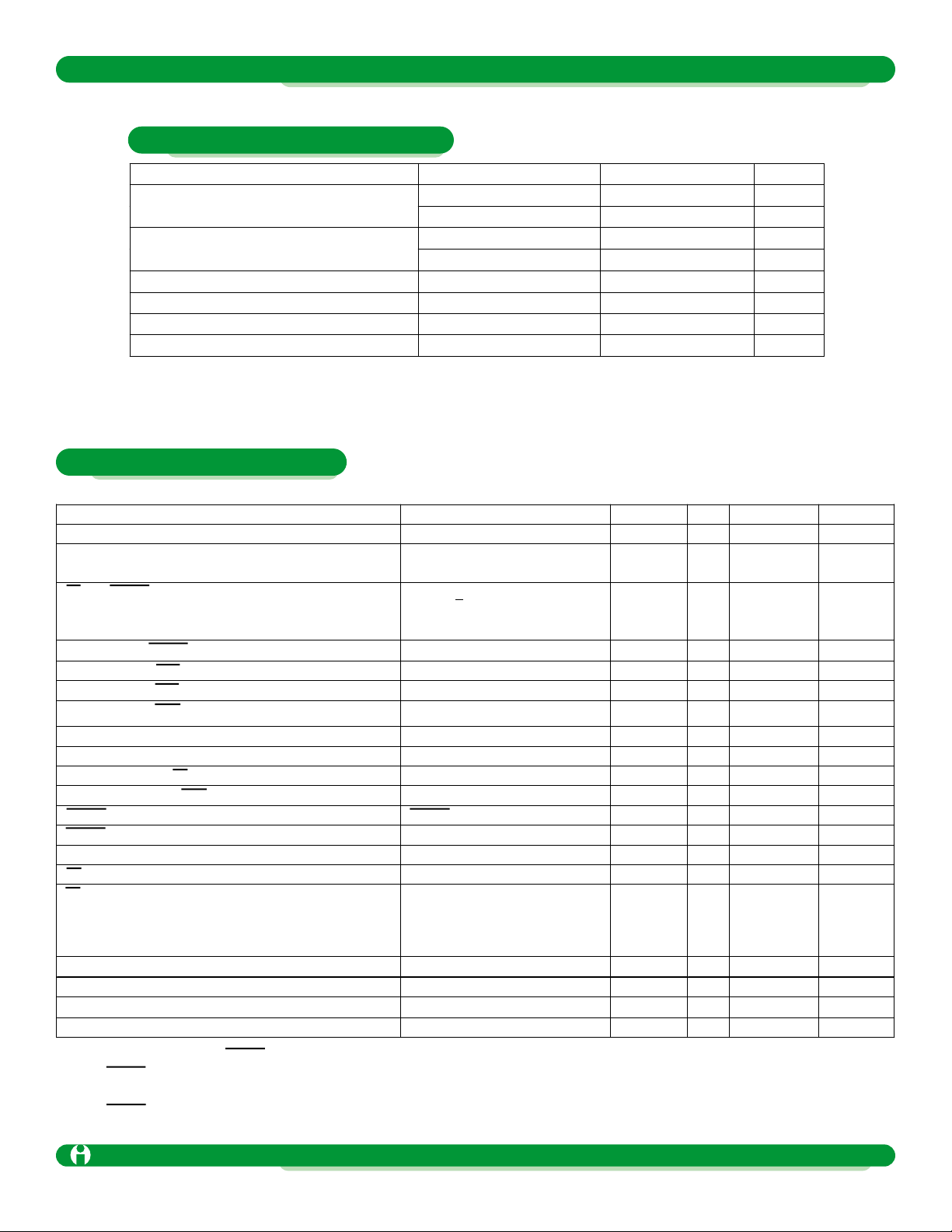

Ordering Information

Typical Circuit

Pin-Package Configurations

Preliminary

Parameter

Symbol

Ratings

Units

VCC

-0.3 to 7.0

V

Terminal Voltage

All other inputs

-0.3 to (VCC + 0.3)

V

VCC

250

mA

Input Current

GND All other inputs

25

mA

Operating Temperature Range

TA

-40 to +85

°C

Storage Temperature Range

-65 to +150

°C

Lead Temperature (Soldering, 10 sec . )

300

°C

Power Dissipation

700

mW

Parameter

Conditions

Min

Typ

Max

Units

Supply Voltage Range, VCC

5.5

V

Supply Current, ICC

VCC = 5V (See Note 1)

VCC = 3.3V (See Note 1)

18

15

30

25

µA

ST and PBRST Input Levels

VIH, VCC > 2.7V

VIH, VCC < 2.7V

VIL

2.0

VCC –0.4

-0.3

VCC + 0.3

VCC + 0.3

0.5

V

Input Leakage PBRST, IIL

(See Note 2)

±1

µA

Output Voltage, RST, RST

I

SOURCE

= 350µA, VCC = 3.3V

2.4

V

Output Voltage, RST, RST

I

SINK

= 10mA, VCC = 3.3V

0.4

V

Output Voltage, RST

I

SINK

= 50µA, VCC = 1.4V

0.3

V

VCC 5% Trip Point (Reset Threshold Voltage)

TOL= GND

2.80

2.88

2.97

V

VCC 10% Trip Point (Reset Threshold V ol t age)

TOL= VCC

2.47

2.55

2.64

V

Input Capacitance, ST, TOL

CIN (See Note 3)

5

pF

Output Capacitance, RST, RS T

C

OUT

(See Note 3)

7

pF

PBRST Min. Pulse Width, tPB

PBRST = VIL (See note 4)

20

ms

PBRST Delay, t

PBD

1 4

20

ms

Reset Active Time, t

RST

250

610

1000

ms

ST Pulse W i dt h, tST

20

ns

ST Timeout Period, tTD

TD = 0V

TD = Open

TD = VCC

62.5

250

500

150

600

120

0

250

1000

2000

ms

VCC Fall Time, tF

40

µs

VCC Rise Time, tR

0 ns

VCC Detect to RST Low and RST High, tRPD

VCC Falling at 1.66 mV/µs

5 8

µs

VCC Detect to RST Open and RST Low, tRPU

VCC Rising

250

610

1000

ms

VCC= 3 to 5.5V, TA= Operating Temperature Range, unless otherwise noted.

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at

or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

Operating ranges define those limits between which the functionality of the device is guaranteed.

Note 1: ICCis measured with PBRST and all outputs open and inputs within 0.5V of supply rails.

Note 2: PBRST has an internal 40kΩ (typical) pull-up resistor to VCC.

Note 3: Guaranteed by design at TA= 25°C.

Note 4: PBRST must be held low for a minimum of 20ms to guarantee a reset.

µP Supervisory Circuit

Preliminary

Impala Linear Corporation

2

(408) 574-3939

www.impalalinear.com

October 1999

ILC1832 1.1

Electrical Characteristics

Absolute Maximum Ratings

Loading...

Loading...