IMP IMP805LMJA, IMP805LCSA, IMP802LCSA, IMP802MEPA, IMP802MCSA Datasheet

...

Key Features

Applications

◆ Embedded control systems

◆ Battery–operated systems

◆ Intelligent instruments

◆ Wireless communication systems

◆ PDAs and handheld equipment

◆

µP/µC power supply monitoring

◆

Design improvement over Maxim

MAX690A/692A/802L/802M/805L

— 70% lower current than Maxim:

100µA maximum

— RESET Operation to 1.1V

◆

Two precision supply-voltage monitor options

— 4.65V (IMP690A/802L/805L)

— 4.40V (IMP692A/802M)

◆

Battery-backup power switch on-chip

◆

Watchdog timer: 1.6 second timeout

◆

Power failure/low battery detection

◆

Short-circuit protection and thermal limiting

◆

Small 8-pin SO package

◆

No external components

◆

Specified over full temperature range

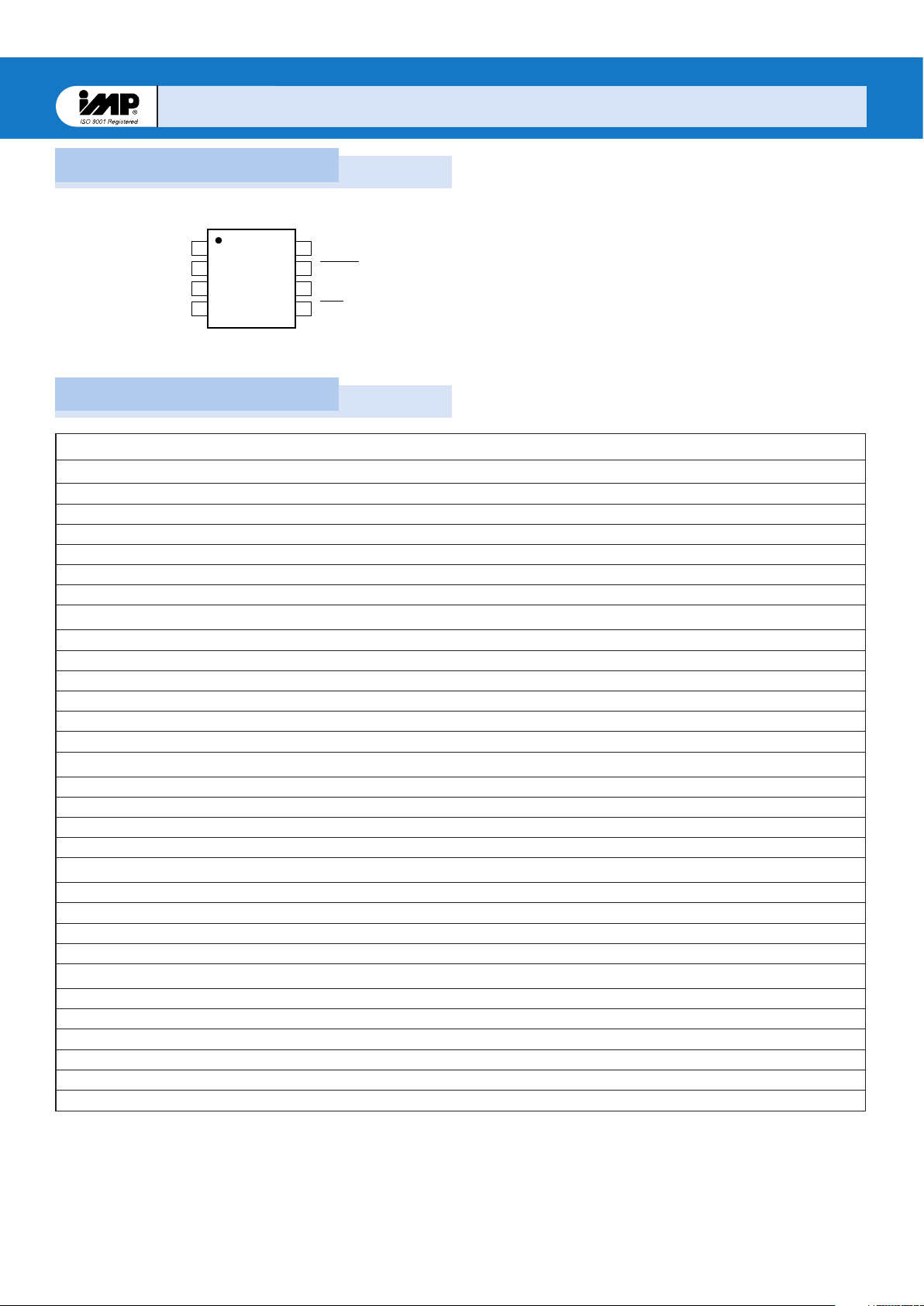

Block Diagrams

+

–

GND

Unregulated DC Regulated +5V

V

OUT

V

CC

WDI

3.6V

Lithium

Battery

0.1µF

PFO

V

BATT

PFI

R

1

R

2

RESET

RESET

V

CC

GND

GND

V

CC

CMOS

RAM

NMI

I/O LINE

BUS

690A_01.eps

IMP690A

IMP690A

IMP690A

, 692A

, 692A

, 802L/M, 805L

, 802L/M, 805L

POWER MANAGEMENT

µµP P

P Pooww

er Suppl

er Suppl

y Super

y Super

visor

visor

wit

wit

h Batt

h Batterer

y Bac

y Bac

kup Switc

kup Switchh

The IMP690A/IMP692A/IMP802L/IMP802M/IMP805L simplify power

supply monitoring and control in microprocessor systems. Each circuit

implements four functions: Reset control, watchdog monitoring, batterybackup switching and power-failure monitoring. In addition to

microprocessor reset under powerup and power-down conditions, these

devices provide battery-backup switching to maintain control in powerloss and brown-out situations. Additional monitoring capabilities

can provide an early warning of unregulated power-supply loss before

the voltage regulator drops out. The important features of these four

functions are:

a) 1.6 second watchdog timer to keep microprocessor responsive

b) 4.40V or 4.65V V

CC

threshold for microprocessor reset at power-up

and power-down

c) SPDT (single-pole, double-throw) PMOS switch connects backup

power to RAM if V

CC

fails

d) 1.25V threshold detector for power loss or general purpose voltage

monitoring

While these features are pin–compatible with the industry standard

power–supply supervisors offered by Maxim, the IMP devices are superior replacements and can reduce power requirements by 70 percent

when compared to Maxim MAX690/MAX692A/MAX802L/MAX802M/

MAX805L devices. Short-circuit and thermal protection have also

been added.

The IMP690A/IMP802L/IMP805L generate a reset pulse when the

supply voltage drops below 4.65V, and the IMP692A/IMP802M

generate a reset below 4.40V. The IMP802L/IMP802M have power–fail

accuracy to ±2%. The IMP805L is the same as the IMP690A except that

RESET is provided instead ofRESET.

IMP, Inc. San Jose, CA 408-432-9100/www.impweb.com

+

+

+

+

+

+

+

+

V

CC

V

OUT

1

7

5

3

PFI

WDI

GND

V

BATT

8

2

6

4

PFO

IMP690A, IMP692A, IMP802L, IMP802M,

IMP805L

RESET

(RESET)

( ) IMP805L

Battery-Switchover

Circuit

Reset

Generator

Watchdog

Timer

3.5V

1.25V

1.25V

0.8V

690A_03.eps

Typical Application

Ordering Information

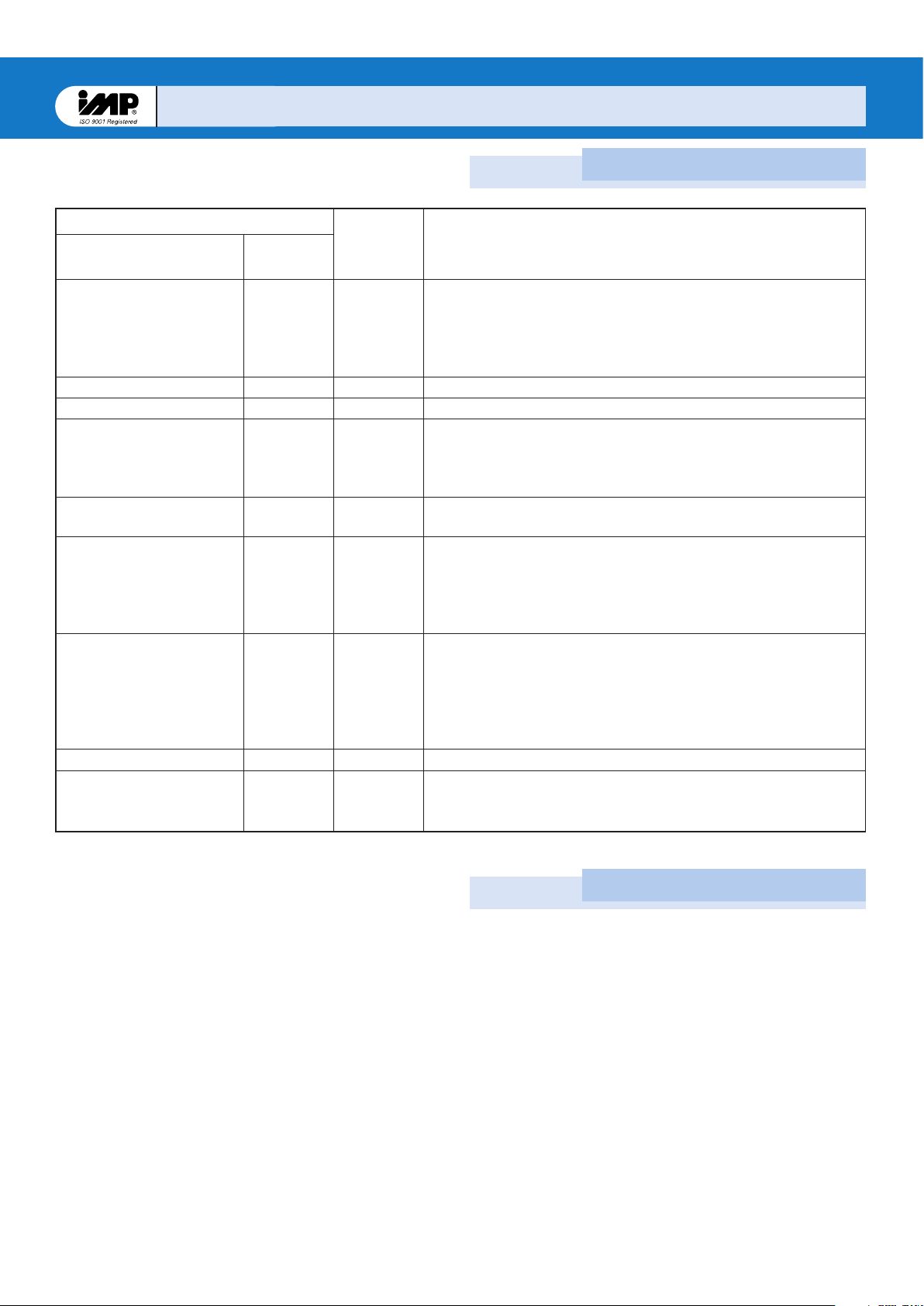

Pin Configuration

2

IMP690A

IMP690A

, 692A

, 692A

, 802L, 802M, 805L

, 802L, 802M, 805L

4PFI

3GND

2V

CC

1V

OUT

5 PFO

6 WDI

7 RESET (RESET)

8 V

BATT

690A_02.eps

IMP690A

IMP692A

IMP802L

IMP802M

IMP805L

( ) IMP805L

Plastic/CerDip/SO

Part Number Reset Threshold (V) Temperature Range Pins-Package

IMP690A

IMP690ACPA 4.5 to 4.75 0°C to +70°C 8-Plastic DIP

IMP690ACSA 4.5 to 4.75 0°C to +70°C 8-SO

IMP690AC/D 4.5 to 4.75 25°C DICE

IMP690AEPA –40°C to +85°C 8-Plastic DIP

IMP690AESA 4.5 to 4.75 –40°C to +85°C 8-SO

IMP690AMJA 4.5 to 4.75 Contact Factory 8-CerDIP

IMP692A

IMP692ACPA 4.25 to 4.50 0°C to +70°C 8-Plastic DIP

IMP692ACSA 4.25 to 4.50 0°C to +70°C 8-SO

IMP692AC/D 4.25 to 4.50 25°C DICE

IMP692AEPA 4.25 to 4.50 –40°C to +85°C 8-Plastic DIP

IMP692AESA 4.25 to 4.50 –40°C to +85°C 8-SO

IMP692AMJA 4.25 to 4.50 Contact Factory 8-CerDIP

IMP802L

IMP802LCPA 4.5 to 4.75 0°C to +70°C 8-Plastic DIP

IMP802LCSA 4.5 to 4.75 0°C to +70°C 8-SO

IMP802LEPA 4.5 to 4.75 –40°C to +85°C 8-Plastic DIP

IMP802LESA 4.5 to 4.75 –40°C to +85°C 8-SO

IMP802M

IMP802MCPA 4.25 to 4.50 0°C to +70°C 8-Plastic DIP

IMP802MCSA 4.25 to 4.50 0°C to +70°C 8-SO

IMP802MEPA 4.25 to 4.50 – 40°C to +85°C 8-Plastic DIP

IMP802MESA 4.25 to 4.50 – 40°C to +85°C 8-SO

IMP805L

IMP805LCPA 4.5 to 4.75 0°C to +70°C 8-Plastic DIP

IMP805LCSA 4.5 to 4.75 0°C to +70°C 8-SO

IMP805LC/D 4.5 to 4.75 25°C DICE

IMP805LEPA 4.5 to 4.75 – 40°C to +85°C 8-Plastic DIP

IMP805LESA 4.5 to 4.75 – 40°C to +85°C 8-SO

IMP805LMJA 4.5 to 4.75 Contact Factory 8-CerDIP

IMP690A

IMP690A

, 692A

, 692A

, 802L, 802M, 805L

, 802L, 802M, 805L

Absolute Maximum Ratings

Pin Description

Pin Terminal Voltage with Respect to Ground

V

CC

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3V to 6.0V

V

BATT

. . . . . . . . . . . . . . . . . . . . . . . . . . . . –0.3V to 6.0V

All Other Inputs* . . . . . . . . . . . . . . . . . . . – 0.3V to (V

CC

+ 0.3V)

Input Current at V

CC

. . . . . . . . . . . . . . . . . . 200mA

Input Current at V

BATT

. . . . . . . . . . . . . . . . . 50mA

Input Current at GND . . . . . . . . . . . . . . . . . 20mA

Output Current:

V

OUT

. . . . . . . . . . . . . . . Short circuit protected

All Other Inputs . . . . . . . . . . . . . . . . . . . 20mA

Rate of Rise: V

BATT

and V

CC

. . . . . . . . . . 100V/µs

Continuous Power Dissipation

Plastic DIP (derate 9mW/°C above 70°C) . . . 800mW

SO (derate 5.9mW/°C above 70°C) . . . . . . . . 500mW

CerDIP (derate 8mW/°C above 70°C) . . . . . . 650mW

Operating Temperature Range (C Devices) . . . . 0°C to 70°C

Operating Temperature Range (E Devices) . . . . – 40°C to 85°C

Storage Temperature Range . . . . . . . . . . . . . . . . . –65°C to 160°C

Lead Temperature Soldering, (10 sec) . . . . . . . . 300°C

* The input voltage limits on PFI and WDI may be exceeded if the

current is limited to less than 10mA

These are stress ratings only and functional operation is not implied.

Exposure to absolute maximum ratings for prolonged time periods may

affect device reliability.

Pin Number

IMP690A/IMP692A

IMP802L/IMP802M IMP805L Name Function

1 1 V

OUT

Voltage supply for RAM. When VCCis above the reset threshold, V

OUT

connects to VCCthrough a P-channel MOS device. If VCCfalls below the

reset threshold, this output will be connected to the backup supply at

V

BATT

(or VCC, whichever is higher) through the MOS switch to provide

continuous power to the CMOS RAM.

2 2 V

CC

+5V power supply input

3 3 GND Ground

4 4 PFI Power failure monitor input. PFI is connected to the internal power fail

comparator which is referenced to 1.25V. The power fail output (PFO)

is active LOW but remains HIGH if PFI is above 1.25V. If this feature is

unused, the PFI pin should be connected to GND or V

OUT

.

5 5 PFO Power-fail output. PFO is active LOW whenever the PFI pin is less than

1.25V.

6 6 WDI Watchdog input. The WDI input monitors microprocessor activity. An

internal timer is reset with each transition of the WDI input. If WDI is held

HIGH or LOW for longer than the watchdog timeout period, typically 1.6

seconds, RESET (orRESET) is asserted for the reset pulse width time,

tRS, of 140ms, minimum.

7 –––– RESET Active-LOW reset output. When triggered by VCCfalling below the reset

threshold or by watchdog timer timeout, RESET (orRESET) pulses low

for the reset pulse width, tRS, typically 200ms. It will remain low if VCCis

below the reset threshold (4.65V in the IMP690A/IMP802L and 4.4V in

the IMP692A/IMP802L) and remains low for 200ms after VCCrise above

the reset threshold.

–––– 7 RESET Active-HIGH reset output. The inverse ofRESET.

8 8 V

BATT

Auxiliary power or backup-battery input. V

BATT

should be connected to

GND if the function is not used. This input has about 40mV of hysteresis

to prevent rapid toggling between VCCand V

BATT

.

3

Loading...

Loading...