MICROWAVE TEST SET 6200B SERIES

6200B 10 MHz to 20 GHz 6201B 10 MHz to 8 GHz 6202B 10 MHz to 2 GHz 6203B 10 MHz to 26.5 GHz 6204B 10 MHz to 46 GHz

© IFR Ltd. 1998

No part of this book may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, or recorded by any information storage or retrieval system, without permission in writing by IFR Ltd.

IFR Ltd was formerly known as Marconi Instruments Ltd. Any reference in this manual to Marconi Instruments or MI should be construed as IFR Ltd.

Printed in the UK

Manual part no. 46882-240W Issue 4

17 November 1998

CONTENTS

Preface

Precautions

- Chapter 1 TECHNICAL DESCRIPTION

- Chapter 2 MAINTENANCE

- Chapter 3 ADJUSTMENT & CALIBRATION

- Chapter 4 INITIAL REPAIR

- Chapter 5 FAULT DIAGNOSIS

- Chapter 6 REPLACEABLE PARTS

- Chapter 7 SERVICING DIAGRAMS

Preface

CONVENTIONS

The following conventions apply throughout this manual:

| CAPS | Capitals are used to identify names of controls and panel markings, or system functions where no direct reference to an associated key is intended. |

|---|---|

| [CAPS] | Capitals in square brackets indicate hard key titles. |

| [Italics] | Italics in square brackets indicate soft key titles. |

SOFTWARE STATUS

The operating software for this instrument is contained in EEPROMs fitted inside the unit. The software issue number can be determined by pressing [UTILITY][Service][Status][Display Build State].

PATENT PROTECTION

The 6200B Series Microwave Test Sets are protected by the following Patents:

US4609881 US5237291 and others

PRECAUTIONS

WARNINGS, CAUTIONS and NOTES

The following terms have specific meanings in this manual:

WARNINGS contain information to prevent personal injury. CAUTIONS contain information to prevent damage to the equipment. Notes contain important general information.

Symbols

The meaning of hazard symbols appearing on the equipment is as follows:-

General hazard

Description

Dangerous voltage

Toxic hazard

Static sensitive components

General conditions of use

This product is designed and tested to comply with the requirements of EN61010-1/IEC1010-1 'Safety requirements for electrical equipment for measurement, control and laboratory use', for Class I portable equipment and is for use in a pollution degree 2 environment. The equipment is designed to operate from an installation category II supply.

Equipment should be protected from the ingress of liquids and precipitation such as rain, snow, etc. When moving the equipment from a cold to a hot environment, it is important to allow the temperature of the equipment to stabilise before it is connected to the supply to avoid condensation forming. The equipment must only be operated within the environmental conditions specified in Chapter 1 'Performance data' in the Operating manual, otherwise the protection provided by the equipment may be impaired.

This product is not approved for use in hazardous atmospheres or medical applications. If the equipment is to be used in a safety-related application, e.g. avionics or military applications, the suitability of the product must be assessed and approved for use by a competent person.

WARNING - Electrical hazards (AC supply voltage)

This equipment conforms with IEC Safety Class I, meaning that it is provided with a protective grounding lead. To maintain this protection the supply lead must always be connected to the source of supply via a socket with a grounded contact.

Be aware that the supply filter contains capacitors that may remain charged after the equipment is disconnected from the supply. Although the stored energy is within the approved safety requirements, a slight shock may be felt if the plug pins are touched immediately after removal.

Fuses

Note that there are supply fuses in both the live and neutral wires of the supply lead. If only one of these fuses should rupture, certain parts of the equipment could remain at supply potential.

Removal of covers

Disconnect the supply before removing the covers so as to avoid the risk of exposing high voltage parts. If any internal adjustment or servicing has to be carried out with the supply on, it must only be performed by a skilled person who is aware of the hazard involved.

WARNING - Toxic hazards

Some of the components used in this equipment may include resins and other materials which give off toxic fumes if incinerated. Take appropriate precautions, therefore, in the disposal of these items.

WARNING - Beryllia

Beryllia (beryllium oxide) is used in the construction of the following components in this equipment:

RF Board, A2 (44829/780): IC502, TR204 and TR206. Microwave chassis: YIG tuned oscillators.

This material, when in the form of fine dust or vapour and inhaled into the lungs, can cause a respiratory disease. In its solid form, as used here, it can be handled quite safely although it is prudent to avoid handling conditions which promote dust formation by surface abrasion.

Because of this hazard, you are advised to be very careful in removing and disposing of these components. Do not put them in the general industrial or domestic waste or despatch them by post. They should be separately and securely packed and clearly identified to show the nature of the hazard and then disposed of in a safe manner by an authorized toxic waste contractor.

WARNING - Lithium

A Lithium battery (or a Lithium battery contained within an IC) is used in the following components in this equipment:

Rear panel battery compartment

Lithium batteries present two types of hazards:

As Lithium is a toxic substance, the battery should in no circumstances be crushed, incinerated or disposed of in normal waste.

Do not attempt to recharge this type of battery. Do not short circuit or force discharge since this might cause the battery to vent, overheat or explode.

WARNING - Beryllium copper

Some mechanical components within this instrument are manufactured from beryllium copper. This is an alloy with a beryllium content of approximately 5%. It represents no risk in normal use.

The material should not be machined, welded or subjected to any process where heat is involved.

It must be disposed of as "special waste".

It must NOT be disposed of by incineration.

CAUTION - STATIC SENSITIVE COMPONENTS

The presence of static sensitive devices is indicated in the equipment by labels bearing the appropriate symbol (see page iv). Certain handling precautions must be observed to prevent these components being permanently damaged by static charges or fast surges.

- (1) If a printed circuit board containing static sensitive components (as indicated by a warning label) is removed, it must be temporarily stored in a conductive plastic bag.

- (2) If a static sensitive component is to be removed or replaced the following anti-static equipment must be used:

A work bench with a grounded conductive surface.

Metallic tools grounded either permanently or by repeated discharges.

A low-voltage grounded soldering iron.

A grounded wrist strap and a conductive grounded seat cover for the operator, whose outer clothing must not be of man-made fibre.

- (3) As a general precaution avoid touching the leads of a static sensitive component. When handling a new one, leave it in its conducting mount until it is required for use.

- (4) If using a freezer aerosol in fault finding, take care not to spray programmable ICs as this may affect their contents.

CAUTION - IC REMOVAL

Damage can be caused if an IC mounted in a PLCC (plastic leaded chip carrier) is removed without the use of a special tool. This tool is available from Marconi Instruments Service Division (address on rear cover), part no. WP02.

CAUTION - CLEANING OF LCD WINDOW

The LCD window should be cleaned by wiping a slightly damp, soft, lint-free cloth gently over the surface. To remove grease or smears, use a clean, cotton cloth moistened with Heptane. No other cleaning agents should be used. Clean the window using either horizontal or vertical strokes, NEVER a circular action.

CAUTION - TILT FACILITY

When the instrument is in the tilt position, it is advisable, for stability reasons, not to stack other instruments on top of it.

CAUTION - FAN FILTER CLEANING

This instrument is cooled by a fan whose filters are fabricated from wire gauze. The fan must be removed and cleaned periodically. Clean with a suction cleaner and, if necessary, with hot soapy water. Do not use a solvent cleaner.

CAUTION - PRECISION CONNECTOR

The precision connectors fitted to this equipment may be damaged by mating with a non-precision type. Damage to the connectors may also occur if the connector interface parameters are not within specification. This should be checked with an appropriate gauging tool. Refer to Chapter 2 of the Operating Manual for further information on connector care.

Chapter 1 TECHNICAL DESCRIPTION

CONTENTS

C

C

C

| INTRODUCTION | |

|---|---|

| Synthesizer | |

| Microwave Chassis | |

| Digital PCB | |

| Analogue PCB | |

| Auxiliary Interface PCB | |

| Dynamic Calibrator PCB | |

| Floppy Drive Controller PCB | 1-7 |

| LCD Interface PCB | |

| Keyboard PCB | |

| Colour Display | |

| Power Supply Unit | 1-7 |

| SYNTHESIZER | 1-15 |

| Introduction | 1-15 |

| Overall Description | 1-15 |

| DEDCB | 1 16 |

| 1-10 | |

| Introduction | 1-16 |

| VCOs | 1-19 |

| Oscillators | 1-19 |

| Direct and Divider Bands | |

| Direct Band Path | |

| Dividers | |

| Filters | |

| Mixer Band. | |

| Beat Frequency Oscillator. | |

| Down Converter. | 1-21 |

| 1-22 | |

| Noltage Controlled Attenuator | |

| Voltage Controlled Attenuator | |

| Samplar Drive Amplifier | |

| 1-23 | |

| Filters and Loop Pandwidth Switching | |

| Force vCO Tulle | |

| VCO Tuning Monitor | |

| Introduction | 1 24 |

| VIG Tuning and Bias Switching | |

| Output Levelling | |

| Fractional N Synthesizer | |

| BEO Phase I ocked I oon | 1-20 |

| Sampler IF Amplifier and Filters | 1-20 |

| VTO Phase-I ocked I oon | 1-29 |

| Frequency Counter |

1-30

1 20 |

| Digital Board Interface |

1-32

1_33 |

| TIMEBASE PCB | 1_36 |

| 1 26 | |

| Operating Modes |

1-30

1_36 |

| operating into avoid the second s |

| Oscinator Tuning | 1-37 |

|---|---|

| 30 MHz VCXO | 1-37 |

| Frequency Division | 1-37 |

| Phase/Frequency Comparator and PLL | 1-37 |

| SYNTHESIZER POWER SUPPLY FILTER PCB | 1-38 |

| FREQUENCY STANDARD PCB | 1-38 |

| ANALOGUE PCB | 1-39 |

| Introduction | 1-39 |

| Front End Amplifiers - Scalar Detector | 1-39 |

| Front End Amplifiers - Power Sensor Amplifier | 1-39 |

| Chopper Drive | 1-40 |

| Sensor Zeroing | 1-40 |

| Sensor/Detector Identification | 1-40 |

| Alternate Input Multiplexer | 1-43 |

| Second Stage Amplifier | 1-43 |

| Amplifier Nulling | 1-44 |

| Gain Calibration | 1-44 |

| Sweep Filter | 1-45 |

| Sample and Hold Amplifier | 1-45 |

| Autoranging | 1-45 |

| Range Comparators | 1-45 |

| A to D Converter | 1-46 |

| Input Multiplexer | 1-46 |

| ADC Operation | 1-46 |

| Graphics Processing | 1-47 |

| Graphics Processor | 1-47 |

| Transputer Interface | 1-47 |

| Colour Palette and Video Outputs | 1-48 |

| LCD Control | 1-48 |

| LCD Control | 1-48 |

| LCD Control |

1-48

1-48 1-49 |

| DIGITAL PCB |

1-48

1-48 1-49 1-49 |

| LCD Control DIGITAL PCB Introduction Memory Map and Address Ranges |

1-48

1-48 1-49 1-49 1-49 |

| LCD Control DIGITAL PCB Introduction Memory Map and Address Ranges |

1-48

1-48 1-49 1-49 1-49 1-49 |

| LCD Control |

1-43

1-48 1-49 1-49 1-49 1-53 |

|

LCD Control

DIGITAL PCB Introduction Memory Map and Address Ranges High Level Address Decode Low Level Address Decode Main Processor, Address Latches, Decoding and Support Main Processor |

1-48

1-48 1-49 1-49 1-49 1-53 1-54 |

| LCD Control |

1-48

1-48 1-49 1-49 1-49 1-53 1-54 1-54 |

| LCD Control |

1-48

1-48 1-49 1-49 1-49 1-53 1-54 1-54 1-54 |

|

LCD Control

DIGITAL PCB Introduction Memory Map and Address Ranges High Level Address Decode Low Level Address Decode Main Processor, Address Latches, Decoding and Support Main Processor Graphics Transputer and Adapter Interface |

1-43

1-48 1-49 1-49 1-49 1-53 1-54 1-54 1-54 1-54 |

|

LCD Control

DIGITAL PCB Introduction Memory Map and Address Ranges High Level Address Decode Low Level Address Decode Main Processor, Address Latches, Decoding and Support Main Processor Graphics Transputer and Adapter Interface Address Latches Address Decoding Event Hendler |

1-43

1-48 1-49 1-49 1-49 1-53 1-54 1-54 1-54 1-54 1-54 |

|

LCD Control

DIGITAL PCB Introduction Memory Map and Address Ranges High Level Address Decode Low Level Address Decode Main Processor, Address Latches, Decoding and Support Main Processor Graphics Transputer and Adapter Interface Address Latches |

1-43

1-48 1-49 1-49 1-49 1-53 1-54 1-54 1-54 1-54 1-55 1-55 |

|

LCD Control

DIGITAL PCB Introduction Memory Map and Address Ranges High Level Address Decode Low Level Address Decode Main Processor, Address Latches, Decoding and Support Main Processor Graphics Transputer and Adapter Interface Address Latches Address Decoding Event Handler Wait State Generator |

1-43

1-48 1-49 1-49 1-49 1-53 1-54 1-54 1-54 1-54 1-54 1-55 1-55 |

| LCD Control DIGITAL PCB Introduction Memory Map and Address Ranges High Level Address Decode Low Level Address Decode Main Processor, Address Latches, Decoding and Support. Main Processor Graphics Transputer and Adapter Interface Address Latches Address Latches Maddress Decoding Event Handler Wait State Generator Memconfig Dueffering |

1-43

1-48 1-49 1-49 1-49 1-53 1-54 1-54 1-54 1-54 1-55 1-55 1-55 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-55 1-56 1-56 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-55 1-56 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-56 |

|

LCD Control

DIGITAL PCB |

1-43 1-48 1-49 1-53 1-54 1-55 1-56 1-56 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-56 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-56 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-56 1-57 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-56 1-56 1-57 1-57 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-54 1-55 1-56 1-57 |

|

LCD Control

DIGITAL PCB |

1-43 1-48 1-49 1-53 1-54 1-54 1-55 1-56 1-56 1-57 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-56 1-57 1-58 1-58 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-54 1-55 1-56 1-57 1-58 |

| LCD Control | 1-43 1-48 1-49 1-53 1-54 1-55 1-56 1-57 1-58 |

| 1-59 |

|---|

| 1-59 |

| 1-60 |

| 1-60 |

| 1-60 |

| 1-60 |

| 1-6 |

| 1-61 |

| 1-6 ] |

| 1-61 |

| 1-61 |

| 1-62 |

| 1-62 |

| 1-62 |

| 1-62 |

| 1-63 |

| 1-64 |

| 1-64 |

| 1-64 |

| 1-64 |

| 1-65 |

| 1-66 |

| 1-66 |

| 1-67 |

| 1-67 |

| 1-67 |

| 1-67 |

| 1-68 |

| 1-68 |

| 1-69 |

| 1-69 |

| 1-70 |

| 1-70 |

| 1-70 |

| 1-70 |

| 1-71 |

|

1-71

1-71 |

|

1-71

1-71 |

|

1-71

1-71 1-72 |

|

1-71

1-71 1-72 1-72 |

|

1-71

1-71 1-72 1-72 1-72 |

|

1-71

1-71 1-72 1-72 1-72 1-72 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-72 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-72 1-72 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-72 1-73 1-73 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 1-73 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 1-74 1-74 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 1-74 1-74 1-74 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 1-74 1-74 1-75 1-75 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 1-74 1-74 1-75 1-75 1-75 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 1-73 1-74 1-74 1-75 1-75 1-75 1-75 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 1-74 1-74 1-75 1-75 1-75 1-75 1-77 |

|

1-71

1-71 1-72 1-72 1-72 1-72 1-72 1-73 1-73 1-73 1-73 1-74 1-74 1-75 1-75 1-75 1-77 1-77 |

_

| LCD INTERFACE PCB | 1-79 |

|---|---|

| FLOPPY DRIVE CONTROLLER PCB | 1-79 |

| POWER SUPPLY | |

|

Introduction

Mains Input and RFI Filter |

1-80

1-80 |

| INPUT PCB | |

| Overall Function |

1-80

1-81 1-81 1-81 1-81 1-82 |

| Shut-down Inhibit Line | 1-82 |

| Current Limit Detector | 1-82 |

| SECONDARY PCB | |

| Low Voltage Supplies |

1-83

1-83 1-84 1-84 1-84 |

| Temperature Status Comparators | 1-84 |

| 5.1 V and 25 V Overvoltage Detector | 1-84 |

| Overload Sampler | 1-84 |

| Power-Up Sequence (Soft Start) | 1-85 |

LIST OF FIGURES

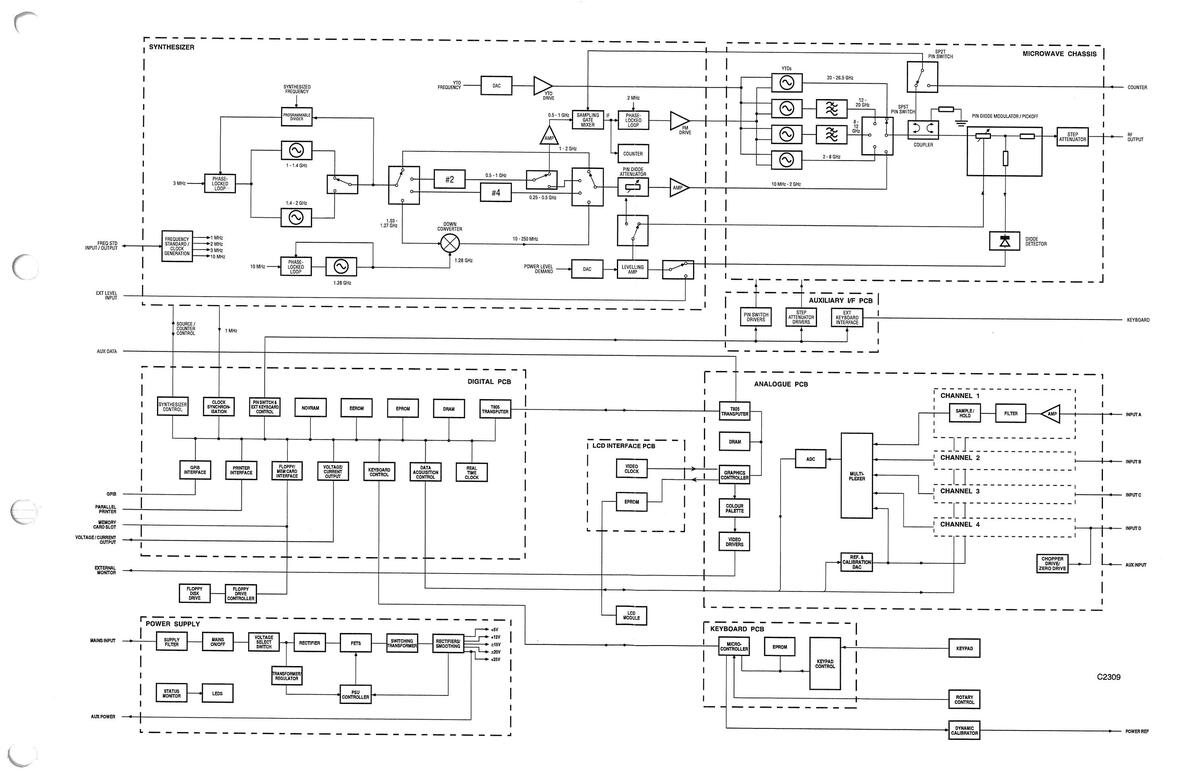

| Fig. 1-1 | Block Schematic Diagram of the MTS (6200B/6201B/6203B) | 1-9 |

|---|---|---|

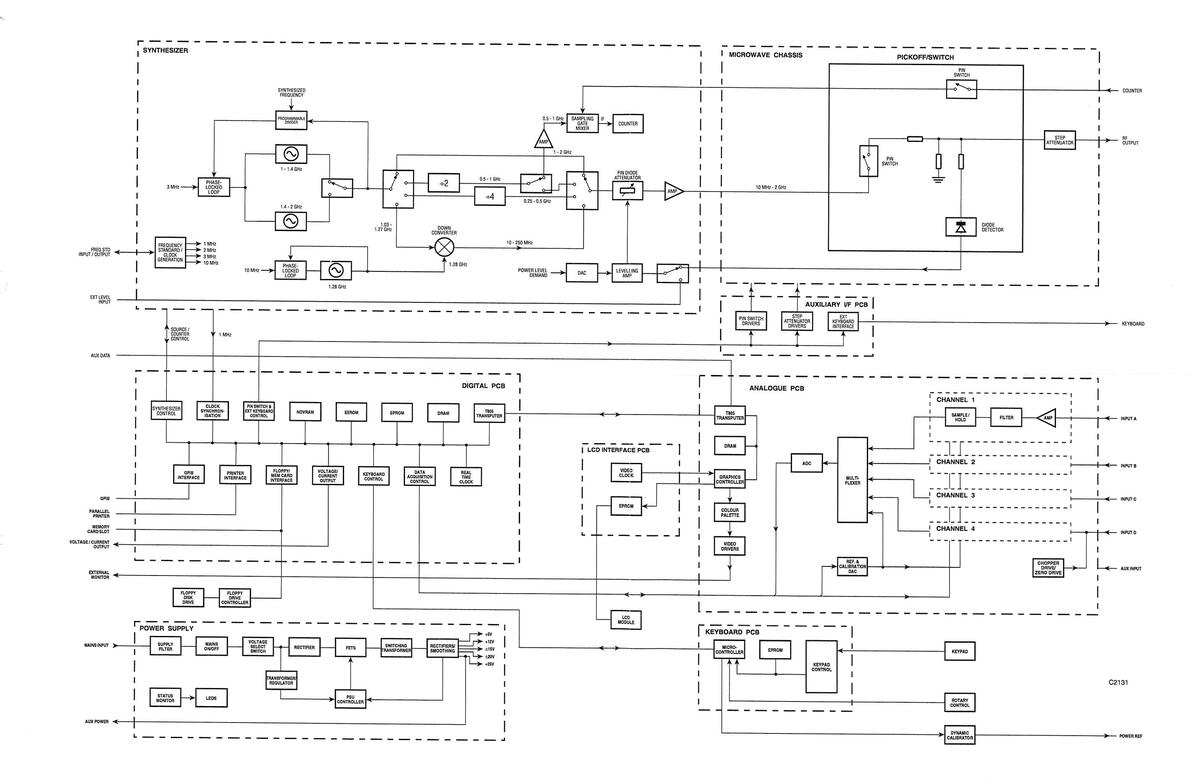

| Fig. 1-2 | Block Schematic Diagram of the MTS (6204B) | 1-11 |

| Fig. 1-3 | Block Schematic Diagram of the 6202B RF Test Set | 1-13 |

| Fig. 1-4 | Synthesizer | 1-17 |

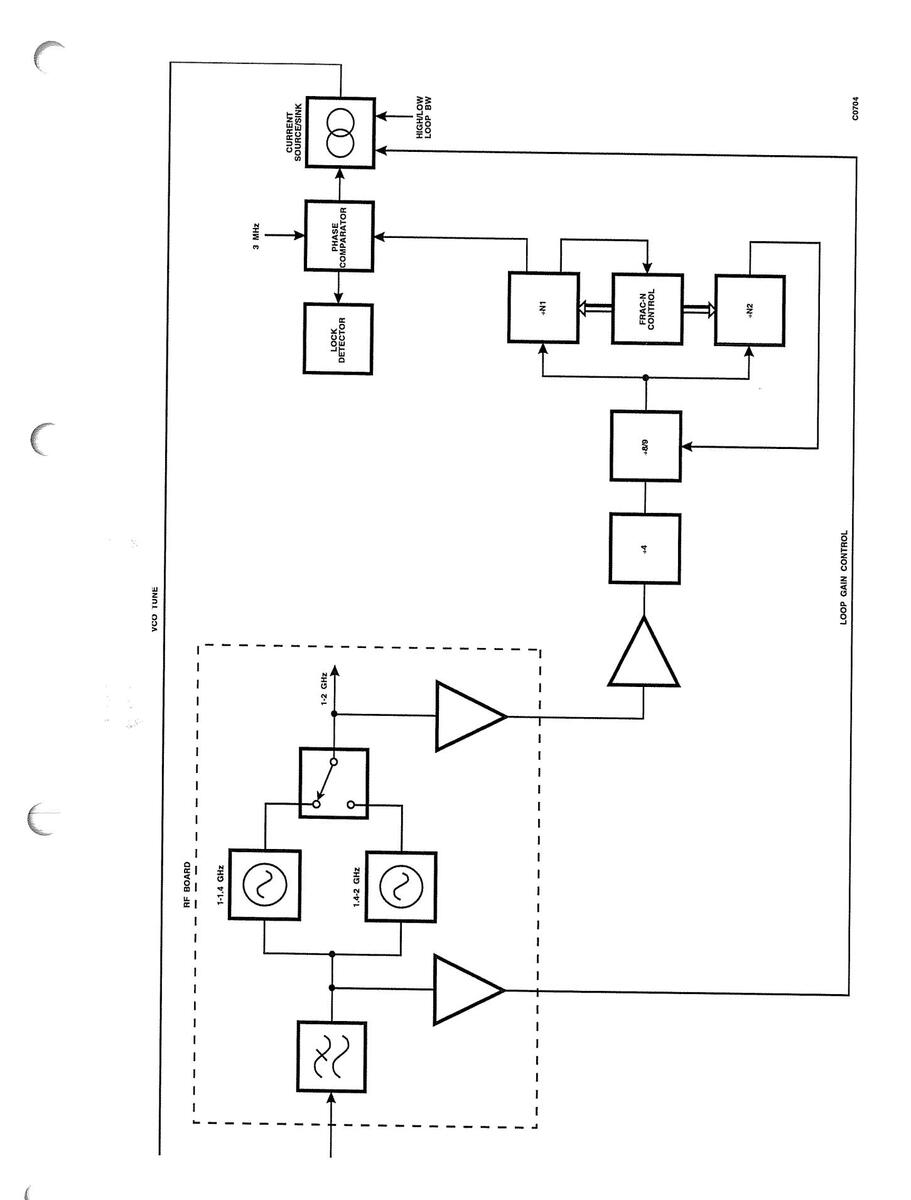

| Fig. 1-5 | Fractional-N Synthesizer | 1-27 |

| Fig. 1-6 | YTO Phase-Locked Loop | 1-31 |

| Fig. 1-7 | Data Acquisition System | 1-41 |

| Fig. 1-8 | Block Diagram of the Digital PCB | 1-51 |

| Fig, 1-9 | Dynamic Calibrator | 1-76 |

INTRODUCTION

The description which follows is intended as an overview of the 6200B Series MTS hardware, and relates to the functional blocks of the instrument as shown in Figs. 1-1 to 1-3, which are simplified block schematic diagrams of the instrument. Fig. 1-1 illustrates the 6203B (10 MHz - 26.5 GHz) MTS; the 6201B (10 MHz - 8 GHz) and 6200B (10 MHz - 20 GHz) are subsets of this structure. The 6204B is illustrated in Fig. 1-2, which differs mainly in the microwave chassis. The 6202B is an RF Test Set, designed to operate up to 2 GHz. Most of the Microwave components are not therefore required, as reflected in the block diagram of Fig. 1-3.

Synthesizer

The synthesizer module is responsible for generating the RF signals in the range 10 MHz to 2 GHz, and also provides the means of controlling and phase-locking the YIG tuned oscillators (YTO) which generate signals above 2 GHz. In addition, it contains the frequency standard circuitry, the power level control circuitry and the frequency counter hardware. The synthesizer functions are carried out by the RF PCB, Control PCB, Timebase PCB and Frequency Standard PCB, but the operation of the synthesizer can be explained more effectively by not representing them separately on the block diagram.

The output of a 30 MHz voltage controlled crystal oscillator (VCXO) is divided down to give the various clock frequencies used within the synthesizer. This oscillator is phase-locked to a 10 MHz oven-controlled crystal oscillator (OCXO). If a 1 or 10 MHz external standard is selected, the VCXO is phase locked to that instead.

Two voltage controlled oscillators provide the coverage between 1 and 2 GHz. These are divided by 2 or 4 to give signals down to 250 MHz, and the 10 MHz to 250 MHz range is generated by a beat frequency oscillator (down converter). The synthesizer uses a programmable divider (using the Marconi Instruments patented fractional-N architecture) to allow high resolution whilst maintaining a high phase detector frequency. This permits a higher loop bandwidth and hence a faster settling time. A variable attenuator is used to control the level of the 10 MHz to 2 GHz signal, and the following amplifier boosts the signal to the required level.

The YTOs which generate signals above 2 GHz within the microwave chassis are sampled by a sampling gate mixer. The mixer is driven by a local oscillator signal provided by the divide-by-2 synthesizer path. The resultant IF signal is processed by a phase-locked loop circuit, whose output is used to drive the FM coils of the YTOs. This does not apply to the 6202B since there are no YTOs.

The sampling gate mixer is also used during frequency counter operation to generate an IF which is counted by the counter circuitry. If the signal is below 400 MHz direct frequency counting is employed (via the sampling gate).

Microwave Chassis

The microwave chassis is responsible for signal generation above 2 GHz by means of one or more YTOs. The number of YTOs depends on the instrument version; one for the 6201B, three for the 6200B and four for the 6203B and 6204B. The 8-12 GHz and 12-20 GHz oscillators are followed by discrete low pass filters to reduce harmonics. The 2-8 GHz oscillator contains an integral tracking filter.

A PIN switch (SP4T for 6200B/6201B, SP5T for 6203B/6204B) selects one of its inputs, which includes the 10 MHz to 2 GHz signal generated by the synthesizer. The switch can be set so that none of the inputs are selected, and no RF signal appears at the output connector. A broadband directional coupler separates out part of the signal from the YTOs (i.e. frequencies above 2 GHz), which is sampled by the sampling gate mixer and used for phase locking as described earlier. The through path of the coupler is followed by a broadband modulator which, together with the resistive pickoff (coupler on 6204B), diode detector and control circuitry in the synthesizer, form the levelling circuit. The modulator is set to minimum attenuation for frequencies less than 2 GHz, generated by the synthesizer. If fitted, the optional step attenuator is situated between the matching resistor and the RF OUTPUT connector.

When the frequency counter is in use, an SP2T switch routes the COUNTER input signal to the sampling gate, instead of the coupled YTO signal.

In the 6204B instrument (Fig. 1-2), the microwave chassis has additional components for the generation of signals between 26.5 and 46 GHz, i.e. a 13.25 - 23 GHz amplifier, a 23 GHz low pass filter and a frequency doubler. A DPDT PIN switch is used to switch these components into the RF path when RF signals in the range 26.5 - 46 GHz are required. A 46 GHz coupler and diode detector provide a levelling signal for outputs in the range 2 to 46 GHz; a resistive pickoff/detector is used for outputs below 2 GHz.

The 6202B is not required to generate frequencies above 2 GHz, so the microwave chassis does not contain any YTOs. The microwave chassis contains only a pickoff/switch assembly and a step attenuator, if this option is fitted. The pickoff/switch assembly contains a PIN diode switch to isolate the RF signal from the output connector when no RF output is required. This function is carried out by the SP4T (SP5T) switch in the other variants. A second PIN switch is used to isolate the COUNTER input from the sampling gate mixer when the counter function is not being used. The assembly also contains a resistive pickoff and diode detector, which provides a sample of the RF signal for use in the levelling circuit.

Digital PCB

The Digital PCB provides all the main control and processing functions of the MTS. The processor used is the T805 transputer which is a 32-bit floating point processor operating at 20 MHz. Associated with this are 4 MBytes of dynamic RAM. The instrument's firmware is located in a block of EPROM. Non-volatile memory is provided by a block of battery backed static RAM (NOVRAM) which contains such things as instrument settings stores, and a block of EEROM which contains the fundamental calibration data for the MTS. A battery backed real-time clock is also located on this board.

Other functional blocks provide the necessary control for the synthesizer module, Analogue PCB, Auxiliary Interface PCB and the keyboard.

Also located on the Digital PCB is the clock synchronisation circuitry. This consists of two phase-locked loops which lock the 20 MHz transputer clock and a 22 MHz clock for the data acquisition system to the 1 MHz reference clock generated from the frequency standard within the synthesizer.

Various input/output functions are handled by the Digital PCB including GPIB, PARALLEL PRINTER and VOLTAGE/CURRENT OUTPUT.

Analogue PCB

The Analogue PCB contains two main areas of circuitry; the data acquisition and the graphics.

The data acquisition consists of four differential amplifier chains for inputs A, B, C and D. Each chain has two gain stages with eight ranges, the range changing being under hardware control. A reference and calibration DAC allows automatic calibration of each gain combination on each of the four amplifier chains. A noise reduction filter is used for slow sweeps. Sample-and-hold circuits for each chain allow simultaneous sampling of data on all four inputs. Each sample-and-hold is then multiplexed in turn to a 16-bit audio ADC whose output is fed to the Digital board. The circuitry for input D is slightly different in that it also generates the necessary power sensor chopper amplifier and zero drive circuitry. The AUX INPUT connection is used to receive detector inputs from the 6210 Reflection Analyzer.

The graphics circuitry is based around the 82786 graphics processor which has three main functions. Firstly, its drawing processor implements a range of drawing commands. Secondly, its DRAM controller manages all the timing and refresh signals for the 1 MByte of video memory associated with the graphics system. Thirdly, its video controller generates the video sync signals for the optional external CRT monitor. Associated with the graphics processor is a second T805 floating point transputer and a further 1 MByte of DRAM. In addition to controlling the graphics processor the transputer performs many other processing functions. The colour palette and video drivers provide the RGB signals required by the external colour monitor.

The AUX DATA connection is used to transfer digital data between the MTS and the AUX DATA port of the 6210 Reflection Analyzer.

Auxiliary Interface PCB

The Auxiliary Interface PCB consists of three functional blocks under the control of the Digital PCB. It provides control circuitry for the microwave chassis PIN switches (SP2T and SP4(5)T) and the optional step attenuator; provides power for the 40 GHz amplifier in the 6204B; contains the interface circuitry for the external keyboard.

Dynamic Calibrator PCB

The Dynamic Calibrator PCB consists essentially of a variable gain amplifier in a digitally controlled levelling loop. This provides a variable power output that is used for calibrating the 6230A/L series EEPROM detectors. It can also generate the 50 MHz, 1 mW POWER REF signal used for calibrating the power meter sensors.

Floppy Drive Controller PCB

This PCB interfaces with the Digital PCB and the floppy disk drive, and is used to control floppy disk functions, such as motor on/off and reading/writing data.

LCD Interface PCB

The LCD Interface PCB contains an EPROM whose address inputs are provided by the graphics controller on the Analogue PCB. The EPROM contains the colour information required by the LCD module. The board also contains a crystal oscillator which provides a 25 MHz video clock for the graphics processor IC on the Analogue PCB.

Keyboard PCB

The purpose of the Keyboard PCB is to handle the keypad and rotary control interfaces. An 8031 microcontroller is used for the following: Detect keypresses and rotary control movement; handle multiple keypresses and key bounce; pre-process rotary control information; communicate the information to the Digital PCB transputer via a serial link. The keyboard software is contained in EPROM.

Colour Display

The display is a VGA TFT colour liquid crystal display, with a resolution of 640 by 480 pixels. A PCB mounted on the rear of the display converts a low voltage supply from the PSU into a high voltage, low current supply for driving the LCD backlight.

Power Supply Unit

The power supply is a switched mode unit and runs directly from the AC supply. After passing through a filter network the incoming AC supply is rectified and smoothed. The AC supply is also passed through a transformer to derive the power for the control circuitry. A PSU controller IC is used to generate a pulse width modulated waveform which drives the switching FETs. These FETs in turn switch the rectified mains line to the switching transformer. The outputs from the transformer secondaries are rectified and smoothed to provide the required output supplies for the instrument. Various status conditions are monitored within the PSU which drive status LEDs on the rear panel of the MTS. The AUX POWER connection is used to supply 25 V DC to the 6210 Reflection Analyzer.

Fig. 1-1 Block Schematic Diagram of the MTS (6200B/6201B/6203B)

1-9

Block Schematic Diagram of the MTS 6200B/6201B/6203B

Fig. 1-2 Block Schematic Diagram of the MTS (6204B)

Fig. 1-3 Block Schematic Diagram of the 6202B RF Test Set

SYNTHESIZER

Introduction

The synthesizer, together with the microwave chassis, forms the MTS source. The synthesizer performs the following functions:

- (a) Signal generation in the range 10 MHz to 2 GHz.

- (b) YTO tuning and phase-locking in the range 2 8 GHz, 2 to 20 GHz or 2 to 26.5 GHz, depending on the instrument. This does not apply to the 6202B, which does not contain YIG oscillators.

- (c) Output level control.

- (d) Frequency counter.

The synthesizer module comprises four PCBs: RF, Control, Timebase and Synthesizer Power Supply Filter. The first three boards are inside the synthesizer tray; the Synthesizer Power Supply Filter board is mounted on the outside of the tray. Although not physically part of the synthesizer module, the Frequency Standard PCB will be described in this section since it is part of the synthesizer function.

The RF and Control boards are mounted either side of a floor in the synthesizer tray, and power and control connections are made via a 26-way ribbon cable which passes through a slot in the floor. Coaxial connections are used for the two RF signals, and the BFO tuning voltage passes through a feedthrough capacitor. The Timebase board is mounted above the Control board; all interconnections are via a 34-way ribbon cable.

In addition to the four boards, there is a microwave sampling gate mounted on the synthesizer tray. This is used as a down-converter for phase-locking the YTOs and also when the source is used as a frequency counter.

Overall Description

Figs. 1-1 to 1-3 show the functional connections to the synthesizer. All YTO supplies and tuning signals come from the Control board, but the SP5T and SP2T switches are driven by the Auxiliary Interface board. The Auxiliary Interface board also supplies the drive signals for the pickoff/switch assembly in the 6202B.

The detector which is connected to the pick/mod (combined PIN diode modulator and pickoff) is used for levelling over the full frequency range of the instrument. In a 6204B instrument, a 46 GHz diode detector is used for levelling above 2 GHz, and a 2 GHz pickoff is used below 2 GHz. Alternatively, the source can be levelled remotely using an external detector or power meter. The modulator in the pick/mod is only used above 2 GHz as it would generate excessive harmonics at lower frequencies. Below 2 GHz it is reverse-biased and a modulator on the RF board is used. This modulator is used for levelling in a 6202B instrument.

The SP2T switch connects a sampling gate mixer to either the 16 dB coupler for YIG locking, or a front panel connector (COUNTER) for frequency counting. In the 6202B, a switch within the pickoff/switch assembly isolates the sampling gate from the COUNTER input when the frequency counter is not required.

Fig. 1-4 is a simplified block diagram of the synthesizer tray, showing the main functions performed on each board. Nearly all connections with the rest of the instrument are via the Control board, the exceptions being the RF output from the RF board, the sampler RF input and the +5.1 V and +15 V supplies via the Synthesizer Power Supply Filter board.

The RF board generates output signals in the range 0.01 - 2 GHz, and also provides 0.5 - 1 GHz LO drive for the sampling gate. Two 1/2-octave VCOs cover the range 1 - 2 GHz. The VCOs' output is divided by 2 or 4 to extend the range down to 250 MHz. Coverage down to 10 MHz is achieved by mixing 1.03 - 1.27 GHz with the output from a 1.28 GHz BFO (beat frequency oscillator). A PIN diode modulator is followed by the output amplifier. The sampler drive is provided by a separate amplifier in the divide-by-2 path.

The dividers and phase comparators used to lock the VCOs are located on the Control board. The 1 - 2 GHz synthesizer uses fractional-N division to give high resolution with a single loop. A single YIG tune DAC is used; its output is switched into one of four drive amplifiers.

The level DAC output is compared with the voltage from either a detector on the microwave chassis or an external detector/power meter. The levelling loop is completed by either the modulator on the microwave chassis, or the modulator on the RF board for output frequencies below 2 GHz.

The YTOs are locked to harmonics of the sampler drive frequency. The IF signal from the sampler is filtered, amplified and divided by 64, then compared with a 2 MHz reference. The resultant error signal is amplified and applied to the YTO FM coils. The frequency counter works by counting IF frequencies derived from the sampler drive and input frequencies.

The control interface for the synthesizer tray is between the Control board and the Digital board, via a 34way ribbon cable. The Control board also monitors a number of voltages and status lines for calibration and diagnostic purposes.

The synthesizer tray uses 1, 2, 3 and 10 MHz as reference frequencies. These are derived from a 30 MHz VCXO on the Timebase board. When the MTS is set to internal standard, the VCXO is locked to an ovencontrolled crystal oscillator (OCXO) on the Frequency Standard PCB, and a 10 MHz output is provided on the rear panel (FREQ STD INPUT/OUTPUT). Alternatively, the VCXO can be locked to a 1 or 10 MHz external standard. A 1 MHz signal is sent to the Digital board, to lock the other frequencies used in the instrument.

RF PCB

Introduction

The RF board is required to generate signals between 10 MHz and 2 GHz at levels between -10 dBm and +7 dBm (+6 dBm for 6204B) at the front panel RF OUTPUT connector. Between the RF board and the instrument front panel there is the microwave chassis, which is used to generate signals above 2 GHz. The microwave chassis has an insertion loss of between 3 dB and 8 dB for signals between 10 MHz and 2 GHz. To ensure the correct front panel output level, the RF board must be capable of compensating for this loss. This gives a required RF board output power level between -7 dBm (-10+3) and +15 dBm (+7+8). The harmonic requirement of the output is -30 dBc, and this must be met over all of the previously derived output power level range. The simplified block diagram of Fig. 1-4 illustrates the various blocks which comprise the RF board.

The frequency range of the RF board is divided into a number of bands as shown below:

| Mixer band | 10 MHz - 250 MHz |

|---|---|

|

|

250 MHz - 500 MHz |

| ÷2 | 500 MHz - 1 GHz |

| Direct | 1 GHz - 2 GHz |

With the exception of the mixer band, each of these bands is again split into two bands each covering a half octave. This is because there are two VCOs on the RF board, each covering a half octave instead of a single VCO covering a whole octave, which would be harder to achieve. The ÷2 and ÷4 bands use pre-scalers to divide the 1 - 2 GHz signal from the VCOs by 2 or 4 to produce frequencies between 250 MHz and 1 GHz. Within the mixer band a signal from the lower 1/2 octave VCO is down converted by a mixer and local oscillator (BFO); filtering is then used to remove unwanted mixer products.

Fig. 1-4 Synthesizer

1-17

1-18

Hence the total number of bands is shown below:

| Mixer band | 10 MHz - 250 MHz |

|---|---|

| ÷4 lower 1/2 octave | 250 MHz - 350 MHz |

| ÷4 upper 1/2 octave | 350 MHz - 500 MHz |

| ÷2 lower 1/2 octave | 500 MHz - 700 MHz |

| ÷2 upper 1/2 octave | 700 MHz - 1.0 GHz |

| Direct lower 1/2 octave | 1.0 GHz - 1.4 GHz |

| Direct upper 1/2 octave | 1.4 GHz - 2.0 GHz |

VCOs

Circuit diagram: Fig. 7-9.

Two VCOs are used to give the required coverage of 1 - 2 GHz. Microwave amplifiers are used to increase the output level of the VCOs, and each oscillator has a low-pass filter to reduce unwanted harmonics.

Oscillators

In order to achieve the required coverage of an octave, two VCOs are used which together produce a signal between 1 GHz and 2 GHz, each VCO operating over half an octave. The first VCO, consisting of TR101 and associated circuitry, covers 1 GHz to 1.4 GHz, while the second, consisting of TR102 and its associated circuitry, covers 1.4 GHz to 2 GHz. These oscillators use a negative resistance technique to produce a sustained oscillation.

The base inductance L101 combined with internal transistor feedback makes the resistive component of the impedance looking into the emitter appear negative above a certain frequency. Hence power gain is available above this frequency. The tuned circuit consisting of L104, C105 and varactor D101 determine the frequency of oscillation. R106 to R108 form a 12 dB pad which helps to buffer the VCO from the following circuitry.

A microwave amplifier (IC101) running into compression is used to produce a constant output level over the VCO's operating frequency range. This level is reduced by the 3 dB pad (R136 to R138) to the required level. A printed low-pass filter (FL101) reduces harmonics of the wanted frequency to less than -40 dBc.

The second VCO, which consists of TR102 etc., is very similar to the first, but requires two varactor diodes to give the necessary frequency coverage.

These oscillators are referred to as the lower and upper half octave respectively. Only one of these oscillators is required to be on at a particular time. Transistors TR103/105 (for the lower half octave) and TR104/106 (for the upper half octave) are used to switch on the appropriate oscillator, as required by the Control board. D104 and R122 form a simple change-over switch which is used to route the signal from the selected oscillator through to the following common circuitry. This circuitry consists of a power splitter (R125 etc.), amplifier (IC105) and 6 dB pad (R142 etc.).

The output from R126, labelled "1-2 GHz RF", represents the major output, which is used by following circuitry to produce signals between 10 MHz and 2 GHz. The output from the 6 dB pad is routed via SKD to the Fractional-N loop on the Control board for locking purposes.

Direct and Divider Bands

Circuit diagram: Fig. 7-11.

To produce signals between 1 and 2 GHz, the output of the appropriate VCO is simply amplified/attenuated to the correct level.

To produce signals between 250 MHz and 1 GHz, two frequency dividers are used on the 1 - 2 GHz signal from the oscillators; a divide-by-2 and a divide-by-4. Four low-pass filters are used to reduce the level of harmonics on the output of these dividers; PIN diode switches are used to select the appropriate filter. Individual pads after each filter provide flexibility in setting the output levels of each of the divided frequency bands.

Direct Band Path

PIN diode package D302 is used to switch between the mixer band and the direct band; D301 is used to switch between the divide-by-2 band and the divide-by-4 band. Only one of these four bands can be selected at any one time, hence only one diode in these two diode packages can be biased on; the other three will be biased off. (One diode in each of these two packages is unused and has simply been bypassed.) The output of IC306 goes to almost +15 V to select the direct band path, which is via forward biased diodes in each of packages D302, D310, D311 and D304.

When the mixer or divider bands are selected, the isolation of this path is critical in determining the spurious or harmonic performance of the output respectively. Also, because of the large physical separation of D310 and D311 (approx. 11 cm), the microstripline which forms this path will have a resonance somewhere between 1 and 2 GHz.

To de-select this path, the output of IC306 goes to -15 V, which switches on shunt diodes D303 and D304. The previously forward biased diodes will now be reverse biased and vice-versa, hence a large amount of isolation will be provided. R333 and R334 are designed to terminate the microstripline when de-selected so that resonances are suppressed.

Dividers

IC301 divides the 1 - 2 GHz signal by two when selected by IC203D, TR303 and TR304, which close the switch consisting of 1/2 D301. IC203D is required to decode the control lines 1/2-1GHzX and SAMPLER DRIVE, because this divider is used in the 0.5 - 1 GHz band and also for production of the drive signal required by the sampling gate, which is used for YIG locking and frequency counting. R304, R337 and R338 form a 6 dB pad which ensures that the input level to the divider is within its limits. When these dividers have no input signal it is possible for self-oscillation to occur; this is prevented by TR304 and R304, which bias the input stage of the divider into a stable region when not in use.

IC302 divides the 1 - 2 GHz input signal by four when selected solely by the 250-500 MHz control line. Baluns T301 and T302 are used to convert the balanced ECL output of these dividers into a single ended output. The level of this output is approximately -8 dBm. The baluns are followed by microwave amplifiers running into compression to both raise and flatten the signal level as the output of the dividers reduces with increasing frequency. These amplifiers are switched off when not in use in order to reduce power consumption and heat generation.

Filters

The circuitry between D308 and D306 consists of two Chebyschev low-pass filters each terminated with a 10.5 dB pad. These filters form the path for signals between 500 MHz and 1 GHz, each used over half an octave. These filters are necessary in order to reduce harmonics of the chosen frequency. Similarly, the filters between D307 and D305 form the path for signals between 250 MHz and 500 MHz. However, the pads following these filters are only 9.5 dB as the output level of IC304 is lower than that of IC303.

IC203, 305 and associated circuitry provide decoding of the control lines and buffering to switch in the appropriate filter. The diodes at each end of the filter/attenuator constitute switches which are switched on/off together. The capacitors in series with the shunt arms of each pad are necessary for decoupling at RF since the DC control signal for the switches is injected here.

Mixer Band.

Circuit diagram: Fig. 7-12.

To generate signals between 10 MHz and 250 MHz, a down converter is used, which consists of a mixer and a beat frequency oscillator (BFO). A signal between 1.03 GHz and 1.27 GHz, supplied by the lower half octave VCO, is mixed with a fixed 1.28 GHz signal supplied by the BFO, to produce an IF signal between 10 MHz and 250 MHz. Filtering of this IF signal reduces unwanted spurious signals to acceptable levels.

Beat Frequency Oscillator

TR401 is the oscillator transistor tuned by the tank circuit consisting of L404, D401 and C403. This oscillator is similar to those described in 'VCOs', and functions in a similar fashion. The output level at TR401 collector is approximately +7 dBm. Unlike the VCOs, this oscillator is locked at a constant 1.28 GHz by a conventional phase locked loop resident on the Control board.

The loop filter consists of R418, C423 and C424 to give a loop bandwidth of approx. 10 kHz. A Zener diode D402 limits the tuning voltage to 12 V. This prevents the oscillator from oscillating much above 1.35 GHz, ensuring correct operation of the frequency divider in the phase locked loop on the Control board. A splitter consisting of R405 to R409 is used to provide the Control board with a small amount of the output - approximately -17 dBm. This is used to lock the BFO to the correct frequency. The major output of approximately -3 dBm is amplified by IC401 to provide the mixer X401 with approximately +8 dBm.

Down Converter.

The mixer X401 is used to down convert the 1.03 - 1.27 GHz input down to 10 - 250 MHz by mixing it with a fixed 1.28 GHz. The conversion loss of this process is approx. 8 dB. The source of the 1.03 - 1.27 GHz is the lower half octave VCO delivering approximately +2 dBm just before the -16 dB pad provided by R422-R424. TR412 and associated components form a 13.5 dB amplifier.

A 300 MHz low-pass filter immediately follows this amplifier to reduce spurious mixer products and breakthrough of mixer input signals. This is followed by another identical amplifier and filter to provide additional amplification and rejection. The final output of the down converter (10-250 MHz RF) goes to the attenuator and output amplifier. To reduce heat and power consumption, the BFO and down converter are only switched on when required. This is accomplished by TR409/410 etc., whenever the control signal 10-250 MHz is true.

Attenuator and Output Amplifier.

Circuit diagram: Fig. 7-10.

A voltage controlled attenuator is used before the amplifier in order to deliver the correct amount of power to the load. This attenuator provides typically 45 dB of range up to 2 GHz, and introduces less than -40 dBc of distortion at 10 MHz and -5 dBm.

The output amplifier is required to provide a substantial amount of gain and output power with low distortion. This amplifier's gain is typically 27 dB ±1 dB up to 2 GHz and distortion less than -30 dBc for output levels up to +15 dBm.

Input Selection

There are two inputs to the attenuator/amplifier; one is from the down converter (10-250 MHz RF) and the other is the combined outputs of the direct and divider bands (1/4-2 GHz RF). A PIN diode changeover switch (D206,207) is used to route the appropriate signal through to the attenuator and amplifier. IC204 is used as a comparator to level shift the output of IC203b, which represents 1/4-2 GHz valid, and to switch on the appropriate diodes which comprise this switch. The 10-250 MHz input has a 9 dB pad before the switch, which is required to terminate the filter in the down converter.

Voltage Controlled Attenuator

The attenuator uses PIN diodes D208 and D209 as current controlled variable resistors in a PI configuration. (The PI configuration exhibits much lower distortion and more range than a T configuration.) IC205 and IC206 etc. ensure that each PIN diode in the attenuator has the correct current and hence the correct RF resistance for any given input control voltage (LEVEL). The insertion loss of the attenuator at minimum attenuation is approximately 3 dB (flat) up to 1 GHz, increasing to 4 dB at 2 GHz.

Output Amplifier

In order to give the required gain and gain flatness to 2 GHz the amplifier consists of four gain stages. These four stages of gain are provided by IC202, TR202, TR204 and TR206. The gain of each of these stages is given below:

| 8 dB |

|---|

| 6 dB |

| 6 dB |

| 7 dB |

| 27 dB |

IC202 is a standard microwave amplifier, and the three transistor stages are standard feedback amplifier configurations. A 1 pF capacitor on the base of TR206 and a short/open circuit stub on the collector output line of TR206 help to improve the gain flatness at the top of the frequency range. The output of the amplifier is routed to the microwave chassis via SKF.

To reduce power dissipation, the amplifier is switched off when not in use. Transistors TR213, 201, 203, 205 are used to switch the individual stages on. IC203a,b,c is used to decode the control lines for each of the bands so that the amplifier can be switched on whenever any one of these control lines is true.

Sampler Drive Amplifier

Circuit diagram: Fig. 7-12.

This amplifier produces the necessary gain and output power for the drive signal between 500 MHz and 1 GHz as required by the sampling gate, which is used for locking YIGs and for frequency counting. The drive signal is derived from the divide-by-2 pre-scaler (Fig. 7-11). An input level of more than +10 dBm ensures that the first amplifier, IC501, is well into compression (gain > 10 dB, 1 dB gain compression level < 18 dBm).

The second stage, IC502, has only 8.5 dB gain typically and 23 dBm compressed output level. Again, this stage is well into compression. Resistors R508 and R509 form an inverted-L attenuator, which helps to match the output of IC502 to the input of the sampling gate and also ensures that the correct power level reaches the sampling gate.

To conserve energy and reduce heat, this amplifier is switched off when not used. TR501-503 are used to switch the amplifiers on and off as required by the SAMPLER DRIVE RF line, which carries both the RF signal and the DC control signal.

UHF Reference and Loop Filters

Circuit diagram: Fig. 7-9.

The UHF PLL (Phase Locked Loop) operates with a 3 MHz reference frequency; this is the highest easily-derived frequency which allows all frequencies above 1 GHz to be generated by the Fractional-N synthesizer. In sweep mode the loop bandwidth is about 50 kHz, for fast settling. In CW mode the loop bandwidth is about 2 kHz, to reduce fractional-N products.

Filters and Loop Bandwidth Switching

The phase comparator drives a switched current source, located on the Control board. When the loop is locked the current source output is a square wave: ±2.5-5 mA in sweep mode and ±250-500 µA in CW mode.

In sweep mode, the reference filter (bounded by C601 and C603) has 415 kHz bandwidth. The loop filter is formed by R603 and C604. In CW mode the VCO tuning signal also passes through the 8 kHz filter bounded by C605 and C608, and the loop filter comprising R604, C609 and C610. Two electrolytic capacitors, connected back-to-back, are used in case the tune line goes negative. Two inductors are used for each filter element, fitted back-to-back to minimise magnetic pick-up from the PSU and display. IC602b, IC602c and IC602d select or bypass the 8 kHz low-pass filter for low or high bandwidth respectively.

Force VCO Tune

The programmable divider on the Control board is not guaranteed to work for input frequencies above 2 GHz. Also, it can oscillate if it has no input signal. However the VCOs may stop oscillating if the tuning voltage is too low, and the 1.4 - 2 GHz VCO can oscillate above 2 GHz. Both of these conditions must be avoided or the loop may latch up and fail to lock.

To prevent this happening, the VCO varactor voltage is forced to a value in the middle of its range (about 10 V) for a short period every time a byte is written to the fractional-N ULA. This is done by IC601a and IC602a, and the period is set by IC603. For high bandwidth the pulse width is 10 µs and for low bandwidth it is 1 ms. The longer period is needed to charge C609 and C610.

Loop Gain Compensation

The PLL bandwidth is proportional to the VCO sensitivity and inversely proportional to the frequency. Over the half-octave tuning range the sensitivity of each oscillator reduces by about 1.4. Thus without any compensation the loop bandwidth at the top of each VCO band would be about half what it was at the bottom.

The nominal tuning voltage range for the VCOs is from 2 to 15 V. IC601b and its associated resistors produce -7.8 to -10.1 V for 2 to 15 V input. This is fed back to the tail of the switched current source (Control PCB, Sheet 7), varying its current output by a factor of two and hence maintaining a roughly constant loop bandwidth.

VCO Tuning Monitor

IC601c, etc. gives an output in the range 0 to +5 V for varactor voltages in the range 0 to +25 V. This is routed to the ADC on the Control board for diagnostic purposes.

CONTROL PCB

Introduction

The Control board performs the following functions:

- YIG tuning and bias switching.

- Output levelling in both synth. and YIG bands.

- Fractional-N division, locking and control of the UHF synthesizer.

- Locking the BFO.

- Sampler IF processing (amplification, ALC, filtering, switching, etc.).

- YTO locking.

- Frequency counting.

- Bi-directional interface with the digital board; decoding source control instructions, monitoring and reporting various voltages and status signals.

References to YIG oscillators and associated circuitry do not apply to the 6202B, since it does not contain any YIG oscillators. The functional blocks of the Control board are shown in Fig. 1-4.

YIG Tuning and Bias Switching

Circuit diagram: Fig. 7-52, 7-54, 7-59.

The YIG oscillators are current tuned. For the 2 - 8 GHz, 8 - 12 GHz and 12 - 20 GHz oscillators, the sensitivity is approximately 20 MHz/mA. For the 20 - 26.5 GHz YTO it is about 30 MHz/mA.

A P-channel/N-channel MOSFET pair is used as the output stage of the YTO driver. R207 is a current sense resistor; the transconductance of the driver is defined by R201, R205 and R207. Low temperature coefficient resistors are used to minimise tuning current variation with temperature. IC213 is a 16-bit DAC; thus the nominal tuning sensitivity is 1 LSB = 500 kHz below 20 GHz, and 750 kHz above 20 GHz.

C213 is connected across the YIG tuning coil (the CW filter) to reduce residual FM due to noise on the tuning current. It slows down the driver however, so it can only be used in CW mode or with very slow sweeps.

Component numbers in the following description refer to the 2 - 8 GHz driver; all drivers are identical. The driver is selected by IC203. When not selected, the tuning current is zero, due to R208. D204 and D205 limit the back e.m.f. when the driver is switched off. The 36 V Zener (D205) speeds up the collapse of tuning current, during retrace, etc.

A logic high at R210 turns on the CW filter. TR201 and TR202 act as a level shifter to provide gate bias to switch TR207 and TR208 on and off. D208 limits Vgs on TR207 and TR208.

All tuning currents are returned via the current sense resistor R207.

The circuitry round IC221 and TR220 provides a regulated -18 V supply for the YTO drivers. The drivers need a clean supply because of the tuning sensitivity of the YIGs; it should also be as high a voltage as is practical, as the current slew rate and hence the sweep speed, are limited by the available voltage and the tuning coil inductance.

In order for the YIG loop to lock, only one YTO at a time must be powered (the heaters are powered continuously to maintain the YIG temperature). The +15 V bias is switched by TR951-TR954. Quad comparator IC952 is used as a level shifter to derive gate bias voltage from the logic-level band select lines. The 2 - 8 GHz YTO also requires -5 V bias; this is supplied by IC951.

Output Levelling

Circuit diagram: Fig. 7-53, 7-54.

A simplified representation of the levelling loop circuitry is shown in Fig. 1-4. IC218 selects internal or external detector; either polarity of external input can be selected. IC219 and IC220 are connected as a differential amplifier with a gain of 19 and a high CMRR. This configuration is used in order to minimise residual AM at low power levels, when the detector voltage is very small.

IC220 output is compared with the output of the 16-bit level DAC IC214 to produce an error voltage, which is amplified by IC204. A small offset voltage is applied via R235. This ensures that the output of IC204 will be negative if the DAC voltage and detector voltage are zero, and therefore guarantees that a DAC code of zero will give maximum attenuation.

IC210 is an integrator with different switched gains, controlled by IC209. The settling time is determined by the loop bandwidth, which is the frequency at which the open-loop gain equals 1. There is considerable variation in maximum output power, even within each band, so the slower the loop settles, the more ripple there will be on fast sweeps. It is therefore important to keep the loop gain as high as possible. In general, settling is slowest at low output powers.

Normally C232 is not connected. Below 2 GHz R242 is selected. Above 2 GHz or with an external detector, R243 and R241 are selected (the FET TR104 is only present on later instruments). R243 is adjusted for the fastest settling consistent with loop stability. If a power meter is used for external levelling, it will have a much longer response time than a detector, so the overall loop bandwidth must be reduced to prevent instability. R240 and C232 are then selected.

In between points in a sweep, the input is disconnected from IC210 to hold the modulator setting until the frequency has almost settled. This is done by a logic high on the LEVEL HOLD input, which sets pin 9 of IC205 high. IC205 decodes the control lines which determine the levelling loop mode.

IC211 selects the appropriate modulator. In the YIG bands the modulator on the RF board is driven with +15 V via R249, which gives maximum attenuation. Below 2 GHz the input to IC216a is pulled negative by R247. This sets the microwave modulator to minimum attenuation, hence giving minimum distortion on the low frequency signals passing through it. When maximum attenuation is required (for AC detection, etc.), IC216a input is pulled positive by R248.

IC216b and its associated circuitry is used to compensate for the non-linearity of the microwave modulator, and hence to reduce the worst-case settling time. The P-N junction (IC222b) gives IC216b an exponential gain characteristic, which increases the gain as the input becomes more positive, ie. when more attenuation is required. IC222c, IC216c, etc. produce an offset which matches the voltage drop across IC222b.

The microwave modulator is current driven; this gives less non-linearity than voltage drive. IC216d is connected as a unity-gain differential amplifier to feed back the voltage developed across the sense resistor R290. This configuration enables a grounded load to be current driven.

The 'unlevelled' detector is a window detector. If IC210 output goes outside the range ±9.9 V, the output of IC212b goes high.

Fractional-N Synthesizer

Circuit diagram: Fig. 7-57, 7-58.

Fig. 1-5 is a block diagram of the fractional-N synthesizer. The system used provides fine frequency resolution without needing analogue correction or compromising the phase detector speed.

The 1 - 2 GHz input at SKK passes through a 6 dB pad, a buffer amplifier (IC509) and a 6 dB pad to provide reverse isolation, before reaching the pre-scaler, IC510. This, in conjunction with buffering on the RF board, ensures that sub-harmonics, etc. generated by IC510 are kept below -60 dBc on the output signal. IC510 divides the input frequency by four, since IC511 is only specified to 500 MHz.

IC502 and IC503 are connected to form a 5-bit programmable counter (/N1), and IC504 is a 3-bit programmable counter (/N2). N1 and N2 are set by the fractional-N controller ULA, IC501. R502-509, R511 and R512 convert the CMOS output levels from IC501 to the ECL voltages needed for the load inputs of IC502-504.

At the start of a count, IC511 divides by 9. When IC504 reaches terminal count, it disables itself and sets IC511 to divide by 8. The count continues until IC502 and IC503 reach terminal count, at which point the new values of N1 and N2 are loaded via IC505d. The overall division ratio is therefore 4(8N1 + N2). The terminal count of IC502 and IC503 also clocks the phase comparator input IC507 pin 11, via the level shifter formed by TR501, TR502, etc. When the new value of N1 is loaded, IC501 is clocked via IC505b, IC505c, TR503 and TR504 to output the next values of N1 and N2.

Fig. 1-5 Fractional-N Synthesizer

IC506a, IC507b and IC508 form a 4-state phase comparator which is run at 3 MHz. The synthesizer produces fractional-N related phase noise which increases in amplitude with increasing offset from the carrier, and whose spectrum is proportional to the loop reference frequency. It is removed by means of a low-pass filter on the VCO TUNE line. The higher the reference frequency, the higher the loop bandwidth can be made (giving faster settling) without incurring significant fractional-N products. 3 MHz is the highest simple frequency which gives full coverage of the 1 - 2 GHz range with the divider configuration used.

The circuitry comprising IC506b, IC507a and TR505 forms a lock detector. If more than π radians of phase error accumulates, TR505 is switched on.

TR506, TR507, TR508 and their associated components act as a symmetrical current source/sink, which is switched by the complementary phase detector outputs. IC512 switches the magnitude of the sourced/sunk current, and hence the loop gain, by a factor of 10. A negative voltage derived from the VCO tuning voltage is fed back at PLB pin 8. This causes the output current to increase with increasing VCO voltage, and helps to compensate for the effect on loop bandwidth of divider ratio and variation in VCO sensitivity. For 5 - 15 V tuning voltage, the current is ±(250 - 500) µA or ±(2. 5- 5) mA. The switched-current output is filtered on the RF board to derive the VCO tuning voltage.

The loop gain switching, combined with further gain and filter switching on the RF board, gives a loop bandwidth of either 1 - 2 kHz or about 50 kHz. Low loop bandwidth is used in CW mode to give reasonable phase noise. In swept mode, high loop bandwidth is selected to give fast settling (within 100 kHz in 250 µs at all frequencies up to 26.5 GHz).

BFO Phase-Locked Loop

Circuit diagram: Fig. 7-53.

The BFO is a VCO on the RF board, which is locked to 1.28 GHz by circuitry on the Control board. The RF input frequency at SKL is divided by 64 by IC401, to give 20 MHz. When the BFO is turned off, the input to IC401 is biased via D401 to prevent self-oscillation. TR401 and TR402 convert the differential ECL output from IC401 to a CMOS compatible level. IC402a divides the 20 MHz by two.

IC403 and IC404 form a 4-state phase comparator which is run at 10 MHz. When the BFO is locked, IC404 pin 6 and IC404 pin 8 give complementary 10 MHz outputs, whose mark/space ratio depends on the phase relationship between the two inputs to the phase comparator. The circuitry comprising IC405 and TR406 forms a lock detector, which gives a logic high output if more than π radians of phase error is accumulated.

TR403-405 and their associated components act as a switched current source/sink, giving +3 mA output at SKM. This is filtered on the RF board to derive the BFO tuning voltage. The loop bandwidth is about 10 kHz, which gives the best compromise between VCO noise and divider noise.

When the BFO is turned off, TR403 base is pulled low via D401, forcing the tuning voltage down to 3 V. This ensures that when the BFO is turned on, it starts oscillating at a low frequency. This prevents the latch-up which could otherwise occur, as IC401 is only guaranteed to work up to 1.3 GHz.

Sampler IF Amplifier and Filters

Circuit diagram: Fig. 7-60.

The sampling gate is used in source mode above 2 GHz and also in frequency counter mode. In source mode the SAMPLER IF signal clocks the input divider in the YIG PLL. In counter mode, LO frequencies in the range 0.5 - 1 GHz are used to produce an IF frequency of about 100 MHz, and the software performs cross checks to eliminate errors. Input frequencies below 400 MHz are counted directly, with the LO set to 1 GHz. The sampler includes an IF amplifier stage which requires bias current; this is provided via R701 and R702.

C703, L701, C704, L702 and C705 form a 410 MHz low-pass filter which rejects LO breakthrough, and images (>600 MHz) when in direct count mode. LO filtering is needed at the input because the LO level may be higher than the wanted signal. Without an input filter the following ALC amplifier could therefore level on the LO rather than the IF.

For the frequency counter the IF input level may be anywhere in the range -50 to 0 dBm. The IF amplifier must therefore have sufficient gain and a wide dynamic range. The amplifier used has wide-range automatic level control, and comprises IC701-703 and associated components. The overall gain is about 60 dB at 410 MHz and higher at lower frequencies. (The amplifier bandwidth must be at least 410 MHz, but in IF count mode image frequencies can fall within this band. A limiter cannot therefore be used at this stage as it would generate in-band intermodulation products which would affect counter operation.)

D703, R716 and C717 form a peak detector. The levelling loop is completed by IC704 and PIN modulators D701 and D702. The levelled output is between +5 and +10 dBm over the range 10 - 400 MHz.

IC706d provides an IF level monitor output to the ADC. This is used in counter mode when the software is trying to determine whether it has got any input signal to count. If there is no input the amplifier will be at maximum gain and the monitor output voltage will be about 4.5 V. As the input level is increased the amplifier gain, and hence the IF monitor voltage, will be reduced.

In direct count mode the IF bandwidth must be at least 400 MHz. In YIG lock mode and most of the time in counter mode, further filtering is needed to reject images generated by LO frequencies down to 500 MHz. This is provided by the 280 MHz low-pass filter comprising C724-726, L703 and L704, and the path switching for the counter is done by D704 and D705, driven by IC706a and IC706c.

C728-732 and L705-708 form a 66 - 256 MHz band-pass filter. The level out of the filter is compared with a fixed threshold voltage by D707, D708, IC706b, etc. As the IF is levelled, the comparator acts as a frequency window detector and gives a logic high output if the IF frequency is in the range 65 - 265 MHz. This is used in counter mode to aid IF acquisition. The YTO phase-locked loop IF input (YIG PLL IF) is taken from after the band-pass filter via a 6 dB pad.

The signal to be counted passes from D705 via a 3 dB pad to IC705. The filtered path between D704 and D705 has about 8 dB more loss than the "straight through" path. As the counter's front end has only a 6 dB guaranteed operating window, more gain and level control are needed. By this time, non-harmonically related frequencies (LO and image) should have been sufficiently attenuated, so a limiter can be used. IC705/D706 acts as the limiting amplifier.

IC701-703 and IC705 are turned off by TR701 and TR702 when the sampler is not in use, to reduce heat generation and spurious products.

YTO Phase-Locked Loop

Circuit diagram: Fig. 7-59.

Fig. 1-6 shows the overall operation of the YTO PLL. The selected oscillator is tuned to the nominal required frequency using the tuning coil and pulled to the exact frequency by means of the FM coil.

The YTO output frequency is fed via a coupler into the sampler, which generates sum and difference products of the YIG frequency and all harmonics of the LO frequency. The LO frequency, fL, is in the range 600 - 800 MHz. After being amplified and filtered, the IF is divided by 64 and compared with a 2 MHz reference. The loop locks when the YTO frequency = NfL + 128 MHz.

The phase comparator output passes through the reference filter and loop filter to the FM drive amplifier. The multiplying DAC compensates for the difference in FM sensitivity between YTOs to maintain a constant loop bandwidth.

IC601 divides the IF frequency by 64. R601 biases its input to prevent self-oscillation when there is no input signal. TR601 and TR602 convert the differential ECL output to CMOS compatible levels.

IC602 and IC603, together with R610-614 and C606, form a 4-state phase comparator which is run at 2 MHz. Incorporating the outputs from IC602 pin 6 and IC602 pin 9 gives the phase comparator a linear range of ±3π radians and increases the loop's slew rate by a factor of about two.

IC606b, IC607b, IC607a, etc. act as a window detector which detects when the loop is out of lock. When it is in lock, the integrator input voltage is zero. If the loop fails to lock, this voltage will be in the range ±(0.7 - 2.1) V. The lock detector gives a logic high output if its input voltage is outside the range -0.27/+0.2 V.

C608, L601, L602 and C609 form a 400 kHz reference filter. The loop filter comprises IC606a and its associated components. In normal operation the YIG PLL has about 50 kHz loop bandwidth and 13 kHz integrator break frequency. The software sets the required loop bandwidth by adjusting the digital inputs of the multiplying DAC, IC608, to give an FM sensitivity of 4 MHz/V at its Vref input. IC606c and the associated resistors provide an FM drive monitor signal which is used during YTO frequency calibration and FM sensitivity calibration.

YIG FM sensitivity calibration is performed with lower loop bandwidth to ensure loop stability, so the integrator break frequency is reduced to 4.6 kHz by switching in C610.

At band changes and when changing frequency in CW mode, the FM drive is momentarily set to zero to stop the loop latching up. This is done by shorting the integrator feedback network via IC605b.

In between successive frequency points in a sweep, the FM drive is held constant for about 140 µs by opening IC605c and IC605d. The integrator is left holding the voltage on C611. This allows the YTO and the UHF synthesizer to settle before the loop is closed, and hence reduces the loop slewing time (assuming very little difference in YIG cal error between successive points). The time constant is produced by IC604a, which is triggered by writing to the YIG frequency DAC.

In AC detection mode the FM drive is also held during the "power off" periods, by means of the FM HOLD signal which is set by software.

The FM drive amplifier consists of IC608, IC606d and IC609. The digital inputs of multiplying DAC IC608 set the amplifier's gain. The DAC has current output and therefore needs an op amp to follow it. IC609 is a high-power unity-gain buffer and is included within the DAC feedback loop. The YTO FM coils are connected in series, and the voltage across current-sensing resistors R630 and R631 is fed back to the DAC. D602 and D603 limit the output current to ±150 mA.

Fig. 1-6 YTO Phase-Locked Loop

0

C

E

Frequency Counter

Circuit diagram: Fig. 7-55.

The counter section of the board is required to count frequencies in the range 10 - 400 MHz. It consists of a counter with serial input and parallel output, and a gate timer which sets the duration of the count.

The gate timer is a 24-bit programmable counter comprising IC101-103. The gate time is loaded as an LS word and an MS byte. The timer is clocked at 1 MHz, which gives a maximum possible gate time of 16.7 s. As the longest gate time set is 1 s, the top four bits are not used.

The timer is started by a rising edge on IC105 pin 3, which causes IC105 pin 5 to go low. On the next rising edge of the 1 MHz clock, IC104 pin 6 goes low, enabling IC103 and IC107 to start counting and setting IC105 pin 5 high again. When the timer reaches terminal count, IC104 pin 9 goes high on the next falling edge of the 1 MHz clock, and on the next rising edge IC104 pin 6 goes high, disabling IC103 and IC107. The actual gate time is therefore 1 µs longer than the value loaded into IC101-103.

The gate timer control as described above is needed to de-glitch the terminal count output of IC101, and also to minimise the skew between delays in opening and closing the gate, which could cause significant inaccuracy when counting 400 MHz.

The counter proper consists of a 4-bit BCD counter (IC107) and a 28-bit binary counter (IC108, IC110-112). The carry output of IC107 is used to clock IC108, and IC105(b) pin 9 clocks IC110-112, which are connected as a 24-bit synchronous counter. Diode D105 is used as an OR gate. The outputs of IC107 and IC108 are output to the data bus by tri-state buffer IC109. IC110-112 incorporate tri-state output registers. The count value is read as two 16-bit words. After it has been read, the counter is cleared by setting the TRIGGER/RESET line low again.

Apart from the inhibit input, all IC107's inputs and outputs are level shifted to interface with CMOS logic. TR101 and TR102 provide the fast interface needed to clock IC108 at up to 40 MHz. Speed is not important for the other outputs.

The actual count sequence output to the data bus for the LS nibble looks like this:

| Count | Output | ||

|---|---|---|---|

| 0 | 1000 (8) | ||

| 1 | 1001 (9) | ||

| 2 | 1010 (10) | ||

| 3 | 1011 (11) | ||

| 4 | 0100 (4) | ||

| 5 | 0101 (5) | ||

| 6 | 0110 (6) | ||

| 7 | 0111 (7) | ||

| 8 | 0000 (0) | ||

| 9 | 0001 (1) | ||

IC108 is clocked on the count of 4, i.e. 6 counts too early, but since all codes in the sequence are unique, the software is able to determine the correct frequency count.

Digital Board Interface

Circuit diagram: Fig. 7-56.

The interface with the Digital board is via PLA, and consists of a 16-bit bi-directional data bus (SD0-SD15), an 8-bit address bus (SAD0-SAD7), write and read strobes (SWR and SRD) and a synthesizer select line (SSEL). SWR, SRD and SSEL are active low. SD0 - SD15 and SAD0 - SAD7 correspond to D16 - D31 and A2 - A9 respectively, on the Digital board. There is also a 1 MHz reference output from the synthesizer; all the other clocks in the instrument are locked back to it. The software interface is as follows:

SAD7 and SAD6 define the general type of write or read operation.

| 0000XXXX | Write to synth tray (except frac-N ULA) |

|---|---|

| 01XXXXXX | Write to frac-N ULA |

| 100000XX | Read from synth tray (except ADC) |

| 11000000 | Read ADC |

Note...

C

Unless otherwise stated, data is +ve logic, i.e. 1 = true.

WRITE OPERATIONS

| Address | Function | Remarks | ||

|---|---|---|---|---|

| 00H | YIG frequency |

16 bits.

Scale: |

LSB SD0

2 - 20 GHz LSB = 500 kHz 20 - 26.5 GHz LSB = 750 k |

nominal

Hz nominal |

| 01H | level | 16 bits. LS | B SD0 | |

| 02H | mode byte 1 |

8 bits

SD0-SD2 SD3 SD4 SD5 SD6 SD7 |

timebase control

int/ext detector +ve/-ve detector detector/power meter counter reset/trigger YIG loop break freq |

0 = int

0 = +ve 0 = detector 0 = reset 0 = high |

| break freq | ||||

| Timebase co | ontrol codes: | |||

| 000 | OCXO internal standard |

001

010

011

100

101

110

111

1 MHz external standard

10 MHz external standard

MTS standard cal

MTS internal standard (VCXO) (not used in 6200B)

not used

not used

not used

| 03H | mode byte 2 |

6 bits

SD0 SD1 SD2 SD3 SD4 SD5 |

CW filter

UHF loop bandwidth max attenuation level hold FM hold FM zero |

1 =

1 = 1 = 1 = 1 = |

filter on

low BW max atten level held FM held FM zeroed |

|

|---|---|---|---|---|---|---|

| 04H | band select |

14 bits

SD0 SD1 SD2 SD3 SD4 SD5 SD6 SD7 SD8 SD9 SD10 SD11 SD12 SD13 |

10 - 250 MHz

250 - 500 MHz 0.5 - 1 GHz 1 - 2 GHz sampler drive 2 - 8 GHz 8 - 12 GHz 12 - 20 GHz 20 - 26.5 GHz 20 - 26.5 GHz lower 1/2 octave upper 1/2 octave direct count count/YIG lock |

|||

| 05H | FM gain | 8 bits. LSB | SD0. | |||

| 06H |

counter gate time

(LS word) |

16 bits. LSB SD0.

LSB = 1 μs |

Ì |

Set gate time to

required time - 1 μs |

||

| 07H |

counter gate time

(MS byte) |

8 bits. LSB SD0

LSB = 1 µs × 2 16 |

||||

| 08H |

freq std tune

(coarse byte) |

8 bits. LSB SD0 | ||||

| 18H |

freq std tune

(fine byte) |

8 bits. LSB SD0 | ||||

FRAC-N ULA

| Address | Function | Remarks |

|---|---|---|

| 40H-7FH | all ULA functions |

8 bits. LSB SD0

All ULA functions can be set by software. |

READ OPERATIONS

| Address | Function | Remarks | |

|---|---|---|---|

| 80H |

freq counter

(LS word) |

16 bits. LSI | B SD0 |

| 81H |

freq counter

(MS word) |

16 bits. LSI | B SD0 |

| 82H | status | 10 bits | |

| SD0 | unlevelled | ||

| SD1 | UHF out of lock | ||

| SD2 | YIG out of lock | ||

| SD3 | not used | ||

| SD4 | BFO out of lock | ||

| SD5 | freq std out of lock | ||

| SD6 | no std. | ||

| SD7 | timebase phase detector output | ||

| 1 = int std freq high | |||

| SD8 | freq counter IF valid | ||

| SD9 | count finished. Goes to 0 <1 µs after | ||

| counter trigger (mode byte 1) |

ADC

Address C016

Sequence:

- 1. Write cycle to load MUX code

- 2. Dummy read cycle to start conversion

- 3. Wait >2.5 μs

- 4. Read cycle to read ADC

MUX codes:

3 bits. SD0-SD2

- 000 not used

- 001 VCO tuning voltage

- 010 YIG FM drive

- 011 freq. counter IF level

- 100 not used

- 101 VCXO tuning voltage

- 110 not used

- 111 not used