Page 1

CIRCUITOS DIGITALES

UTILIZANDO VHDL

SÍNTESIS Y DESCRIPCIÓN DE

IEC FRANCISCO J AVIER T ORRES V ALLE

2001

Page 2

SINTESIS Y DESCRIPCIÓN DE CIRCUITOS DIGITALES UTILIZANDO VHDL

ANTECEDENTES

En los últimos diez años la industria

electrónica ha tenido una gran evolución en el

desarrollo de sistemas digitales; desde

computadoras personales, sistemas de audio y

vídeo hasta dispositivos de alta velocidad para las

comunicaciones. Productos hechos con una alta

tecnología que permite aumentar la funcionalidad,

disminuir costos, mejorar el aprovechamiento de

la energía, así como una marcada tendencia hacia

la miniaturización. Esto ha sido posible gracias a

la implementación de herramientas de diseño

asistidos por computadora, conocidas como

herramientas CAD (Computer Aided Design),

aunque específicamente se hace uso de

herramientas EDA (Electronic Design

Automation), que es el nombre que se le da a

todas las herramientas CAD para el diseño de

sistemas electrónicos. Este software de diseño

electrónico que facilita a los ingenieros el

desarrollo de circuitos es cada vez mas sofisticado

y, además, contamos con computadoras cada vez

más veloces y de mayor capacidad de

procesamiento. Ambos, hardware y software,

constituyen actualmente herramientas muy

importantes que simplifican el trabajo de diseño

electrónico. Además de facilitar el trabajo, el uso

de herramientas EDA también aceleró los

procesos de diseño. Esta situación condujo a

adoptar nuevas metodologías para el diseño y

evaluación de los circuitos electrónicos. El uso de

las herramientas EDA junto con los dispositivos

lógicos programables, que pueden ser utilizados

en diferentes aplicaciones e inclusive

reprogramados, cambiaron bastante el concepto

de diseño de circuitos digitales.

VHDL es un lenguaje que se creó para el

diseño, modelado y documentación de circuitos

complejos. Actualmente se le utiliza para la

síntesis de circuitos digitales utilizando

dispositivos lógicos programables. Es así como

los dispositivos lógicos programables y VHDL,

Very High Speed Integrated Circuit (VHSIC)

Hardware Description Language, constituyen los

elementos fundamentales para estas nuevas

metodologías de diseño.

El presente trabajo considera los dispositivos

lógicos programables, enfocándonos en los PLDs,

CPLDs y FPGAs. Ya que el principal motivo por

el que debemos aprender a utilizar VHDL es el de

diseñar circuitos lógicos utilizando este tipo de

dispositivos. Se expondrán los estilos elementales

de codificación, exponiendo las principales

características de VHDL como lenguaje para

síntesis de circuitos. Finalmente se desarrolla la

implementación de filtros digitales utilizando

FPGAs.

i

IEC FRANCISCO JAVIER TORRES VALLE

Page 3

SINTESIS Y DESCRIPCIÓN DE CIRCUITOS DIGITALES UTILIZANDO VHDL

ÍNDICE

ANTECEDENTES

1. LENGUAJES DE DESCRIPCIÓN DE HARDWARE 1

1.1. INTRODUCCIÓN. 2

1.2. EL CONCEPTO DE HERRAMIENTAS CAD-EDA. 2

1.3. LENGUAJES DE DESCRIPCIÓN DE HARDWARE. 4

1.3.1. VENTAJAS DE LOS HDLS 5

1.4. VHDL 5

1.5. METODOLOGÍA DE DISEÑO UTILIZANDO VHDL 6

2. DISPOSITIVOS LÓGICOS PROGRAMABLES 9

2.1. CONCEPTOS FUNDAMENTALES 10

2.2. DISPOSITIVOS LÓGICOS PROGRAMABLES 10

2.2.1. MATRIZ GENÉRICA PROGRAMABLE 10

2.3. COMPLEX PROGRAMMABLE LOGIC DEVICES 11

2.3.1. MATRIZ DE INTERCONEXIONES PROGRAMABLES 11

2.3.2. BLOQUES LÓGICOS 11

i

2.3.3. DISTRIBUCIÓN DE PRODUCTOS 12

2.3.4. MACROCELDAS 12

2.3.5. CELDA DE ENTRADA/SALIDA 13

2.4. FIELD PROGRAMMABLE LOGIC DEVICES 13

2.4.1. CELDAS LÓGICAS 14

3. SINTAXIS DEL LENGUAJE 17

3.1. INTRODUCCIÓN A LA DESCRIPCIÓN EN VHDL DE CIRCUITOS

18

DIGITALES

3.1.1. MULTIPLEXORES 18

3.1.2. COMPARADORES 19

3.1.3. EL ESTILO DE “PROGRAMACIÓN” EN VHDL 20

3.2. IDENTIFICADORES 21

3.3. OBJETOS DE DATOS 21

3.3.1. CONSTANTES 21

ii

IEC FRANCISCO JAVIER TORRES VALLE

Page 4

SINTESIS Y DESCRIPCIÓN DE CIRCUITOS DIGITALES UTILIZANDO VHDL

3.3.2. VARIABLES 22

3.3.3. SEÑALES 22

3.3.4. ALIAS 22

3.4. TIPOS DE DATOS 22

3.4.1. TIPOS ESCALARES 22

3.4.2. TIPOS COMPUESTOS 25

3.4.3. SUBTIPOS 27

3.4.4. TIPOS PREDEFINIDOS EN VHDL 27

3.4.5. TIPOS NO SOPORTADOS EN VHDL PARA SÍNTESIS 27

3.5. OPERADORES 28

3.5.1. OPERADORES LÓGICOS 28

3.5.2. OPERADORES DE COMPARACIÓN 28

3.5.3. OPERADORES DE ADICIÓN 28

3.5.4. OPERADORES DE MULTIPLICACIÓN 29

3.5.5. OPERADORES MISCELÁNEOS 29

3.5.6. OPERADORES DE ASIGNACIÓN 29

3.5.7. OPERADORES DE ASOCIACIÓN 30

3.5.8. OPERADORES DE CORRIMIENTO 31

3.5.9. OPERACIONES CON VECTORES 31

3.6. ATRIBUTOS 32

3.7. ENTIDADES 32

3.7.1. GENÉRICOS 33

3.7.2. PUERTOS 33

3.7.3. MODOS 33

3.8. ARQUITECTURAS 34

3.9. DESCRIPCIONES DE FLUJO DE DATOS 34

3.9.1. INSTRUCCIONES CONCURRENTES 35

3.9.2. ESTRUCTURAS DE EJECUCIÓN CONCURRENTE 35

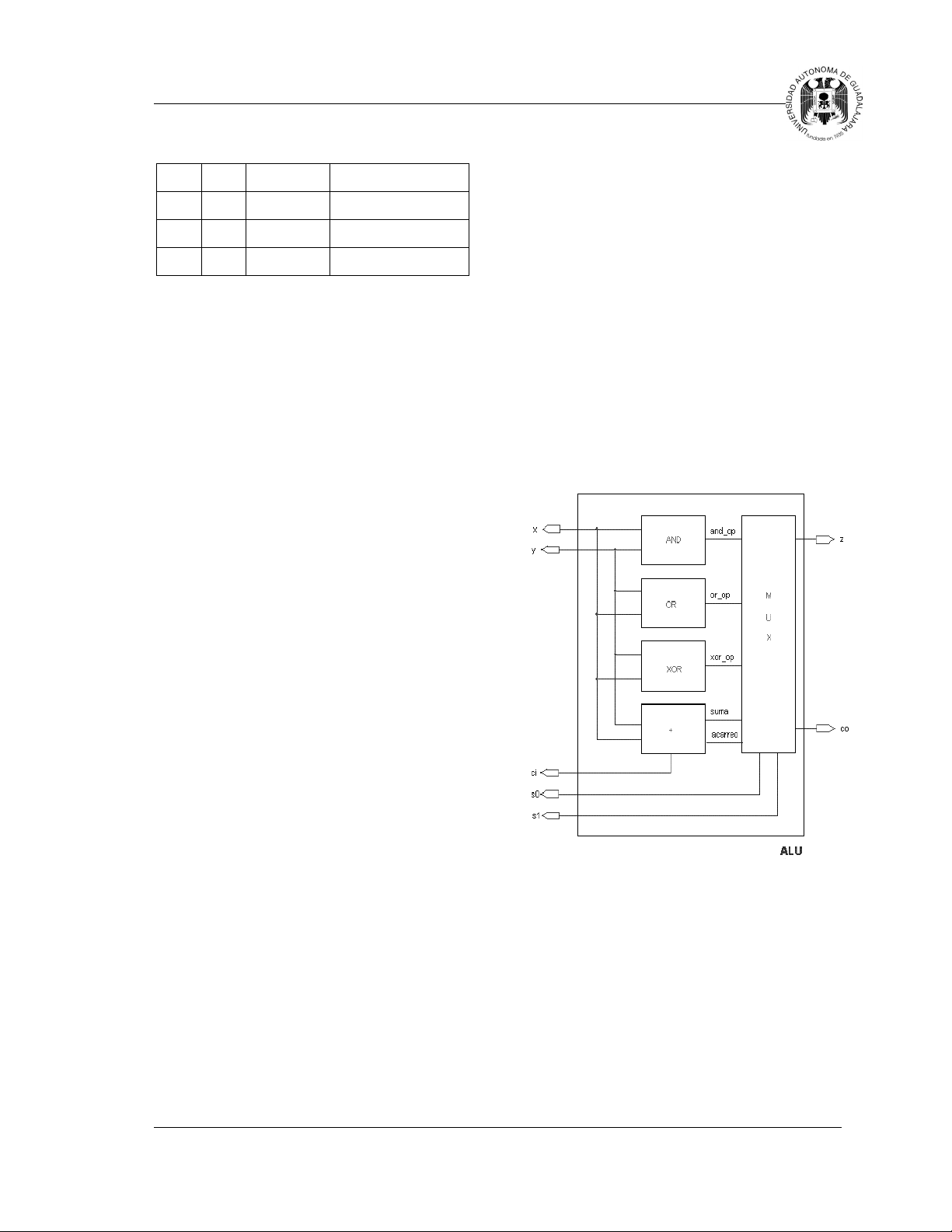

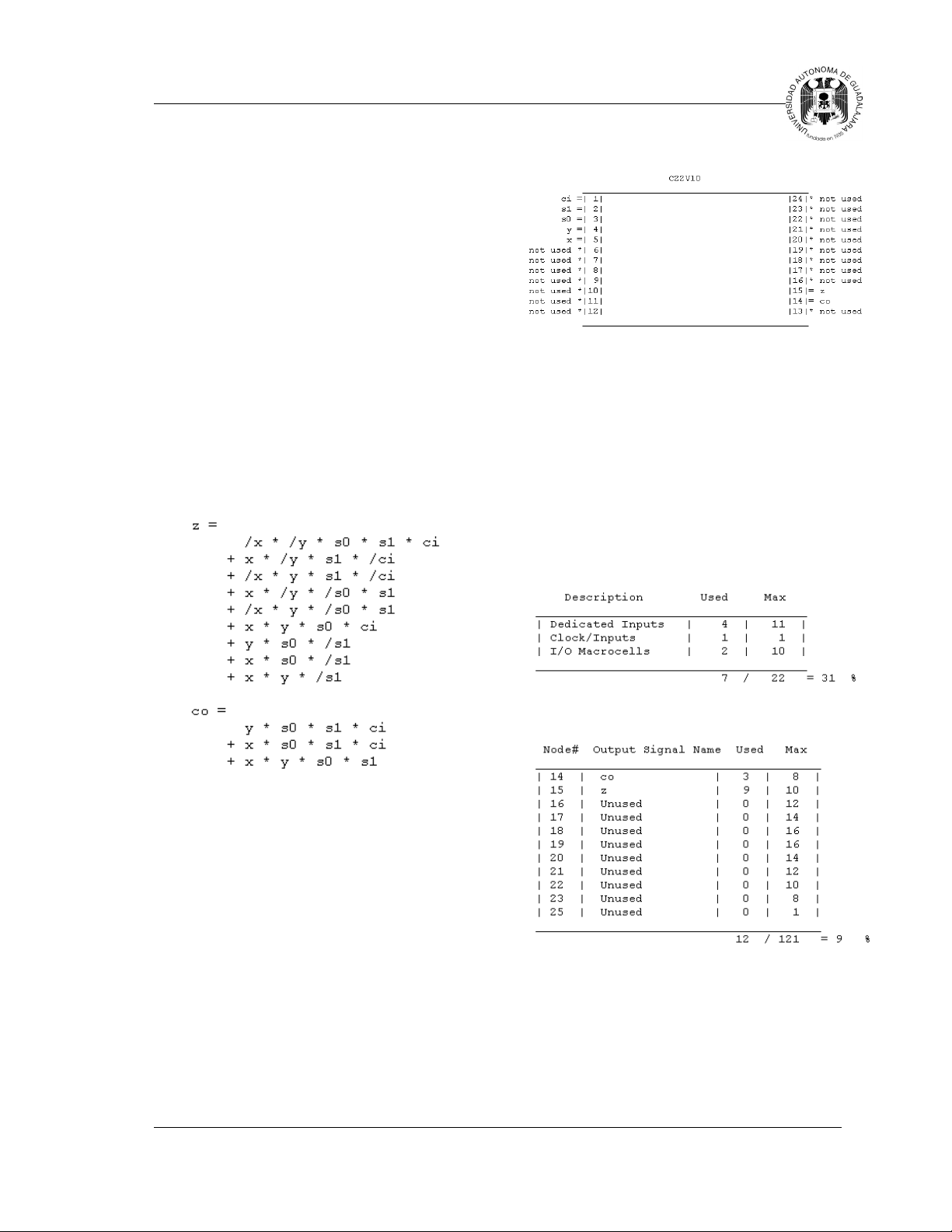

3.9.3. ALU 35

3.10. DESCRIPCIONES COMPORTAMENTALES 38

3.10.1. INSTRUCCIONES SECUENCIALES 38

3.10.2. PROCESOS 38

3.10.3. DIFERENCIAS ENTRE SEÑALES Y VARIABLES 39

3.10.4. ESTRUCTURAS DE EJECUCIÓN SECUENCIAL 40

3.11. DESCRIPCIONES ESTRUCTURALES 42

iii

IEC FRANCISCO JAVIER TORRES VALLE

Page 5

SINTESIS Y DESCRIPCIÓN DE CIRCUITOS DIGITALES UTILIZANDO VHDL

3.11.1. COMPONENTES 42

3.11.2. INSTANCIACIÓN DE COMPONENTES 43

3.11.3. SENTENCIAS DE GENERACIÓN 44

3.12. SUBPROGRAMAS 47

3.12.1. PROCEDIMIENTOS 47

3.12.2. FUNCIONES 47

3.12.3. LLAMADO A SUBPROGRAMAS 48

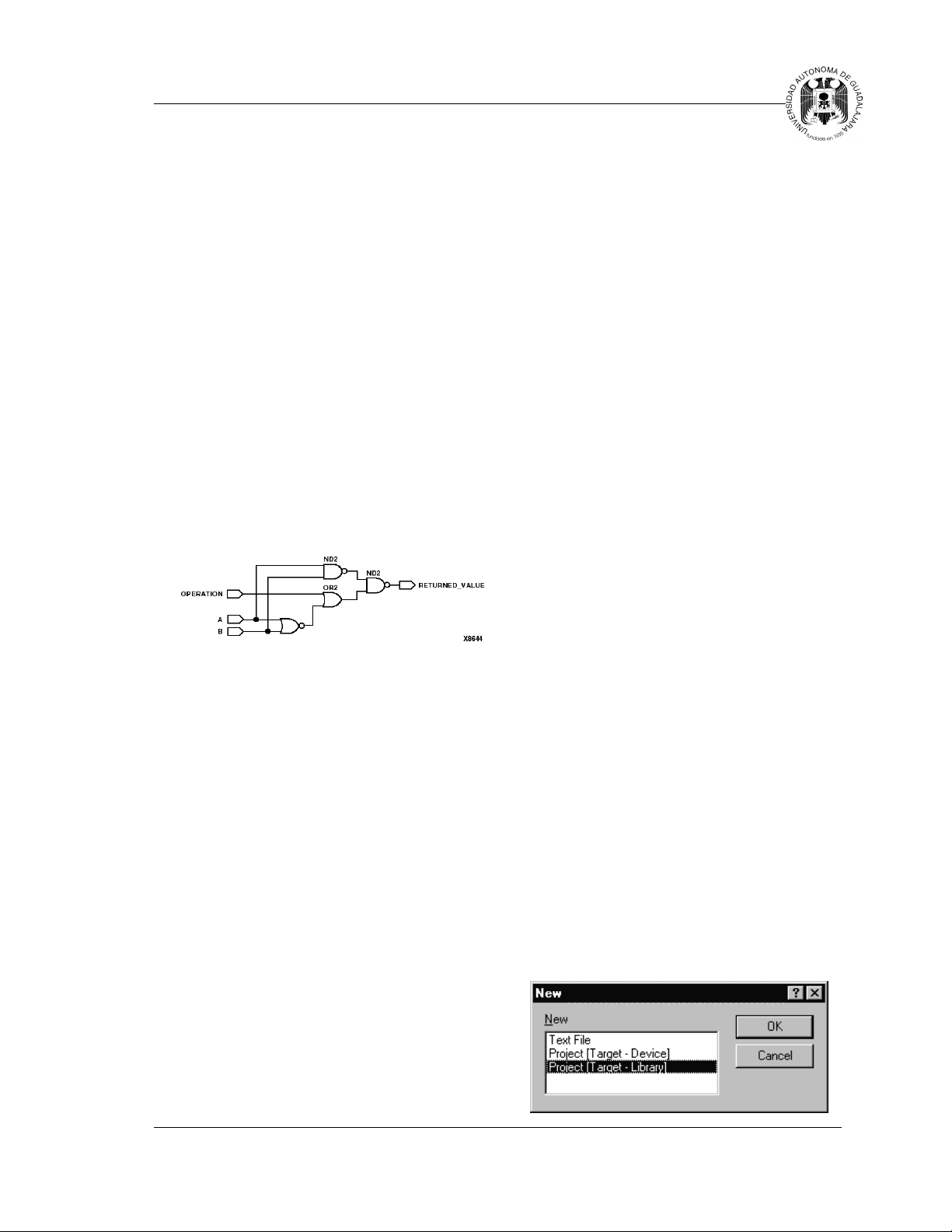

3.12.4. SOBRECARGA DE OPERADORES 50

3.13. LIBRERÍAS 50

3.13.1. SÍNTESIS DE LIBRERÍAS EN WARP 50

3.13.2. PAQUETES 52

4. DESCRIPCIÓN DE CIRCUITOS DIGITALES 54

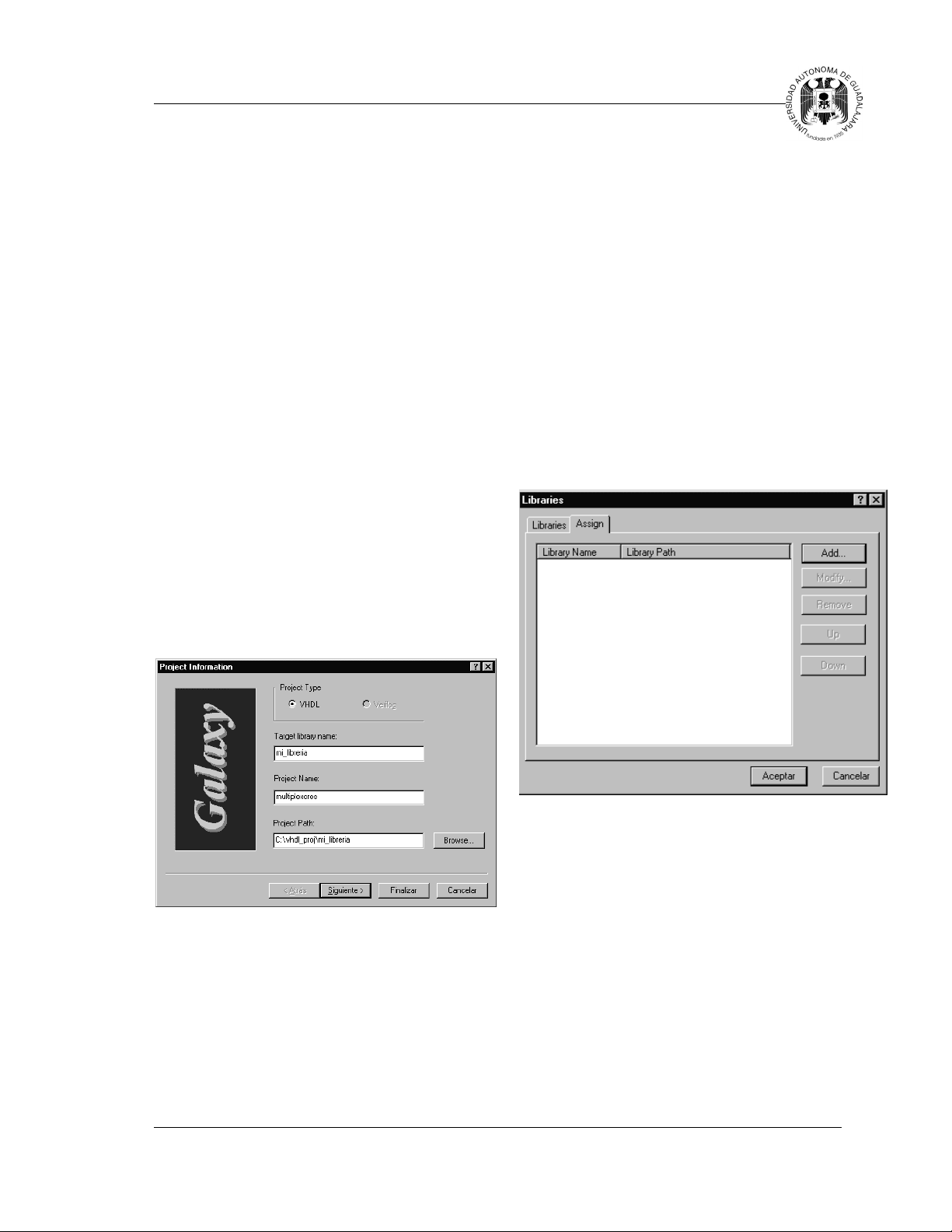

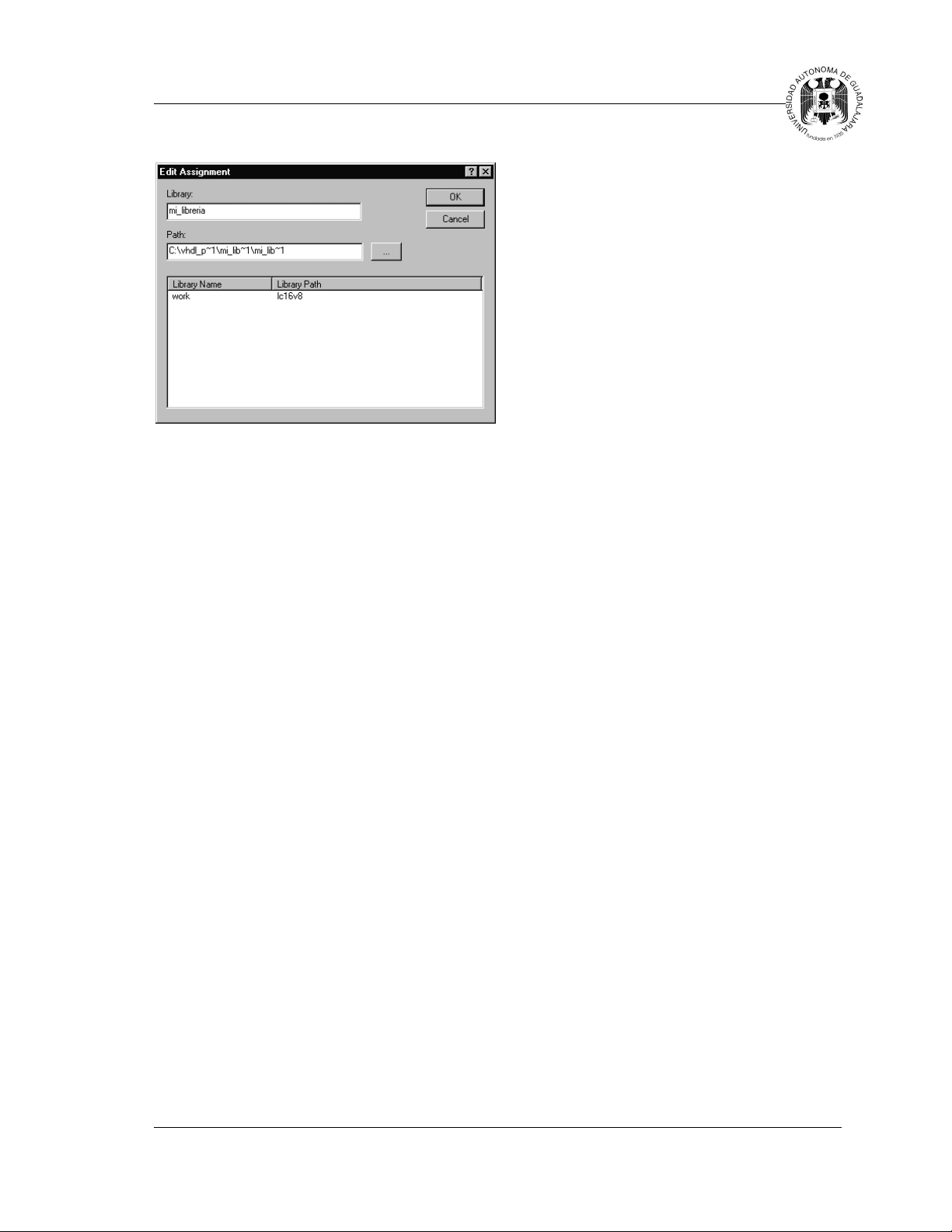

4.1. PROYECTOS EN WARP 5.0 55

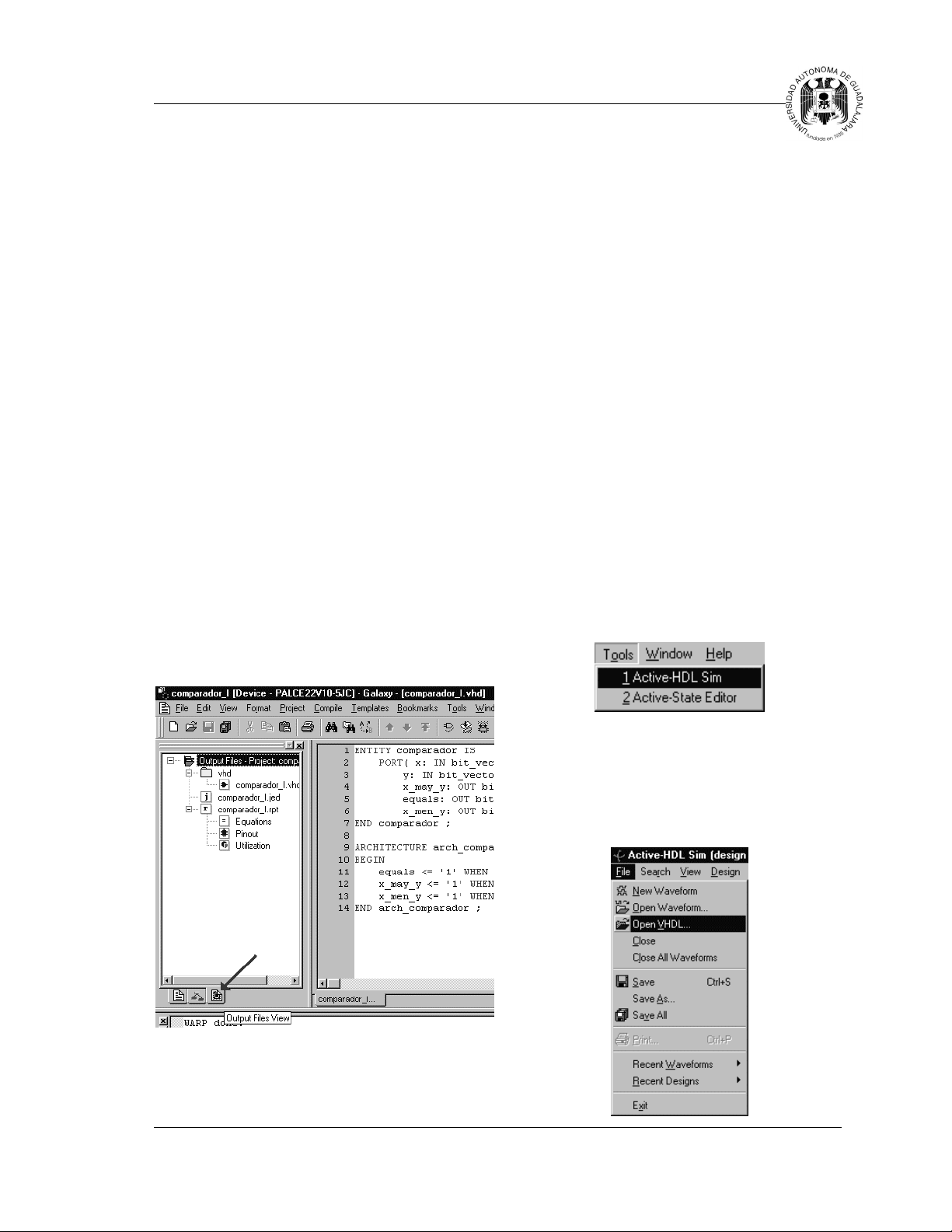

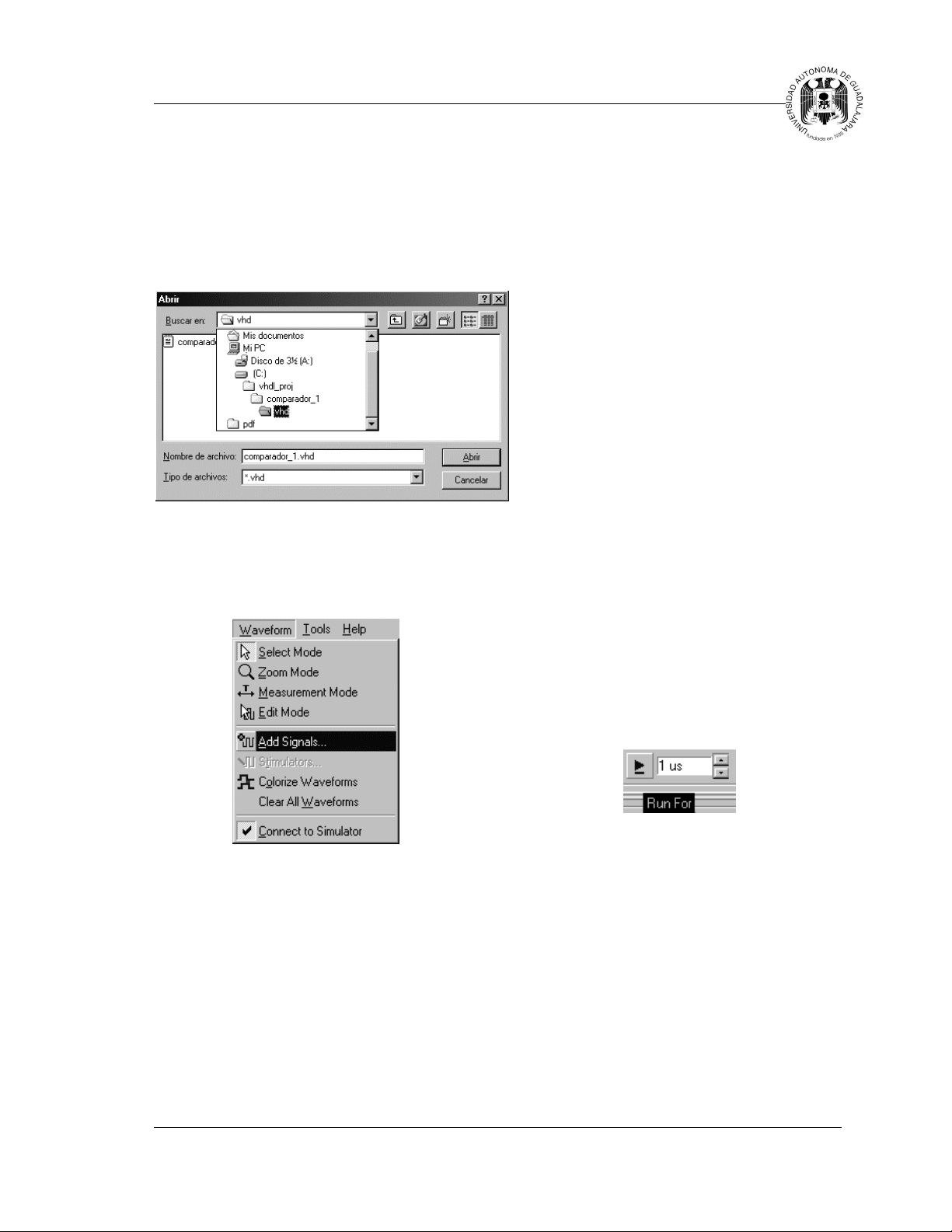

4.2. SIMULACIÓN DE PROYECTOS 57

4.2.1. PROCESO DE SIMULACIÓN 57

4.3. COMPARADORES 60

4.4. MULTIPLEXORES 65

4.4.1. DESCRIPCIÓN DE FLUJO DE DATOS 65

4.4.2. DESCRIPCIÓN COMPORTAMENTAL 66

4.4.3. DESCRIPCIÓN ESTRUCTURAL 67

4.5. SUMADORES 68

4.5.1. SUMADOR TOTAL 68

4.5.2. SUMADOR DE CUATRO BITS 69

4.5.3. SYNTHESIS OFF 70

4.6. REGISTROS 71

4.7. CONTADORES 73

4.8. ALU DE CUATRO BITS 76

4.8.1. DESCRIPCIÓN ESTRUCTURAL 77

4.8.2. DESCRIPCIÓN COMPORTAMENTAL 78

4.9. MÁQUINAS DE ESTADO 79

5. IMPLEMENTACIÓN DE FILTROS DIGITALES EN FPGA'S 83

5.1. INTRODUCCIÓN 84

5.2. ANTECEDENTES 84

iv

IEC FRANCISCO JAVIER TORRES VALLE

Page 6

SINTESIS Y DESCRIPCIÓN DE CIRCUITOS DIGITALES UTILIZANDO VHDL

5.3. MARCO TEÓRICO 84

5.3.1. FILTROS FIR 84

5.3.2. FILTROS IIR 85

5.3.3. METODOLOGÍA DE DISEÑO PARA FILTROS DIGITALES 86

5.4. IMPLEMENTACIÓN EN FPGA'S 86

5.5. DISEÑO DE UN FILTRO PASA-BAJAS 86

5.6. RESULTADOS 93

CONCLUSIONES 95

BIBLIOGRAFÍA 97

v

IEC FRANCISCO JAVIER TORRES VALLE

Page 7

CAPÍTULO I: LENGUAJES DE DESCRIPCIÓN DE HARDWARE

LENGUAJES DE

I

IEC FRANCISCO JAVIER TORRES VALLE

DESCRIPCIÓN DE

HARDWARE

1

Page 8

CAPÍTULO I: LENGUAJES DE DESCRIPCIÓN DE HARDWARE

1.1 INTRODUCCIÓN

A mediados de los años setenta se produce una

fuerte evolución en los procesos de fabricación de

los circuitos integrados, promoviendo el desarrollo

de circuitos digitales hasta la primera mitad de los

años ochenta. En aquellas épocas el esfuerzo de

diseño se concentraba en los niveles eléctricos para

establecer características e interconexiones entre

los componentes básicos al nivel de transistor. El

proceso de diseño era altamente manual y tan sólo

se empleaban herramientas como PSPICE para

simular esquemas eléctricos con modelos

previamente caracterizados a cada una de las

distintas tecnologías. A medida que pasaban los

años, los procesos tecnológicos se hacían más y

más complejos. Los problemas de integración iban

en aumento y los diseños eran cada vez más

difíciles de depurar y de dar mantenimiento.

Inicialmente los circuitos MSI (Medium Scale

Integration) y LSI (Low Scale Integration) se

diseñaron mediante el desarrollo de prototipos

basados en módulos simples. Cada uno de estos

módulos estaba formado por compuertas ya

probadas, pero este método poco a poco iba

quedándose obsoleto conforme aumentaba la

complejidad y tamaño de los circuitos. A finales de

los años setenta se constata el enorme desfase que

existía entre tecnología y diseño.

La considerable dificultad que puede llegar a

tomar el fabricar un circuito de alta escala de

integración, involucra riesgos y costos de diseño

desmesurados e imposibles de asumir por las

empresas. Es entonces, cuando diversos grupos de

investigadores empiezan a crear y desarrollar los

llamados “lenguajes de descripción de hardware”,

lenguajes en los que no fuera necesario

caracterizar eléctricamente cada componente del

circuito al nivel de transistor para así enfocarse

solamente en el funcionamiento lógico del sistema.

Empresas tales como IBM con su IDL, el TI-HDL

de Texas Instruments, ZEUS de General Electric,

etc., así como los primeros prototipos empleados

en las universidades, empezaron a desarrollarse

buscando una solución a los problemas que

presentaba el diseño de sistemas complejos. Sin

embargo, estos lenguajes nunca alcanzaron el nivel

de difusión y consolidación necesarios por motivos

distintos. Unos, los industriales, por ser propiedad

de la empresa permanecieron encerrados en ellas y

no estuvieron disponibles para su estandarización y

mayor difusión, en tanto que los universitarios

perecieron por no disponer de soporte ni

mantenimiento adecuado.

1.2 EL CONCEPTO DE

HERRAMIENTAS CAD-EDA

CAD son las siglas de Computer Aided Design,

o diseño asistido por computadora el cual

constituye todo un proceso de trabajo utilizando

técnicas de análisis apoyadas en gráficos mediante

sofisticadas herramientas de software las cuales

facilitan el estudio de los problemas asociados con

el diseño en cuestión. El concepto CAD se

relaciona con el dibujo como parte importante en

el proceso de diseño pero, además, el diseño de un

circuito debe cumplir con los requerimientos

especificados por el equipo de diseño, por las

normas de calidad existentes, los costos, etc. por lo

que las herramientas CAD intervienen en todas las

fases del diseño. Ya que no sólo son importantes

por acelerar el desarrollo del sistema al permitir

que varias personas puedan trabajar

simultáneamente en distintas etapas del diseño

sino que, además, es posible verificar el

funcionamiento del circuito mediante la

simulación del sistema. Todo esto simplifica la

tarea del equipo de diseño y conduce a la

conclusión del prototipo en menos tiempo. EDA,

Electronic Design Automation, es el nombre que

se le da a todas las herramientas de hardware y

software en el diseño de sistemas electrónicos.

Porque no sólo el software es importante, también

lo es el hecho de que las computadoras cada día

son más veloces y de mayor capacidad de

procesamiento, lo cual influye en el proceso de

diseño de circuitos electrónicos.

El diseño de hardware tiene un problema

fundamental, que no existe en desarrollo de

software. Este problema es el alto costo del ciclo

diseño

reinicio del ciclo, ya que el costo del prototipo

generalmente suele ser bastante elevado. Se

impone la necesidad de reducir este ciclo de diseño

para no incluir la fase de desarrollo del prototipo

más que al final del proceso, evitando la repetición

de varios prototipos que es lo que encarece el

ciclo. Para ello se introduce la fase de simulación y

verificación de circuitos utilizando herramientas

EDA, de tal forma que no sea necesario

implementar físicamente un prototipo para

comprobar el funcionamiento del circuito.

desarrollo del prototipo pruebas

IEC FRANCISCO JAVIER TORRES VALLE

2

Page 9

CAPÍTULO I: LENGUAJES DE DESCRIPCIÓN DE HARDWARE

i

i

i

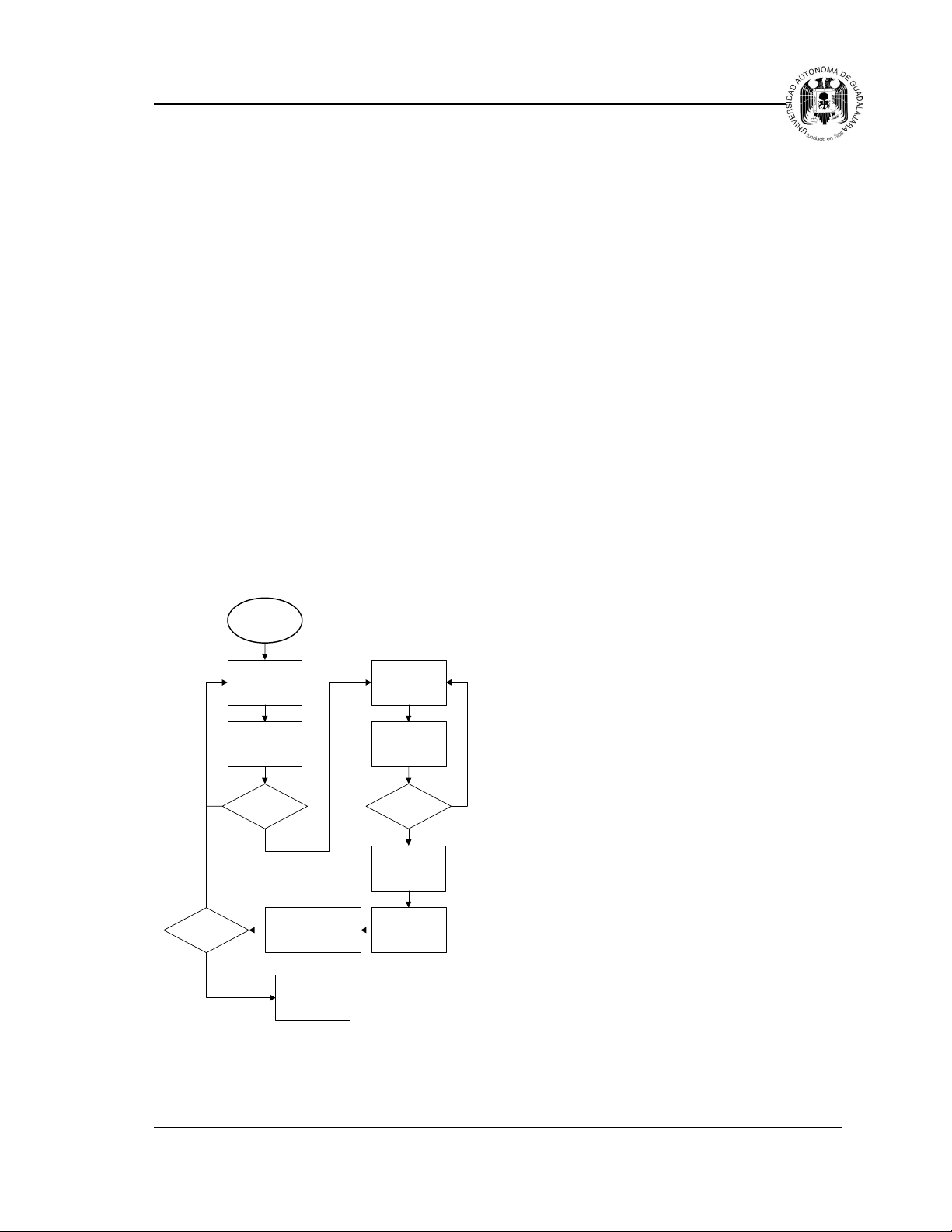

En el ciclo de diseño de circuitos, las

herramientas EDA están presentes en todas las

fases. Primero en la fase de generación del sistema

que puede representarse mediante un diagrama

esquemático, a bloques o de flujo.

Se encuentran también en la fase de simulación

y comprobación de circuitos, donde diferentes

herramientas permiten verificar el funcionamiento

del sistema. Estas simulaciones pueden ser de

eventos, funcionales, digitales o eléctricas, de

acuerdo al nivel de simulación requerido. Después

están las herramientas EDA utilizadas en la

síntesis y programación de circuitos digitales en

dispositivos lógicos programables. Existen,

además, las herramientas EDA orientadas a la

fabricación de circuitos. En el caso del diseño de

hardware estas herramientas sirven para la

realización de PCBs (Printed Circuit Boards o

placas de circuito impreso), o para desarrollar

circuitos integrados de aplicación especifica

conocidos como ASICs (Application Specific

Integrated Circuits). Este ciclo de diseño de

hardware se muestra en la figura 1.1.

IDEA

DESCRIPCIÓN

DEL CIRCUITO

SÍNTESIS

A continuación se mencionan las principales

características y finalidad de algunas herramientas

EDA que intervienen en el diseño de circuitos.

I. Lenguajes de descripción de circuitos.

Son lenguajes mediante los cuales es posible

describir el funcionamiento y estructura de un

circuito eléctrico o digital. La descripción puede

ser mediante bloques donde se muestra la

arquitectura del diseño, o de comportamiento, es

decir, se describe el funcionamiento del circuito en

vez de especificar los elementos de los que está

compuesto.

II. Diagramas esquemáticos.

Es la forma clásica de describir un diseño

electrónico y la más extendida ya que era la única

usada antes de la aparición de las herramientas de

EDA. La descripción está basada en un “plano”

donde se muestran los diferentes componentes

utilizados en el circuito.

III. Grafos y diagramas de flujo.

Es posible describir un circuito o sistema

mediante diagramas de flujo, redes de Petri,

máquinas de estados, etc. En este caso sería una

descripción gráfica y además sería

comportamental, porque no es una descripción

mediante componentes.

no

no

¿FUNCIONA?

s

SIMULACIÓN

FUNCIONAL

¿FUNCIONA?

s

PRUEBAS AL DISEÑO

FINALIZA EL

PROCESO DE

DISEÑO

ANÁLISIS

TEMPORAL

¿FUNCIONA?

s

PROGRAMACIÓN

DEL

DISPOSITIVO

ELABORACIÓN

DEL PROTOTIPO

Figura 1.1 Flujo de diseño en el desarrollo de

sistemas electrónicos

IEC FRANCISCO JAVIER TORRES VALLE

IV. Simulación de eventos.

Estas herramientas se usan para la simulación de

circuitos a grandes rasgos. En esta simulación, los

componentes más importantes son elementos de

no

alto nivel como discos duros, buses de

comunicaciones, memorias RAM etc.

V. Simulación funcional.

Bajando al nivel de compuertas digitales se

puede realizar una simulación funcional de las

mismas. Este tipo de simulación comprueba la

operación de circuitos digitales a partir del

comportamiento lógico de sus elementos con el fin

de comprobar el funcionamiento en conjunto del

circuito mediante unos estímulos dados. Similar a

lo que se realiza en un laboratorio.

VI. Simulación digital.

Esta simulación, también exclusiva de los

circuitos digitales, es como la anterior con la

diferencia de que se tienen en cuenta los retardos

3

Page 10

CAPÍTULO I: LENGUAJES DE DESCRIPCIÓN DE HARDWARE

de propagación de cada compuerta. Es una

simulación muy cercana al comportamiento real

del circuito y prácticamente garantiza el

funcionamiento correcto del circuito en cuestión.

En las herramientas EDA este tipo de simulación

se conoce como análisis temporal o timing.

VII. Simulación eléctrica.

Es la simulación de más bajo nivel donde las

respuestas del sistema se verifican al nivel de

transistor. Sirven tanto para circuitos analógicos

como digitales y su respuesta es prácticamente

idéntica a la realidad ya que se prueban retardos de

tiempo, niveles de voltaje, disipación de potencia,

etc.

VIII. Diseño de PCBs

Con estas herramientas es posible realizar el

trazado de pistas para la fabricación de placas de

circuitos impresos.

IX. Diseño de circuitos integrados

Son herramientas EDA que sirven para la

realización de circuitos integrados. Las

capacidades gráficas de estas herramientas

permiten la realización de las diferentes máscaras

que intervienen en la realización de éstos.

X. Diseño con dispositivos programables.

Estas herramientas facilitan la programación de

dispositivos, ya sean PALs, PLDs, CPLDs o

FPGAs.

1.3 LENGUAJES DE

DESCRIPCIÓN DE

HARDWARE

Los lenguajes de descripción de hardware

(HDLs) son utilizados para describir la

arquitectura y comportamiento de un sistema

electrónico los cuales fueron desarrollados para

trabajar con diseños complejos.

Comparando un HDL con los lenguajes para el

desarrollo de software vemos que en un lenguaje

de este tipo un programa que se encuentra en un

lenguaje de alto nivel (VHDL) necesita ser

ensamblado a código máquina (compuertas y

conexiones) para poder ser interpretado por el

procesador. De igual manera, el objetivo de un

HDL es describir un circuito mediante un conjunto

de instrucciones de alto nivel de abstracción para

que el programa de síntesis genere (ensamble) un

circuito que pueda ser implementado físicamente.

La forma más común de describir un circuito es

mediante la utilización de esquemas que son una

representación gráfica de lo que se pretende

realizar. Con la aparición de herramientas EDA

cada vez más complejas, que integran en el mismo

marco de trabajo las herramientas de descripción,

síntesis, simulación y realización; apareció la

necesidad de disponer de un método de

descripción de circuitos que permitiera el

intercambio de información entre las diferentes

herramientas que componen el ciclo de diseño. En

principio se utilizó un lenguaje de descripción que

permitía, mediante sentencias simples, describir

completamente un circuito. A estos lenguajes se

les llamó Netlist puesto que eran simplemente eso,

un conjunto de instrucciones que indicaban las

interconexiones entre los componentes de un

diseño. A partir de estos lenguajes simples, que ya

eran auténticos lenguajes de descripción hardware,

se descubrió el interés que podría tener el describir

circuitos utilizando un lenguaje en vez de usar

esquemas. Sin embargo, se siguieron utilizando

esquemas puesto que desde el punto de vista del

ser humano son mucho más sencillos de entender,

aunque un lenguaje siempre permite una edición

más rápida y sencilla.

Conforme las herramientas de diseño se

volvieron más sofisticadas, y la posibilidad de

desarrollar circuitos digitales mediante dispositivos

programables era más viable, apareció la necesidad

de poder describir los circuitos mediante un

lenguaje de alto nivel de abstracción. No desde un

punto de vista estructural, sino desde el punto de

vista funcional. Este nivel de abstracción se había

alcanzado ya con las herramientas de simulación,

ya que para poder simular partes de un sistema era

necesario disponer de modelos que describieran el

funcionamiento de bloques del circuito o de cada

componente si fuera necesario. Estos lenguajes

estaban sobre todo orientados a la simulación, por

lo que poco importaba que el nivel de abstracción

fuera tan alto que no fuera sencillo una realización

o síntesis a partir de dicho modelo. Con la

aparición de técnicas para la síntesis de circuitos a

partir de lenguajes de alto nivel de abstracción, se

comenzaron a utilizar los lenguajes de simulación

para sintetizar circuitos. Que si bien alcanzan un

altísimo nivel de abstracción, su orientación era

básicamente la de simular, por lo que los

resultados de una síntesis a partir de descripciones

IEC FRANCISCO JAVIER TORRES VALLE

4

Page 11

CAPÍTULO I: LENGUAJES DE DESCRIPCIÓN DE HARDWARE

con estos lenguajes no eran siempre las más

optimas.

Además, los lenguajes de descripción de

hardware al formar parte de las herramientas EDA

permiten el trabajo en equipo. Así, al estructurar el

desarrollo del proyecto, cada integrante del equipo

de diseño puede trabajar en subproyectos antes de

integrar todas las partes del sistema.

1.3.1 VENTAJAS DE LOS HDLS

Una metodología de diseño que utiliza un HDL

posee varias ventajas sobre la metodología

tradicional de diseño a nivel compuerta. Algunas

de estas ventajas son listadas a continuación.

• Es posible verificar el funcionamiento del

sistema dentro del proceso de diseño sin

necesidad de implementar el circuito.

• Las simulaciones del diseño, antes de que éste

sea implementado mediante compuertas,

permiten probar la arquitectura del sistema

para tomar decisiones en cuanto a cambios en

el diseño.

• Las herramientas de síntesis tienen la

capacidad de convertir una descripción hecha

en un HDL, VHDL por ejemplo, a

compuertas lógicas y, además, optimizar dicha

descripción de acuerdo a la tecnología

utilizada.

• Esta metodología elimina el antiguo método

tedioso de diseño mediante compuertas,

reduce el tiempo de diseño y la cantidad de

errores producidos por el armado del circuito.

• Las herramientas de síntesis pueden

transformar automáticamente un circuito

obtenido mediante la síntesis de un código en

algún HDL, a un circuito pequeño y rápido.

Además, es posible aplicar ciertas

características al circuito dentro de la

descripción para afinar detalles (retardos,

simplificación de compuertas, etc.) en la

arquitectura del circuito y que estas

características se obtengan en la síntesis de la

descripción.

• Las descripciones en un HDL proporcionan

documentación de la funcionalidad de un

diseño independientemente de la tecnología

utilizada.

• Un circuito hecho mediante una descripción

en un HDL puede ser utilizado en cualquier

tipo de dispositivo programable capaz de

soportar la densidad del diseño. Es decir, no es

necesario adecuar el circuito a cada

dispositivo porque las herramientas de síntesis

se encargan de ello.

• Una descripción realizada en un HDL es más

fácil de leer y comprender que los netlist o

circuitos esquemáticos.

1.4 VHDL

VHDL es un lenguaje de descripción de

hardware utilizado para describir circuitos en un

alto nivel de abstracción el cual está siendo

rápidamente aceptado como un medio estándar de

diseño. VHDL es producto del programa Very

High Speed Integrated Circuit (VHSIC)

desarrollado por el Departamento de Defensa de

los Estados Unidos a finales de la década de los

70's. El propósito era hacer un estándar para

diseñar, modelar, y documentar circuitos

complejos de tal manera que un diseño

desarrollado por una empresa pudiera ser

entendido por otra y, además, pudiera ser

procesado por software con propósitos de

simulación.

VHDL es reconocido como un estándar de los

lenguajes HDL por el Instituto de Ingenieros en

Electricidad y Electrónica – IEEE – como su

estándar 1076 el cual fue ratificado en 1987, y por

parte del Departamento de Defensa de los Estados

Unidos como el estándar MIL-STD-454L En 1993

el estándar IEEE-1076 se actualizó y un estándar

adicional, el IEEE-1164, fue adoptado. Para 1996

el estándar IEEE-1076.3 se convirtió en un

estándar de VHDL para síntesis siendo éste el que

se utiliza en el diseño de sistemas digitales. Los

estándares más utilizados en síntesis de circuitos

por la mayoría de las herramientas de diseño son el

IEEE-1164 y el IEEE-1076.3. En la actualidad

VHDL es un estándar de la industria para la

descripción, modelado y síntesis de circuitos

digitales. Por esto, los ingenieros de la mayoría de

las áreas de electrónica, si no es que todas, deben

aprender a programar en VHDL para incrementar

su eficiencia.

VHDL divide los circuitos en dos “vistas”

entidades y arquitecturas. La entidad modela al

circuito, componente o sistema externamente

IEC FRANCISCO JAVIER TORRES VALLE

5

Page 12

CAPÍTULO I: LENGUAJES DE DESCRIPCIÓN DE HARDWARE

definiendo a este mediante un nombre y sus

conexiones que vienen siendo las entradas y

salidas del circuito. En tanto que la arquitectura,

que es la vista interna, define el funcionamiento

del circuito. Después de definir las interfaces de la

entidad, otras entidades pueden utilizar a la

primera como un subcircuito, al mismo tiempo que

todas están siendo desarrolladas, es decir, están

siendo detalladas en su funcionamiento. Este

concepto de vistas externas e internas es propio de

VHDL y permite segmentar un sistema en bloques.

Así, una entidad es relativa a otras entidades a

través de sus conexiones y comportamiento. Por lo

que es posible experimentar cada entidad con

diferentes arquitecturas sin necesidad de cambiar

el resto del diseño. Y obviamente cada entidad

puede ser reutilizada en otros sistemas aunque no

hayan sido diseñadas específicamente para estos.

Un modelo de hardware de VHDL es mostrado

en la siguiente figura.

Figura 1.2 Modelo de Hardware de VHDL

Una entidad en VHDL, que ya es todo un

diseño, posee una o más conexiones hacia los

sistemas que la rodean. Una entidad puede estar

compuesta de otras entidades, de procesos y por

componentes, todos ellos trabajando

concurrentemente. Cada entidad está definida por

su arquitectura la cual se forma de instrucciones en

VHDL, ya sean aritméticas, asignaciones a señales

o de simples instanciaciones de componentes.

Los PROCESS en VHDL son utilizados para

modelar tanto circuitos secuénciales como

combinacionales utilizando un estilo de

descripción secuencial. Para interconectar procesos

distintos se utilizan SIGNALS que no son otra

cosa que simples cables.

Una señal posee una fuente (driver) y uno más

destinos (receptores) y un tipo de dato que le

proporciona características de interconexión. Por

ejemplo, una señal que se define como tipo bit

puede manejar los valores binarios ‘0’ y ‘1’

solamente, en tanto que una señal que se define

como bit_vector puede manejar mas de una

posición binaria.

La forma de diseñar circuitos en VHDL se

divide en tres categorías de acuerdo a su

complejidad: flujo de datos, comportamental, y

estructural. Estos tres estilos de diseño se detallan

a continuación.

• F

LUJO DE DATOS

En este estilo el diseño del circuito no es

complicado por lo que basta con describir como

fluyen los datos través de la entidad, de las

entradas hacia las salidas. La operación del sistema

está definida en términos de un conjunto de

transformaciones de datos expresadas como

instrucciones concurrentes.

• C

OMPORTAMENTAL

El diseño es un poco más complicado ya que

requiere de varias decisiones antes de definir los

datos de salida correctos. Por lo que se requiere de

una descripción algorítmica del funcionamiento

del circuito para facilitar el diseño del sistema. En

VHDL esto se obtiene expresando el

funcionamiento del diseño mediante una estructura

PROCESS la cual se compone de instrucciones

secuénciales.

• E

STRUCTURAL

Una descripción estructural se utiliza en

circuitos que requieren de más de una función,

hablando en términos de hardware, para realizar la

finalidad del sistema. Para ello segmentamos el

sistema en subcircuitos o componentes para

facilitar el diseño. Cada componente es

caracterizado en particular ya sea utilizando una

descripción de flujo de datos o comportamental. Y

a la entidad donde se describen las interconexiones

de estos componentes recibe el nombre de

descripción estructural.

Lo que ha hecho que VHDL sea en un tiempo

tan corto el lenguaje de descripción de hardware

más utilizado por la industria electrónica, es su

independencia con la metodología utilizada por

cada diseñador, su capacidad de descripción a

diferentes niveles de abstracción, y en definitiva la

IEC FRANCISCO JAVIER TORRES VALLE

6

Page 13

CAPÍTULO I: LENGUAJES DE DESCRIPCIÓN DE HARDWARE

posibilidad de poder reutilizar en diferentes

aplicaciones un mismo código.

1.5 METODOLOGÍA DE DISEÑO

UTILIZANDO VHDL

I. Definición de los requerimientos del

sistema.

Antes de comenzar a realizar la descripción del

diseño, es muy importante que se tenga una idea

clara de los objetivos y requerimientos. Tales

como: funciones del circuito, máxima frecuencia

de operación, y los puntos críticos del sistema.

Esto servirá para poder definir a grandes rasgos

cual será la arquitectura del circuito y así comenzar

a realizar la descripción.

II. Descripción del circuito en VHDL.

Antes de comenzar a escribir el código es

recomendable seleccionar alguna metodología de

diseño como: Top-Down, Bottom-Up, o Flat. Los

dos primeros involucran la creación de diseños

jerárquicos que generalmente son grandes, y el

último es utilizado normalmente en el diseño de

circuitos pequeños.

La metodología Top-Down consiste en dividir

el sistema en varios bloques de tal manera que se

puedan resolver los problemas por separado,

además, cada bloque a su vez se puede dividir en

otros bloques si es necesario. El objetivo es que

cada bloque tenga una función especifica

representada mediante un componente que

desempeñe dicha función. Bottom-Up es todo lo

contrario, comenzamos por caracterizar los

componentes básicos del circuito y con estos

formamos bloques de mayor tamaño que

representen un circuito más complejo que sus

partes individuales. La metodología Flat es

comúnmente utilizada para diseños pequeños,

donde los requerimientos son pocos y no muy

complejos por lo que no nos distraen y no

perdemos de vista la funcionalidad del circuito.

Este método de diseño es el que utilizamos

cotidianamente en el diseño de circuitos digitales,

y se le llama Flat por que no es necesario

seccionar el circuito para poder diseñarlo.

Después de decidir cual será la metodología que

debemos implementar entonces comenzamos a

describir el circuito de acuerdo con lo que se había

establecido. Es recomendable utilizar algún tipo de

diagrama a bloques con la descripción del

funcionamiento de cada bloque, diagramas de

estado, o usar alguna tabla de funcionamiento

donde se resumen las funciones de cada bloque en

particular. Obviamente existe la posibilidad de

cometer errores en VHDL, pero generalmente

estos son de son de sintaxis, como ";" al final de

cada instrucción, o simplemente por no utilizar

adecuadamente alguna instrucción. Algunas

ocasiones se podrán tener problemas al tratar de

sintetizar el código y esto se debe a que se comete

el error de pensar en términos de programación en

vez de enfocarnos en la descripción del circuito.

Cuando se utiliza VHDL el objetivo principal es

el diseño de hardware y para ello debemos de

utilizar técnicas de síntesis apropiadas al lenguaje,

ya que se suele cometer el error de comenzar a

programar en vez de describir y esto provoca que

nos olvidemos del objetivo que es el hardware.

LA CLAVE PARA DESCRIBIR Y SINTETIZAR

FÁCILMENTE CIRCUITOS DIGITALES CON

VHDL ES PENSAR EN TÉRMINOS DE

COMPUERTAS Y REGISTROS Y NO EN

FUNCIÓN DE VARIABLES Y SUBRUTINAS

III. Simulación de la descripción en VHDL.

La simulación del código, o simulación

funcional, nos permite detectar y corregir errores

antes que se implemente en el dispositivo. La

modularidad implementada facilita la evaluación

del circuito, porque al describir el circuito por

bloques podemos analizar cada uno por separado

antes de unirlos. Esta simulación equivale a la

depuración de programas en los lenguajes de

computación.

IV. Síntesis

Síntesis consiste en reducir una descripción

realizada en un lenguaje de alto nivel de

abstracción a un nivel de compuerta que pueda ser

implementada en un circuito. Dicho de otra

manera, síntesis es el proceso mediante el cual una

descripción es convertida en un listado de

conexiones (netlist) entre las compuertas, registros,

multiplexores, etc. de un dispositivo lógico

programable.

Por ejemplo, una compuerta XOR puede ser

sustituido por su equivalente: A XOR B =

A'B+AB', o una instrucción IF puede ser en

algunas ocasiones una compuerta AND, en otras

IEC FRANCISCO JAVIER TORRES VALLE

7

Page 14

CAPÍTULO I: LENGUAJES DE DESCRIPCIÓN DE HARDWARE

una OR, o inclusive toda una función booleana que

involucra diferentes tipos de compuertas. Por lo

que el proceso de síntesis depende del dispositivo

utilizado. Generalmente una misma función es

implementada de diferentes formas de acuerdo al

dispositivo que estemos utilizando y esto no

cambia la funcionalidad del diseño y será la

misma si se selecciona el componente adecuado a

la complejidad del diseño. El proceso utilizado

para sintetizar un código en un CPLD es conocido

como Fitting o ajuste y consiste en adaptar las

ecuaciones booleanas en los diferentes bloques

lógicos del dispositivo. Cuando se utiliza un FPGA

el proceso empleado se le llama Place And Route

y consiste en adecuar las ecuaciones a través de

varias celdas lógicas. Aunque la finalidad es la

misma, la manera en que se sintetiza un código en

un CPLD es totalmente distinta a la síntesis de

circuitos utilizando FPGAs.

Por otro lado la optimización en la conversión

del código VHDL a ecuaciones booleanas depende

de tres factores:

I. La descripción del circuito.

II. Los recursos disponibles en el dispositivo

seleccionado.

III. Las directivas de síntesis seleccionadas por el

diseñador.

La descripción es el punto más importante

porque de esto dependen los otros dos. En la

descripción no solamente tenemos que “decir”

como funciona el circuito, además, tenemos que

describir en que “forma” debe de hacerlo. No es lo

mismo describir el diseño de un sumador de cuatro

bits utilizando cuatro módulos que realizan la

suma basándose en propagación de bits de acarreo

entre estos, a describir un circuito que realice la

suma de manera paralela sin utilizar

retroalimentaciones. Finalmente suman pero no lo

hacen igual. Los recursos afectan la forma en que

son implementadas las ecuaciones lógicas en el

dispositivo. Por ejemplo, un contador de 4 bits con

borrado asíncrono no puede ser implementado en

un 16V8, porque el registro de la macrocelda de

salida del dispositivo no cuenta con esta

característica. Finalmente las directivas de

síntesis influyen directamente en el proceso de

cálculo de las ecuaciones que son implementadas

en el dispositivo. Algunas de estas directivas son:

asignación de pines, sintetizar para maximizar

velocidad, sintetizar para optimizar área, y algunas

que son descritas en el mismo código, como por

ejemplo forzar a que un nodo no sea simplificado o

eliminado y pueda ser retenido a la salida de una

macrocelda. Cuando se sintetiza para maximizar la

frecuencia generalmente quedan funciones con

varios términos e incluso hay términos que se

repiten en las ecuaciones de los nodos de salida,

pero esto se hace para evitar la retroalimentación.

V. Simulación del código sintetizado

Aún y cuando la simulación funcional se haya

realizado con éxito, debemos volver a evaluar el

circuito que realmente quedó sintetizado en el

dispositivo. Ya que las sustituciones de funciones,

como el caso de la compuerta XOR, dependerán de

las características del dispositivo utilizado. Y es

posible que ciertas funciones se ejecuten en más

tiempo de los esperado y esto altere el

funcionamiento del resto del diseño. Simular el

código sintetizado en el circuito permite verificar

los retrasos de tiempo de un nodo a otro, evaluar la

máxima frecuencia de operación del circuito y

verificar que éste funcione adecuadamente. En

dado caso que el código no pudiera ser sintetizado

podemos tratar de mejorar la descripción, es decir,

mejorar el diseño tratando de eliminar registros,

compuertas, buffers, etc., encontrar algún error en

la descripción, cambiar las directivas de síntesis o

definitivamente seleccionar otro dispositivo.

VI. Programación del dispositivo

Después de completar la descripción, la síntesis

y la simulación del circuito con éxito, el siguiente

paso es generar el archivo que nos permite

implementar físicamente nuestro diseño en un

dispositivo programable. Todos los programas de

VHDL para síntesis generan un archivo con el que

podemos programar el dispositivo. Ya sea JEDEC,

JTAG, BITSTREAM, etc. de acuerdo al tipo

dispositivo y fabricante.

IEC FRANCISCO JAVIER TORRES VALLE

8

Page 15

CAPÍTULO II: DISPOSITIVOS LÓGICOS PROGRAMABLES

II

DISPOSITIVOS LÓGICOS

PROGRAMABLES

9

IEC FRANCISCO JAVIER TORRES VALLE

Page 16

CAPÍTULO II: DISPOSITIVOS LÓGICOS PROGRAMABLES

2.1 CONCEPTOS

FUNDAMENTALES

La fabricación de dispositivos de lógica

programable se basa en los siguientes dos

conceptos.

UNCIONALIDAD COMPLETA

• F

La cual se fundamenta en el hecho de que

cualquier función lógica se puede realizar

mediante una suma de productos.

• C

ELDAS DE FUNCIONES UNIVERSALES.

También denominadas generadores de

funciones, son bloques lógicos configurados para

procesar cualquier función lógica, similares en su

funcionamiento a una memoria. En estas celdas se

almacenan los datos de salida del circuito

combinacional en vez de implementar físicamente

la ecuación booleana.

2.2 DISPOSITIVOS LÓGICOS

PROGRAMABLES

Un dispositivo lógico programable, o PLD

(Programmable Logic Device), es un dispositivo

cuyas características pueden ser modificadas y

almacenadas mediante programación. El

dispositivo programable más simple es el PAL

(Programmable Array Logic). El circuito interno

de un PAL consiste en una matriz de conexiones,

un matriz de compuertas AND y un arreglo de

compuertas OR. Una matriz de conexiones es una

red de conductores distribuidos en filas y columnas

con un fusible en cada punto de intersección,

mediante la cual se seleccionan cuales entradas del

dispositivo serán conectadas al arreglo AND cuyas

salidas son conectadas al arreglo OR y de esta

manera obtener una función lógica en forma de

suma de productos.

La mayoría de los PLDs están formados por una

matriz de conexiones, una matriz de compuertas

AND, y una matriz de compuertas OR y algunos,

además, con registros. Las matrices pueden ser

fijas o programables. Con estos recursos se

implementan las funciones lógicas deseadas

mediante un software especial y un programador

de dispositivos. El tipo más sencillo de matriz

programable, que data de los años 60, era una

matriz de diodos con un fusible en cada punto de

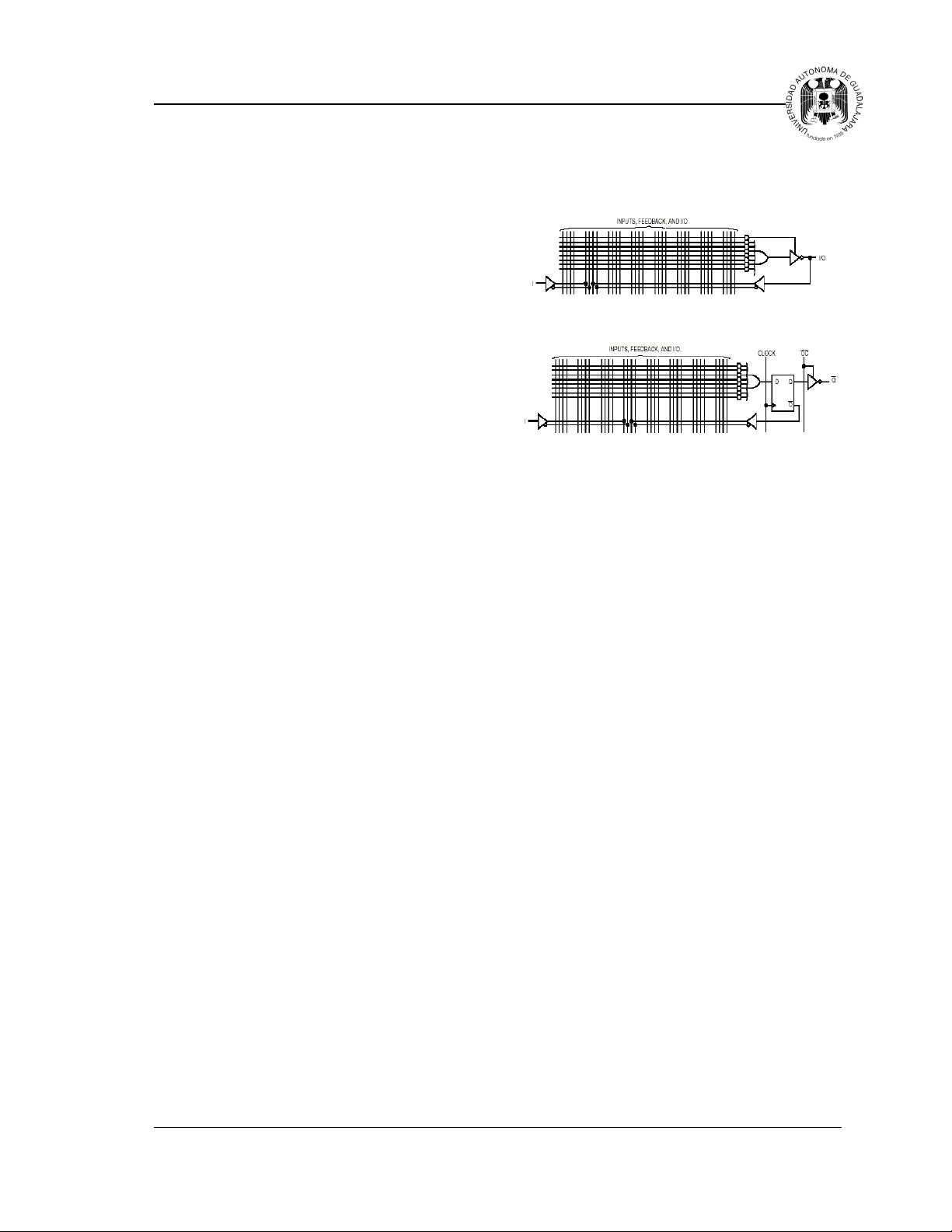

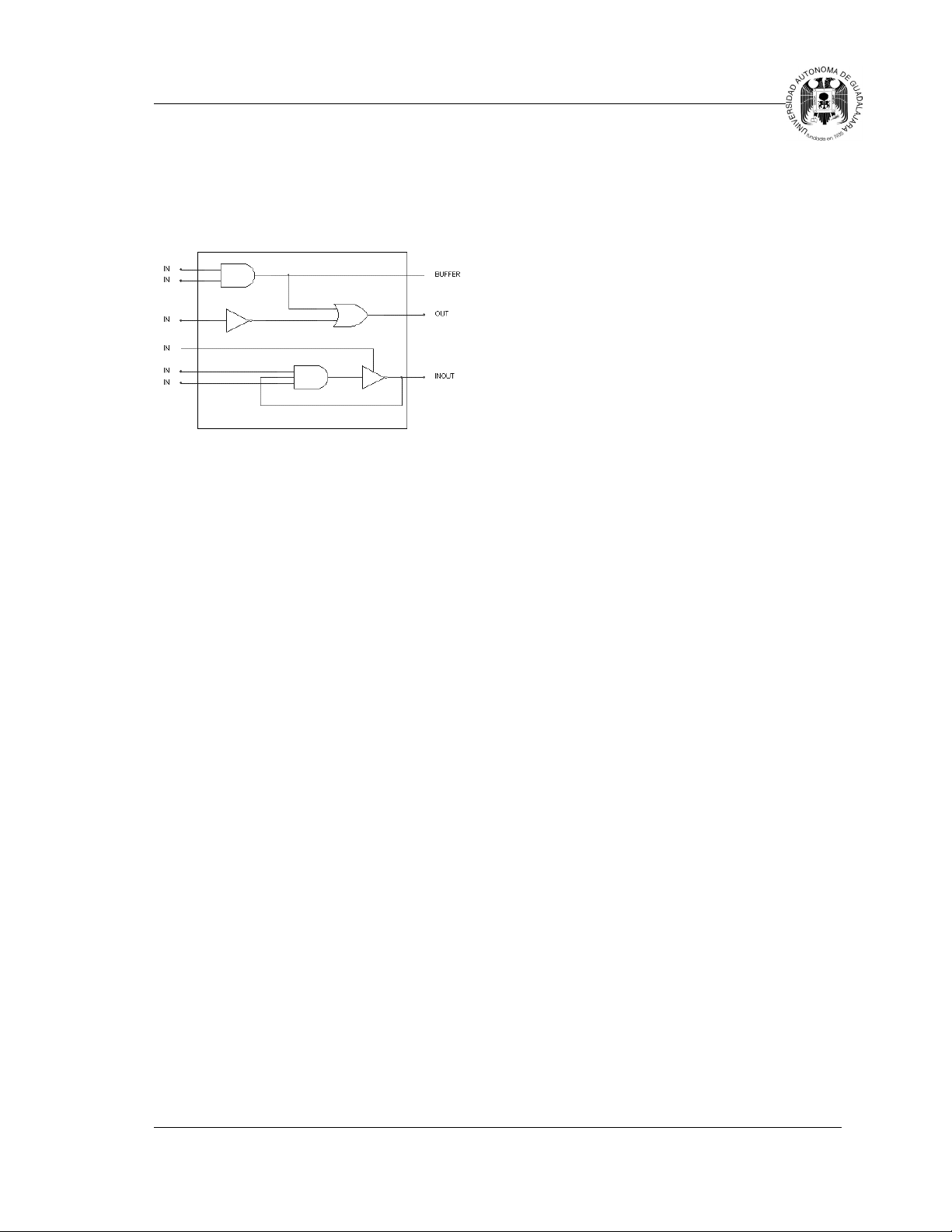

intersección de la misma. En la figura 2.1 se

muestran los circuitos básicos para la mayoría de

los PLDs.

Figura 2.1 Estructuras comúnmente utilizadas en

PLDs

2.2.1 MATRIZ GENÉRICA PROGRAMABLE

Una Matriz Genérica Programable, GAL

(Generic Array Logic), es una denominación que

utilizaba originalmente Lattice Semiconductor y

que más tarde se licenció a otros fabricantes. Un

GAL en su forma básica es un PLD con una matriz

AND reprogramable, una matriz OR fija y una

lógica de salida programable mediante una

macrocelda. Esta estructura permite implementar

cualquier función lógica en forma de suma de

productos con un numero de términos definido. En

los PLDs no reprogramables la síntesis de las

ecuaciones lógicas se realiza mediante la quema de

fusibles en cada punto de intersección de los pines

de entrada con las compuertas. En un GAL el

fusible se reemplaza por una celda CMOS

eléctricamente borrable (EECMOS) y mediante

programación se activa o desactiva cada celda

EECMOS. Una celda activada conecta su

correspondiente intersección de fila y columna, y

una celda desactivada desconecta dicha

intersección. Con esta estructura se puede aplicar

cualquier combinación de variables de entrada, o

sus complementos, a una compuerta AND para

generar cualquier operación producto que se desee.

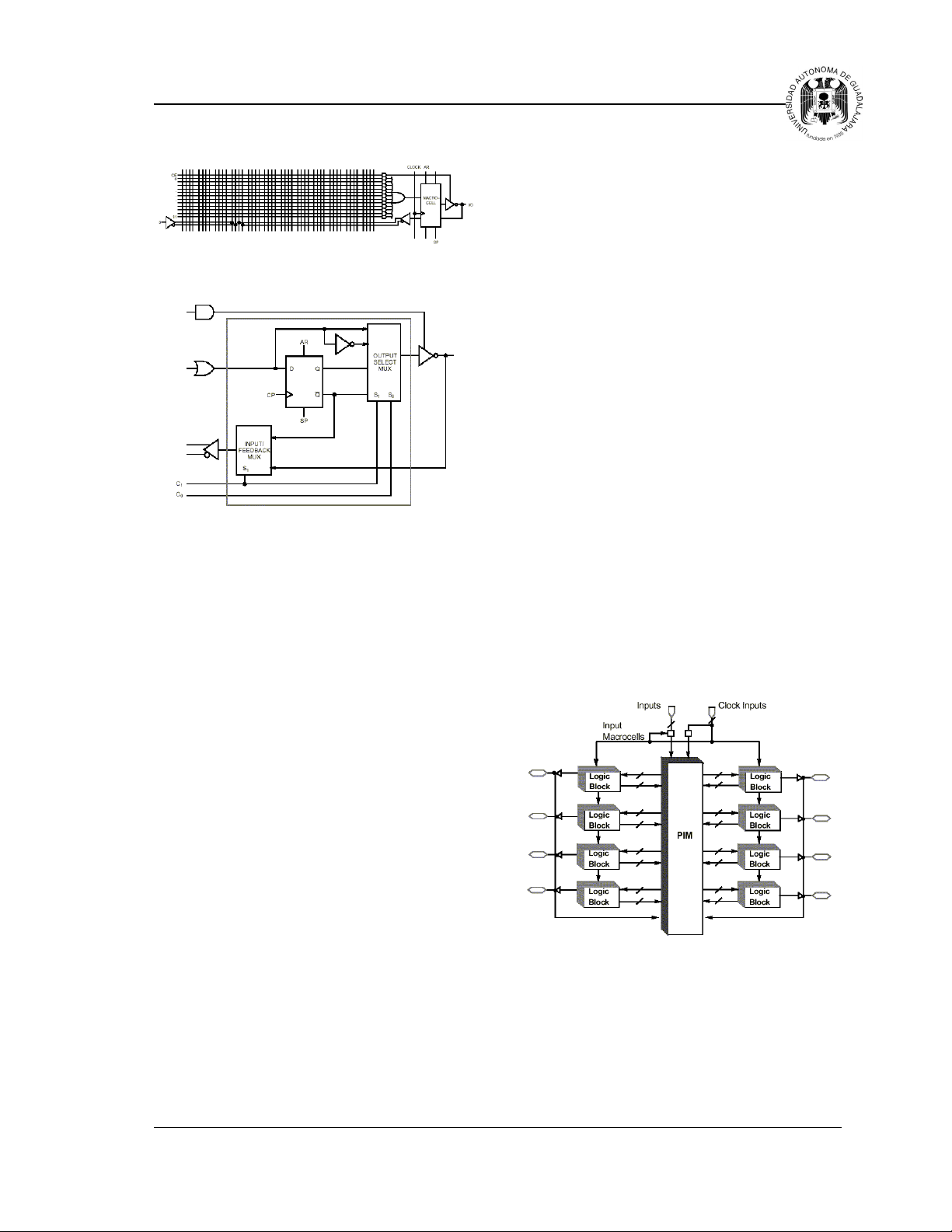

A continuación se muestran las estructuras típicas

de un dispositivo GAL y la macrocelda de salida

del GAL22V10.

10

IEC FRANCISCO JAVIER TORRES VALLE

Page 17

CAPÍTULO II: DISPOSITIVOS LÓGICOS PROGRAMABLES

Figura 2.2 Estructura típica de un GAL

FIGURA 2.3 Macrocelda de un GAL22V10

2.3 CPLD

Un CPLD (Complex Programmable Logic

Device) extiende el concepto de un PLD a un

mayor nivel de integración ya que permite

implementar sistemas más eficientes porque

utilizan menos espacio, mejoran la confiabilidad

en el circuito, y reducen costos. Un CPLD se

forma con múltiples bloques lógicos, cada uno

similar a un PLD. Los bloques lógicos se

comunican entre sí utilizando una matriz

programable de interconexiones lo cual hace más

eficiente el uso del silicio y conduce a un mejor

desempeño. A continuación se explican

brevemente las principales características de la

arquitectura de un CPLD.

multiplexores. La primera se basa en una matriz

de filas y columnas con una celda EECMOS en

cada intersección. Al igual que en el GAL esta

celda puede ser activada para conectar/desconectar

la correspondiente fila y columna. Esta

configuración permite una total interconexión

entre las entradas y salidas de los bloques lógicos.

Sin embargo, estas ventajas provocan que

disminuya el desempeño del dispositivo además de

aumentar el consumo de energía y el tamaño del

componente. En la interconexión mediante

multiplexores, existe un multiplexor por cada

entrada al bloque lógico. Las vías de interconexión

programables son conectadas a las entradas de un

numero fijo de multiplexores por cada bloque

lógico. Las entradas de selección de estos

multiplexores son programadas para permitir que

sea seleccionada únicamente una vía de la matriz

de interconexiones por cada multiplexor, la cual se

propaga hacia el bloque lógico. Cabe mencionar

que estos multiplexores no tienen acceso a todas

las vías de la matriz por lo que la rutabilidad se

incrementa usando multiplexores de mayor

tamaño, permitiendo así que cualquier

combinación de señales de la matriz de

interconexión pueda ser enlazada hacia cualquier

bloque lógico. Sin embargo, el uso de grandes

multiplexores incrementa el tamaño de dispositivo

y reduce su desempeño.

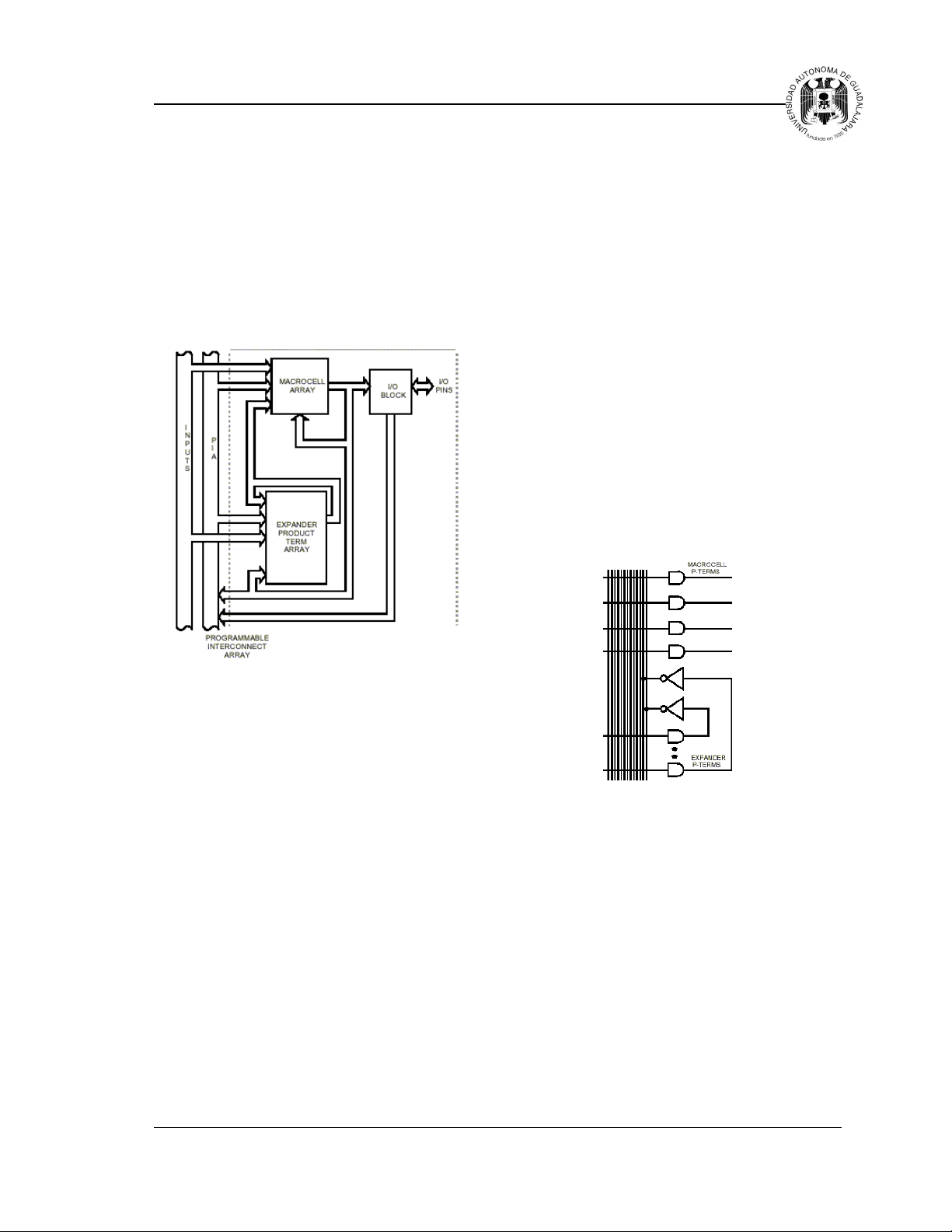

2.3.1 MATRIZ DE INTERCONEXIONES

PROGRAMABLES

La matriz de interconexiones programables,

PIM Programmable Interconect Matrix (véase la

figura 2.4), permite unir los pines de entrada/salida

a las entradas del bloque lógico, o las salidas del

bloque lógico a las entradas de otro bloque lógico,

o inclusive a las entradas del mismo bloque. La

mayoría de los CPLDs usan una de dos

configuraciones para esta matriz: interconexión

mediante arreglo o interconexión mediante

11

IEC FRANCISCO JAVIER TORRES VALLE

Figura 2.4 Arquitectura Básica de un CPLD

2.3.2 BLOQUES LÓGICOS

Un bloque lógico es muy similar a un PLD, cada

uno de ellos poseen generalmente una matriz de

compuertas AND, una matriz de compuertas OR y

una configuración para la distribución de los

Page 18

CAPÍTULO II: DISPOSITIVOS LÓGICOS PROGRAMABLES

productos en las diferentes macroceldas del boque.

El tamaño del bloque lógico es una medida de la

capacidad del CPLD, ya que de esto depende el

tamaño de la función booleana que pueda ser

implementada dentro del bloque. Los bloques

lógicos usualmente tienen de cuatro a veinte

macroceldas. La cantidad de bloques lógicos que

puede poseer un CPLD depende de la familia y

fabricante del dispositivo.

familia MAX se colocan 4 productos por

macrocelda los cuales pueden ser compartidos con

otras macroceldas. Cuando un producto puede ser

únicamente utilizado por una macrocelda se le

conoce como termino - producto dirigido, y

cuando estos pueden ser utilizados por otras

macroceldas se le llama termino - producto

compartido. Mediante estos productos

compartidos se mejora la utilización del

dispositivo, sin embargo, esto produce un retardo

adicional al tener que retroalimentar un producto

hacia otra macrocelda y con esto disminuye la

velocidad de trabajo del circuito. La forma en que

son distribuidos los productos repercute en la

flexibilidad que proporciona el dispositivo para el

diseñador. Además, que estos esquemas

proporcionan también flexibilidad para los

algoritmos del programa de síntesis que es el que

finalmente selecciona la mejor forma en que deben

ser distribuidas las ecuaciones lógicas en el

componente.

Figura 2.5 Estructura de un Bloque Lógico en

dispositivos de las familias MAX340 y MAX5000

2.3.3 DISTRIBUCIÓN DE PRODUCTOS

Existen pequeñas diferencias en cuanto a la

distribución de los productos en un CPLD, esto

dependerá de la familia del dispositivo y del

fabricante. Obviamente el tamaño de las sumas

sigue siendo el factor más importante para la

implementación de funciones lógicas. Pero cada

fabricante distribuye los productos de diferente

forma.

La familia MAX de CPLDs que fue

desarrollada por Cypress Semiconductor

conjuntamente con Altera Corporation, siendo

los primeros en sacar al mercado unan familia de

CPLDs, Altera la llamó MAX5000 y Cypress por

su parte la clasificó como MAX340, la

distribución de productos no es igual a la de un

PLD. En un dispositivo como el 22V10 tenemos

que la suma de productos es fija por cada

macrocelda -8, 10, 12, 14 o 16 productos-, en la

Figura 2.6 Distribución de Productos en

dispositivos de las familias MAX340 y MAX5000

2.3.4 MACROCELDAS

Las macroceldas de un CPLD son similares a las

de un PLD. Estas también están provistas con

registros, control de polaridad, y buffers para

utilizar salidas con alta impedancia. Por lo general

un CPLD tiene macroceldas de entrada/salida,

macroceldas de entrada y macroceldas internas

u ocultas (buried macrocells), en tanto que un

22V10 tiene solamente macroceldas de

entrada/salida. Una macrocelda interna es similar a

una macrocelda de entrada/salida, sólo que esta no

puede ser conectada directamente a una terminal

del dispositivo. La salida de una macrocelda

12

IEC FRANCISCO JAVIER TORRES VALLE

Page 19

CAPÍTULO II: DISPOSITIVOS LÓGICOS PROGRAMABLES

interna va conectada directamente a la matriz de

interconexiones programable. Por lo que es posible

manejar ecuaciones y almacenar el valor de salida

de estas internamente utilizando los registros de

estas macroceldas.

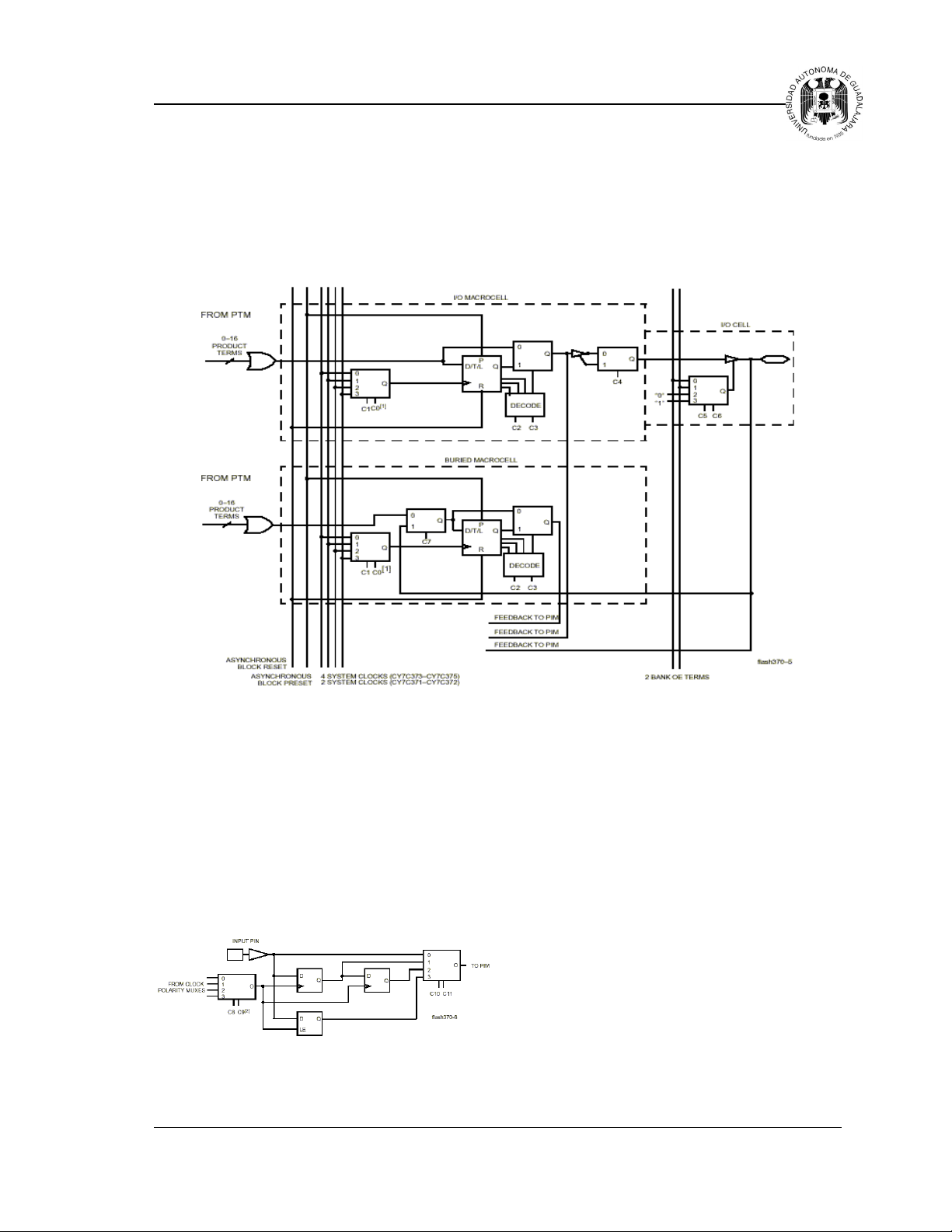

En la figura 2.7 se muestran la arquitectura

interna de un CPLD de la familia FLASH 370 de

Cypress Semiconductors. En esta podemos

apreciar las macroceldas de entrada/salida,

macroceldas ocultas y celdas de entrada/salida con

las que cuenta el dispositivo.

Figura 2.7 Macroceldas de entrada/salida, macroceldas ocultas y celdas de entrada/saliad en dispositivos

de la familia FLASH 370

Las macroceldas de entrada, como la que se

muestra en la figura 2.8, son utilizadas para

proporcionar entradas adicionales para las

funciones lógicas. En el diagrama se muestra la

macrocelda de entrada de la familia FLASH 370.

En general las macroceldas de entrada incrementan

la eficiencia del dispositivo al ofrecer algunos

registros adicionales con los que se pueden

almacenar el valor de la terminal de entrada.

2.3.5 CELDA DE ENTRADA/SALIDA

En la figura 2.7 se puede apreciar una celda de

entrada/salida, que bien podría considerarse parte

del bloque lógico, pero no necesariamente tienen

que estar a la salida de un bloque lógico. La

función de una celda de entrada/salida es permitir

el paso de una señal hacia dentro o hacia el

exterior del dispositivo. Dependiendo del

fabricante y de la arquitectura del CPLD estas

celdas son pueden ser consideradas o no parte del

bloque lógico.

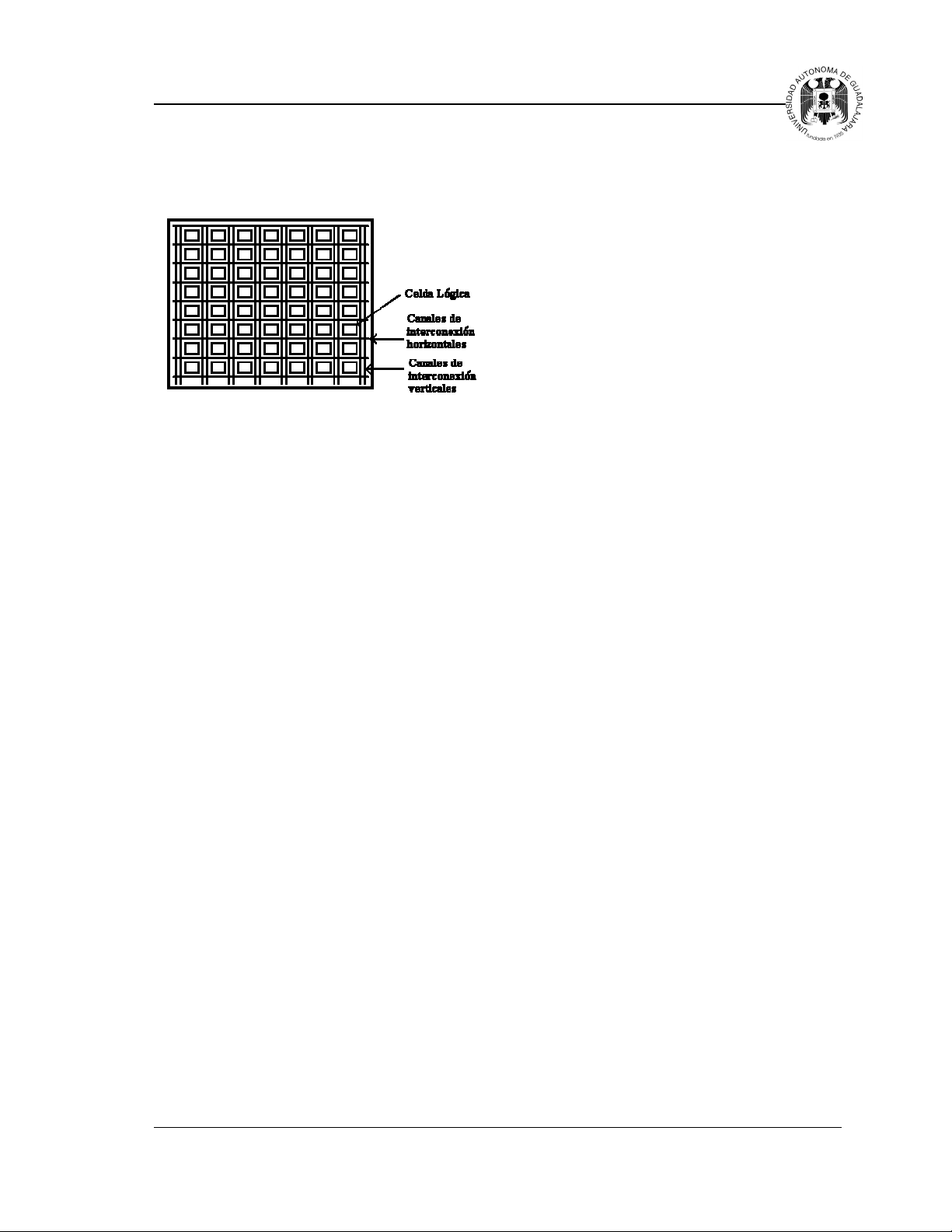

2.4 FPGA

La arquitectura de un FPGA (Field

Figura 2.8 Macrocelda de entrada en dispositivos

de la familia FLASH 370

Programmable Gate Array) consiste en arreglos de

varias celdas lógicas las cuales se comunican unas

con otras mediante canales de conexión verticales

13

IEC FRANCISCO JAVIER TORRES VALLE

Page 20

CAPÍTULO II: DISPOSITIVOS LÓGICOS PROGRAMABLES

y horizontales tal y como se muestra en la figura

2.9.

Figura 2.9 Arquitectura básica de un FPGA

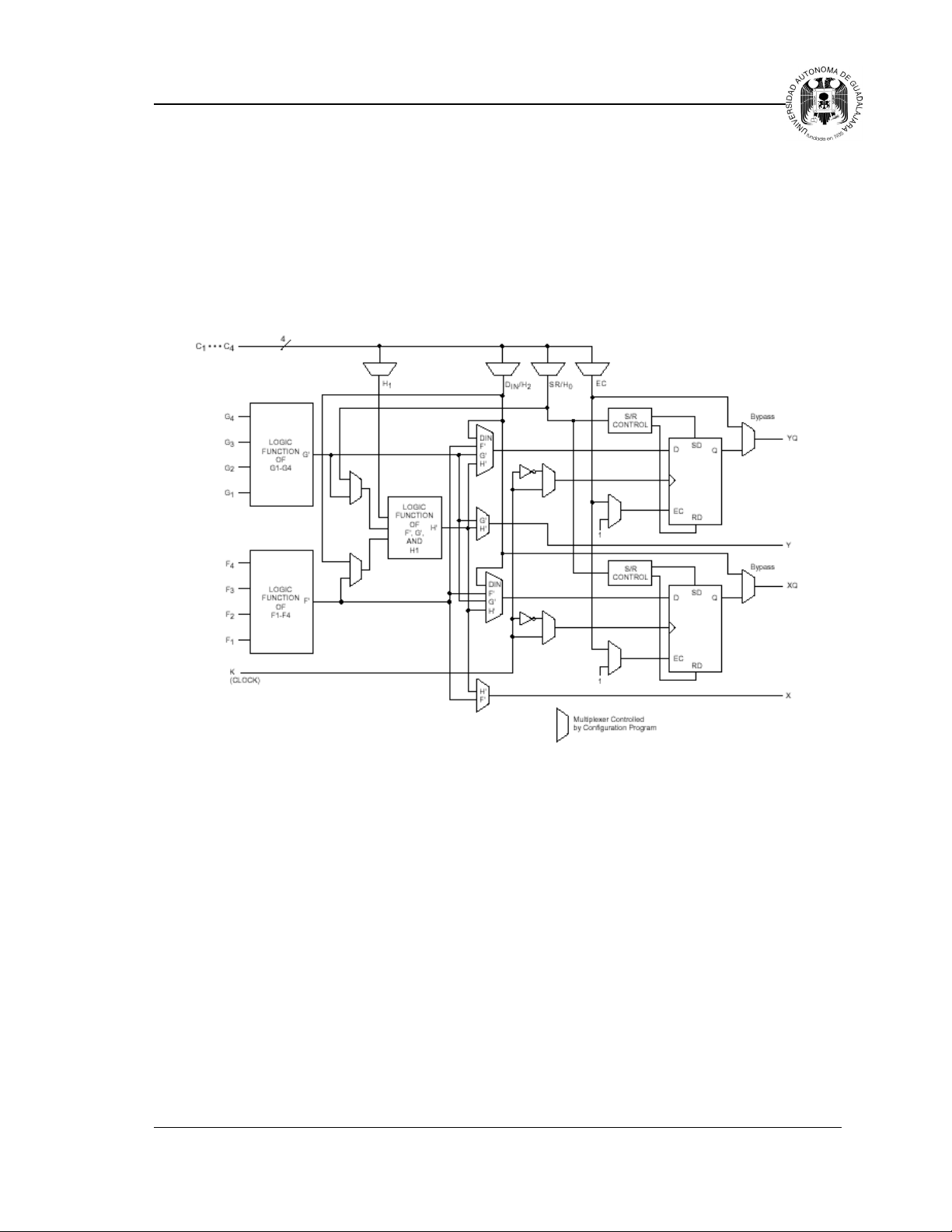

2.4.1 CELDAS LÓGICAS

Cada celda lógica es funcionalmente similar a

los bloques lógicos de un CPLD. La diferencia

está en que un FPGA normalmente utiliza

generadores de funciones en vez de compuertas.

Cada uno de estos generadores es como una

memoria en donde en vez de implementar la

función lógica mediante compuertas, se precalcula

el resultado y se almacena en el generador. Las

entradas al generador funcionan como un bus de

direcciones, y mediante las diferentes

combinaciones de las entradas al generador se

selecciona el resultado correcto. Esto le da una

gran densidad al dispositivo ya que se maneja un

gran número de generadores, pero el tiempo de

propagación al implementar una función lógica en

estos generadores es menor al que se necesitaría si

utilizáramos compuertas. La estructura de las

celdas lógicas y las formas en que estas pueden ser

interconectadas, tanto salidas como entradas de la

celda, varían de acuerdo al fabricante. En general

una celda lógica tiene menos funcionalidad que la

combinación de sumas de productos y macroceldas

de un CPLD, pero como cada FPGA tienen una

gran cantidad de celdas lógicas es posible

implementar grandes funciones utilizando varias

celdas lógicas en cascada. Además de las celdas

lógicas también es importante la tecnología

utilizada para crear las conexiones entre los

canales, las más importantes son las siguientes.

• ANTIFUSE

Al igual que la tecnología PROM, un FPGA que

utiliza este tipo de tecnología sólo se puede

programar una sola vez y utilizan algo similar a un

fusible para realizar las conexiones. Una vez que

éste es programado ya no se puede recuperar. La

diferencia radica en que en un fusible normal se

desactiva deshabilitando la conexión, en tanto que

en estos anti - fusibles cuando son programados se

produce una conexión por lo que normalmente se

encuentran abiertos. La desventaja obvia es que no

son reutilizables, pero por el contrario disminuyen

considerablemente el tamaño y costo de los

dispositivos.

• SRAM

Las celdas SRAM son implementadas como

generadores de funciones para remplazar la lógica

combinacional mediante compuertas y, además,

son usadas para controlar multiplexores e

interconectar las celdas lógicas entre ellas. En estas

el contenido se almacena mediante un proceso de

configuración en el momento de encendido del

circuito que contiene al FPGA. Ya que al ser

SRAM, el contenido de estos bloques de memoria

se pierde cuando se deja de suministrar la energía.

La información binaria de las celdas SRAM

generalmente se almacena en memorias seriales

EEPROM conocidas como memorias de

configuración. En el momento de encendido del

circuito toda la información binaria es transferida a

las celdas del FPGA mediante el proceso de

configuración el cual es generalmente automático

y el propio FPGA contiene un circuito interno que

se encarga de hacer todo el proceso.

Un FPGA que tiene una gran cantidad de

canales de interconexión tiende a tener pequeñas

celdas lógicas con muchas entradas y salidas en

comparación con el número de compuertas que

tiene la celda, este tipo de FPGAs generalmente

utilizan tecnología ANTIFUSE. Un FPGA que

tiene una estructura pequeña en canales de

interconexión tiende a tener grandes celdas lógicas

con pocas entradas y salidas en comparación con el

número de compuertas que hay en la celda. Este

tipo de FPGA generalmente está fabricado con

tecnología SRAM. Una arquitectura con celdas

lógicas pequeñas permite utilizar todos los

recursos del dispositivo. Sin embargo, si las celdas

lógicas son muy pequeñas entonces tendremos que

utilizar un gran número de estas para poder

implementar funciones lógicas de varios términos,

lo cual agrega un tiempo de retardo por cada celda

lógica implementada. Cuando el tamaño de la

celda lógica es grande sucede lo contrario, en este

tipo de celdas lógicas es posible utilizar un gran

número de compuertas por lo que podemos

IEC FRANCISCO JAVIER TORRES VALLE

14

Page 21

CAPÍTULO II: DISPOSITIVOS LÓGICOS PROGRAMABLES

implementar funciones lógicas de varios términos

con pocas celdas lógicas. El que el tamaño de la

celda sea grande no afecta la frecuencia máxima de

trabajo porque estamos hablando de que existe un

gran numero de compuertas que pueden ser usadas

en la función paralelamente, siendo el mismo

tiempo de retardo para todas. Sin embargo, cuando

las funciones son pequeñas en comparación con el

tamaño de la celda no es necesario utilizar todas

las compuertas de la celda, por lo que este tipo de

celdas no son precisamente las más indicadas para

desempeñar pequeñas funciones. La tecnología

SRAM es utilizada por Altera, Lucent

Technologies, Atmel, Xilinx y otros. La tecnología

ANTIFUSE es utilizada por Cypress, Actel,

QuickLogic, y Xilinx. A continuación se muestran

algunas celdas lógicas de distintos fabricantes.

Figura 2.10 Bloque Lógico Configurable de la familia XC4000 de Xilinx, Inc.

IEC FRANCISCO JAVIER TORRES VALLE

15

Page 22

CAPÍTULO II: DISPOSITIVOS LÓGICOS PROGRAMABLES

Figura 2.11 Elemento Lógico de la familia APEX20K de Altera Corporation

Figura 2.12Modulo Lógico de la familia ACT3 de Actel Corporation

IEC FRANCISCO JAVIER TORRES VALLE

16

Page 23

CAPÍTULO III: SINTAXIS DEL LENGUAJE

SINTAXIS DEL

III

IEC FRANCISCO JAVIER TORRES VALLE

LENGUAJE

17

Page 24

CAPÍTULO III: SINTAXIS DEL LENGUAJE

3.1 INTRODUCCIÓN A LA

DESCRIPCIÓN EN VHDL DE

CIRCUITOS DIGITALES

En este capítulo se discutirán los elementos

fundamentales de VHDL que son comúnmente

utilizados en síntesis de circuitos. Primero se

exponen el diseño de multiplexores y

comparadores con VHDL para hacer una

analogía con la metodología convencional de

diseño. Ya que es muy importante comprender

porque VHDL es un lenguaje para describir y no

para programar. Posteriormente se expondrán los

elementos básicos del lenguaje, tales como:

identificadores, objetos de datos, tipos de datos,

operadores y tipos de instrucciones.

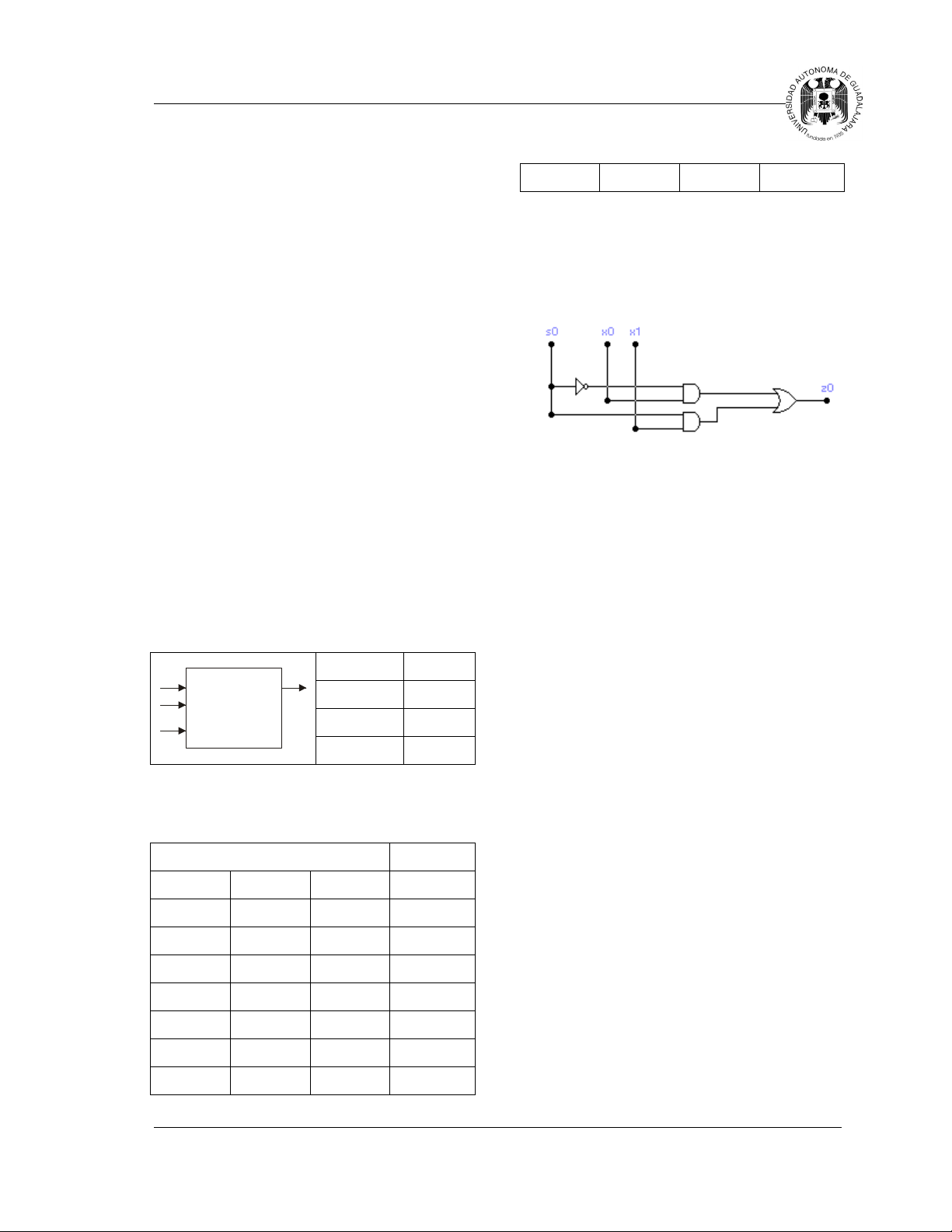

3.1.1 MULTIPLEXORES

Antes de examinar la descripción en VHDL de

multiplexores, analizaremos el funcionamiento

interno y la metodología tradicional de diseño

utilizada en este tipo de circuitos para después

realizar la descripción del circuito en VHDL. En

la figura 3.1 se describe externamente a un

multiplexor y la tabla resume su funcionalidad.

ENTRADA SALIDA

x0

x1

s0

z0

s0 z0

0 x0

1 x1

Figura 3.1 Multiplexor 2 a 1

La tabla de verdad completa sería la siguiente.

ENTRADAS SALIDA

s0 x0 x1 z0

0 0 0 0

0 0 1 0

0 1 0 1

0 1 1 1

1 0 0 0

1 0 1 1

1 1 0 0

1 1 1 1

Utilizando cualquier técnica de simplificación

de ecuaciones obtenemos: z0 = s0’·x0+s0·x1. Y el

circuito quedaría como se muestra en la figura

3.2.

Figura 3.2 Circuito del Multiplexor 2 a 1

En VHDL podemos describir el circuito ya sea

mediante la descripción completa de todas las

combinaciones de las entradas, utilizando la tabla

simplificada de funcionamiento o si lo deseamos

es posible realizar la descripción compuerta por

compuerta del circuito. Al primer estilo se le

conoce como de flujo de datos y en este debemos

describir como fluyen los datos de entrada hacia

la salida. A continuación se muestra la

descripción de flujo de datos del multiplexor con

VHDL utilizando la tabla completa de

funcionamiento del mismo. Las palabras en

negritas son palabras reservadas en VHDL y los

comentarios comienzan con dos guiones (--).

ENTITY multiplexor IS

PORT (s0, x0, x1: IN bit;

z0: OUT bit);

END multiplexor;

ARCHITECTURE data_flow OF multiplexor IS

SIGNAL temp: bit_vector (2 DOWNTO 0);

BEGIN

z0 <= '0' WHEN temp = "000" ELSE

'0' WHEN temp = "001" ELSE

'1' WHEN temp = "010" ELSE

'1' WHEN temp = "011" ELSE

'0' WHEN temp = "100" ELSE

'1' WHEN temp = "101" ELSE

'0' WHEN temp = "110" ELSE

'1';

temp <= s0 & x0 & x1; -- Concatenación

-- de las entradas en un

-- solo bus.

END data_flow;

Las descripciones en VHDL son creadas a

partir de dos estructuras que son fundamentales

IEC FRANCISCO JAVIER TORRES VALLE

18

Page 25

CAPÍTULO III: SINTAXIS DEL LENGUAJE

para el lenguaje: la entidad y la arquitectura.

Básicamente la entidad es la estructura en la que

se define cuales son las entradas y salidas del

circuito que deseamos representar, la cual

podemos asociar con una “caja” en la que se que

precisan cuales son las interfaces de

comunicación con el exterior, siendo la

arquitectura donde se detalla el comportamiento

interno de esa “caja”. Observe que en la

descripción anterior se utilizó un objeto de datos

llamado SIGNAL para crear el bus “temp” y

concatenar “s0”, “x0” y “x1” en un solo objeto y

así facilitar la descripción. A continuación

utilizaremos la tabla simplificada para diseñar el

multiplexor, ya que si observamos la salida

depende fundamentalmente de la entrada de

selección “s0”, por lo que atendiendo a esta

característica la descripción de flujo de datos

quedaría tal y como se muestra a continuación.

ENTITY multiplexor IS

PORT (s0, x0, x1: IN bit;

z0: OUT bit);

END multiplexor;

ARCHITECTURE data_flow OF multiplexor IS

BEGIN

z0 <= x0 WHEN s0 = '0' ELSE x1;

END data_flow;

En ambas descripciones hemos definido el

funcionamiento de la salida apoyándonos en las

entradas. Note que existe cierto “paralelismo” de

las entradas hacia las salidas, es decir, no importa

cual combinación de entradas se dé, sólo una

opción será asignada a la salida. Por lo que no

importa cual orden se haya seguido en la

descripción del circuito. Y esta es una de las

principales características de VHDL, es decir, no

importa tanto el orden de las instrucciones, lo cual

no es así en lenguaje de programación de

software. Tal vez este “paralelismo” se perciba

con mayor detalle realizando la descripción del

circuito compuerta por compuerta utilizando la

ecuación simplificada del circuito obtenida

anteriormente.

ENTITY multiplexor IS

PORT (s0, x0, x1: IN bit;

z0: OUT bit);

END multiplexor;

ARCHITECTURE data_flow OF multiplexor IS

SIGNAL not_s0, and1, and2: bit;

BEGIN

z0 <= and1 OR and2;

and1 <= not_s0 AND x0;

not_s0 <= NOT s0;

and2 <= s0 AND x1;

END data_flow;

La descripción anterior también es de flujo de

datos y no sigue ningún orden en particular en el

uso de las instrucciones y esto se ha hecho para

destacar el comportamiento paralelo o

concurrente de VHDL. Observe que cada

ecuación describe a cada una de las compuertas

que se muestran en la figura 3.2, por lo cual no

hubiera importado el orden que hayamos seguido

siempre y cuando se realicen las conexiones

correctamente.

Pensemos en el circuito implementado

físicamente en el laboratorio. Cada una de estas

compuertas posee características eléctricas que les

asignan un funcionamiento definido. Estas

particularidades eléctricas cumplen con leyes

físicas que se están cumpliendo todo momento y,

entonces, no importa como se hayan ordenado

los circuitos entre sí lo importante es realizar

correctamente las conexiones para obtener la

función deseada. En VHDL se trata de emular ese

comportamiento, por lo tanto el orden que se haya

seguido en cada una de las instrucciones

anteriores no es importante, ya que hicimos

correctamente la interconexión entre las

compuertas.

3.1.2 COMPARADORES

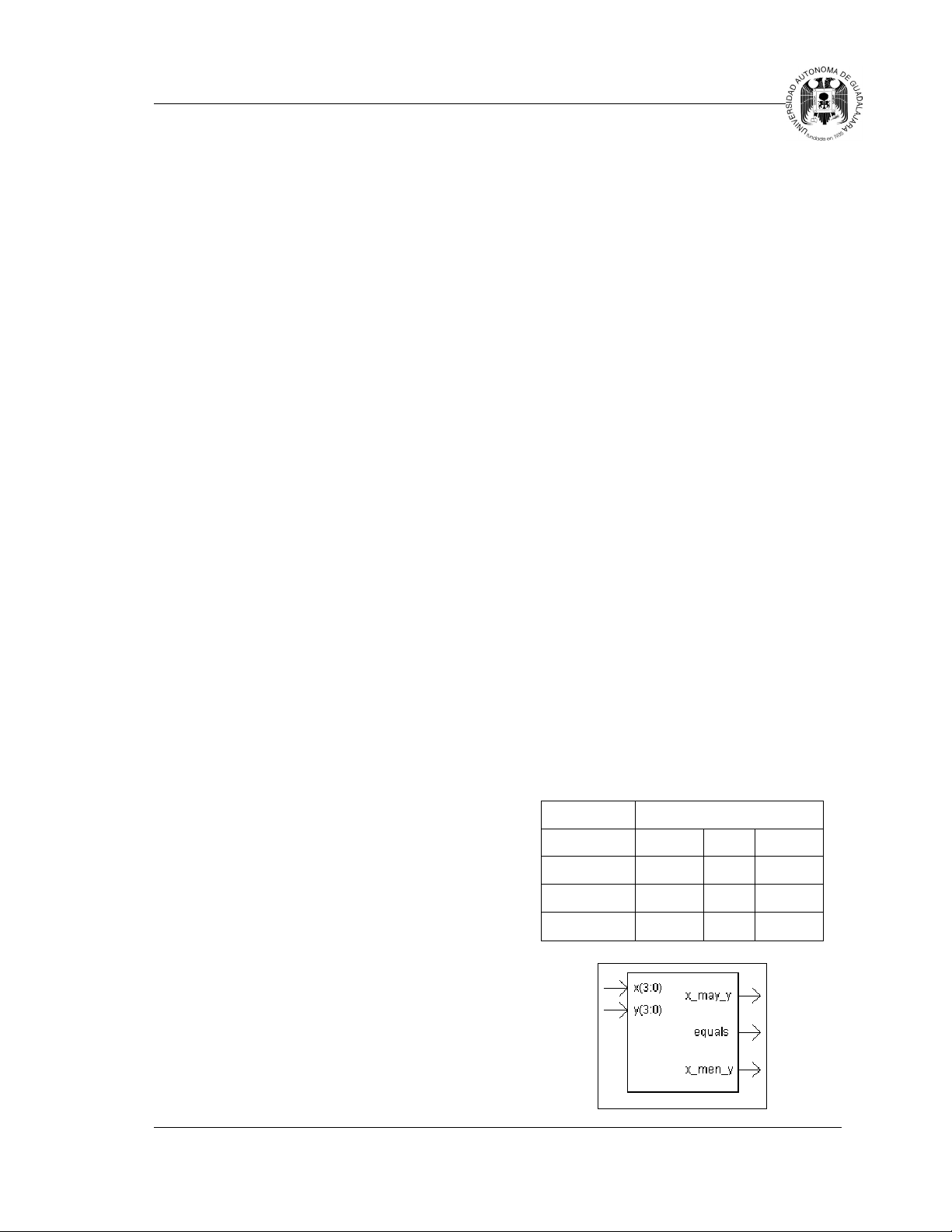

La figura 3.3 representa a un comparador y la

siguiente tabla resume su funcionalidad.

ENTRADAS SALIDAS

x_may_y equals x_men_y

x > y 1 0 0

x = y 0 1 0

x < y 0 0 1

IEC FRANCISCO JAVIER TORRES VALLE

19

Page 26

CAPÍTULO III: SINTAXIS DEL LENGUAJE

Figura 3.3 Comparador

En el diseño convencional de un comparador

tendríamos que realizar una tabla de todos los

posibles valores lógicos de las salidas respecto a

las entradas. Lo cual en este caso sería de 256

combinaciones, dado que tenemos ocho bits de

entrada para obtener las tres ecuaciones de salida.

En VHDL basta con describir de una forma

general el funcionamiento del hardware y el

sintetizador se encargará de generar toda esta

tabla de 256 combinaciones y obtener las

ecuaciones lógicas de las tres salidas. El código

mostrado a continuación corresponde al

comparador mostrado en la figura 3.3.

ENTITY comparador IS

PORT ( x: IN bit_vector (3 DOWNTO 0);

END comparador;

ARCHITECTURE data_flow OF comparador IS

BEGIN

equals <= '1' WHEN x = y ELSE '0';

x_may_y <= '1' WHEN x > y ELSE '0';

x_men_y <= '1' WHEN x < y ELSE '0';

END data_flow;

y: IN bit_vector (3 DOWNTO 0);

equals: OUT bit;

x_may_y: OUT bit;

x_men_y: OUT bit);

Nótese que en la primera declaración de

puertos, dentro de la entidad del comparador, se

definen dos bus de entrada de cuatro bits de

magnitud (x, y), en cambio las salidas son de

solamente un bit. En la entidad lo único que

hacemos es describir como es el circuito, o

aquello del circuito que permite a la entidad

comunicarse hacia otras entidades, sin mencionar

para nada su comportamiento interno. Y es en la

arquitectura, después del BEGIN, es donde se

realiza la descripción del comportamiento del

circuito atendiendo únicamente a la funcionalidad

del mismo, es decir, no es necesario analizar cada

caso en particular de las 256 posibles

combinaciones.

3.1.3 EL ESTILO DE “PROGRAMACIÓN”

N VHDL

E

Haciendo una comparación con un lenguaje de

programación de alto nivel podemos ver que el

código es similar en cuanto a las sentencias

utilizadas, sin embargo, no es así en el flujo de

ejecución de las instrucciones. Un código de

programación en VHDL no es precisamente un

“programa”, ya que un programa es un conjunto

de instrucciones que se ejecutan paso a paso para

llevar a cabo una tarea determinada, y en este

caso no podemos decir que las instrucciones se

estén ejecutando de esta manera, porque esto no

corresponde en la realidad al comportamiento de

un circuito. En VHDL las instrucciones se están

ejecutando en todo momento lo cual sí se asemeja

al comportamiento real de un circuito. Así cuando

cambie alguna señal de entrada cambiará

inmediatamente la salida y, por consiguiente,

estamos describiendo cual es el verdadero

funcionamiento del circuito. La forma en que se

“programa” en VHDL al principio resultará un

tanto extraña, pero si asociamos éste código con

el circuito que estamos describiendo, podemos

darnos cuenta que en él los componentes siempre

están activos, y es esto es precisamente lo que

describimos mediante VHDL. Tal vez alguna vez

ha utilizado PSPICE o algún programa de

entrada esquemática de diseño para modelar y

simular circuitos, estos también son para la

descripción de circuitos. En PSPICE la

descripción se realiza mediante un listado de

conexiones (netlist) entre los componentes, en

tanto que en los otros lo hacemos de manera

gráfica y en ambos se considera que todos los

componentes siempre están funcionando para que

la simulación o modelado del diseño sea de

acuerdo a la realidad. Por esto en VHDL el orden

de las instrucciones no es tan importante como en

el caso de un lenguaje de programación de

software, porque las instrucciones se están

ejecutando al mismo tiempo y así sí se modela

adecuadamente un circuito. Posteriormente se

explicarán los tipos de instrucciones y sus

diferencias, ya que VHDL si permite la

“descripción secuencial” utilizando instrucciones

de esta naturaleza dentro de una estructura

llamada PROCESS. En esta estructura las

instrucciones se ejecutan “paso a paso” como en

los lenguajes de programación de software. Pero

de cualquier manera esta estructura siempre esta

activa, como si fuera un componente o subcircuito

del diseño, por lo que todo lo que se obtenga

dentro del proceso se ejecutará paralelamente con

el resto de las instrucciones que están fuera de

esta estructura.

Otro punto importante es el dispositivo lógico

programable que estemos utilizando, ya que si

éste no tiene la capacidad para realizar lo que

“dice” nuestra descripción nunca podremos

IEC FRANCISCO JAVIER TORRES VALLE

20

Page 27

CAPÍTULO III: SINTAXIS DEL LENGUAJE

sintetizar el código. Por ejemplo, si en el

dispositivo que usemos no es posible que las

salidas puedan ser programadas para que trabajen

con alta impedancia, aún y cuando la descripción

sea correcta nunca podremos sintetizarla en el

dispositivo.

Al principio generalmente se comete el error de

tratar de “programar” como si fuera C++, Pascal,

Visual Basic o cualquier otro lenguaje de

programación de software, además de olvidar que

el PLD, CPLD, o FPGA que utilicemos tiene

características propias que deben ser consideradas

cuando se hace la descripción. Pero basta con

recordar que estamos diseñando hardware y que

por lo tanto no se trata de un lenguaje secuencial

de programación para software.

3.2 IDENTIFICADORES

Un identificador se define como un conjunto de

caracteres con el cual podemos representar

diferentes elementos dentro de una descripción.

En VHDL un identificador está compuesto por

una secuencia de uno o más caracteres

alfabéticos, numéricos, o del carácter de

subrayado. Las condiciones que debe de seguir un

identificador son las siguientes:

• VHDL permite la utilización de las letras

mayúsculas (A.. Z), minúsculas (a.... z),

dígitos (0...9), y el carácter de subrayado (_).

• El primer carácter de un identificador debe

ser una letra.

• El ultimo carácter de identificador no puede

ser el carácter de subrayado. Además, el

carácter de subrayado no puede aparecer dos

o más veces consecutivas.

• Mayúsculas y minúsculas son consideradas

idénticas. Así, Signal_A, signal_a, y

SIGNAL_A se refieren al mismo

identificador.

• Los comentarios en VHDL comienzan con

dos guiones consecutivos (--), y se extienden

hasta el final de la línea. Los comentarios

pueden aparecer en cualquier lugar dentro de

una descripción en VHDL.

• VHDL define un grupo de palabras

reservadas, llamadas "palabras clave"

(keywords), las cuales no pueden ser usadas

como identificadores.

EJEMPLOS

-- Este es un comentario.

ENTITY contador IS -- comentario al final

-- de una línea

Los siguientes ejemplos son de identificadores

válidos en VHDL.

Mi_entidad

Mux4a2

TTL_7490

A continuación se muestran ejemplos de

identificadores no válidos en VHDL.

3er_Modulo -- un identificador no

-- puede iniciar con un

-- dígito

_salida_x -- o con el carácter de

-- subrayado

M__24xmax -- no se permiten dos

-- caracteres de

-- subrayado seguidos

My_design_ -- un identificador no

-- debe terminar con un

-- carácter de subrayado

Unidad& -- el caracter "&", no

-- es un carácter válido

SIGNAL -- palabra reservada

3.3 OBJETOS DE DATOS

Un objeto de datos en VHDL es un elemento

que toma un valor de algún tipo de dato

determinado. Según sea este tipo de dato, el

objeto poseerá un conjunto de propiedades que se

le podrán aplicar, como las operaciones en las que

el objeto puede ser usado. En VHDL los objetos

de datos son generalmente de una de tres clases:

constantes, variables o señales.

3.3.1 CONSTANTES

Una constante es un elemento que puede tomar

un único valor de un tipo dado. A las constantes

se les debe asignar un valor en el momento de la

declaración. Una vez que se le ha asignado algún

valor, éste no puede ser cambiado dentro de la

descripción del diseño. Las constantes pueden ser

IEC FRANCISCO JAVIER TORRES VALLE

21

Page 28

CAPÍTULO III: SINTAXIS DEL LENGUAJE

declaradas dentro de las entidades, arquitecturas,

procesos o paquetes. Las constantes que se

declaren en un paquete pueden ser utilizadas en

cualquier descripción en la que se este utilizando

dicho paquete. Por otra parte las constantes

declaradas dentro de una entidad pueden ser

utilizadas por la o las arquitecturas en las que se

este haciendo la descripción de dicha entidad, y

aquellas constantes que sean declaradas dentro de

una arquitectura o proceso, son válidas

únicamente dentro de la estructura

correspondiente.

D

ECLARACIÓN DE CONSTANTES

CONSTANT identificador: tipo := valor;

EJEMPLO

CONSTANT byte: integer := 8;

3.3.2 VARIABLES

Los objetos de datos de la clase variable son

similares a las constantes, con la diferencia que su

valor puede ser modificado cuando sea necesario.

Las variables en VHDL son similares a cualquier

tipo de variable de un lenguaje de programación

de alto nivel. A las variables también se les puede

asignar un valor inicial al momento de ser

declaradas. Se utilizan únicamente en los

procesos y subprogramas (funciones y

procedimientos). Las variables generalmente se

utilizan como índices, principalmente en

instrucciones de bucle, o para tomar valores que

permitan modelar componentes. Las variables no

representan conexiones o estados de memoria.

DECLARACIÓN DE VARIABLES

VARIABLE identificador: tipo [:=valor];

EJEMPLO

VARIABLE aux1, aux2: bit;

3.3.3 SEÑALES

representan elementos de memoria o conexiones y

si pueden ser sintetizadas.

Los puertos de una entidad son implícitamente

declarados como señales en el momento de la

declaración, ya que estos representan conexiones.

También pueden ser declaradas en las

arquitecturas antes del BEGIN, lo cual nos

permite realizar conexiones entre diferentes

estructuras de programación. La asignación de

valores a un objeto de datos del tipo señal no es

inmediata como en el caso de las variables, esto

se explicará más detalladamente cuando se

exponga la estructura PROCESS y los tipos de

instrucciones.

DECLARACIÓN DE SEÑALES

SIGNAL identificador: tipo [:=valor];

EJEMPLOS

SIGNAL A, B: bit := '0'; -- el valor

-- inicial es

-- opcional

SIGNAL dato: bit_vector (7 DOWNTO 0);

3.3.4 ALIAS

Un ALIAS no es precisamente un objeto de

datos. La instrucción ALIAS permite que

utilicemos un identificador diferente para hacer

referencia a un objeto de datos, o a parte de él, ya

existente. Este no es un objeto de datos nuevo,

sino que nos permite manipular fragmentos del

objeto de datos original para facilitar la

programación. Al modificar el ALIAS se

modifica el objeto de datos al que señala.

DECLARACIÓN DE ALIAS

ALIAS identif: tipo IS identif2 <rango>;

EJEMPLO

ALIAS instr: bit_vector (3 DOWNTO 0) IS

dato (7 DOWNTO 4);

Un objeto de la clase señal es similar a un

objeto de la clase variable, con una importante

diferencia: las señales si pueden almacenar o

pasar valores lógicos, mientras que una variable

no lo puede hacer. Las señales, por lo tanto,

IEC FRANCISCO JAVIER TORRES VALLE

3.4 TIPOS DE DATOS

Un tipo de dato especifica el grupo de valores

que un objeto de datos puede tomar así como las

operaciones que son permitidas con esos valores.

En VHDL es sumamente importante el tipo de

22

Page 29

CAPÍTULO III: SINTAXIS DEL LENGUAJE

dato, los objetos de datos no pueden tomar o no se

les puede asignar un objeto de datos de otro tipo,

y no todas las operaciones se pueden utilizar con

los diferentes tipos de datos a menos que se

utilicen las librerías adecuadas en las que estén

definidas funciones para la conversión de tipos.

Además, es posible que el usuario defina subtipos

y tipos compuestos, modificando los tipos

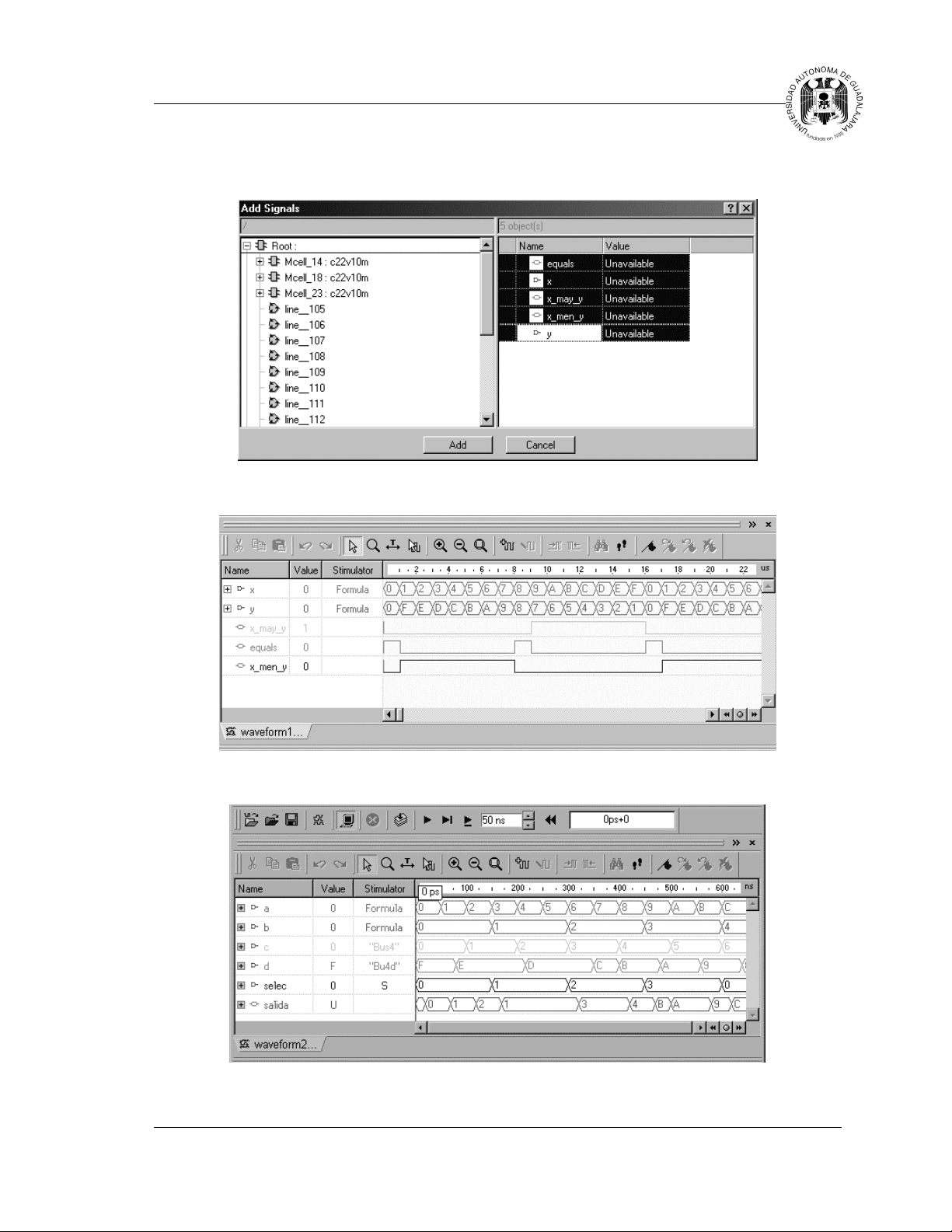

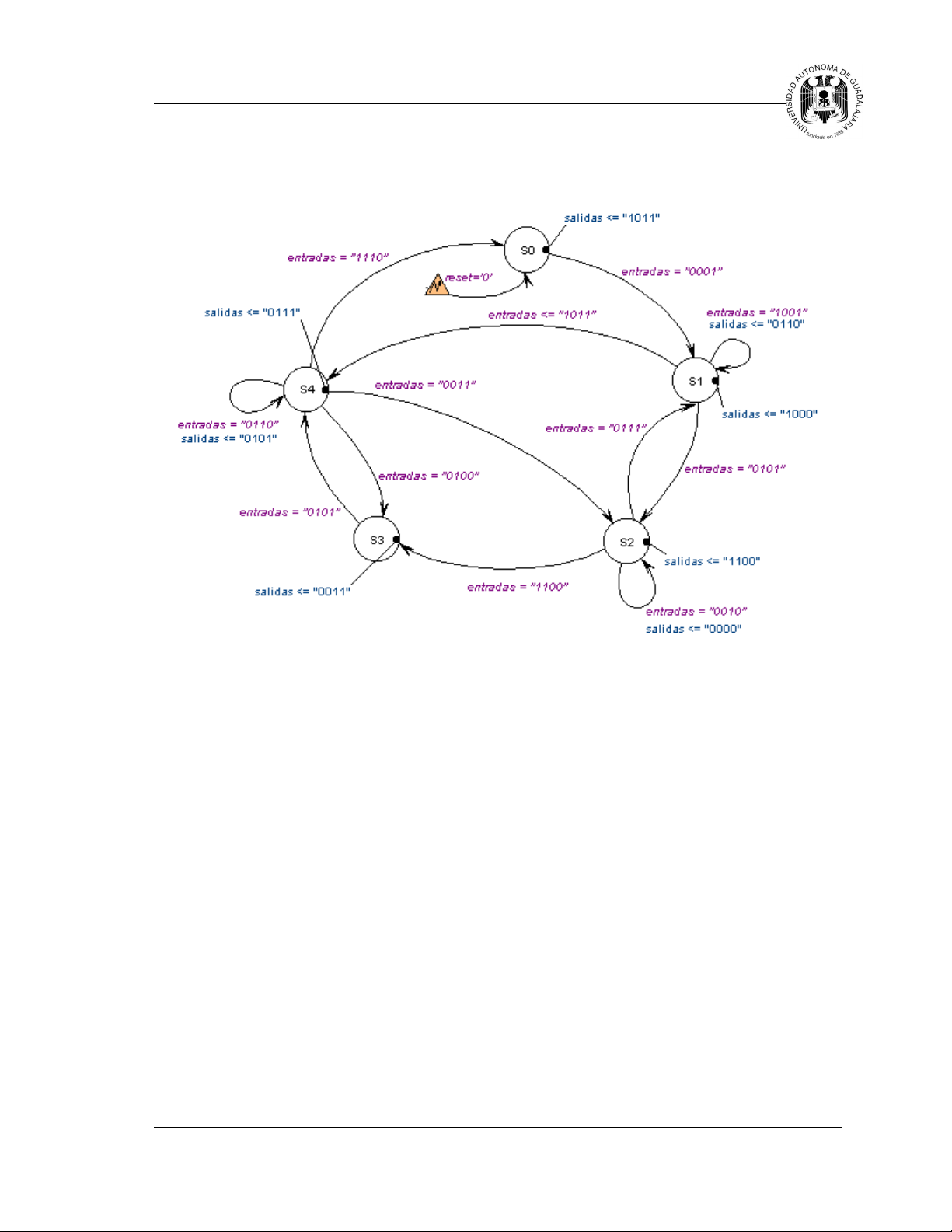

básicos, así como definir tipos particulares con