Page 1

Tsi310

User Manual

80B6020_MA001_05

®

IDT

™

PCI-X® Bridge

September 2009

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

©2009 Integrated Device Technology, Inc.

Printed in U.S.A.

Page 2

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance

and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The

Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

GENERAL DISCLAIMER

Code examples provided by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of the code examples below is completely

at your own risk. IDT MAKES NO REPRESENT ATIONS OR WARRANTIES OF ANY KIND CONCERNING THE NONINFRINGEMENT, QUALITY, SAFETY OR SUITABILITY

OF THE CODE, EITHER EXPRESS OR IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. FURTHER, IDT MAKES NO REPRESENT ATIONS OR WARRANTIES AS TO THE TRUTH, ACCURACY OR COMPLETENESS

OF ANY STATEMENTS, INFORMATION OR MATERIALS CONCERNING CODE EXAMPLES CONTAINED IN ANY IDT PUBLICATION OR PUBLIC DISCLOSURE OR

THAT IS CONTAINED ON ANY IDT INTERNET SITE. IN NO EVENT WILL IDT BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, I NCIDENTAL, INDIRECT, PUNITIVE OR

SPECIAL DAMAGES, HOWEVER THEY MAY ARIS E, AND EVEN IF IDT HAS BEEN PREVIOUSLY ADVISED ABOUT THE POSSIBILITY OF SUCH DAMAGES. The code

examples also may be subject to United States export control laws and may be subject to the export or import laws of other countries and it is your responsibility to comply with

any applicable laws or regulations.

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to

such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform,

when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device

or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

CODE DISCLAIMER

LIFE SUPPORT POLICY

Page 3

Contents

About this Document. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Document Conventions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

Related Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1. Functional Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.1 Overview of the Tsi310 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.2 Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.1 PCI-X Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.2 Memory Buffer Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.3 Power Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.2.4 Transaction Forwarding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.5 Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

3

1.2.6 Optional Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.7 Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.2.8 IEEE

®

1149.1 JTAG Port . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.3 Operation Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.3.1 Supported Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.3.2 Buffer Structure. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.3.3 Address Decoding. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

1.3.4 Bus Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

1.4 Technology Highlights . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

2. Bus Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.1 Overview of Bus Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

2.1.1 Types of Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

2.2 Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.2.1 Posted Write Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

2.2.2 Delayed/Split Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.2.3 Immediate Write Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

2.3 Read Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.3.1 Memory Read Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

2.3.2 I/O Read . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

2.3.3 Configuration Read. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Tsi310 User Manual

80B6020_MA001_05

Page 4

Contents4

2.3.4 Non-Prefetchable and DWord Reads. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .35

2.3.5 Prefetchable Reads . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

2.4 Configuration Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .37

2.4.1 Configuration Type 0 Access to Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

2.4.2 Type 1 to Type 0 Translation by Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

2.4.3 Type 1 to Type 1 Forwarding by Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

2.4.4 Special Cycle Generation by the Bridge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

3. Clocking and Reset Options. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .45

3.1 Clocking Domains. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

3.2 Clock Jitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.3 Mode and Clock Frequency Determination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 46

3.3.1 Primary Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .46

3.3.2 Secondary Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

3.4 Clock Stability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .48

3.5 Driver Impedance Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .49

3.6 Reset Functions and Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.6.1 Primary Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

3.6.2 Secondary Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .51

3.7 Bus Parking and Bus Width Determination . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

3.8 Power Management and Hot-Plug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .54

3.9 Secondary Device Masking. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.10 Handling of Address Phase Parity Errors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .55

3.11 Optional Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

3.12 Optional Configuration Register Access from the Secondary Bus. . . . . . . . . . . . . . . . . . . . . . . .56

3.13 Short Term Caching . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

4. Transaction Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .59

4.1 Overview of Transaction Ordering . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.2 General Ordering Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

4.3 Ordering Rules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

5. Configuration Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

5.1 Overview of Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

5.1.1 Terms and Abbreviations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .63

5.1.2 Configuration Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

5.1.3 Type 1 PCI Configuration Space Header . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .64

5.2 Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Tsi310 User Manual

80B6020_MA001_05

Page 5

Contents 5

5.3 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

5.4 PCI Configuration Space Header Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.4.1 Vendor ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

5.4.2 Device ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

5.4.3 Command Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

5.4.4 Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 75

5.4.5 Revision ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.4.6 Class Code Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

5.4.7 Cache Line Size Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 78

5.4.8 Latency Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 79

5.4.9 Header Type Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.4.10 BIST Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 80

5.4.11 Lower Memory Base Address Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

5.4.12 Upper Memory Base Address Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

5.4.13 Primary Bus Number Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

5.4.14 Secondar y Bus Number Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

5.4.15 Subordinate Bus Number Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

5.4.16 Secondary Latency Timer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

5.4.17 I/O Base Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 88

5.4.18 I/O Limit Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

5.4.19 Secondary Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

5.4.20 Memory Base Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 92

5.4.21 Memory Limit Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

5.4.22 Prefetchable Memory Base Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

5.4.23 Prefetchable Memory Limit Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

5.4.24 Prefetchable Base Upper 32 Bits Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

5.4.25 Prefetchable Limit Upper 32 Bits Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

5.4.26 I/O Base Upper 16 Bits Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

5.4.27 I/O Limit Upper 16 Bits Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

5.4.28 Capabilities Pointer Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

5.4.29 Reserved Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

5.4.30 Interrupt Line Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.4.31 Interrupt Pin Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

5.4.32 Bridge Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

5.5 Device-Specific Configuration Space Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

5.5.1 Primary Data Buffering Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Tsi310 User Manual

80B6020_MA001_05

Page 6

Contents6

5.5.2 Secondary Data Buffering Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

5.5.3 Miscellaneous Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

5.5.4 Arbiter Mode Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

5.5.5 Arbiter Enable Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

5.5.6 Arbiter Priority Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

5.5.7 SERR# Disable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

5.5.8 Primary Retry Counter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1 21

5.5.9 Secondary Retry Counter Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .123

5.5.10 Discard Timer Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 125

5.5.11 Retry and Timer Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 127

5.5.12 Opaque Memory Enable Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 128

5.5.13 Opaque Memory Base Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 129

5.5.14 Opaque Memory Limit Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 130

5.5.15 Opaque Memory Base Upper 32 Bits Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 131

5.5.16 Opaque Memory Limit Upper 32 Bits Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 132

5.5.17 PCI-X ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 133

5.5.18 Next Capabilities Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 134

5.5.19 PCI-X Secondary Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 135

5.5.20 PCI-X Bridge Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .137

5.5.21 Secondary Bus Upstream Split Transaction Register . . . . . . . . . . . . . . . . . . . . . . . . .140

5.5.22 Primary Bus Downstream Split Transaction Register. . . . . . . . . . . . . . . . . . . . . . . . .141

5.5.23 Power Management ID Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

5.5.24 Next Capabilities Pointer Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 142

5.5.25 Power Management Capabilities Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 143

5.5.26 Power Management Control/Status Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 144

5.5.27 PCI-to-PCI Bridge Support Extensions Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

5.5.28 Data Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 145

5.5.29 Secondary Bus Private Device Mask Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .146

5.5.30 Miscellaneous Control Register 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 148

6. Signals and Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .151

6.1 Overview of Signals and Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

6.2 Primary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

6.3 Secondary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .154

6.4 Strapping Pins and Other Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

6.5 Test Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

6.6 Power and Ground Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .161

Tsi310 User Manual

80B6020_MA001_05

Page 7

Contents 7

6.6.1 Filter Requirements for P_VDDA and S_VDDA . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

6.7 Pinout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 163

6.7.1 Pinout — Sorted by Signal Name. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

6.7.2 Pinout — Sorted by Grid Position . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

7. JTAG Boundary Scan. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

7.1 Overview of JTAG Boundary Scan . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

7.2 TAP Controller Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

7.3 JTAG Design Considerations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

7.3.1 Including the Tsi310 in a JTAG Scan Ring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

7.3.2 Excluding the Tsi310 from a JTAG Scan Ring. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

7.4 Instruction Register and Codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.5 Bypass Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

7.6 JTAG Device ID Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

7.7 Boundary Scan Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 174

7.7.1 Boundary Scan Register Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

8. Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

8.1 PCI/PCI-X Specification Conformance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 191

8.2 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

8.3 Recommended DC Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

8.4 AC Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

8.5 Power Dissipation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

9. Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

9.1 Package Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

9.2 Thermal Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

A. Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

A.1 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Index . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 203

Tsi310 User Manual

80B6020_MA001_05

Page 8

Contents8

Tsi310 User Manual

80B6020_MA001_05

Page 9

List of Figures

Figure 1: Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Figure 2: Configuration Transaction Address Formats . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Figure 3: Programmable Pull-up Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Figure 4: De-assertion of S_RST# . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 52

Figure 5: Filter Requirements for P_VDDA and S_VDDA. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Figure 6: Inductor L1 Impedance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Figure 7: Pinout — Viewed from Above (Looking Through the Device). . . . . . . . . . . . . . . . . . . . . . . . . 163

Figure 8: Package Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 198

9

Tsi310 User Manual

80B6020_MA001_05

Page 10

List of Figures10

Tsi310 User Manual

80B6020_MA001_05

Page 11

List of Tables

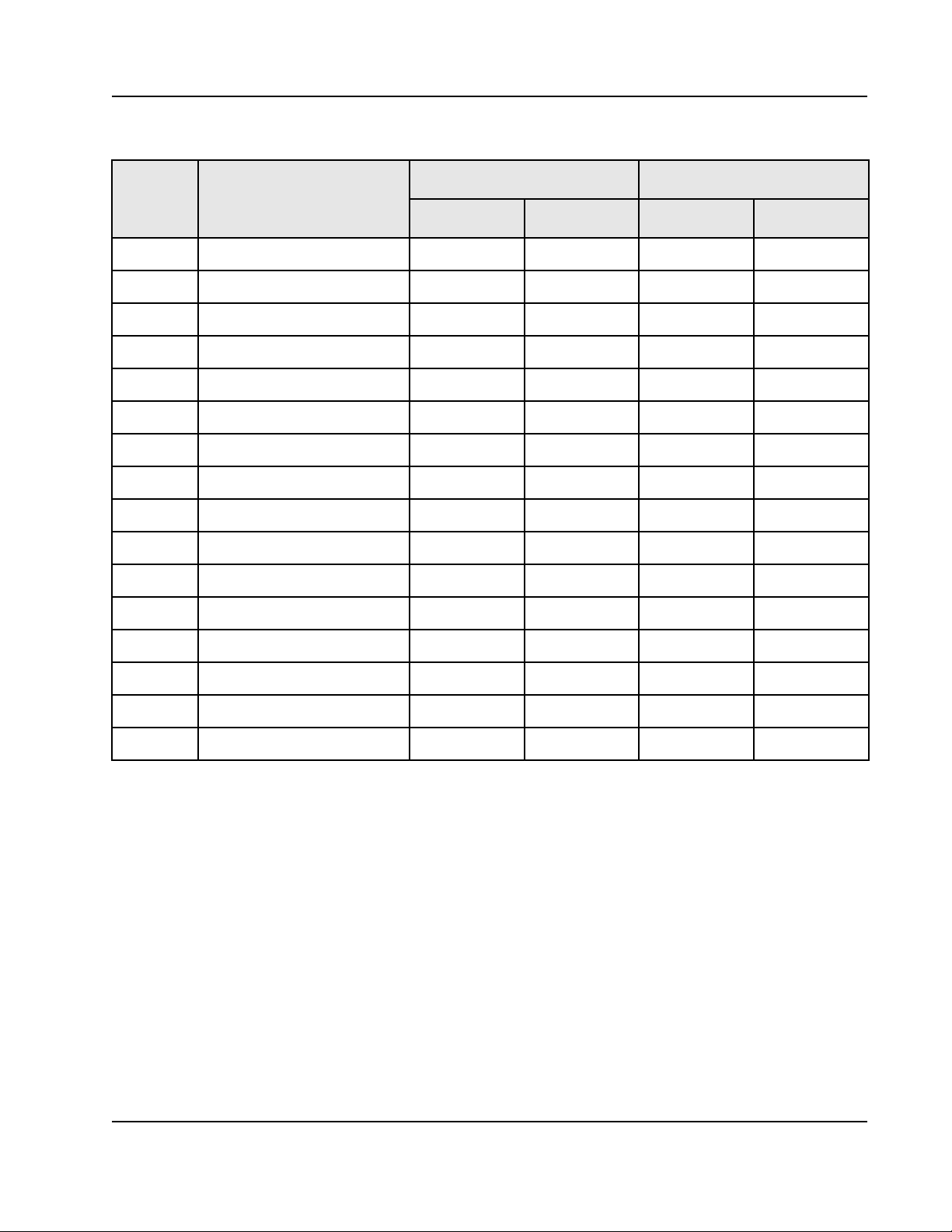

Table 1: PCI Transactions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Table 2: PCI-X Transactions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Table 3: Write Transaction Handling . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Table 4: Read Transaction Handling. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Table 5: IDSEL Generation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Table 6: Driver Impedance Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

Table 7: Delay Times for De-assertion of S_RST#. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Table 8: Tsi310 Ordering Rules — PCI-X Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Table 9: Tsi310 Ordering Rules — PCI Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Table 10: Register Terms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

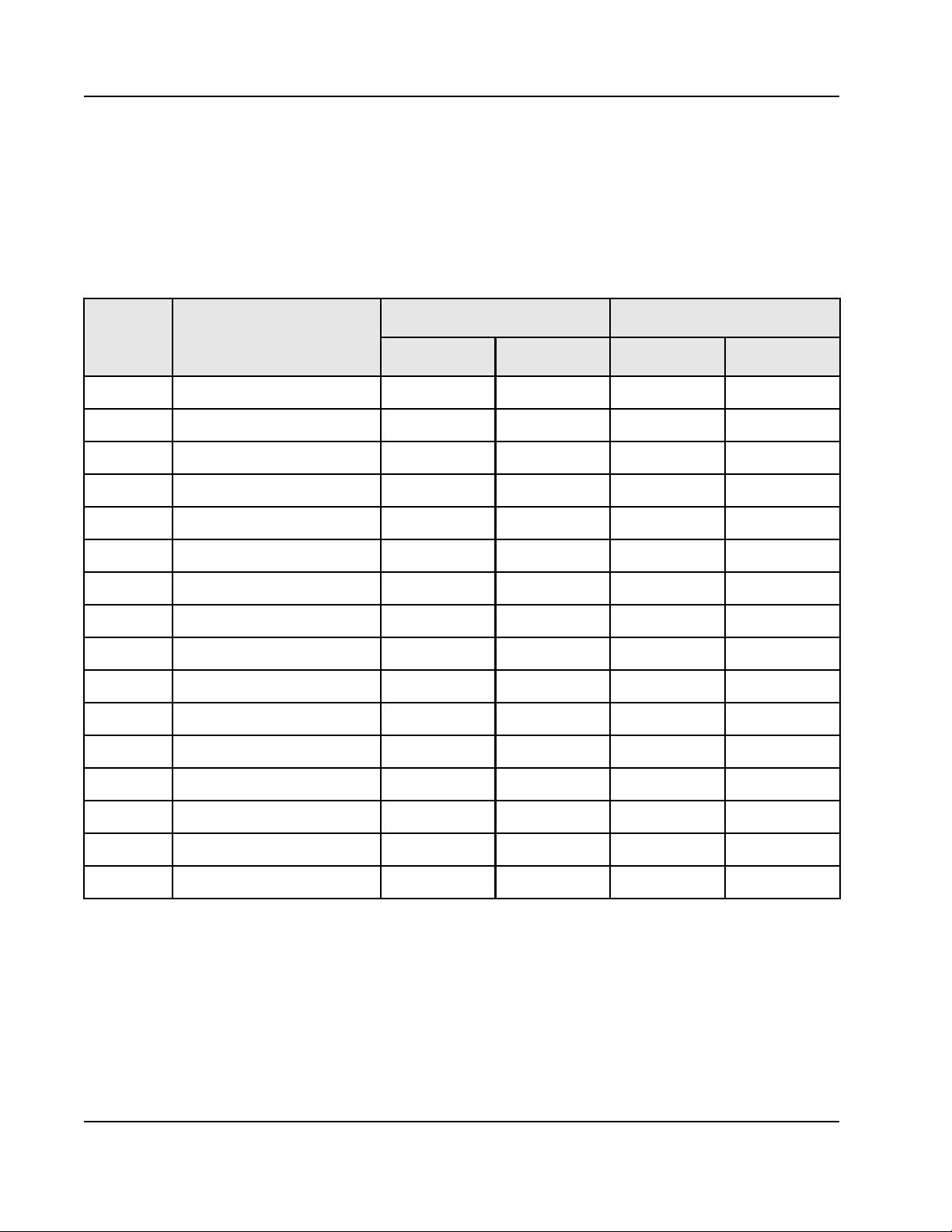

Table 11: Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 65

Table 12: Register Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

11

Table 13: Primary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 151

Table 14: Secondary Interface Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 154

Table 15: Strapping Pins and Other Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 157

Table 16: Test Signals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

Table 17: Power and Ground Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

Table 18: Inductor L1 Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

Table 19: Signal Pin Listing by Signal Name . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

Table 20: Signal Pin Listing by Grid Position. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Table 21: JTAG Logic Instruction Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 173

Table 22: Boundary Scan Register Bit Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 175

Table 23: Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 192

Table 24: Recommended DC Operating Conditions (T

Table 25: AC Operating Conditions (T

= 0 to 70°C). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

A

= 0 to 70°C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

A

Table 26: Tsi310 Power Dissipation (Total = I/O + Core) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

Table 27: Package Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

Table 28: Package Thermal Resistance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 199

Table 29: Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 201

Tsi310 User Manual

80B6020_MA001_05

Page 12

List of Tables12

Tsi310 User Manual

80B6020_MA001_05

Page 13

About this Document

This chapter discusses general document information about the Tsi310 PCI-X Bus Bridge User

Manual. The following topics are described:

• “Revision History” on page 13

• “Document Conventions” on page 14

• “Related Information” on page 17

Revision History

80B6020_MA001_05, Formal, September 2009

13

This version of the document was rebranded as IDT. It does not include any technical changes.

80B6020_MA001_04, Formal, December 2004

This document was updated to address the following changes:

• Added maximum rating information for V

• Revised V

conditions (see Section 8.3 on page 193)

• Added power dissipation numbers (see Section 8.5 on page 194)

• Added part ordering information for Pb-free Tsi310 (see Section A on page 201)

(Maximum) and V

IL

(Minimum) numbers for Recommended DC operating

IH

(Input voltage) (see Section 8.2 on page 192)

IN

80B6020_MA001_03, Formal, June 2004

This document was updated to incorporate a non-technical change.

80B6020_MA001_02, Formal, March 2004

This document was updated to incorporate several non-technical changes.

Tsi310 User Manual

80B6020_MA001_05

Page 14

80B6020_MA001_01, Formal, February 2004

This document supports the Tsi310 (part numbers Tsi310A-133CE and Tsi310-133CE). For

information about the differences between these devices, see the Tsi310 Differences Document.

This document differs from the 80B6000_MA001_03 user manual in the following ways:

• Updated the Revision ID number (see Section 5.4.5 on page 77)

• Revised the explanation of the Secondary Retry Counter Register (see Section 5.5.9 on

page 123)

• Added a note about the P_CFG_BUSY signal (see Table 15 on page 157)

• Revised the reset value for the JTAG Device ID register (see Section 7.6 on page 174)

• Added a caution note in the Hot plug section about powering up Tsi310’s I/O pads (see

Section 3.8 on page 54)

• Revised the 1111 PCI command code row in Table 1 on page 28

• Added a new bullet in the section describing PCI commands not supported by the Tsi310

(see Section 2.1.1 on page 28)

14

• Added more information about PCI-to-PCI transactions (see Section 2.2.1.3 on page 31)

Document Conventions

This section explains the document conventions used in this manual.

Signal Notation

Signals are either active high or active low. Active low signals are defined as true (asserted)

when they are at a logic low. Similarly, active high signals are defined as true at a logic high.

Signals are considered asserted when active and negated when inactive, irrespective of voltage

levels. For voltage levels, the use of 0 indicates a low voltage while a 1 indicates a high voltage.

Signals that assume a logic low state when asserted are followed by a number sign as the last

non-numerical character “#” (for example, SIGNAL#). Signals that assume a logic high state

are not followed by an underscore character (for example, SIGNAL).

Tsi310 User Manual

80B6020_MA001_05

Page 15

15

Bit Ordering Notation

When referring to PCI-X transactions, this document assumes the most significant bit is the

largest number (also known as little-endian bit ordering). For example, the PCI address/data bus

consists of AD[31:0], where AD[31] is the most significant bit and AD[0] is the least-significant

bit of the field (see the following graphic).

msb

313029282726252423222120191817161514131211109876543210

lsb

Object Size Notation

The following object size conventions are used for PCI/X transactions:

•A byte is an 8-bit object.

•A word is a 16-bit (2-byte) object.

•A doubleword (Dword) is a 32-bit (4-byte) object.

•A quadword is a 64-bit (8-byte) object.

Numeric Notation

The following numeric conventions are used:

• Hexadecimal values are in single quotation marks and are preceded by an x. For example:

x‘0B00’.

• Undefined hexadecimal values are indicated by a capital X. For example: x’X1’ =

undefined on reset.

• Binary values are spelled out (zero and one) or appear in single quotation marks and are

preceded by b. For example: b‘0101’.

Typographic Notation

The following italic typographic conventions are used in this manual:

• Book titles: For example, PCI Local Bus Specification (Revision 2.2).

• Important terms: For example, when a device is granted access to the PCI bus it is called

the bus master.

• Undefined values: For example, the device supports four channels depending on the setting

of the Ax register.

Tsi310 User Manual

80B6020_MA001_05

Page 16

Units of Measure

Tip

The following units of measure are used in this manual:

• Prefixes: K=1024, k=1000

• Bits and bytes: An uppercase “B” stands for bytes. For example, 1 KB means 1024 bytes.

• A lowercase “b” refers to bits. For example, 1 Kb means 1024 bits.

Symbols Used

The following symbols are used in this manual:

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or

damage to the device.

16

This symbol indicates a basic design concept or information considered helpful.

Document Status Information

“Tsi” technical documentation is classified as either Advance, Prelim inary, or Final:

• Advance: The Advance manual contains information that is subject to change and exists

until prototypes are available.

• Preliminary: The Preliminary manual contains information about a product that is near

production-ready , and is revised as required. The Preliminary manual exists until the

product is released to production.

• Formal: The Final manual contains information about a final, customer-ready product. This

type of manual can be downloaded from our website once the product is released to

production.

Tsi310 User Manual

80B6020_MA001_05

Page 17

17

Related Information

The following information is useful for reference purposes when using this manual:

PCI Local Bus Specification

(Revision 2.2)

PCI-X Addendum to PCI Local

Bus Specification (Revision 1.0a)

PCI-to-PCI Bridge Architecture

Specification (Revision 2.0)

PCI Bus Power Management

Interface Specification

(Revision 2.0)

This document defines the PCI hardware system including

the protocol, electrical, mechanical and configuration

specification for the PCI local bus components and

expansion boards. For more information, see

www .pcisig.com.

This document addresses the need for increased

bandwidth of PCI Devices. PCI-X enables the design of

systems and devices that can operate at speeds

significantly higher than today's specification allows. For

more information, see www.pcisig.com.

This document establishes the minimum behavioral

requirements that PCI-to-PCI bridges must meet to be

compliant to the PCI Local Bus Specification

(Revision 2.2). Recommendations and guidance on

optional PCI-to PCI bridge features are also provided by

this specification. For more information, see

www .pcisig.com.

This document defines power management capabilities

that enhance the base PCI architecture. For more

information, see www.pcisig.com.

Tsi310 User Manual

80B6020_MA001_05

Page 18

18

Tsi310 User Manual

80B6020_MA001_05

Page 19

1. Functional Overview

This chapter describes the main features and functions of the Tsi310. The following topics are

discussed:

• “Overview of the Tsi310” on page 19

• “Features” on page 22

• “Technology Highlights” on page 26

• “Operation Overview” on page 24

1.1 Overview of the Tsi310

The Tsi310 transparently connects two electrically separate PCI-X bus domains, allowing

concurrent operations on both buses. This results in good utilization of the buses in various

system configurations and enables hierarchical expansion of I/O bus structures.

19

As described by the PCI-X architecture, the Tsi310 is capable of handling 64-bit data at a

maximum bus frequency of 133 MHz (depending upon the bus topology and load) and is

backward compatible with all 3.3V I/O conventional PCI interfaces.

The Tsi310 also provides extensive buffering and prefetching mechanisms for efficient transfer

of data through the device, facilitating multi-threaded operation and high system throughput.

Tsi310 User Manual

80B6020_MA001_05

Page 20

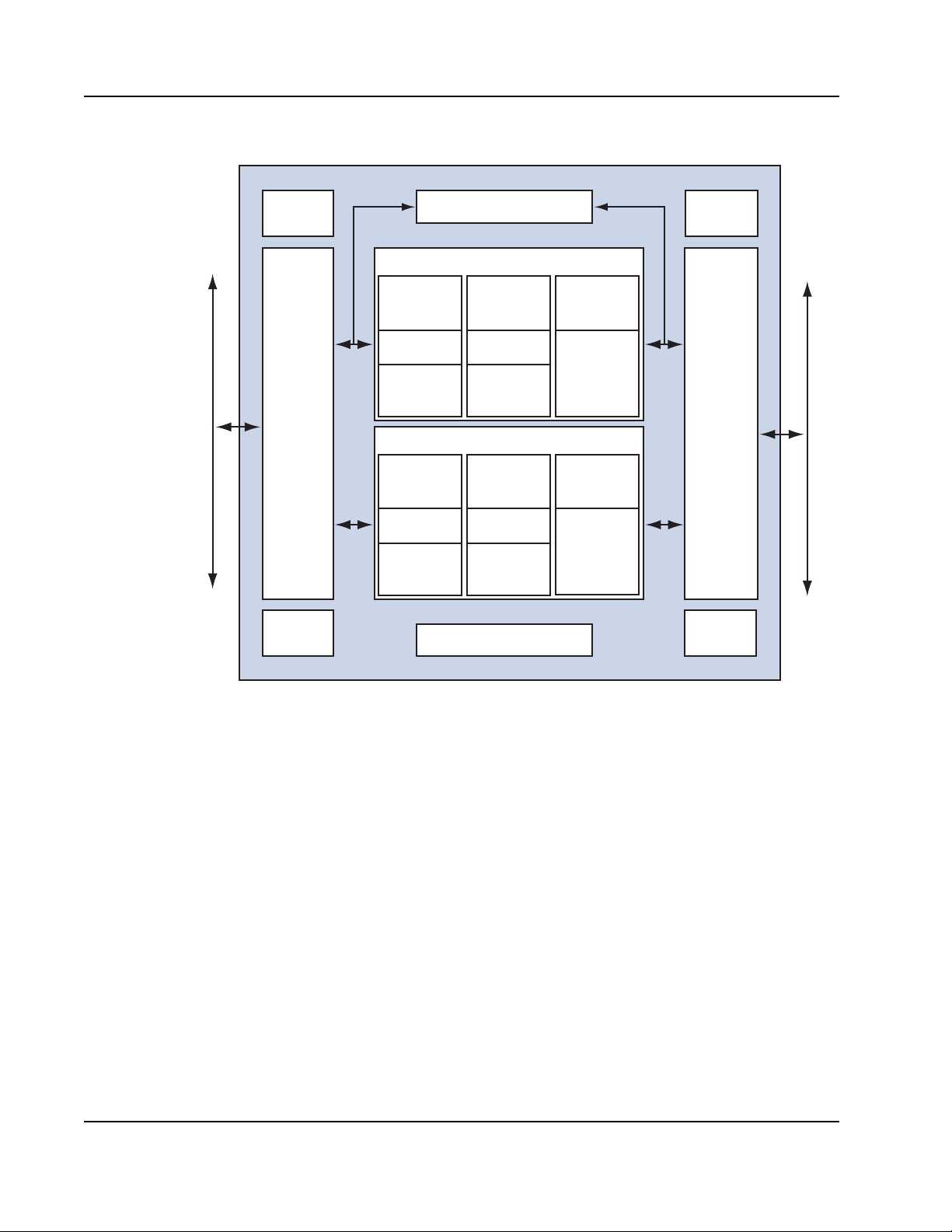

Figure 1: Block Diagram

Primary PCI/PCI-X Bus

Secondary PCI/PCI-X Bus

80B6000_BK001_02

JTAG

Secondary

Bus Arbiter

Primary

Clock PLL

Secondary

Clock PLL

PCI-X

Interface

Bus

Master

Bus

Slave

PCI-X

Interface

Configuration Registers

Clocking & Reset

Data/Control Unit

Queue

Compare

Logic

Read Queue

8 entries

PW Queue

8 entries

Address

Decode

Control

Logic

Burst Read

Buffer

4 Kbytes

Posted Write

Buffer

1 Kbyte

Single Data

Phase Buffer

4 Bytes

Data/Control Unit

Queue

Compare

Logic

Read Queue

8 entries

PW Queue

8 entries

Address

Decode

Control

Logic

Burst Read

Buffer

4 Kbytes

Posted Write

Buffer

1 Kbyte

Single Data

Phase Buffer

4 Bytes

Bus

Slave

Bus

Master

1. Functional Overview20

Tsi310 User Manual

80B6020_MA001_05

The Tsi310 is composed of the following major functional blocks (see Figure 1):

• The device has two PCI-X interfaces. Each interface handles the PCI/PCI-X protocol for its

respective bus and depending on the type of transaction, can act as either a bus master or a

bus slave. These interfaces transfer data and control information flowing to and from the

blocks shown in the middle of the diagram.

• Two phase-locked loops (PLLs), one for the primary clock domain and one for the

secondary clock domain. The PLL for each clock domain is used when that bus is running

in PCI-X mode; in PCI mode, the PLL is bypassed to allow the full frequency range as

defined by the bus architecture. The two bus clocks may be run synchronously or

asynchronously. A spread-spectrum clock input, within the architectural bounds, is

supported for either or both interfaces.

• One set of configuration registers, programmable either from the primary or secondary

interface. The first 64 bytes of this address space conform to the architectural format for

bridge devices, called Header Type 1. The remaining 192 bytes are device-specific

registers. Each register is fully defined in Section 5.1.2 on page 64.

Page 21

1. Functional Overview 21

• T wo data/control units, one for downstream transactions and one for upstream transactions.

These symmetric units each contain separate buffers for burst read, posted write, and single

data phase operations. Read and write queues, queue compare logic, address decoding,

control logic, and other control functions are also included in these blocks.

• An arbiter for the secondary bus, which can be disabled if an external arbiter is employed.

When enabled, bus arbitration is provided for the Tsi310 and up to six other masters. Each

client can be assigned high or low priority, or can be masked off.

• A clocking and reset control unit to manage these common device functions.

• A JTAG controller, compliant with IEEE Standard 1149.1, to facilitate boundary scan

testing.

Tsi310 User Manual

80B6020_MA001_05

Page 22

1.2 Features

The Tsi310 has the following key features:

1.2.1 PCI-X Interfaces

• Complies with the following specifications:

— PCI Local Bus Specification (Revision 2.2)

— PCI-to-PCI Bridge Architecture Specification (Revision 2.0)

— PCI-X Addendum to PCI Local Bus Specification (Revision 1.0a)

• Uses the 3.3V signaling environment and does not support the optional 5 V I/O signaling

levels

• Primary and secondary interface clocks may be run synchronously or asynchronously

• Concurrent primary and secondary bus operations

• Supports configurations of PCI mode or PCI-X mode on either bus in any combination

1. Functional Overview22

1.2.2 Memory Buffer Architecture

• 4KB of buffering for upstream memory burst read commands, with up to eight active

transactions allowed

• 4KB of buffering for downstream memory burst read commands, with up to eight active

transactions allowed

• 1KB of buffering for upstream posted memory write commands, with up to eight active

transactions allowed

• 1KB of buffering for downstream posted memory write commands, with up to eight active

transactions allowed

• Allows one active single data phase (4-byte) delayed or split transaction in each direction

1.2.3 Power Management

• Supports D0 and D3 power states

Tsi310 User Manual

80B6020_MA001_05

Page 23

1. Functional Overview 23

1.2.4 T ransaction Forwarding

• I/O, Memory, and Prefetchable Memory base and limit registers for downstream

forwarding

• Inverse address decoding for upstream forwarding

• Flat addressing model

• Supports VGA-compatible addressing and palette snooping for upstream transactions

• Supports full 64-bit addressing and Dual Address Cycles

• Responds as medium-speed device on both interfaces

1.2.5 Configuration Registers

• 1 set of standard PCI and device specific configuration registers, accessible from both the

primary and secondary interfaces

• Supports Type 0 and Type 1 configuration cycles

1.2.6 Optional Features

• Capable of defining an optional opaque (undecoded) memory address region to facilitate

applications with embedded processors

• Supports secondary side PCI-X device privatization

• Optional Definable Base Address Register for use by embedded sub-systems on the

secondary bus

• Optional access to configuration register space from the secondary bus

1.2.7 Bus Arbitration

• On-chip programmable bus arbiter for the secondary bus with support for up to six external

masters

• Priority and masking control for each agent

1.2.8 IEEE® 1149.1 JTAG Port

• Performs boundary-scan testing

Tsi310 User Manual

80B6020_MA001_05

Page 24

1.3 Operation Overview

This section briefly describes the operation of various aspects of the Tsi310. For more

information on each topic, refer to subsequent chapters.

1.3.1 Supported Modes

The Tsi310 is a full-function transparent PCI-X to PCI-X bridge. As such, either interface may

be configured to operate using the conventional PCI bus protocol or the PCI-X bus protocol. In

mixed-mode configurations, the Tsi310 hardware handles the conversion from one protocol to

the other.

Any allowed bus clock frequency range for a particular mode may be used: up to 66 MHz for

PCI mode, and up to 133 MHz for PCI-X mode. Operation at a particular speed depends on the

bus topology and loading. Since the two clock domains are asynchronous and independent, a

different bus speed may be used on each interface. Speed-matching is accomplished using the

buffering structure of the Tsi310 design.

The Tsi310 implements a 64-bit bus on both interfaces. The PCI architecture also allows either

side to be connected to a 32-bit bus or to 32-bit devices. Full 64-bit addressing capability is also

provided, including support for dual address cycles (DAC).

1. Functional Overview24

The Tsi310 uses the 3.3V signaling environment and is not tolerant of 5V signal

levels. When the Tsi310 is mounted on an adapter card, the card must use the 3.3V

connector keying scheme.

1.3.2 Buffer Structure

The Tsi310 contains two symmetric sets of buffers with associated queues, one for upstream

transactions and the other for downstream transactions.

1.3.2.1 Burst Read Buffers

Each burst read buffer shown in Figure 1 on page 20 contains 4 KB to hold data from memory

burst read transactions. Each buffer is logically divided into eight independent 512 -by te bu ffers

to allow for multi-threading. Each 512-byte buffer has a read queue providing up to eight active

read transactions in each direction.

Tsi310 User Manual

80B6020_MA001_05

Page 25

1. Functional Overview 25

Every 512-byte buffer is further divided into four 128-byte subsections. Activity generally

occurs on these 128-byte boundaries. Filling and/or emptying 128 bytes causes bus transactions

to be initiated. While each read queue entry has up to 512 bytes of buffer space associated with

it, to keep data flowing efficiently the 128-byte subsections are re-used as needed when they are

emptied. This means that when the primary and secondary interfaces are running at similar

frequencies and there is little bus contention, long transfers can proceed without disconnection,

after the initial latency needed to fill the first 128-byte subsection. For large transfers when the

two buses are running at vastly dissimilar frequencies, disconnections may occur on the faster

bus as often as every 128 bytes as the 512-byte buffer becomes completely full or empty.

1.3.2.2 Posted Write Buffers

The posted write buffers each have a capacity of 1 KB to hold data from posted memory write

transactions. Each is logically divided into eight independent 128-byte segments to allow

transactions to be issued on the destination bus before they have been completed on the

originating bus. Unlike the burst read buffers, the amount of space assigned to each transaction

is dynamic. A single transaction can utilize from one to eight 128-byte subsections as needed.

Each posted write queue is an 8-entry FIFO, providing up to eight active write transactions in

each direction. Activity generally occurs when a 128-byte segment is filled or emptied, this

keeps data flowing by re-using 128-byte subsections as they become available.

1.3.2.3 Single Data Phase Buffers

There is one single data phase buffer for each direction to hold read or write data from 4-byte

split or delayed transactions. These transactions include all I/O or configuration operations as

well as doubleword memory read operations.

1.3.3 Address Decoding

The Tsi310 is a transparent bridge that uses a flat addressing model. Both the PCI and PCI-X

address spaces are split between the primary bus and the secondary bus. Address ranges residing

on the secondary bus are defined by the I/O, memory, prefetchable memory base and limit, and

the optional base address registers 0 and 1 in the bridge configuration space. All other addresses

are assumed to reside on the primary bus. Inverse address decoding determines when to forward

transactions upstream. The only exception is when the optional opaque address range is enabled

and defined by T si310’s base and limit registers. The T si310 does not recognize transactions for

addresses within the opaque range on either bus. This region may be used, for example, for

peer-to-peer communication between devices on the secondary bus.

The Tsi310 supports full 64-bit addressing and handles dual address cycles on both interfaces.

The device provides no capability for translating addresses.

Tsi310’s configuration registers are accessible from either the primary or secondary interface

using T ype 0 configuration read s and writes. On the secondary interface, the bridge claims Type

1 configuration write transactions that specify conversion to a special cycle on an upstream bus

segment.

Tsi310 User Manual

80B6020_MA001_05

Page 26

1.3.4 Bus Arbitration

The T si310 contains an arbiter for the secondary interface that is enabled or disabled through an

input signal pin. It provides bus arbitration for up to six additional masters, each of which may

be assigned high or low priority or may be masked off. When the internal arbiter is used and the

Tsi310 request is not masked off, the bus is parked at the bridge whenever there are no pending

requests.

The arbiter implements a two-level fairness algorithm that allows each device within a level to

receive grant requests cyclically. The arbiter uses the arbitration priority register to determine

which agents are high priority (HP) devices and which are low priority (LP) devices. At

different points in time, snapshots are taken of all pending requests for each priority level. All

captured HP requests are serviced first, then one of the captured LP requests is serviced. At this

point, a new HP snapshot is taken, picking up any new HP requests. All captured HP requests

are serviced before continuing with the next LP request still pending from the previous LP

snapshot. A new snapshot of pending LP requests is taken only after all requests from the

previous LP snapshot have been serviced.

1. Functional Overview26

1.4 Technology Highlights

The Tsi310 is implemented using a 0.25 micron (m) lithography process with a 0.18 m

L

effective

3.3 V to power the device I/O circuits. The device is packaged in a 31mm thermally and

electrically enhanced plastic ball grid array (HPBGA) with 304 balls. For more information, see

Section 8 on page 191 and Section 9 on page 197.

. The device requires two power supplies, one at 2.5 V for internal logic and the other at

Tsi310 User Manual

80B6020_MA001_05

Page 27

2. Bus Operation

This chapter discusses the following topics:

• “Overview of Bus Operation” on page 27

• “Write Transactions” on page 30

• “Read Transactions” on page 33

• “Configuration Transactions ” on page 37

2.1 Overview of Bus Operation

This chapter presents a summary of the PCI and PCI-X transactions, transaction forwarding

across the Tsi310, and transaction termination.

27

Tsi310 User Manual

80B6020_MA001_05

Page 28

2.1.1 Types of Transactions

Tables 1 and 2 list the command code and name for each PCI and PCI-X transaction. For each

transaction type, the middle two columns indicate whether the T si310 can initiate the transaction

as a master on the primary bus and on the secondary bus. The last two columns indicate whether

the bridge responds to the transaction as a target on the primary bus and on the secondary bus.

Table 1: PCI Transactions

Initiates as Master Responds as Target

Command

Code

0000 Interrupt Acknowledge No No No No

0001 Special Cycle Yes Yes No No

0010 I/O Read Yes Yes Yes Yes

0011 I/O Write Yes Yes Yes Yes

0100 Reserved No No No No

T ype of Transaction

Primary Secondary Primary Secondary

2. Bus Operation28

0101 Reserved No No No No

0110 Memory Read Yes Yes Yes Yes

0111 Memory Write Yes Yes Yes Yes

1000 Reserved No No No No

1001 Reserved No No No No

1010 Configuration Read No Yes Yes Type 0

1011 Configuration Write Type 1 Yes Yes Yes

1100 Memory Read Multiple Yes Yes Yes Yes

1101 Dual Address Cycle Yes Yes Yes Yes

1110 Memory Read Line Yes Yes Yes Yes

1111 Memory Wr ite and Invalidate No No Yes Yes

Tsi310 User Manual

80B6020_MA001_05

Page 29

2. Bus Operation 29

Table 2: PCI-X Transactions

Initiates as Master Responds as Target

Command

Code

0000 Interrupt Acknowledge No No No No

0001 Special Cycle Yes Yes No No

0010 I/O Read Yes Yes Yes Yes

0011 I/O Write Yes Yes Yes Yes

0100 Reserved No No No No

0101 Reserved No No No No

0110 Memory Read Yes Yes Yes Yes

0111 Memory Write Yes Yes Yes Yes

1000 Alias to Memory Read Block No No Yes Yes

Type of Transaction

Primary Secondary Primary Secondary

1001 Alias to Memory Write Block No No Yes Yes

1010 Configuration Read No Yes Yes Type 0

1011 Configuration Write Type 1 Yes Yes Yes

1100 Split Completion Yes Yes Yes Yes

1101 Dual Address Cycle Yes Yes Yes Yes

1110 Memory Read Block Yes Yes Yes Yes

1111 Memory Wr ite Block Yes Yes Yes Yes

As indicated in the previous tables, certain commands are not supported by the Tsi310:

• The bridge never initiates a transaction with a reserved command code and, as a target, the

bridge ignores reserved command codes.

• The bridge never initiates an interrupt acknowledge transaction and, as a target, the bridge

ignores interrupt acknowledge transactions. Interrupt acknowledge transactions are

expected to reside entirely on the primary bus closest to the host bridge.

• The bridge does not respond to special cycle transactions. To generate special cycle

transactions on other buses, either upstream or downstream, a Type 1 configuration

command must be used.

• The Tsi310’s response to Type 1 Configuration accesses on the secondary interface is

limited. The Tsi310 only responds to Type 1 configuration writes that get converted to

special cycles going upstream, as described in Section 2.4.4 on page 42.

Tsi310 User Manual

80B6020_MA001_05

Page 30

• The Tsi310 does not generate Type 0 configuration transactions on the primary interface.

• The T si310 never initiates a Memory Write and Invalidate command on either interface. As

a target, the bridge will accept a Memory Write and Invalidate command and forward it to

the destination interface as a Memory Write command.

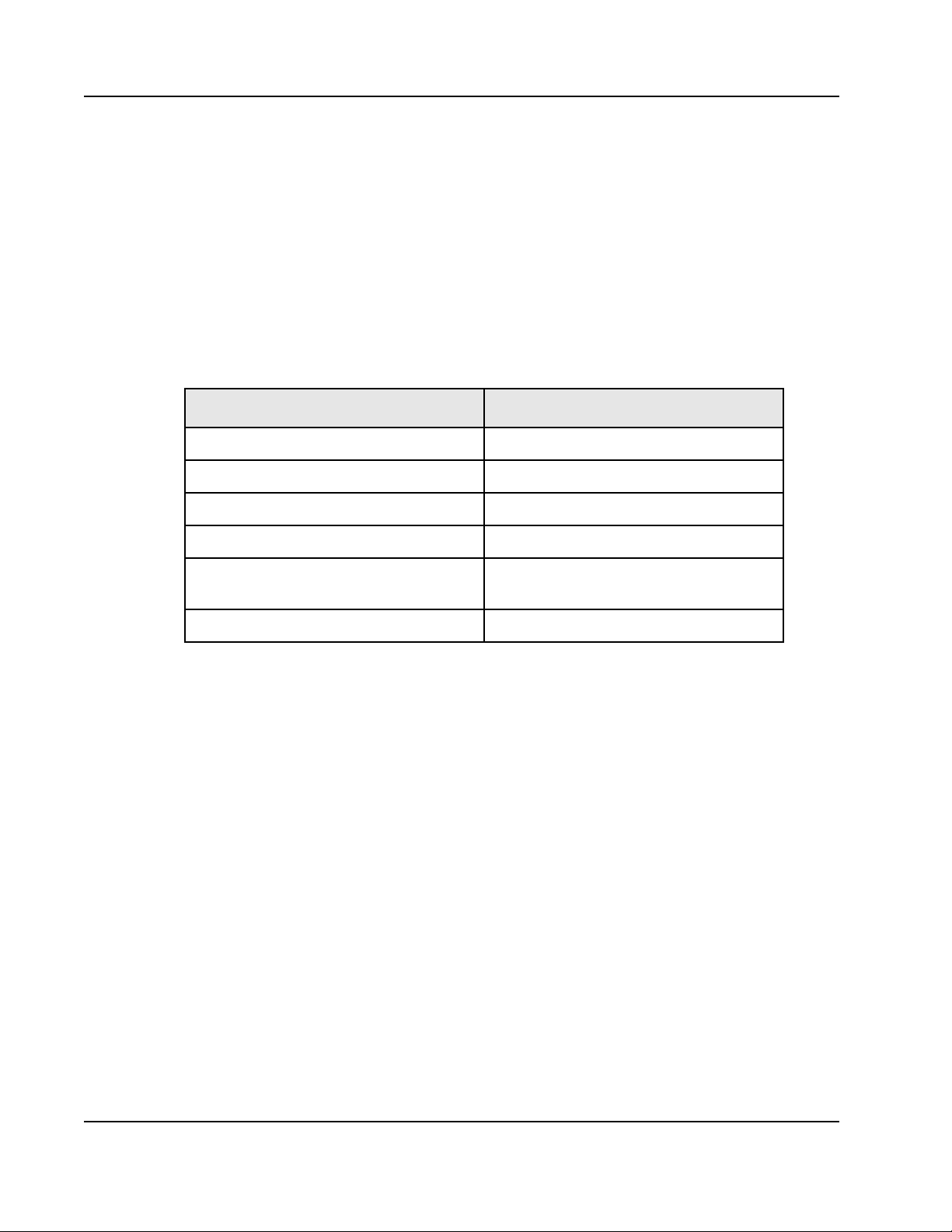

2.2 Write Transactions

Write transactions are treated as either posted, delayed/split (PCI-X), or immediate write

transactions, as shown in the following table.

Table 3: Write Transaction Handling

Type of Transaction Type of Handling

Memory Write Posted

Memory Write and Invalidate Posted

Memory Write Block (PCI-X) Posted

2. Bus Operation30

I/O Write Delayed/Split (PCI-X)

Type 0 Configuration Write Immediate on the primary bus, Delayed/Split

Type 1 Configuration Write Delayed/Split (PCI-X)

2.2.1 Posted Write Transactions

The posted mode is the default mode used for the memory-write and

memory-write-and-invalidate transactions. The memory-write-block transaction also uses the

posted mode. Posted is the only mode used for the memory-write-block command.

When the Tsi310 determines that a memory write transaction is to be forwarded across the

bridge, it first checks for empty space in the posted write buffer. If space is available in the

posted write buffer, the Tsi310 accepts data until the buffer is full or the transaction is

terminated. If the transaction is terminated because the buffer is full, the transaction is

terminated on a 128-byte boundary. If there is no space in the posted write buffer , the transaction

is terminated with retry.

Up to eight posted write transactions can be enqueued in the Tsi310.

(PCI-X) on the secondary bus.

Tsi310 User Manual

80B6020_MA001_05

Page 31

2. Bus Operation 31

2.2.1.1 PCI to PCI-X Transactions

When the originating bus is operating in the conventional PCI mode and the destination bus is

operating in PCI-X mode, the Tsi310 must buffer memory write transactions from the

conventional PCI interface and count the number of bytes to be forwarded to the PCI-X

interface. If the conventional PCI transaction uses the memory write command and some byte

enables are not asserted, the Tsi310 must use the PCI-X memory write command. If the

conventional PCI command is memory write and all byte enables are asserted, the bridge will

use the memory write PCI-X command. If the conventional transaction uses the memory write

and invalidate command, the bridge uses the PCI-X memory write block command.

The Tsi310 attempts to transfer the write data on the PCI-X interface as soon as the transaction

ends or a 128-byte boundary is crossed, whichever comes first. Writes of greater than 128 bytes

are possible only if more than one 128-byte sector fills up before the write operation is issued on

the PCI-X interface.

2.2.1.2 PCI-X to PCI Transactions

When the originating bus is operating in PCI-X mode and the destination bus is operating in the

conventional PCI mode, the Tsi310 uses the conventional memory write command for both the

PCI-X memory write and PCI-X memory write block commands.

The Tsi310 attempts to transfer write data on the conventional PCI interface when the PCI-X

data crosses a 128-byte boundary or the end of the PCI-X transfer occurs, whichever comes

first. As long as a 128-byte buffer is full, or the end of transfer remains from the PCI-X memory

write command when a 128-byte boundary is crossed, the transfer will continue on the

conventional PCI interface.

2.2.1.3 PCI to PCI Transactions

When both buses are operating in conventional PCI mode, the Tsi310 passes a memory write

command that it receives to the destination interface. However, if command received is a

memory write and invalidate command, the T si310 will forward it on to the destination interface

as a memory write command.

The Tsi310 attempts to transfer a memory write command when the transaction ends or a

128-byte boundary is crossed, whichever comes first. As long as a 128-byte buffer is full or the

end of transfer remains from the PCI memory write command when a 128-byte boundary is

crossed, the transfer will continue.

Tsi310 User Manual

80B6020_MA001_05

Page 32

2.2.1.4 PCI-X to PCI-X Transactions

When both buses are operating in PCI-X mode, the Tsi310 passes the memory write command

that it receives to the destination interface along with the originating byte count and transaction

ID.

The Tsi310 attempts to transfer a memory write command when the transaction ends or a

128-byte boundary is crossed, whichever comes first. As long as a 128-byte buffer is full or the

end of transfer remains from the PCI-X memory write command when a 128-byte boundary is

crossed, the transfer will continue.

If a transaction is disconnected on the destination interface in the middle of a continuing

transfer, the byte count and address are updated and the transaction is presented again on the

destination interface. If a transaction is disconnected in the middle of a continuing transfer on

the originating interface, the originator must present the transaction again with the updated byte

count and address.

2.2.2 Delayed/Split Write Transactions

I/O writes, Type 1 configuration writes, and Type 0 configuration writes on the secondary bus

are treated as delayed transactions by the T si310. These commands are retried on the originating

bus, completed on the destination bus if necessary, and then completed on the originating bus.

The Tsi310 executes DWord transactions only as delayed transactions in the conventional PCI

mode and as split requests in PCI-X mode.

2. Bus Operation32

There is only one request queue entry for either delayed or split write transactions.

2.2.3 Immediate Write Transactions

Type 0 configuration writes on the primary PCI interface meant for the Tsi310 are treated as an

immediate write transaction by the bridge. The Tsi310 executes the transaction and indicates its

completion by accepting the DWord of data immediately.

Tsi310 User Manual

80B6020_MA001_05

Page 33

2. Bus Operation 33

2.3 Read Transactions

Read transactions are treated as either delayed (PCI), split (PCI-X), or immediate read

transactions, as shown in the following table.

Table 4: Read Transaction Handling

Type of Transaction Type of Handling

Memory Read Delayed

Memory Read Line Delayed

Memory Read Multiple Delayed

Memory Read DWord (PCI-X) Split (PCI-X)

Memory Read Block (PCI-X) Split (PCI-X)

I/O Read Delayed/Split (PCI-X)

Type 0 Configuration Read Immediate on the primary bus, Delayed/Split

(PCI-X) on the secondary bus

Type 1 Configuration Read Delayed/Split (PCI-X)

2.3.1 Memory Read Transactions

The conventional PCI memory-read, memory-read-line, memory-read-multiple, PCI-X

memory-read-DWord, and PCI-X memory-read-block transactions are used to transfer memory

data from the originating side of the Tsi310 to the destination side. All memory read

transactions are either delayed or split on the originating interface depending on the mode of the

originating interface.

2.3.1.1 PCI to PCI-X Transactions

The Tsi310 must translate the conventional memory read command to either the memory read

DW ord or the memory read block PCI-X Command. If the conventional memory read command

targets non-prefetchable memory space, the command is translated into a memory read DWord.

In any other instance the conventional memory read command gets translated into a memory

read block PCI-X command. The prefetching algorithm for the conventional memory read

command in the prefetchable space is controlled by bits 9:8 of the primary and secondary data

buffering control registers. The default value of these bits indicates that one cache line will be

prefetched.

The Tsi310 must translate the conventional memory read line command to the memory read

block PCI-X command. The prefetching algorithm is controlled by bits 7:6 of th e primary and

secondary data buffering control registers. The default value of these bits indicates that one

cache line will be prefetched.

Tsi310 User Manual

80B6020_MA001_05

Page 34

The T si310 must translate the conventional memory read multiple command to the memory read

block PCI-X command. The prefetching algorithm is controlled by bits 5:4 of th e primary and

secondary data buffering control registers. The default value of these bits indicates that a full

prefetch will be done, subject to the limit imposed by the maximum memory read byte count

value set by bits (14:12) of the same register. The default value for this field is 512 bytes or an

entire read buffer. Using a value greater than this is possible, but it may be constrained by the

setting of the split transaction commitment limit value in the upstream or downstream split

transaction register, since the target bus is in PCI-X mode (or more information about these

registers, see Section 5.5.21 on page 140 and Section 5.5.22 on page 141, respectively). Data

fetching operations will be disconnected at all 1MB boundaries.

2.3.1.2 PCI-X to PCI Transactions

The Tsi310 translates PCI-X memory read DWord commands into conventional memory read

commands.

The T si310 translates a PCI-X memory read block command into one of three conventional PCI

memory read commands based on the byte count and starting address. If the starting address and

byte count are such that only a single DWord (or less) is being read, the conventional transaction

uses the memory read command. If the PCI-X transaction reads more than one DWord, but does

not cross a cache line boundary (as indicated by the Cache Line Size register in the conventional

Configuration Space header), the conventional transaction uses the memory read line command.

If the PCI-X transaction crosses a cache line boundary, the conventional transaction uses the

memory read multiple command.

2. Bus Operation34

If a disconnect occurs before the byte count of the PCI-X memory read block command is

exhausted, the bridge continues to issue the command until all the bytes in the count are

received. The bridge disconnects once the buffer is filled and prefetches more data as 128-byte

sectors of the buffer become free when split completion data is returned to the originator, until

the byte count is exhausted.

2.3.1.3 PCI to PCI Transactions

This mode does not involve any translation.

If the memory read command targets non-prefetchable memory space, the memory read fetches

only the requested double word. Bits 9:8 of the primary and secondary data buffering control

registers control the prefetching algorithm for the memory read command in prefetchable space.

The default value of these bits indicates that up to one cache line will be prefetched.

For the memory read line command, the prefetching algorithm is controlled by bits 7:6 of the

primary and secondary data buffering control registers. The default value of these bits indicates

that up to one cache line will be prefetched.

Tsi310 User Manual

80B6020_MA001_05

Page 35

2. Bus Operation 35

For the memory read multiple command, the prefetching algorithm is controlled by bits 5:4 of

the primary and secondary data buffering control registers. The default value of these bits

indicates that a full prefetch will be done, subject to the limit imposed by the maximum memory

read byte count value set by bits (14:12) of the same register. The default value is 512 bytes or

an entire read buffer. Data fetching operations will be disconnected at all 1 MB boundaries.

2.3.1.4 PCI-X to PCI-X Transactions

This mode does not involve any translation.

The amount of data that is fetched is controlled by the downstream and upstream split

transaction control register. The split transaction capacity and split transaction commitment

limit fields control how much data is requested at any one time (for more information, see

Section 5.5.21 on page 140 and Section 5.5.22 on page 141).

2.3.2 I/O Read

The I/O Read command is not translated and fetches a DWord of data. The command will either

be split in the PCI-X mode or delayed in the conventional PCI mode.

2.3.3 Configuration Read

2.3.3.1 Type 1 Configuration Read

The Type 1 configuration read command is only accepted on the primary interface. The

command will either be split in PCI-X mode or delayed in the conventional PCI mode.

2.3.3.2 Type 0 Configuration Read

The Type 0 configuration read command is accepted on either the primary or secondary

interface. The command returns immediate data on the primary interface regardless of the

interface mode. On the secondary interface the command is treated as a delayed transaction in

PCI mode, and as a split transaction in PCI-X mode.

2.3.4 Non-Prefetchable and DWord Reads

A non-prefetchable read transaction is a read transaction in which the Tsi310 requests exactly

one DWord from the target and disconnects the initiator after delivering that one DWord of read

data. Unlike prefetchable read transactions, the Tsi310 forwards the read byte enable

information for the data phase.

Non-prefetchable behavior is used for I/O, configuration, memory read transactions that fall into

the non-prefetchable memory space for PCI mode, and all DWord read transactions in PCI-X

mode.

Tsi310 User Manual

80B6020_MA001_05

Page 36

2.3.5 Prefetchable Reads

A prefetchable read transaction is a read transaction where the Tsi310 performs speculative

reads, transferring data from the target before it is requested from the initiator. This behavior

allows a prefetchable read transaction to consist of multiple data transfers. For prefetchable read

transactions, all byte enables are asserted for all data phases.

Prefetchable behavior is used for memory read line and memory read multiple transactions, as

well as for memory read transactions that fall into prefetchable memory space and are allowed

to fetch more than a DWord. The amount of data that is prefetched depends on the type of

transaction and the setting of bits in the primary and secondary data bufferi ng co ntro l registers

in configuration space. The amount of prefetching may also be affected by the amount of free

buffer space available in the T si310, and by any read address boundaries encountered. Examples

of these boundaries are cache line for cache line reads and 1M address boundary to ensure that a

read does not cross into another devices’ space.

2.3.5.1 Algorithm for PCI-to-PCI Mode

The algorithm used for transfers in PCI-to-PCI mode is user defined in the primary and

secondary data buffering control registers. These registers have bits for memory read to

prefetchable space, memory read line, and memory read multiple transactions. For memory

read, the bits select whether to read a DWord, read to a cache line boundary, or to fill the

prefetch buffer. For memory read line and memory read multiple transactions, the bits select

whether to read to a cache line boundary or to fill the prefetch buffer. In all cases, if the bits are

selected to fill the prefetch buffer, the maximum amount of data that is requested on the target

interface is controllable by the setting of the maximum memory read byte count bits of the

Primary and Secondary Data Buffering Control registers. When more than 512 bytes are

requested, the Tsi310 fetches data to fill the buffer and then fetches more data to keep the buf fer

filled as sectors (128 bytes) are emptied and become free to use again.

2. Bus Operation36

2.3.5.2 Algorithm for PCI-to-PCI-X Mode

The algorithm for transfers in this mode is much the same as for transfers in PCI-to-PCI mode,

except that the maximum request amount may be additionally constrained by the setting of the

split transaction commitment limit value in the upstream or downstream split transaction

register. The only other dif ference is that prefetching will not cease when the originating master

disconnects. Prefetching will only cease when all of the requested data is received, as required

by the PCI-X architecture.

Tsi310 User Manual

80B6020_MA001_05

Page 37

2. Bus Operation 37

2.3.5.3 Algorithm for PCI-X-to-PCI and PCI-X-to-PCI-X Mode

The algorithm for transfers in these modes is to transfer the amount of requested data.

In the PCI-X-to-PCI mode, the Tsi310 continues to generate data requests to the PCI interface

and keeps the prefetch buffer full until the entire amount of data requested is transferred.

In the PCI-X to PCI-X mode, the algorithm is controlled by the split transaction commitment

limit value contained in the upstream or downstream split transaction register. If the value is

greater than or equal to the split transaction capacity (4KB) but less than 32KB, the maximum

request amount is 512 bytes. Larger transfers will be decomposed into a series of smaller

transfers, until the original byte count has been satisfied. If the commitment limit value indicates

32KB or more, the original request amount is used and decomposition is not performed (for

more information, see Section 5.5.21 on page 140 and Section 5.5.22 on page 141).

If the original request is broken into smaller requests the Tsi310 waits until the previous

completion has been totally received before a new request is issued. This ensures that the data

does not get out of order and that two requests with the same sequence ID are not issued. In any

case, the bridge generates a new requester ID for each request passed through the bridge.

2.4 Configuration Transactions

The PCI Local Bus Specification (Revision 2.2) defines two configuration transaction types,

Type 0 and Type 1. These two configuration formats are distinguished by the value of bus

address bits (1:0). If address bits (1:0) are b‘00’ during a configuration transaction, a Type 0

configuration transaction is being indicated. A Type 0 configuration transaction is used to

access configuration information for devices on the current bus segment. A Type 0

configuration transaction is not forwarded across the Tsi310, but rather is used to configure the

bridge itself. If address bits (1:0) are b‘01’ during a configuration transaction, a Type 1

configuration transaction is being indicated. T ype 1 configuration transactions are used to access

devices that reside behind one or more bridges.

Figure 2 shows the address formats for Type 0 and Type 1 configuration transactions.

The register number is found in both T ype 0 and Type 1 formats and gives the DW ord address of

the configuration register to be accessed. The function number is also included in both formats

and indicates which function of a multi-function device is to be accessed. For single-function

devices, this value is not decoded. Configuration transaction addresses for Type 1 and PCI-X

T ype 0 formats also include a 5-bit field designating the device number that identifies the device

on the target PCI bus that is to be accessed. This device number is decoded to determine which

IDSEL signal is asserted for the transaction. Finally, Type 1 transactions also include a bus

number field that is used by the T si310 to determine where in the bus hierarchy the transaction is

targeted.

Tsi310 User Manual

80B6020_MA001_05

Page 38

Figure 2: Configuration Transaction Address Formats

31 027811 10

Reserved

Function

Register Number 0 1

1

PCI Type 1

Device NumberBus Number

15162324

Number

AD(31:0)

31

027811 10

Function

Register Number 0 0

1

PCI Type 0

See PCI 2.2 Specification and table below

Number

AD(31:0)