Integrated Device Technology Inc IDT77905D, IDT77905C Datasheet

®

Integrated Device Technology, Inc.

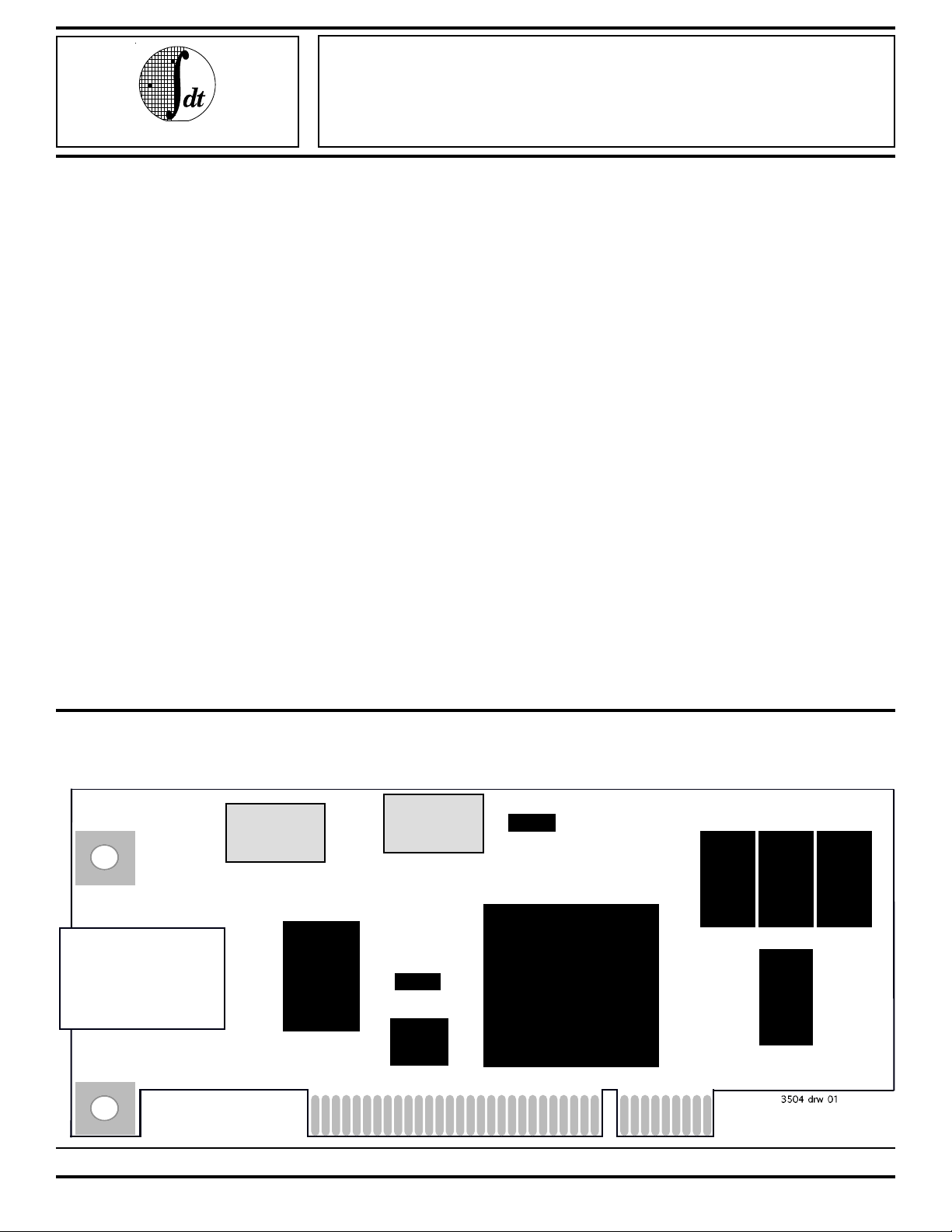

NICStAR™ Reference Design

155Mbps Network Interface

Card (NIC)

ADVANCE INFORMATION

IDT77904C/D

IDT77905C/D

FEATURES:

• Complete 155Mbps PCI-bus ATM Network Interface

Card

• Supports 33MHz, 32-bit PCI bus

• 155Mbps Multimode fiber optical interface (77904)

• 155Mbps UTP-5 PHY interface (77905)

• Complete reference design including schematics, bill of

materials, and data bases needed for production.

• Capable of supporting up to 16K receive connections

• Supports tens of thousands of transmit connections

•E2 PROM layout for Sub-vendor ID

• Small Form Factor: 2.5 x 6 inches

• "SARWIN" software evaluation program available for

Windows 3.1™

• Third Party Software available:

- Telogy Networks

Windows NT™ Drivers and other Windows Drivers

21 Firstfield Road, Gaithersburg, Maryland 20878

(301) 527-2788 (phone) (301) 417-0324 (FAX)

hluterman@telogy.com

- Harris & Jefferies

Novel Netware™ Drivers

888 Washington Street, Dedham,

Massachusetts, 02026

(617) 329-3200 (phone) (617) 329-4148 (FAX)

chrisb@hjinc,com

- Advancenet Systems Inc.

Windows NT™ and Windows 95™ Drivers

406 Timbermill Rd., Durham, North Carolina 27713

(919) 544-5601 (phone) (919) 544-4601 (FAX)

j.harford@ieee.org or

75141,2635@compuserve.com

DESCRIPTION:

The IDT77904 and IDT77905 are designed to provide

stable reference platforms for evaluation, design, and production of a 155Mbps NIC. The IDT77904 provides a fiber media

physical (PHY) interface; the 77905 supports Unshielded

Twisted Pair, Category 5 (UTP-5) cabling. Otherwise identical, they both feature complete PCI-bus ATM NIC functionality, plugging directly into PCI bus expansion slots.

COMPATIBILITY AND CONFIGURATION

The board is designed for use in PCI systems, which may

include PC compatibles, MIPS, Alpha, Windows NT systems,

future PowerPC Macintosh systems, and so on. It supports

the 32 bit, 33 MHz, 5V part of the PCI spec, although this also

permits operation in a 64-bit, 33 MHz, 5V PCI slot.

OVERVIEW

The heart of the board is the IDT 77201 NICStAR™, which

is an ATM Segmentation And Reassembly (SAR) controller.

The NICStAR™ connects directly to the PCI bus, a private

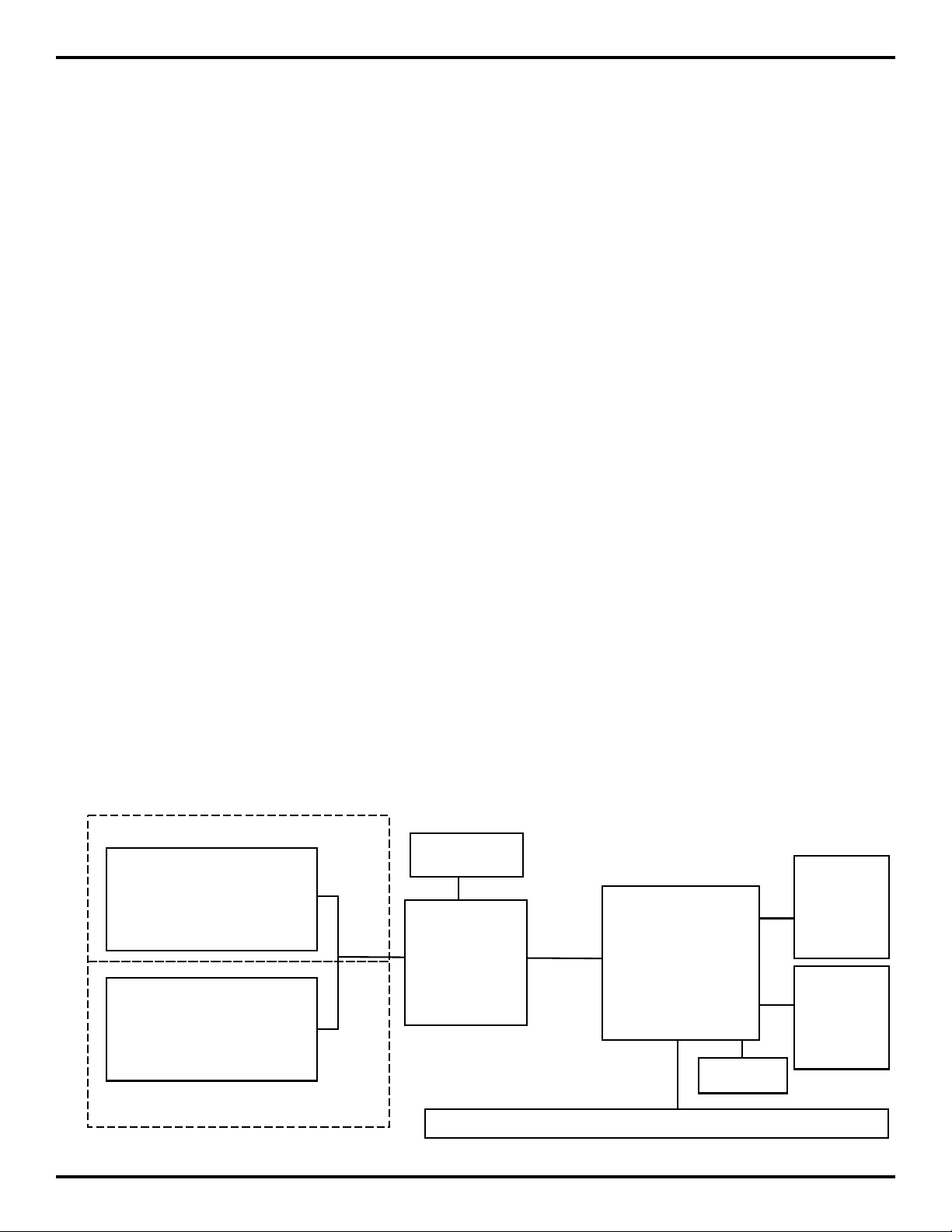

FUNCTIONAL BLOCK DIAGRAM

19MHz

Osc

Osc

77904/5C only

ODL (77904C/D)

50MHz

or

RJ45 +

Magnetics

IDT

77155

PHY

IDT74FCT

3384Q

(77905C/D)

PAL

COMMERCIAL TEMPERATURE RANGE JANUARY 1997

©1996 Integrated Device Technology, Inc.

8.14 1

2

PROM

E

32K

x8

SRAM

IDT

77201

SAR

32K

x8

SRAM

32K

x8

SRAM

32K

x8

SRAM

IDT77904C/D/77905C/D ADVANCED INFORMATION

NICStAR™ Reference Design Commercial Temperature Range

SRAM/EPROM bus, and the Utopia PHY interface. The PHY

device is aIDT 77155 PHY. The PHY device connects in turn

to a Hewlett-Packard HFBR-5103 Optical Data Link (ODL)

device for the fiber optic connection (IDT77904), or to a Micro

Linear ML6672CH transciever for the UTP-5 connection

(IDT77905). The ODL incorporates its own fiber optic connectors; the UTP option requires a line interface/filter transformer

and a standard RJ-45 jack.

THEORY OF OPERATION

The NICStAR™ has 50 signal pins which connect directly

to the PCI bus edge connector. 32 of these are multiplexed

address/data signals, and the remainder are control signals.

The NICStAR™ is compatible with the 5V, 33 MHz portion of

the PCI spec, so the eval board will work in motherboards with

32 or 64 bit, 5V, 33 MHz slots. The board will not work in 3.3V

slots.

The NICStAR™ receives two clock input signals. One is

from the PCI bus, and this one can vary from DC to 33.333MHz.

The other is from a local oscillator on the 77904/5. The

NICStAR™’s main clock is the SAR_CLK. It runs typically at

50 MHz. The rate of the Utopia interface, PHY_CLK is

connected to a devide by 2 output clock from the SAR.

Optionally, this clock can be supplied via a separate osallator,

the PHY clock, and runs typically at 25 MHz. All clock

oscillators on the board have ferrite-bead power supply filters,

and both SAR oscillator sockets have 33 Ohm source series

and 330/220 Ohm end parallel termination resistors provided

for optimum signal integrity.

The NICStAR™ has a private local SRAM/EPROM data

bus, SR_I/O[31:0] and address bus, SR_A[16:0]. It also

supports a four-wire private EEPROM bus, three of which are

outputs (EE_SCLK, EE_CS#, EE_DO) and one of which is an

input (EE_DI).

NICStAR™ supports 4 32Kx8 or 128Kx8 asynchronous

SRAMS. SRAM timing is fixed at one cycle. The NICStAR™

spec requires 20 ns access time SRAMs when the NICStAR™

is running at 50 MHz.

NICStAR™ supports 1 32Kx8 or 128Kx8 EPROM. EPROM

timing is fixed at three cycles. NICStAR™ requires a 70 ns

access time EPROM.

NICStAR™ supports 1 EEPROM device. The four EEPROM

signals are completely under software control, so access

times and protocols can be specified by the user. The eval

board uses a Xicor X25020 EEPROM. This device requires

EE_CS# to be asserted low during all operations. Control or

data bits are taken from EE_DO at the rising edge of EE_SCLK,

and EE_DI changes on the falling edge of EE_SCLK. Refer to

the X25020 documentation for more information. The 77904/

5 provides LEDs on EE_DO (D6) and EE_SCLK (D5). These

LEDs illuminate when the corresponding signal is asserted

low, and may be used to signal status to the user when the

EEPROM is not being accessed.

The NICStAR™ has a multiplexed utility bus, UTL_AD[7:0]

plus five UTL control signals. This bus may be used to

communicate with external 8-bit devices. The 77904/5 uses

the utility bus in this way to communicate with the registers on

the PHY. This interface is also under software control, so

protocol can be specified by the user.

FUNCTIONAL BLOCK DIAGRAM

77904 only

Optial Data

Link (ODL)

Fiber Interface)

ATM Network

RJ-45

Connector

and

Magnetics

77905 only

19MHz

OSC

IDT 77155

SwitchSTAR

PHY

8.14 2

SRAM

IDT 77201

NICStAR

SAR

50MHz

OSC

E2 PROM

5V 33-MHz 32-bit PCI Bus

3504 drw 02

Loading...

Loading...