Integrated Device Technology Inc IDT77901D, IDT77901C Datasheet

®

Integrated Device Technology, Inc.

NICStAR Evaluation Board

ADVANCE INFORMATION

for IDT77201 PCI Segmentation and

Reassembly Controller

IDT77901C/D

FEATURES:

• Complete 155Mbps PCI-bus ATM Network Interface

Card

• Complete reference design including schematics, bill of

materials, and theory of operation

• Connectors for logic analyzers and oscilloscopes

• Supports 33MHz, 32-bit PCI 2.0 bus

• 155Mbps Multimode fiber optical interface

• Complete reference design including schematics, bill of

materials, and data bases needed for production.

• Capable of supporting up to 16K receive connections

• Supports tens of thousands of transmit connections

•E2 PROM layout for Sub-vendor ID

• "SARWIN" software evaluation program available for

Windows 3.1™

• Third Party Software available:

- Telogy Networks

Windows NT™ Drivers and other Windows Drivers

21 Firstfield Road, Gaithersburg, Maryland 20878

(301) 527-2788 (phone) (301) 417-0324 (FAX)

hluterman@telogy.com

- Harris & Jefferies

Novel Netware™ Drivers

888 Washington Street, Dedham,

Massachusetts, 02026

(617) 329-3200 (phone) (617) 329-4148 (FAX)

chrisb@hjinc,com

- Advancenet Systems Inc.

Windows NT™ and Windows 95™ Drivers

406 Timbermill Rd., Durham, North Carolina 27713

(919) 544-5601 (phone) (919) 544-4601 (FAX)

j.harford@ieee.org or

75141,2635@compuserve.com

DESCRIPTION:

The IDT77901 is designed to provide a stable reference

platform for evaluation, design, and test of IDT's 77201

Segmentation and Reassembly controller. The IDT77901

provides a fiber media physical (PHY) interface. The IDT77901

features complete PCI-bus ATM NIC functionality, plugging

directly into PCI bus expansion slots.Test points, including

sockets for logic analyzer and oscilloscope probes are provided on all buses. These connectors may be used for simple

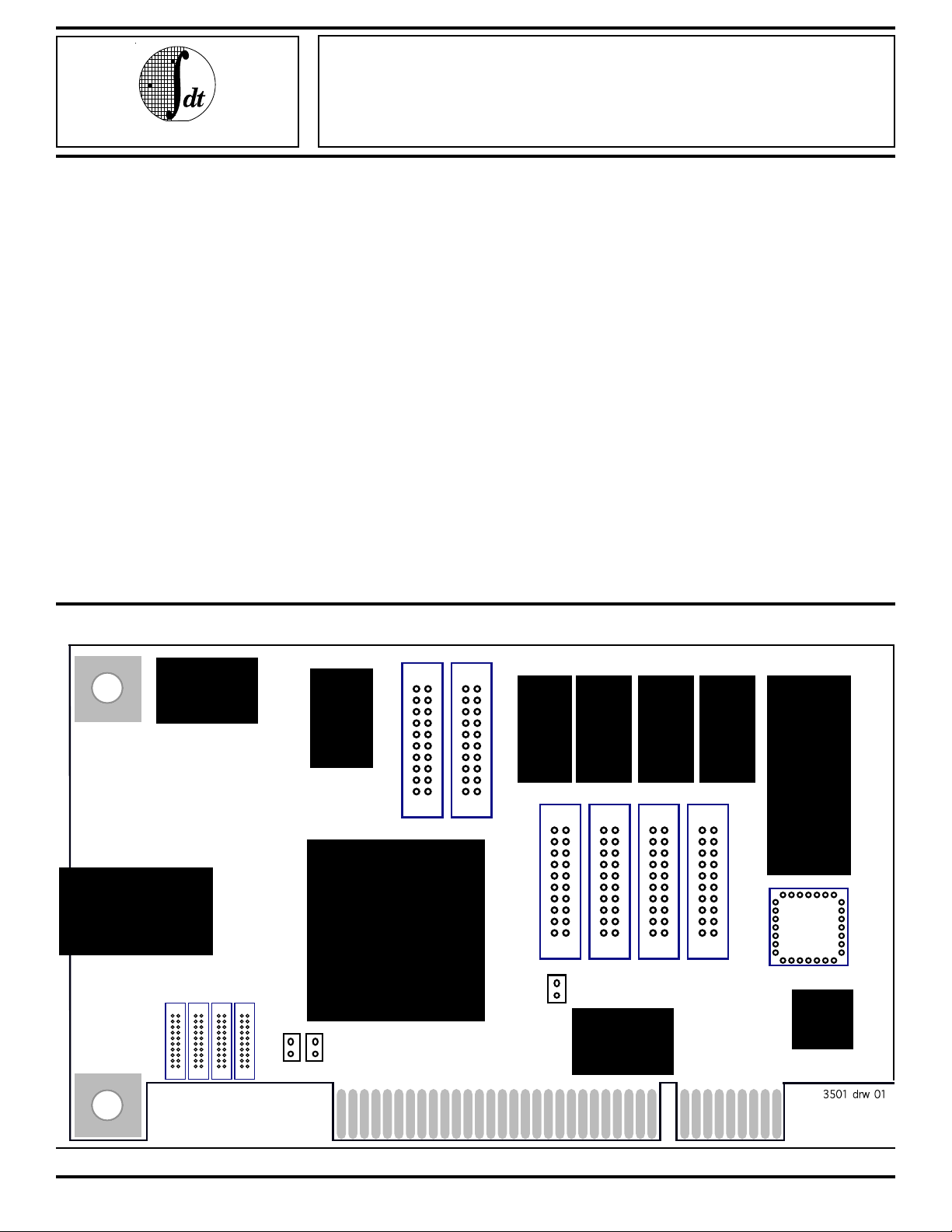

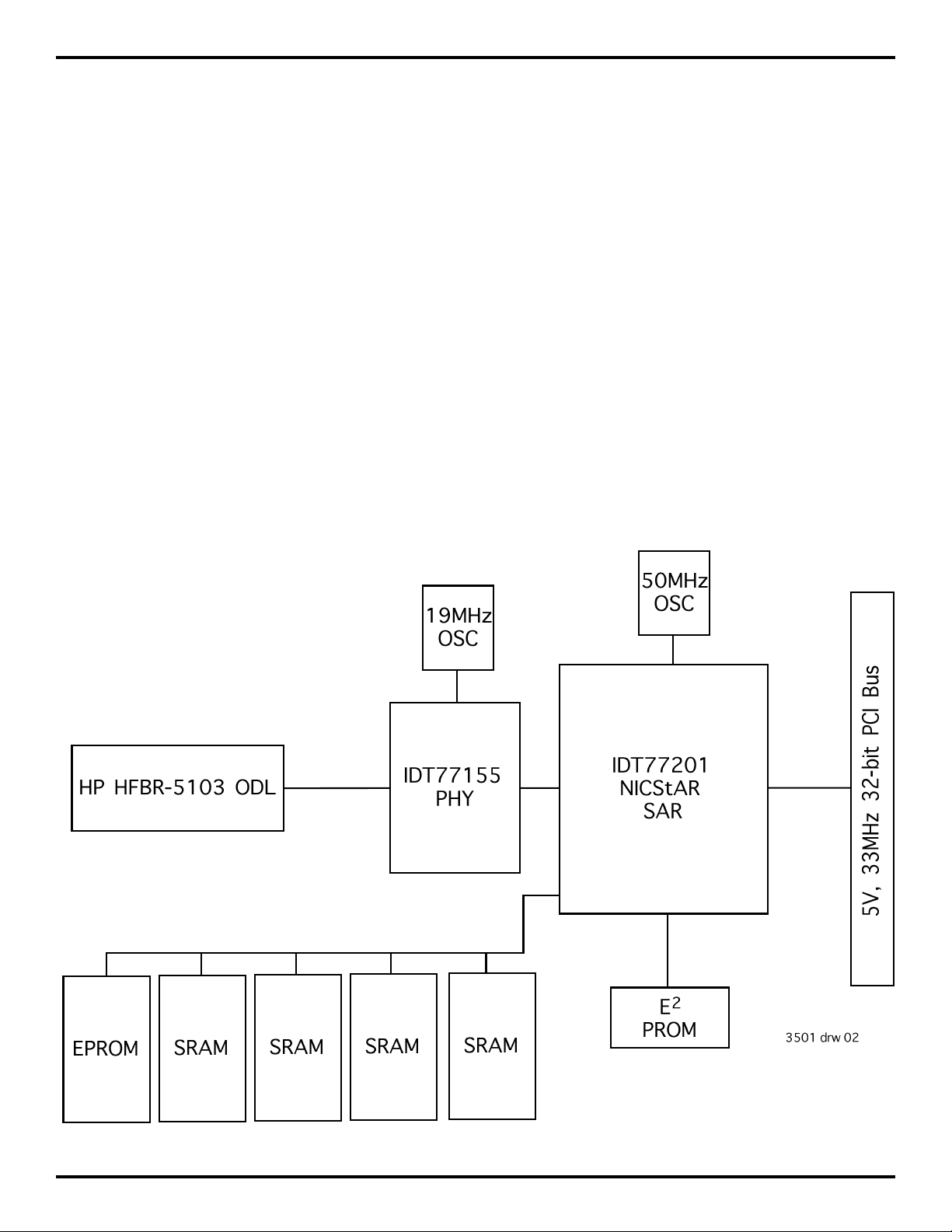

FUNCTIONAL BLOCK DIAGRAM

19MHz

OSC

IDT77155

ODL

PHY

SwitchStar

IDT77201

NICStAR

SAR

32K

x8

SRAM

32K

x8

SRAM

50MHz

OSC

32K

x8

SRAM

32K

x8

SRAM

EPROM

2

E

PROM

COMMERCIAL TEMPERATURE RANGE JANUARY 1997

©1996 Integrated Device Technology, Inc.

8.09 1

IDT77901C/D ADVANCED INFORMATION

NICStAR Evaluation Board Commercial Temperature Range

probing into all buses and active signals lines for hardware

and/or software design, verification, and debugging operations.

FUNCTIONAL OVERVIEW

COMPATIBILITY AND CONFIGURATION

The board is designed for use in PCI systems, which may

include PC compatibles, MIPS, Alpha, Windows NT systems,

future PowerPC Macintosh systems, and so on. It supports

the 32 bit, 33 MHz, 5V part of the PCI spec, although this also

permits operation in a 64-bit, 33 MHz, 5V PCI slot.

OVERVIEW

The heart of the board is the IDT 77201 NICStAR, which is

an ATM Segmentation And Reassembly (SAR) controller.

The NICStAR connects directly to the PCI bus, a private

SRAM/EPROM bus, and the Utopia PHY interface. The PHY

device is an IDT77155. The PHY device connects in turn to a

Hewlett-Packard HFBR-5103 Optical Data Link (ODL) device

for the fiber optic connection. The ODL incorporates its own

fiber optic connectors.

THEORY OF OPERATION

The NICStAR has 50 signal pins which connect directly to

the PCI bus edge connector. 32 of these are multiplexed

address/data signals, and the remainder are control signals.

The NICStAR is compatible with the 5V, 33 MHz portion of the

PCI spec, so the eval board will work in motherboards with 32

or 64 bit, 5V, 33 MHz slots. The board will not work in 3.3V

slots.

The 77901 connects the PCI bus PRSNT1# and PRSNT2#

pins to ground; R59 (see schematic) is provided between the

PCI bus RST# signal and the NICStAR’s RST# input to

facilitate testing. This resistor is normally 0 Ohms but it could

be removed, and the pads used to insert some sort of AND

gate to allow the NICStAR to be reset without resetting the

host computer.

The NICStAR receives two clock input signals. One is from

the PCI bus, and this one can vary from DC to 33.333MHz. The

other is from a local oscillator on the 77901. U14 is the

NICStAR’s main clock: SAR_CLK. It runs typically at 50 MHz.

The rate of the Utopia interface, PHY_CLK is connected to a

FUNCTIONAL BLOCK DIAGRAM

8.09 2

Loading...

Loading...