Integrated Device Technology Inc IDT75FCT833AE, IDT75FCT833AD, IDT75FCT833BSO, IDT75FCT833BP, IDT75FCT833BL Datasheet

...

Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES MAY 1992

1992 Integrated Device Technology, Inc. 7.21 DSC-4621/2

FAST CMOS

PARITY BUS

TRANSCEIVER

FEATURES:

• Equivalent to AMD’s Am29833 bipolar parity bus

transceiver in pinout/function, speed and output drive

over full temperature and voltage supply extremes

• High-speed bidirectional bus transceiver for processororganized devices

• IDT54/74FCT833A equivalent to Am29833A speed and

output drive

• IDT54/74FCT833B 30% faster than Am29833A

• Buffered direction and three-state controls

• Error flag with open-drain output

•I

OL = 48mA (commercial) and 32mA (military)

• TTL input and output level compatible

• CMOS output level compatible

• Substantially lower input current levels than AMD’s

bipolar Am29800 series (5µA max.)

• Available in plastic DIP, CERDIP, LCC and SOIC

• Product available in Radiation Tolerant and Radiation

Enhanced versions

• Military product compliant to MIL-STD-883, Class B

DESCRIPTION:

The IDT54/74FCT833s are high-performance bus

transceivers designed for two-way communications. They

each contain an 8-bit data path from the R (port) to the T (port),

an 8-bit data path from the T (port) to the R (port), and a 9-bit

parity checker/generator. The error flag can be clocked and

stored in a register and read at the

ERR

output. The clear

(

CLR

) input is used to clear the error flag register.

The output enables

OE

T and OER are used to force the

port outputs to the high-impedance state so that the device

can drive bus lines directly. In addition,

OE

R and OET can be

used to force a parity error by enabling both lines

simultaneously. This transmission of inverted parity gives the

designer more system diagnostic capability. The devices are

specified at 48mA and 32mA output sink current over the

commercial and military temperature ranges, respectively.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

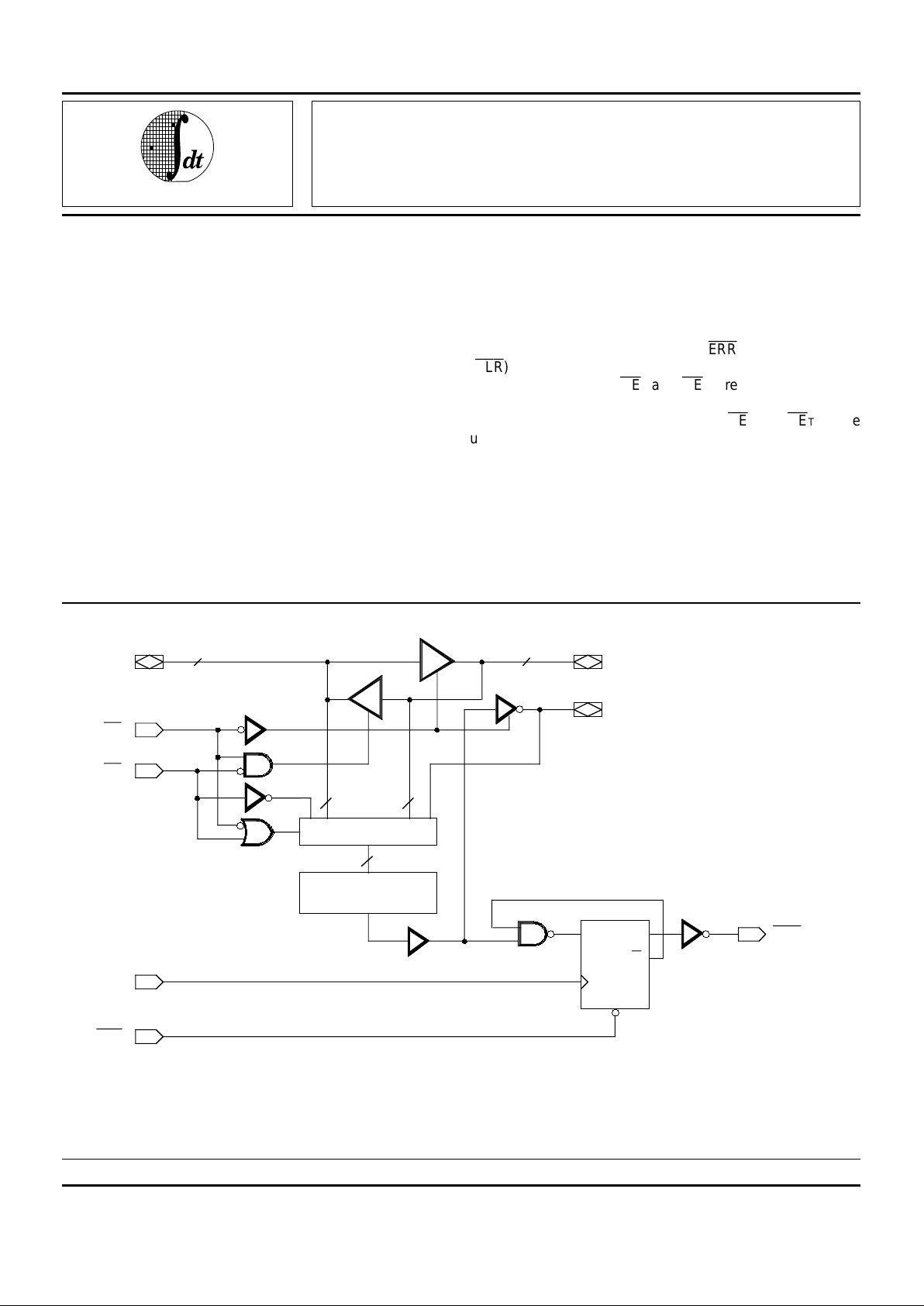

FUNCTIONAL BLOCK DIAGRAM

OE

T

S MUX

OE

R

9-BIT

PARITY TREE

9

8

RI

8

8

T

D

CLR

CP

Q

Q

PARITY

CLK

CLR

ERR

2557 drw 01

P

8

I

IDT54/74FCT833A

IDT54/74FCT833B

1

7.21 2

IDT54/74FCT833A/B

FAST CMOS PARITY BUS TRANSCEIVER MILITARY AND COMMERCIAL TEMPERATURE RANGES

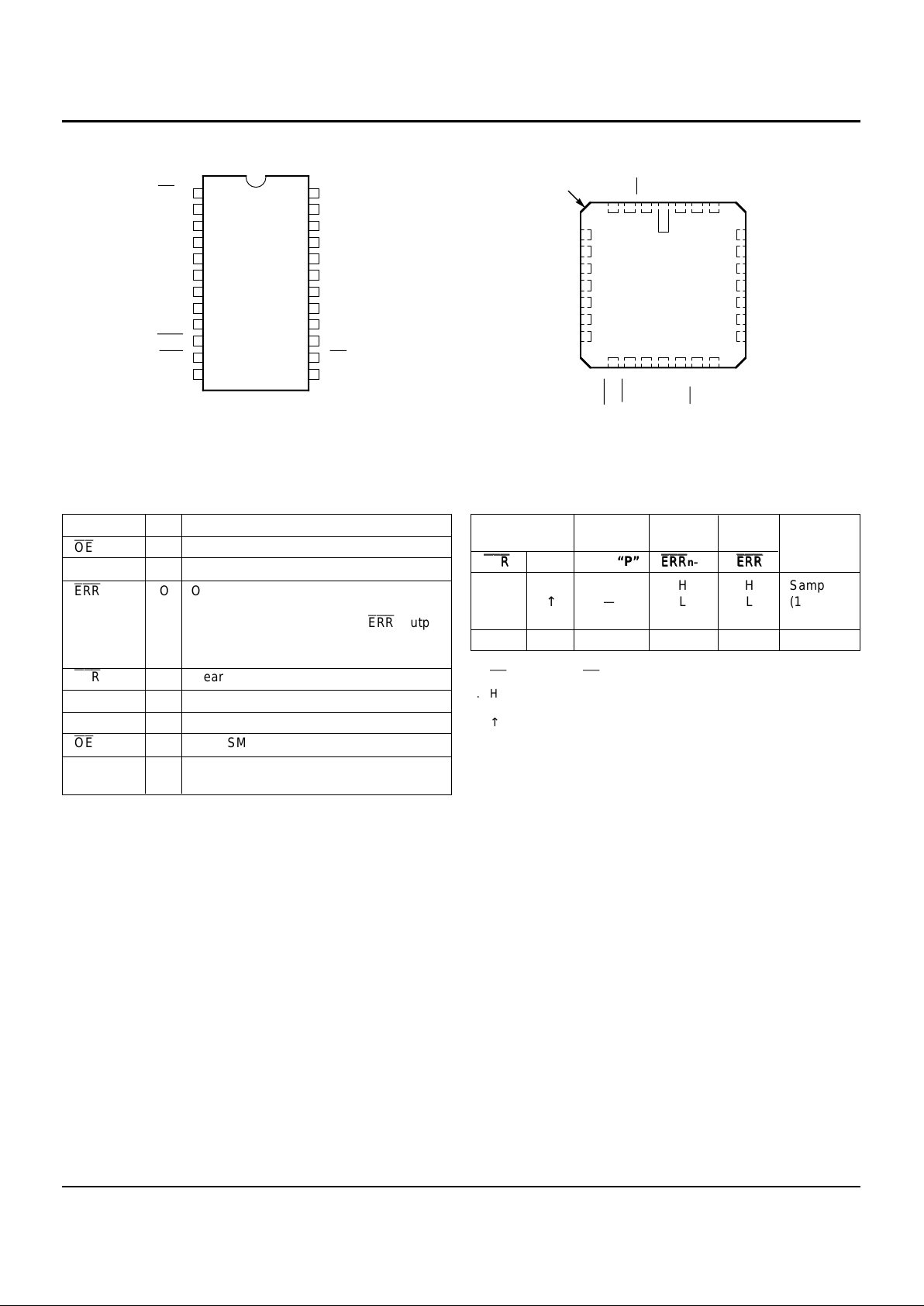

PIN CONFIGURATIONS

DIP/SOIC/CERPACK

TOP VIEW

LCC

TOP VIEW

2557 tbl 01

PIN DESCRIPTION

Pin Name I/O Description

OE

R I RECEIVE enable input.

R

I I/O 8-bit RECEIVE data input/output.

ERR

O Output from fault registers. Register

detection of odd parity fault on rising clock

edge (CLK). A registered

ERR

output

remains LOW until cleared. Open drain

output, requires pull up resistor.

CLR

I Clears the fault register output.

T

I I/O 8-bit TRANSMIT data input/output.

PARITY I/O 1-bit PARITY output.

OE

T I TRANSMIT enable input.

CLK I External clock pulse input for fault register

flag.

ERROR FLAG OUTPUT FUNCTION TABLE

(1,2)

Internal Output

Inputs To Device Pre-State Output

CLR

CLR

CLK Point “P”

ERR

ERR

n–1

ERR

ERR

Function

H ↑ H H H Sample

H ↑ — L L (1’s

H ↑ L — L Capture)

L — — — H Clear

NOTES: 2557 tbl 02

1.

OE

T is HIGH and OER is LOW.

2. H = HIGH

L = LOW

↑ = LOW-to-HIGH transition of clock

– = Don't Care or Irrelevant

5

6

7

8

9

10

11

12

GND

R

1

R

2

R

3

1

2

3

4

24

23

22

21

20

19

18

17

Vcc

16

15

14

13

OE

P24-1,

D24-1,

S024-2

&

E24-1

T

1

R

4

R

5

R

6

T

2

T

3

T

4

T

5

CLK

CLR OE

ERR PARITY

T

T

6

T

7

T

0

R

R

7

R

0

5

6

7

8

9

10

11

L28-1

25

24

23

22

21

20

19

12 13 14 15 16 17 18

432128 27 26

INDEX

2557 drw 02

R

2

R

3

R

4

R

5

R

6

T

2

T

3

T

4

T

5

T

6

T

7

R

7

NC NC

R

1

Vcc

OE

T

1

T0

R

R0

NC

GND

CLK

CLR

OE

ERR

PARITY

T

NC

IDT54/74FCT833A/B

FAST CMOS PARITY BUS TRANSCEIVER MILITARY AND COMMERCIAL TEMPERATURE RANGES

7.21 3

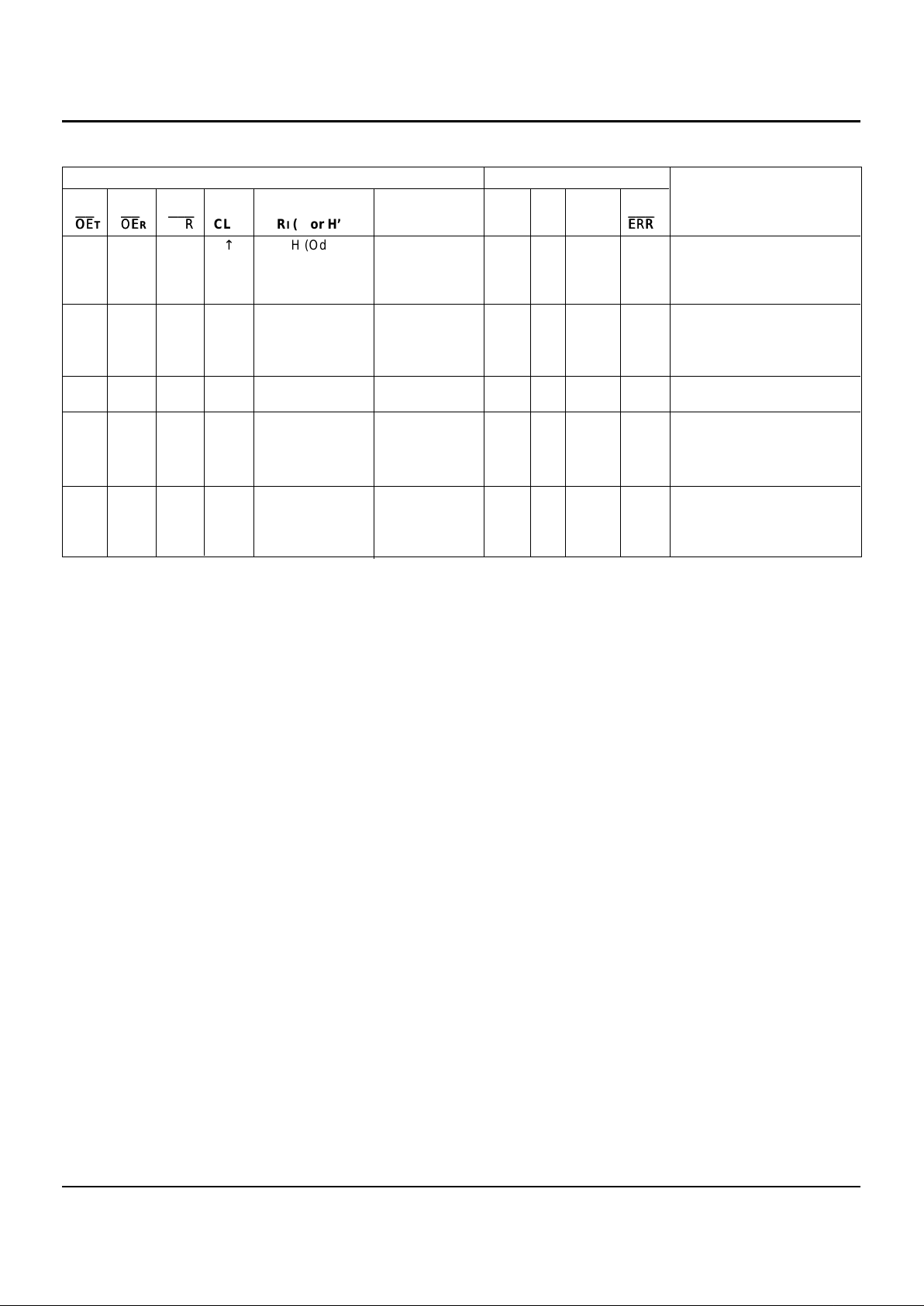

FUNCTION TABLE

(2)

Inputs Outputs

T

I Incl Parity

OE

OE

T

OE

OE

R

CLR

CLR

CLK RI (∑ or H’s) (∑ of H’s) RI TI Parity

ERR

ERR

(1)

Function

LHH↑ H (Odd) NA NA H L H Transmit data from R Port

LHH↑ H (Even) NA NA H H L to T Port with parity;

LHH↑ L (Odd) NA NA L L H receiving path is disabled.

LHH↑ L (Even) NA NA L H L

HLH↑ NA H (Odd) H NA NA H Receive data from T Port

HLH↑ NA H (Even) H NA NA L to R Port with parity test

HLH↑ NA L (Odd) L NA NA H resulting in flag:

HLH↑ NA L (Even) L NA NA L transmitting path is disabled.

— — L — — — NA NA NA H Clear the state of error flag

register.

H H H H or L — — Z Z Z * Both transmitting and

H H L — — — Z Z Z H receiving paths are disabled.

HHH↑ H or L (Odd) — Z Z Z H Parity logic defaults to

HHH↑ H or L (Even) — Z Z Z L transmit mode.

LLH↑ H (Odd) NA NA H H L Forced-error checking.

LLH↑ H (Even) NA NA H L H

LLH↑ L (Odd) NA NA L H L

LLH↑ L (Even) NA NA L L H

NOTES: 2557 tbl 03

1. Output state assumes HIGH output pre-state.

2. H = HIGH Z = High Impedance Odd = Odd number of logic one’s

L = LOW NA = Not Applicable Even = Even number of logic one’s

↑ = LOW-to-HIGH transition of clock – = Don’t Care or Irrelevant I = 0, 1, 2, 3, 4, 5, 6, 7

*No change to stored Error State

Loading...

Loading...