IDT IDT54FCT821A, IDT54FCT821B, IDT54FCT821C, IDT54FCT823A, IDT54FCT823B User Manual

...

查询IDT54FCT821ADB供应商

Integrated Device Technology, Inc.

HIGH-PERFORMANCE

CMOS BUS INTERFACE

REGISTERS

IDT54/74FCT821A/B/C

IDT54/74FCT823A/B/C

IDT54/74FCT824A/B/C

IDT54/74FCT825A/B/C

FEATURES:

• Equivalent to AMD’s Am29821-25 bipolar registers in

pinout/function, speed and output drive over full temperature and voltage supply extremes

• IDT54/74FCT821A/823A/824A/825A equivalent to

FAST speed

• IDT54/74FCT821B/823B/824B/825B 25% faster than

FAST

• IDT54/74FCT821C/823C/824C/825C 40% faster than

FAST

• Buffered common Clock Enable (EN) and asynchronous

Clear input (

•I

OL = 48mA (commercial) and 32mA (military)

• Clamp diodes on all inputs for ringing suppression

• CMOS power levels (1mW typ. static)

• TTL input and output compatibility

• CMOS output level compatible

• Substantially lower input current levels than AMD’s

bipolar Am29800 series (5µA max.)

• Product available in Radiation Tolerant and Radiation

Enhanced versions

• Military product compliant to MIL-STD-883, Class B

CLR

)

DESCRIPTION:

The IDT54/74FCT800 series is built using an advanced

dual metal CMOS technology.

The IDT54/74FCT820 series bus interface registers are

designed to eliminate the extra packages required to buffer

existing registers and provide extra data width for wider

address/data paths or buses carrying parity. The IDT54/

74FCT821 are buffered, 10-bit wide versions of the popular

‘374 function. The IDT54/74FCT823 and IDT54/74FCT824

are 9-bit wide buffered registers with Clock Enable (EN) and

Clear (

CLR

) – ideal for parity bus interfacing in high-performance microprogrammed systems. The IDT54/74FCT825 are

8-bit buffered registers with all the ‘823 controls plus multiple

enables (

interface, e.g., CS, DMA and RD/WR. They are ideal for use

as an output port requiring HIGH IOL/IOH.

family are designed for high-capacitance load drive capability,

while providing low-capacitance bus loading at both inputs

and outputs. All inputs have clamp diodes and all outputs are

designed for low-capacitance bus loading in high-impedance

state.

OE

1, OE2, OE3) to allow multiuser control of the

All of the IDT54/74FCT800 high-performance interface

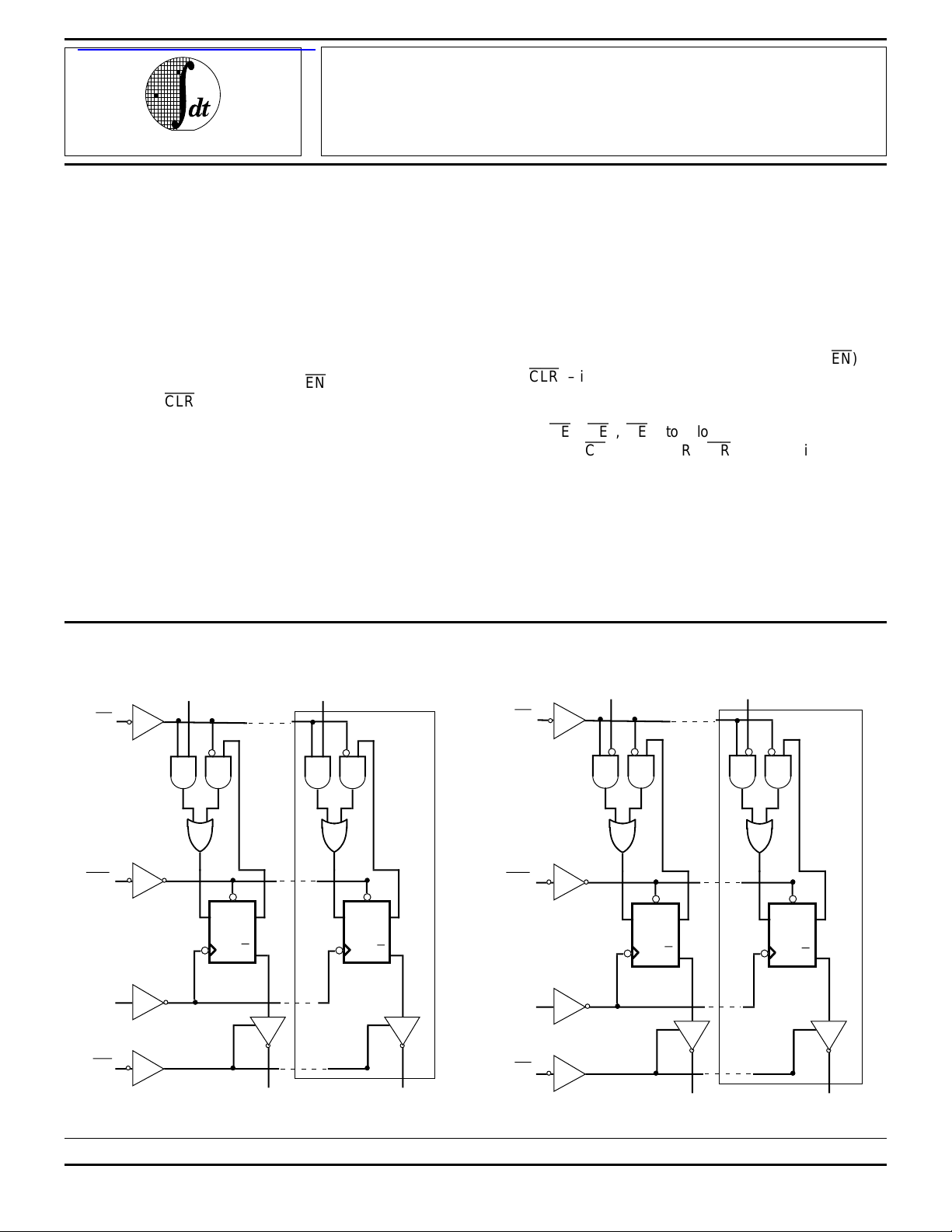

FUNCTIONAL BLOCK DIAGRAMS

IDT54/74FCT821/823/825

D0 DN

EN

CLR

CL

D

Q

CP

Q

CP

OE

Y0 YN

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FAST is a trademark of National Semiconductor Co.

D

CL

CP

Q

Q

2608 cnv* 01

IDT54/74FCT824

EN

CLR

CP

OE

D0 DN

CL

D

Q

CP

Q

Y0 YN

D

CP

CL

Q

Q

2608 cnv* 02

MILITARY AND COMMERCIAL TEMPERATURE RANGES MAY 1992

1992 Integrated Device Technology, Inc. 7.19 DSC-4618/2

1

IDT54/74FCT821/823/824/825A/B/C

HIGH-PERFORMANCE CMOS BUS INTERFACE REGISTERS MILITARY AND COMMERCIAL TEMPERATURE RANGES

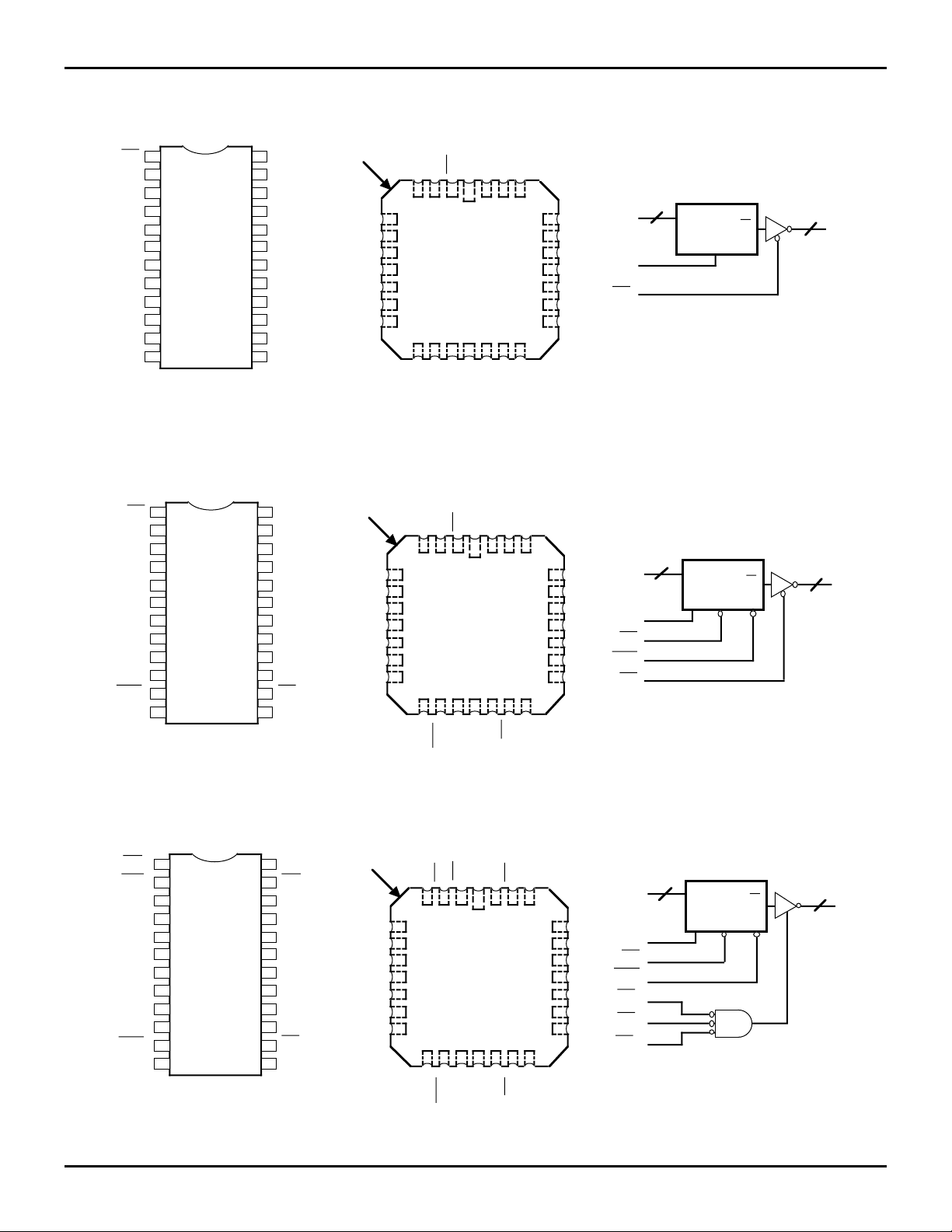

PIN CONFIGURATIONS LOGIC SYMBOLS

IDT54/74FCT821 10-BIT REGISTER

INDEX

V

Y

Y

Y

Y

Y

Y

Y

Y

Y

Y

CP

CC

0

1

2

3

4

5

6

7

8

9

D

D

D

NC

D

D

D

0

1

D

OE

D

32

4

2

5

3

6

4

7

8

5

9

6

10

7

11

L28-1

1213

9

8

D

D

GND

1

NC

NC

CC

V

CP

0

1

Y

Y

CP

OE

10

D

D

QY

10

CP

262728

Y

Y

Y

NC

Y

Y

Y

2

3

4

5

6

7

25

24

23

22

21

20

19

1817161514

9

8

Y

Y

LCC

TOP VIEW

2608 cnv* 03

OE

D

D

D

D

D

D

D

D

D

D

GND

1

0

2

1

3

4

5

6

7

SO24-2

8

9

10

11

P24-1

D24-1

E24-1

2

3

4

5

6

7

8

9

12

24

23

22

21

20

19

&

18

17

16

15

14

13

DIP/SOIC/CERPACK

TOP VIEW

IDT54/74FCT823/824 9-BIT REGISTERS

24

23

22

21

20

19

18

17

16

15

14

13

VCC1

Y

Y1

Y2

Y3

Y4

Y

Y6

Y7

Y

EN

CP

0

5

8

OE

D

D1

D2

D3

D4

D5

D6

D7

D

CLR

GND

2

0

3

4

P24-1

D24-1

5

SO24-2

6

&

7

E24-1

8

9

10

8

11

12

DIP/SOIC/CERPACK

TOP VIEW

IDT54/74FCT825 8-BIT REGISTER

24

V

23

22

21

20

19

18

17

16

15

14

13

OE

Y

Y

Y

Y

Y

Y

Y

Y

EN

CP

CC

0

1

2

3

4

5

6

7

OE

OE

CLR

GND

1

1

2

2

3

D

0

4

5

6

7

8

9

10

P24-1

D24-1

E24-1

SO24-2

D

1

D

2

D

3

D

4

D

5

D

6

D

7

11

12

DIP/SOIC/CERPACK

TOP VIEW

&

3

INDEX

INDEX

D2

D

D4

NC

D

D6

D7

NC

CC

1

NC

NC

V

CP

Y0

262728

1817161514

EN

Y1

25

24

23

22

21

20

19

8

Y

Y2

Y3

Y4

NC

Y

Y6

Y7

9

D

D

CP CLR

QY

EN

9

CP

EN

5

CLR

OE

D0

OE

D1

32

4

5

6

3

7

8

9

5

L28-1

10

11

1213

D8

CLR

GND

LCC

TOP VIEW

CC

OE2

D0

OE1

NC

32

D

1

5

2

6

D

7

D

3

8

9

D

4

D

5

10

11

D

6

4

1

L28-1

1213

D7

CLR

GND

NC

V

CP

OE3

262728

1817161514

EN

Y0

25

24

23

22

21

20

19

7

Y

Y

Y

Y

NC

Y

Y

Y

8

D

1

CP

2

EN

3

D

CP CLR

QY

EN

CLR

4

OE

OE

OE

1

2

3

5

6

2608 cnv* 04

8

LCC

TOP VIEW

2608 cnv* 05

7.19 2

IDT54/74FCT821/823/824/825A/B/C

HIGH-PERFORMANCE CMOS BUS INTERFACE REGISTERS MILITARY AND COMMERCIAL TEMPERATURE RANGES

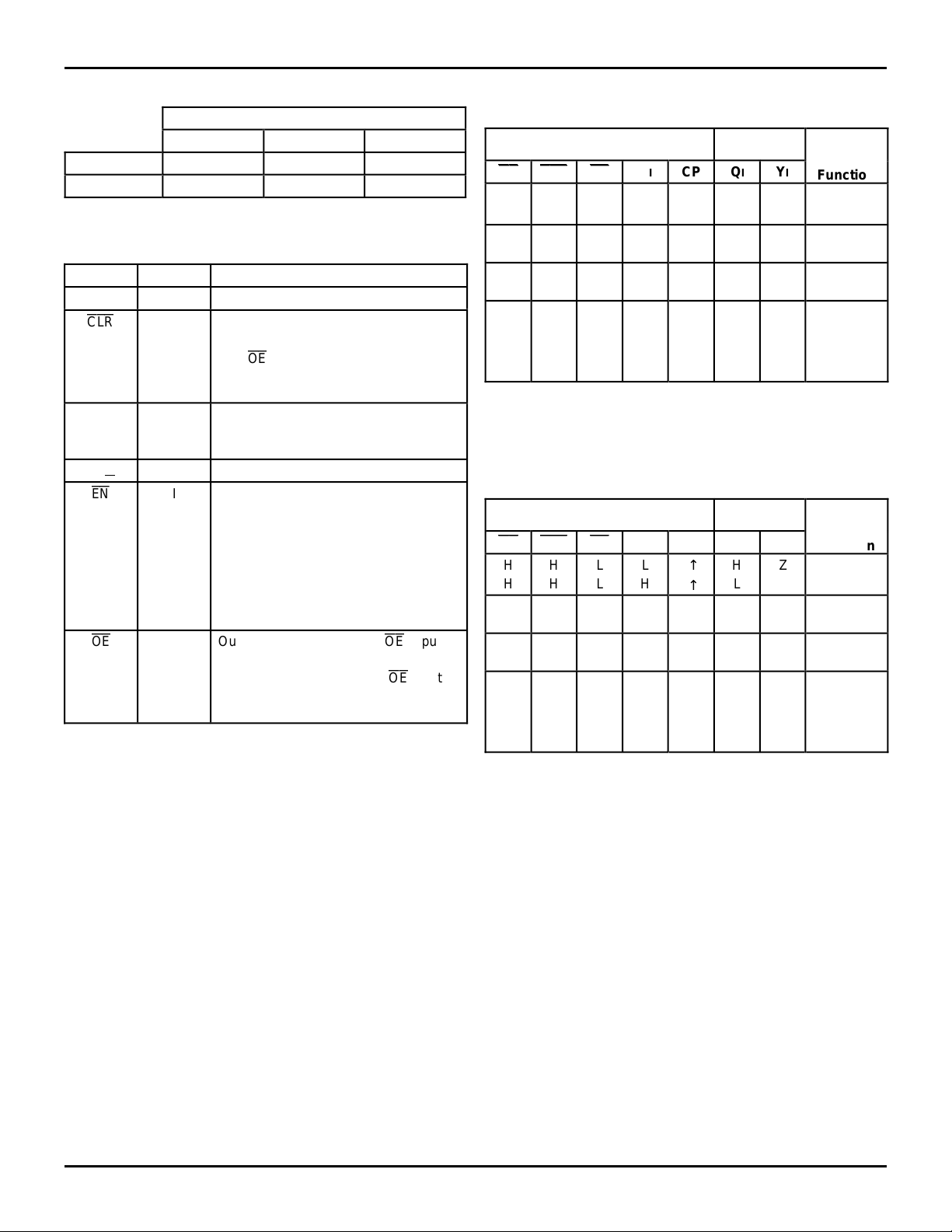

PRODUCT SELECTOR GUIDE

Device

10-Bit 9-Bit 8-Bit

Non-inverting 54/74FCT821A/B/C 54/74FCT823A/B/C 54/74FCT825A/B/C

Inverting 54/74FCT824A/B/C

2608 tbl 01

PIN DESCRIPTION

Name I/O Description

DI I The D flip-flop data inputs.

CLR

CP I Clock Pulse for the Register; enters

YI , YI

EN

OE

I For both inverting and non-inverting

registers, when the clear input is LOW

and OE is LOW, the Q

I outputs are

LOW. When the clear input is HIGH,

data can be entered into the register.

data into the register on the LOW-toHIGH transition.

O The register three-state outputs.

I Clock Enable. When the clock enable

is LOW, data on the D

transferred to the Q

I input is

I output on the

LOW-to-HIGH clock transition. When

the clock enable is HIGH, the Q

outputs do not change state,

regardless of the data or clock input

transitions.

I Output Control. When the OE input is

HIGH, the Y

I outputs are in the high

impedance state. When the OE input is

LOW, the TRUE register data is

present at the Y

I outputs.

2608 tbl 10

FUNCTION TABLE

(1)

IDT54/74FCT821/823/825

↑

↑

↑

↑

↑

↑

Internal/

Outputs

L

Z

H

Z

L

Z

L

L

NC

NCZNC

L

Z

H

H

Z

L

L

H

Inputs

OEOECLR

CLRENEN

H

H

H

H

H

H

H

H

NOTE: 2608 tbl 02

1. H = HIGH, L = LOW, X = Don’t Care, NC = No Change, ↑ = LOW-to-HIGH

Transition, Z = High Impedance

L

L

L

H

L

H

H

H

L

H

L

H

FUNCTION TABLE

DI CP QI YI

L

L

L

H

X

X

X

X

X

X

H

X

X

H

X

X

L

L

L

H

L

L

L

H

(1)

IDT54/74FCT824

↑

↑

↑

↑

↑

↑

Internal/

Outputs

H

Z

L

Z

L

Z

L

L

NC

NCZNC

H

H

Z

L

Z

H

L

L

Inputs

OEOECLR

CLRENEN

H

I

NOTE:

1. H = HIGH, L = LOW, X = Don’t Care, NC = No Change, ↑ = LOW-to-

H

H

H

H

H

H

H

HIGH Transition, Z = High Impedance

L

L

L

H

L

H

H

H

L

H

L

H

DI CP QI YI

L

L

L

H

X

X

X

X

X

X

H

X

X

H

X

X

L

L

L

H

L

L

L

H

Function

High Z

Clear

Hold

Load

Function

High Z

Clear

Hold

Load

2608 tbl 03

7.19 3

Loading...

Loading...