Integrated Device Technology Inc IDT74FCT573SOB, IDT74FCT573CPB, IDT74FCT573CP, IDT74FCT573CLB, IDT74FCT573CEB Datasheet

...

Integrated Device Technology, Inc.

FAST CMOS OCTAL

TRANSPARENT LATCHES

IDT54/74FCT373/A/C

IDT54/74FCT533/A/C

IDT54/74FCT573/A/C

FEATURES

• IDT54/74FCT373/533/573 equivalent to FAST speed

and drive

• IDT54/74FCT373A/533A/573A up to 30% faster than

FAST

• Equivalent to FAST output drive over full temperature

and voltage supply extremes

•I

OL = 48mA (commercial) and 32mA (military)

• CMOS power levels (1mW typ. static)

• Octal transparent latch with 3-state output control

• JEDEC standard pinout for DIP and LCC

• Product available in Radiation Tolerant and Radiation

Enhanced versions

• Military product compliant to MIL-STD-883, Class B

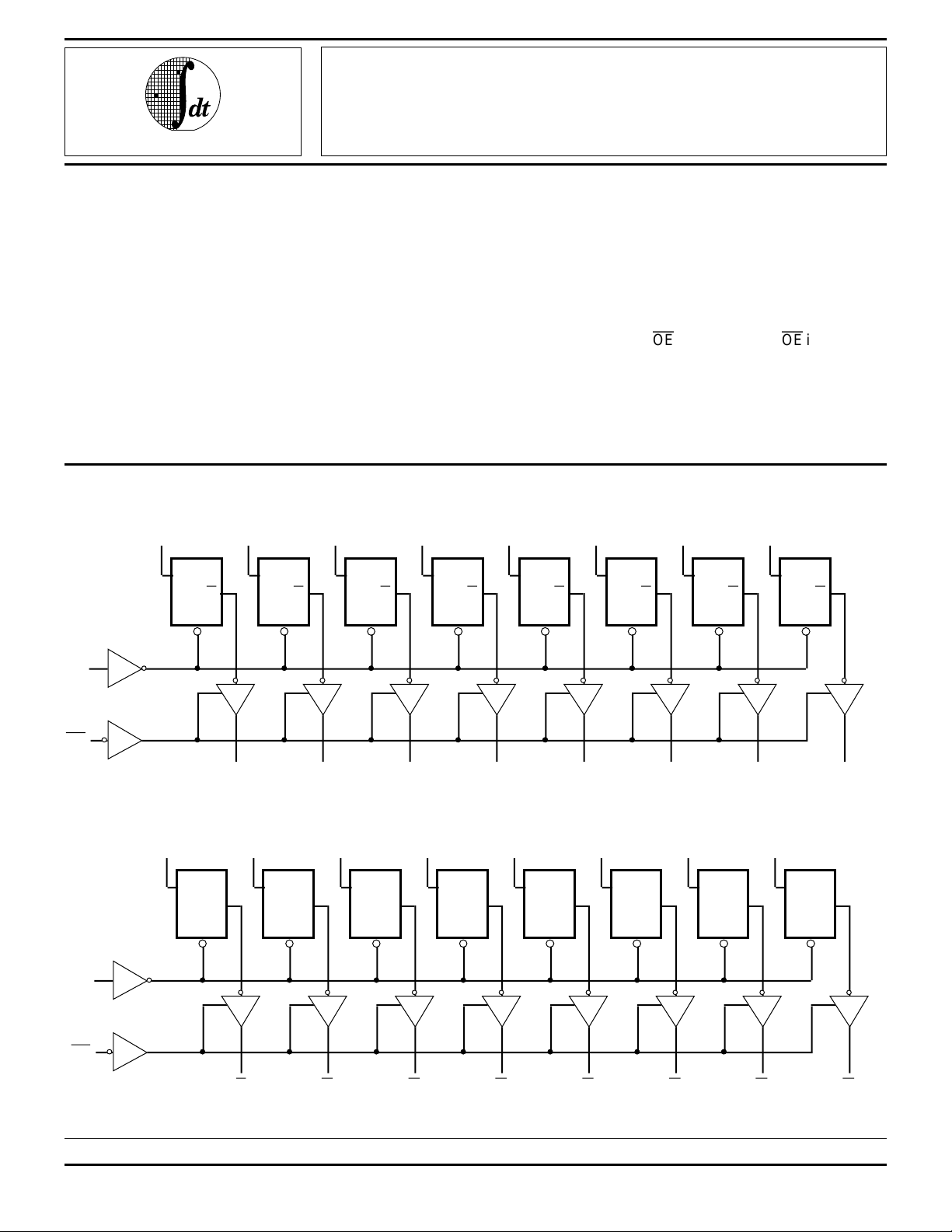

FUNCTIONAL BLOCK DIAGRAMS

IDT54/74FCT373 AND IDT54/74FCT573

D

0

D

G

D

1

D

O

G

D

2

D

O

D

3

D

O

G

DESCRIPTION

The IDT54/74FCT373/A/C, IDT54/74FCT533/A/C and

IDT54/74FCT573/A/C are octal transparent latches built using an advanced dual metal CMOS technology. These octal

latches have 3-state outputs and are intended for bus oriented

applications. The flip-flops appear transparent to the data

when Latch Enable (LE) is HIGH. When LE is LOW, the data

that meets the set-up time is latched. Data appears on the bus

when the Output Enable (OE) is LOW. When OE is HIGH, the

bus output is in the high-impedance state.

D

4

D

O

G

G

D

5

D

O

G

D

6

D

O

G

D

7

D

O

G

O

LE

OE

0

O

1

O

2

O

3

O

4

O

5

O

6

O

7

O

2602 cnv* 01

IDT54/74FCT533

D0

D

G

LE

OE

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FAST is a trademark of National Semiconductor Co.

D1

D

O

G

0

O

D2

D

O

G

1

O

D3

D

O

G

2

O

D4

D

O

G

3

O

D5

D

O

G

4

O

D6

D

O

G

5

O

D7

D

O

O

G

6

O

7

O

2602 cnv* 02

MILITARY AND COMMERCIAL TEMPERATURE RANGES MAY 1992

1992 Integrated Device Technology, Inc. 7.12 DSC-4624/2

1

IDT54/74FCT373/533/573/A/C

FAST CMOS OCTAL TRANSPARENT LATCHES MILITARY AND COMMERCIAL TEMPERATURE RANGES

PIN CONFIGURATIONS

IDT54/74FCT373

IDT54/74FCT573

OE

O0

D0

D1

O1

O2

D2

D3

O3

GND

2

3

4

5

6

7

8

9

10 11

DIP/SOIC/CERPACK

OE

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

GND

DIP/SOIC/CERPACK

20

19

18

P20-1

D20-1

SO20-2

E20-1

17

16

15

&

14

13

12

TOP VIEW

1

2

3

4

5

6

7

8

9

P20-1

D20-1

SO20-2

E20-1

20

19

18

17

16

15

&

14

13

12

10 11

TOP VIEW

VCC1

O

D7

D6

O6

O5

D

D4

O4

LE

INDEX

O0

7

D1

O1

O2

5

D2

D3

D0

3 2 20 19

4

1

5

6

L20-2

7

8

OE

VCC

O7

18

D7

D6

17

O6

16

O5

15

14

D5

9 10111213

4

LE

D4

O

O3

GND

LCC

TOP VIEW

V

O

O

O

O

O

O

O

O

LE

CC

0

1

2

3

4

5

6

7

INDEX

0

1

D

D

3 2 20 19

D

D

D

D

D

4

2

5

3

4

6

7

5

8

6

1

L20-2

9 10111213

7

D

OE

LE

CC

V

7

O

0

O

6

O

18

17

16

15

14

O

1

O

2

O

3

O

4

O

5

GND

LCC

TOP VIEW

IDT54/74FCT533

OE

O

0

2

D0

D1

O1

O2

D2

D3

O3

GND

3

4

5

6

7

8

9

10 11

DIP/SOIC/CERPACK

P20-1

D20-1

SO20-2

&

E20-1

TOP VIEW

20

19

18

17

16

15

14

13

12

VCC1

O

D7

D6

O6

O5

D

D4

O4

LE

INDEX

7

D1 D7

O1

O2

5

D2

D3

4

5

6

7

8

0D0

O

3 2 20 19

1

L20-2

OE

CC

V

7

O

18

D

17

16

15

14

6

O6

O5

D5

9 10111213

4

LE

4

O

D

3

O

GND

LCC

TOP VIEW

7.12 2

2602 cnv* 03–08

IDT54/74FCT373/533/573/A/C

FAST CMOS OCTAL TRANSPARENT LATCHES MILITARY AND COMMERCIAL TEMPERATURE RANGES

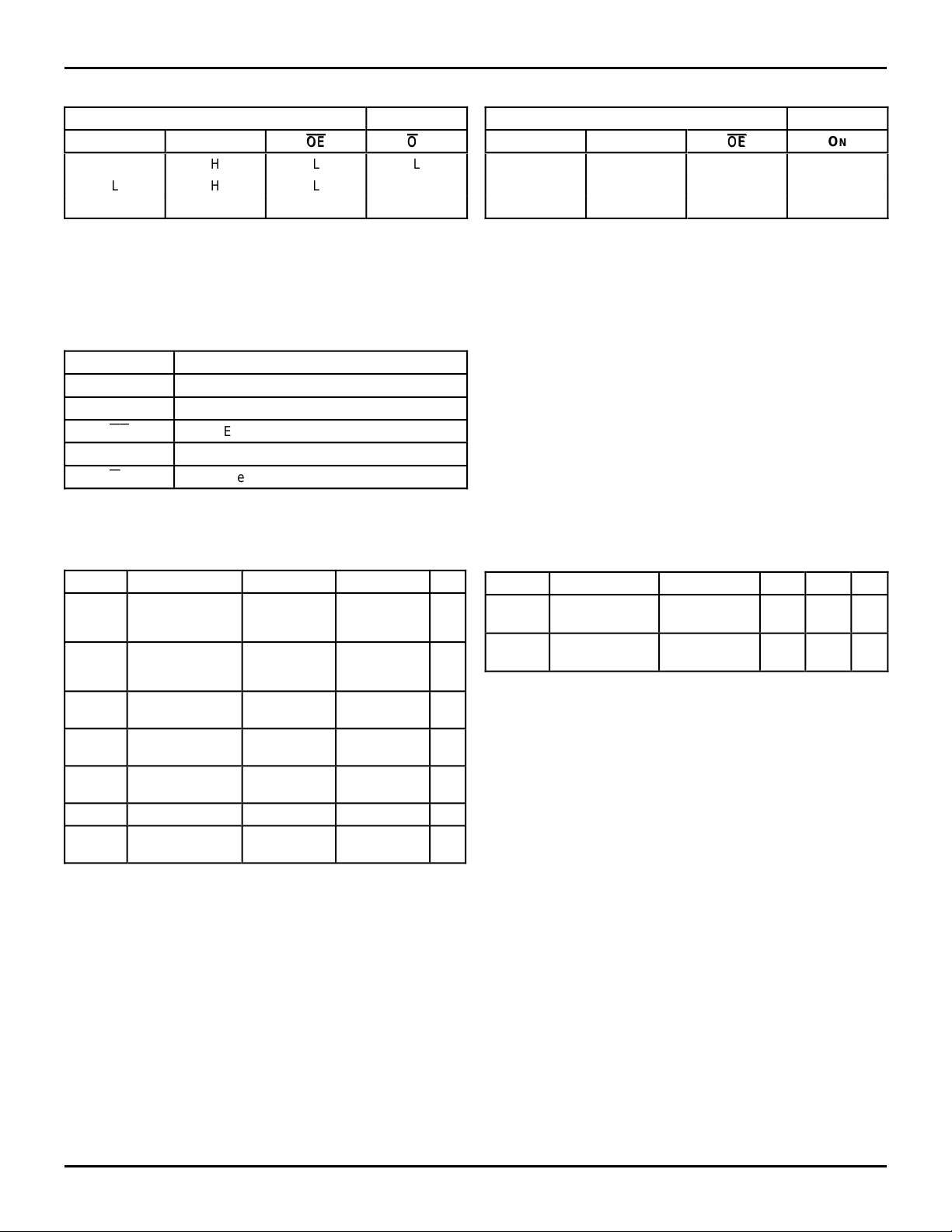

FUNCTION TABLE (FCT533)

(1)

FUNCTION TABLE (FCT373 and FCT573)

(1)

Inputs Outputs

DN LE

OE

OE

O

N

O

HHLL

LHLH

XXHZ

NOTE:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

Z = High Impedance

2602 tbl 05

PIN DESCRIPTION

Pin Names Description

DN Data Inputs

LE Latch Enable Input (Active HIGH)

OE

ON 3-State Outputs

O

N Complementary 3-State Outputs

ABSOLUTE MAXIMUM RATINGS

Symbol Rating Commercial Military Unit

(2)

VTERM

VTERM

TA Operating

TBIAS Temperature

TSTG Storage

PT Power Dissipation 0.5 0.5 W

IOUT DC Output

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM

RATINGS may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability. No terminal voltage

may exceed V

2. Input and V

3. Outputs and I/O terminals only.

Terminal Voltage

with Respect to

GND

(3)

Terminal Voltage

with Respect to

GND

Temperature

Under Bias

Temperature

Current

Output Enable Input (Active LOW)

–0.5 to +7.0 –0.5 to +7.0 V

–0.5 to V

CC –0.5 to VCC V

0 to +70 –55 to +125 °C

–55 to +125 –65 to +135 °C

–55 to +125 –65 to +150 °C

120 120 mA

CC by +0.5V unless otherwise noted.

CC terminals only.

2602 tbl 07

(1)

2602 tbl 01

Inputs Outputs

DN LE

OE

OE

ON

HHLH

LHLL

XXHZ

NOTE:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

Z = High Impedance

2602 tbl 06

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter Conditions Typ. Max. Unit

CIN Input

Capacitance

COUT Output

Capacitance

NOTE: 2602 tbl 02

1. This parameter is measured at characterization but not tested.

VIN = 0V 6 10 pF

VOUT = 0V 8 12 pF

7.12 3

Loading...

Loading...