Integrated Device Technology Inc IDT74FCT574TDB, IDT74FCT574TD, IDT74FCT574TQB, IDT74FCT574TQ, IDT74FCT574TPYB Datasheet

...

MILITARY AND COMMERCIAL TEMPERATURE RANGES AUGUST 1995

1995 Integrated Device Technology, Inc. 6.13 DSC-4214/5

Integrated Device Technology, Inc.

DESCRIPTION

The FCT374T/FCT2374T, FCT534T and FCT574T/

FCT2574T are 8-bit registers built using an advanced dual

metal CMOS technology. These registers consist of eight Dtype flip-flops with a buffered common clock and buffered 3state output control. When the output enable (OE) input is

LOW, the eight outputs are enabled. When the OE input is

HIGH, the outputs are in the high-impedance state.

Input data meeting the set-up and hold time requirements

of the D inputs is transferred to the Q outputs on the LOW-toHIGH transition of the clock input.

The FCT2374T and FCT2574T have balanced output drive

with current limiting resistors. This offers low ground bounce,

minimal undershoot and controlled output fall times-reducing

the need for external series terminating resistors. FCT2xxxT

parts are plug-in replacements for FCTxxxT parts.

1

FAST CMOS OCTAL D

REGISTERS (3-STATE)

FEATURES:

• Common features:

– Low input and output leakage ≤1µA (max.)

– CMOS power levels

– True TTL input and output compatibility

– VOH = 3.3V (typ.)

– V

OL = 0.3V (typ.)

– Meets or exceeds JEDEC standard 18 specifications

– Product available in Radiation Tolerant and Radiation

Enhanced versions

– Military product compliant to MIL-STD-883, Class B

and DESC listed (dual marked)

– Available in DIP, SOIC, SSOP, QSOP, CERPACK

and LCC packages

• Features for FCT374T/FCT534T/FCT574T:

– Std., A, C and D speed grades

– High drive outputs (-15mA IOH, 48mA IOL)

• Features for FCT2374T/FCT2574T:

– Std., A, and C speed grades

– Resistor outputs (-15mA IOH, 12mA IOL Com.)

(-12mA IOH, 12mA IOL Mil.)

– Reduced system switching noise

D0

Q0

D1

Q1

D2

Q2

D3

Q3

D4

Q4

D5

Q5

D6

Q6

D7

Q7

CP

OE

D

Q

CP

D

CP

D

CP

D

CP

D

CP

D

CP

D

CP

D

CP

2569 drw 01

QQQ Q

Q

QQ

2569 drw 02

D0

Q0

D1

Q1

D2

Q2

D3

Q3

D4

Q4

D5

Q5

D6

Q6

D7

Q7

CP

OE

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

D

Q

CP

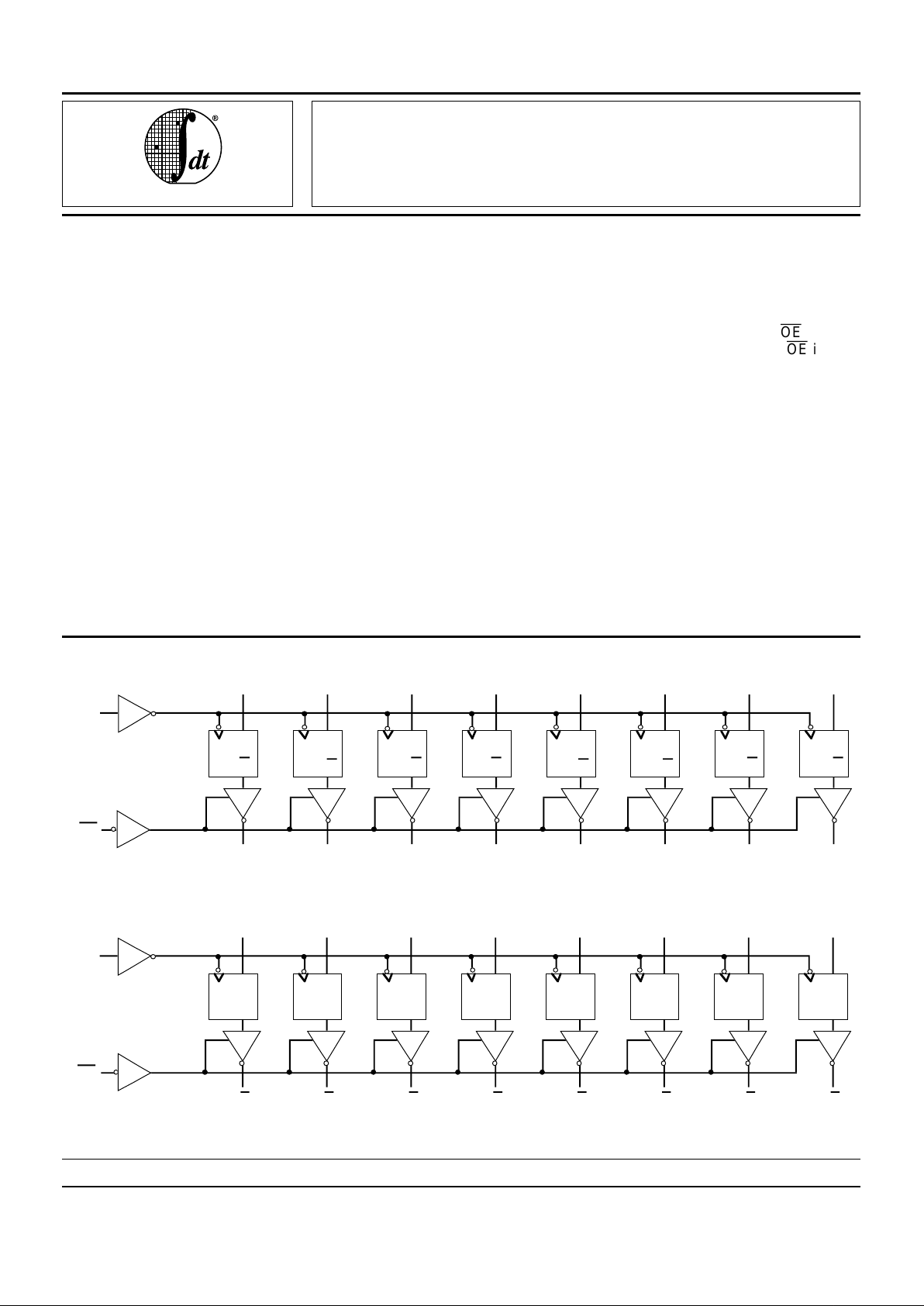

FUNCTIONAL BLOCK DIAGRAM FCT534T

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

IDT54/74FCT374T/AT/CT/DT - 2374T/AT/CT

IDT54/74FCT534T/AT/CT

IDT54/74FCT574T/AT/CT/DT - 2574T/AT/CT

FUNCTIONAL BLOCK DIAGRAM FCT374/FCT2374T AND FCT574/FCT2574T

6.13 2

IDT54/74FCT374T/AT/CT/DT - 2374T/AT/CT, IDT54/74FCT534T/AT/CT, IDT54/74FCT574T/AT/CT/DT - 2574T/AT/CT

FAST CMOS OCTAL D REGISTERS (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

IDT54/74FCT534T

PIN CONFIGURATIONS

IDT54/74FCT374T

IDT54/74FCT574T

2569 drw 04

2569 drw 05

2569 drw 03

INDEX

D

1

Q

1

Q

2

D

2

D

3

D

7

D

6

Q

6

Q

5

D

5

LCC

TOP VIEW

3 2 20 19

1

4

5

6

7

8

18

17

16

15

14

910111213

L20-2

D

0Q0

OE

V

CCQ7

Q

3

GND

CP

Q

4

D

4

OE

Q

0

D0

D1

Q1

Q2

D2

D3

Q3

GND

Q

7

D7

D6

Q6

Q5

D4

CP

D

5

Q4

VCC1

2

3

4

5

6

7

8

9

10 11

12

13

14

15

16

17

18

19

20

DIP/SOIC/SSOP/QSOP/CERPACK

TOP VIEW

P20-1

D20-1

SO20-2

SO20-7

SO20-8

&

E20-1

OE

D

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

GND

Q

0

Q

1

Q

2

Q

3

Q

4

Q

6

CP

Q

5

Q

7

V

CC

1

2

3

4

5

6

7

8

9

10 11

12

13

14

15

16

17

18

19

20

DIP/SOIC/SSOP/QSOP/CERPACK

TOP VIEW

P20-1

D20-1

SO20-2

SO20-7

SO20-8

&

E20-1

OE

Q

0

D0

D1

Q1

Q2

D2

D3

Q3

GND

Q

7

D7

D6

Q6

Q5

D4

CP

D

5

Q4

VCC1

2

3

4

5

6

7

8

9

10 11

12

13

14

15

16

17

18

19

20

DIP/SOIC/QSOP/CERPACK

TOP VIEW

P20-1

D20-1

SO20-2

SO20-8

&

E20-1

INDEX

D1 D7

LCC

TOP VIEW

D

6

Q6

Q5

D5

Q1

Q2

D2

D3

3 2 20 19

1

4

5

6

7

8

18

17

16

15

14

9 10111213

L20-2

D0

VCC

Q7

Q0

OE

Q3

GND

CP

Q

4

D4

INDEX

D2

D3

D4

D5

D6

Q1

Q2

Q3

Q4

Q5

D7

GND

CP

Q

7

Q6

LCC

TOP VIEW

3 2 20 19

1

4

5

6

7

8

18

17

16

15

14

9 10111213

L20-2

D1

D0

OE

V

CC

Q0

IDT54/74FCT374T/AT/CT/DT - 2374T/AT/CT, IDT54/74FCT534T/AT/CT, IDT54/74FCT574T/AT/CT/DT - 2574T/AT/CT

FAST CMOS OCTAL D REGISTERS (3-STATE) MILITARY AND COMMERCIAL TEMPERATURE RANGES

6.13 3

PIN DESCRIPTION

FUNCTION TABLE

(1)

ABSOLUTE MAXIMUM RATINGS

(1)

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Rating Commercial Military Unit

VTERM

(2)

Terminal Voltage

with Respect to

GND

–0.5 to +7.0 –0.5 to +7.0 V

VTERM

(3)

Terminal Voltage

with Respect to

GND

–0.5 to

V

CC +0.5

–0.5 to

VCC +0.5

V

TA Operating

Temperature

0 to +70 –55 to +125 °C

TBIAS Temperature

Under Bias

–55 to +125 –65 to +135 °C

TSTG Storage

Temperature

–55 to +125 –65 to +150 °C

PT Power Dissipation 0.5 0.5 W

IOUT DC Output

Current

–60 to +120 –60 to +120 mA

2569 tbl 01

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions

above those indicated in the operational sections of this specification is

not implied. Exposure to absolute maximum rating conditions for

extended periods may affect reliability. No terminal voltage may exceed

V

CC by +0.5V unless otherwise noted.

2. Input and V

CC terminals only.

3. Outputs and I/O terminals only.

2569 lnk 03

NOTE: 2569 tbl 02

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

Z = High Impedance

NC = No Change

↑ = LOW-to-HIGH transition

NOTE:

1. This parameter is measured at characterization but not tested.

2569 lnk 04

Symbol Parameter

(1)

Conditions Typ. Max. Unit

CIN Input

Capacitance

VIN = 0V 6 10 pF

COUT Output

Capacitance

VOUT = 0V 8 12 pF

Pin Names Description

DN D flip-flop data inputs

CP Clock Pulse for the register. Enters data on

LOW-to-HIGH transition.

QN 3-state outputs, (true)

Q

N 3-state outputs, (inverted)

OE

Active LOW 3-state Output Enable input

534 374/574

Inputs Outputs Internal Outputs Internal

Function

OE

OE

CP DN

Q

Q

N QN QN

Q

Q

N

HI-Z H

H

L

H

X

X

Z

Z

NC

NC

Z

Z

NC

NC

LOAD REGISTER L

L

H

H

↑

↑

↑

↑

L

H

L

H

H

L

Z

Z

L

H

L

H

L

H

Z

Z

H

L

H

L

Loading...

Loading...