Integrated Device Technology Inc IDT74AUCR16245BVI, IDT74AUCR16245PAI, IDT74AUCR16245PFI Datasheet

IDT74AUCR16245

1.8V CMOS 16-BIT BUS TRANSCEIVER WITH 3-STATE OUTPUTS

INDUSTRIAL TEMPERATURE RANGE

1.8V CMOS 16-BIT BUS

TRANSCEIVER WITH

3-STATE OUTPUTS

FEA TURES:

• ESD > 2000V per MIL-STD-883, Method 3015; > 200V using

machine model (C = 200pF, R = 0)

• 1.8V Optimized

• 0.8V to 2.7V Operating Range

• Inputs/outputs tolerant up to 3.6V

• Output drivers: ±4.5mA @ VDD = 2.3V

• Low switching noise

• Supports hot insertion

• Available in TSSOP, TVSOP, and VFBGA packages

APPLICA TIONS:

• High performance, low voltage communications systems

• High performance, low voltage computing systems

IDT74AUCR16245

ADVANCE

INFORMATION

DESCRIPTION:

This 16-bit bus transceiver is built using advanced CMOS technology. The

AUCR16245 is designed specifically for asynchronous communications between data buses. The control function implementation minimizes external timing

requirements.

This device can be used as one 16-bit transceiver or two 8-bit transceivers.

It allows data transmission from A bus to B bus or from B bus to A bus, depending

on the logic level at the direction-control (DIR) input. The output-enable (OE)

input can be used to disable the device so that the buses are effectively isolated.

This device is fully specified for partial power-down applications using IOFF.

The IOFF circuitry disables the outputs, preventing damaging current backflow

through the device when it is powered down.

The AUCR16245 has series resistors in the device output structure which will

reduce line noise when used with light loads. This driver has been designed

with a ±4.5mA output driver at the designated threshold levels.

To ensure the high-impedance state during power up or power down, OE

should be tied to VDD through a pull-up resistor; the minimum value of the resistor

is determined by the current-sinking capability of the driver.

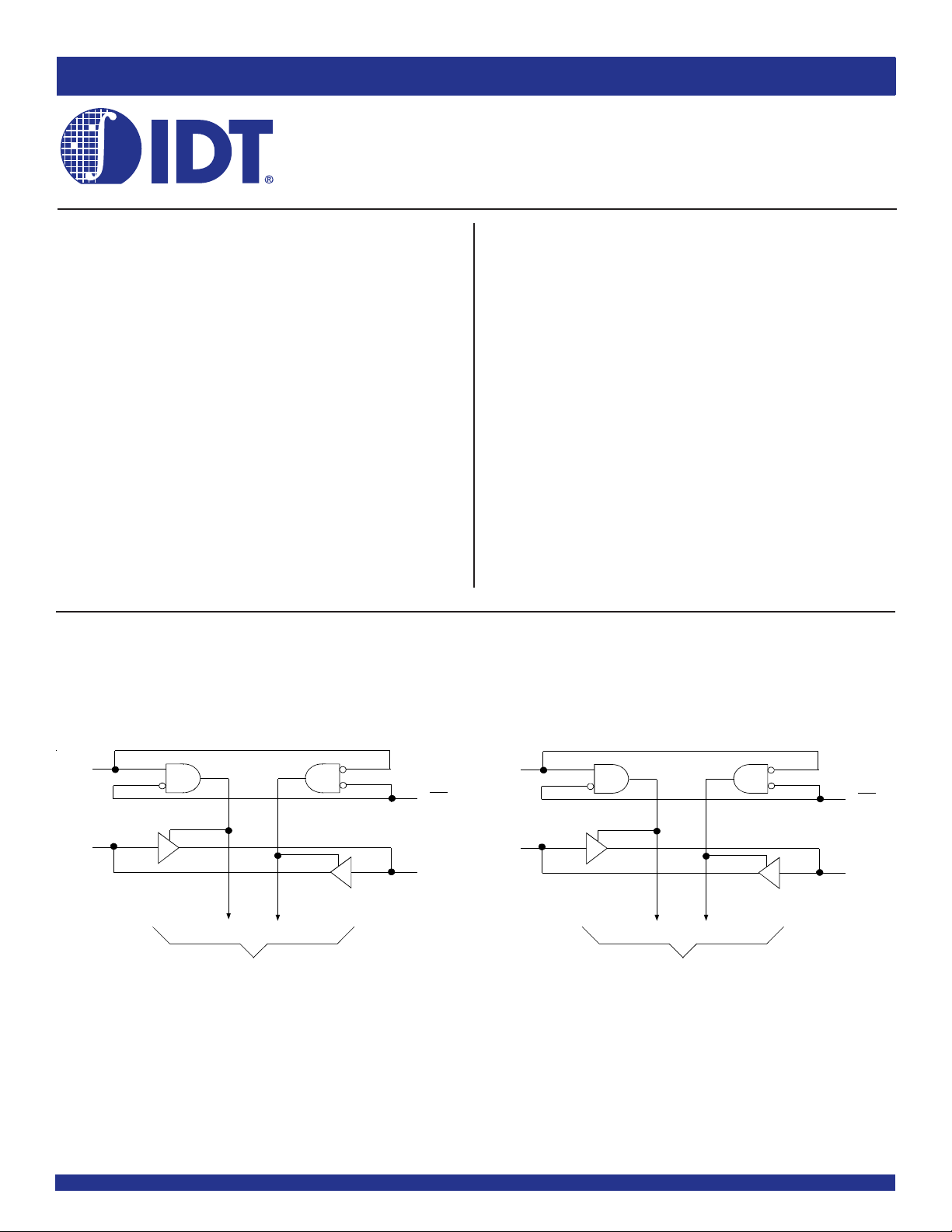

FUNCTIONAL BLOCK DIAGRAM

1

1DIR

47

1A1

TO SEVEN OTHER CHANNELS

24

2DIR

48

1OE

36

2A1

2

1

B1

TO SEVEN OTHER CHANNELS

25

2OE

13

2

B1

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

INDUSTRIAL TEMPERATURE RANGE

1

© 2003 Integrated Device Technology, Inc. DSC-5969/10

JUNE 2003

IDT74AUCR16245

1.8V CMOS 16-BIT BUS TRANSCEIVER WITH 3-STATE OUTPUTS

PINOUT CONFIGURATION

INDUSTRIAL TEMPERATURE RANGE

1OE

6

NC

5

NC

4

NC

3

NC

2

1DIR

1

A

NOTE:

NC = No Internal Connection

1A2

1A1

GND

GND

1B1

1B2

B

1A4

1A3

V

DD

VDD

1B3

1B4

C

1A6

1A5

GND

GND

1B5

1B6

D

1A8

1A7

1B7

1B8

E

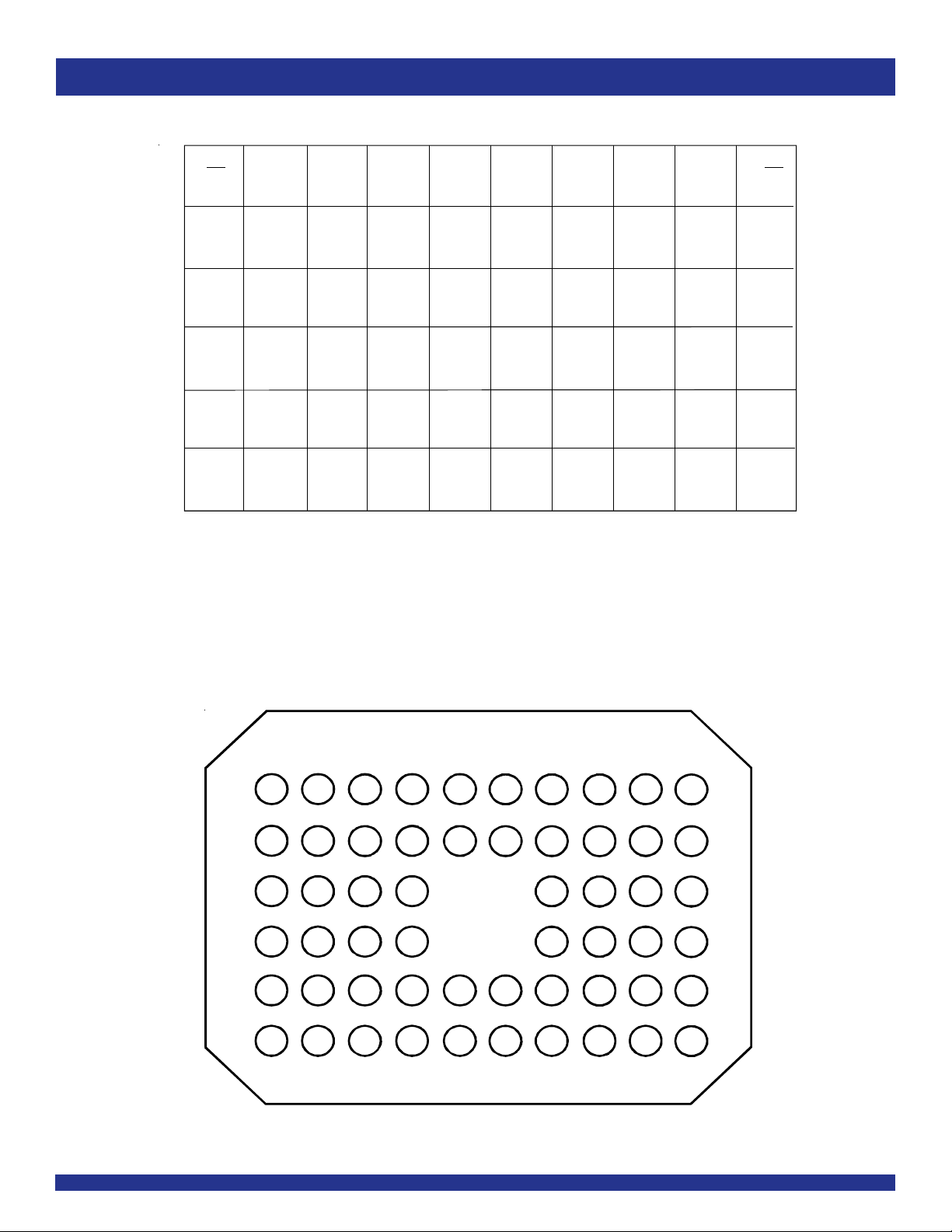

VFBGA

2A1

2A2

2B2

2B1

F

2A3

2A4

GND

GND

2B4

2B3

G

2A5

2A6

V

DD

VDD

2B6

2B5

H

2A7

2A8

GND

GND

2B8

2B7

J

2OE

NC

NC

NC

NC

2DIR

K

56 BALL VFBGA P ACKAGE LA YOUT

A B C D E F G H J K

6

5

4

3

2

1

TOP VIEW

2

IDT74AUCR16245

1.8V CMOS 16-BIT BUS TRANSCEIVER WITH 3-STATE OUTPUTS

INDUSTRIAL TEMPERATURE RANGE

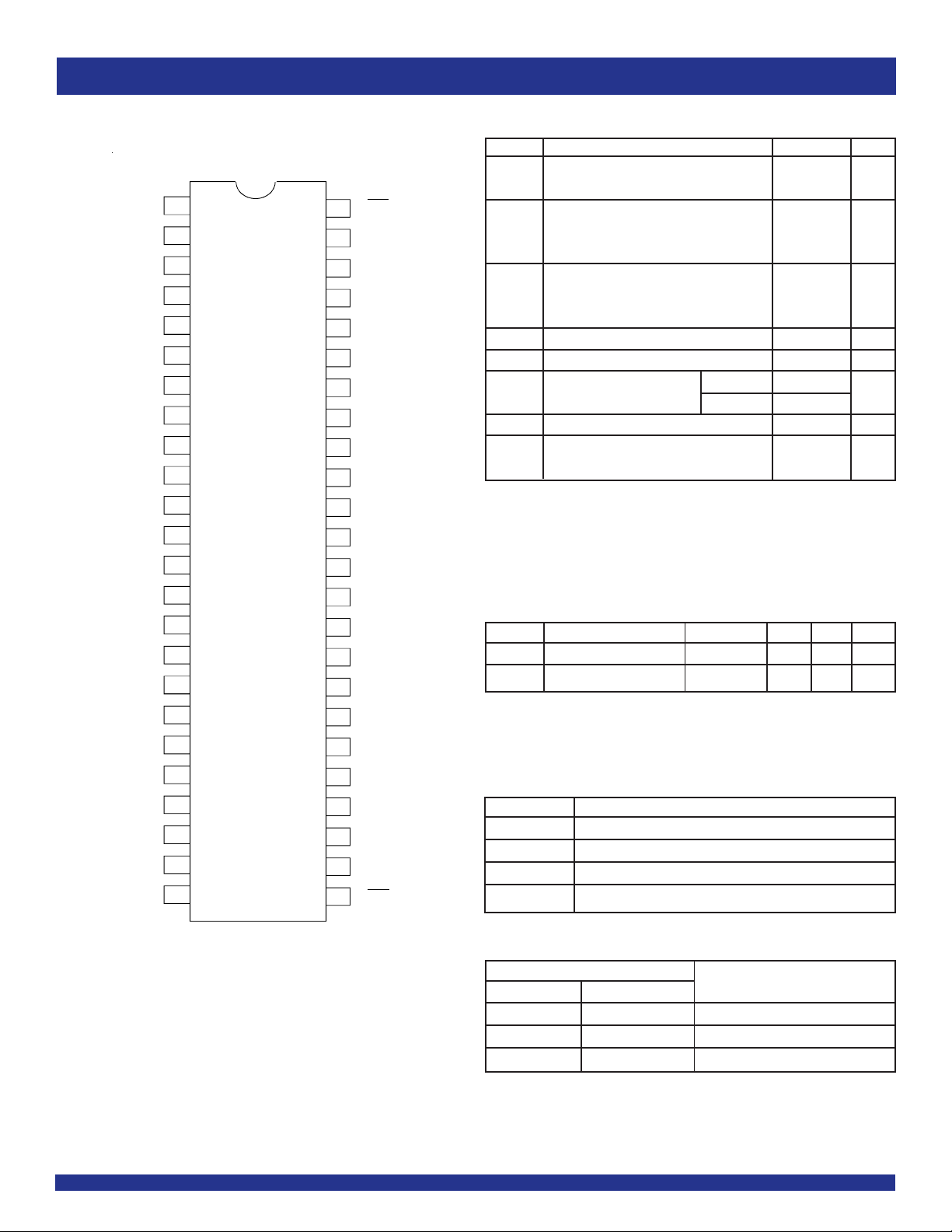

PIN CONFIGURATION

1DIR

1B1

B2

1

GND

1B3

B4

1

VDD

1

B5

B6

1

GND

1B7

B8

1

B1

2

1

2

3

4

5

6

7

8

9

10

11

12

13

48

47

46

45

44

43

42

41

40

39

38

37

36

1OE

1A1

A2

1

GND

1A3

A4

1

VDD

A5

1

1

A6

GND

1

A7

A8

1

2

A1

ABSOLUTE MAXIMUM RATINGS

Symbol Description Max Unit

V

TERM Terminal Voltage with Respect to GND –0.5 to +3.6 V

(all input and VDD terminals)

V

TERM Terminal Voltage with Respect to GND –0.5 to +3.6 V

(any I/O or Output terminals in highimpedance or power-off state)

V

TERM Terminal Voltage with Respect to GND –0.5 to +3.6 V

(any I/O or Output terminals in high or

low state)

TSTG Storage Temperature –65 to +150 °C

IOUT Continuous DC Output Current ±20 mA

I

IK Continuous Clamp Current VI > VDD +50 mA

VI < 0 –50

IOK Continuous Clamp Current, VO < 0 –50 mA

I

DD Continuous Current through ±100 mA

I

SS each VDD or GND

NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

(1)

2

B2

GND

2B3

2

B4

DD

V

B5

2

2

B6

GND

2B7

2

B8

2

DIR

14

15

16

17

18

19

20

21

22

23

24

TSSOP/ TVSOP

TOP VIEW

35

34

33

32

31

30

29

28

27

26

25

A2

2

GND

2A3

2

A4

VDD

2

A5

2

A6

GND

2A7

A8

2

OE

2

CAPACITANCE (TA = +25°C, f = 1.0MHz, VDD = 2.5V)

Symbol Parameter Conditions Typ. Max. Unit

CIN Input Capacitance

C

I/O I/O Port Capacitance

NOTES:

1. Applies to the Control Inputs.

2. Applies to ports A and B.

(1)

VIN = 0V 3 pF

(2)

VIN = 0V 8 pF

PIN DESCRIPTION

Pin Names Description

xOE 3-State Output Enable Inputs (Active Low)

xDIR Di rec tio n Co ntrol Inputs

xAx A Side Inputs or 3-State Outputs

xBx B Side Inputs or 3-State Outputs

FUNCTION T ABLE (EACH 8-BIT SECTION)

Inputs

xOE xDIR Outputs

L L Bus B Data to Bus A

L H Bus A Data to Bus B

HXZ

NOTE:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don't Care

Z = High-Impedance

(1)

3

Loading...

Loading...