Integrated Device Technology Inc IDT72V71643BC, IDT72V71643DA Datasheet

3.3 VOLT TIME SLOT INTERCHANGE

DIGITAL SWITCH WITH RATE

MATCHING

4,096 x 4,096

FEATURES:

••

•

Up to 32 serial input and output streams

••

••

•

Maximum 4,096 x 4,096 channel non-blocking switching

••

••

•

Accepts data streams at 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s or

••

16.384 Mb/s

••

Rate matching capability: Mux/Demux mode and Split mode

•

••

••

• Output Enable Indication Pins

••

••

• Per-channel Variable Delay mode for low-latency applications

••

••

• Per-channel Constant Delay mode for frame integrity applications

••

••

•

Automatic identification of ST-BUS® and GCI serial streams

••

••

Automatic frame offset delay measurement

•

••

••

Per-stream frame delay offset programming

•

••

••

• Per-channel high-impedance output control

••

••

• Per-channel Processor mode to allow microprocessor writes to

••

TX streams

••

• Direct microprocessor access to all internal memories

••

••

•

Memory block programming for quick setup

••

••

• IEEE-1149.1 (JTAG) Test Port

••

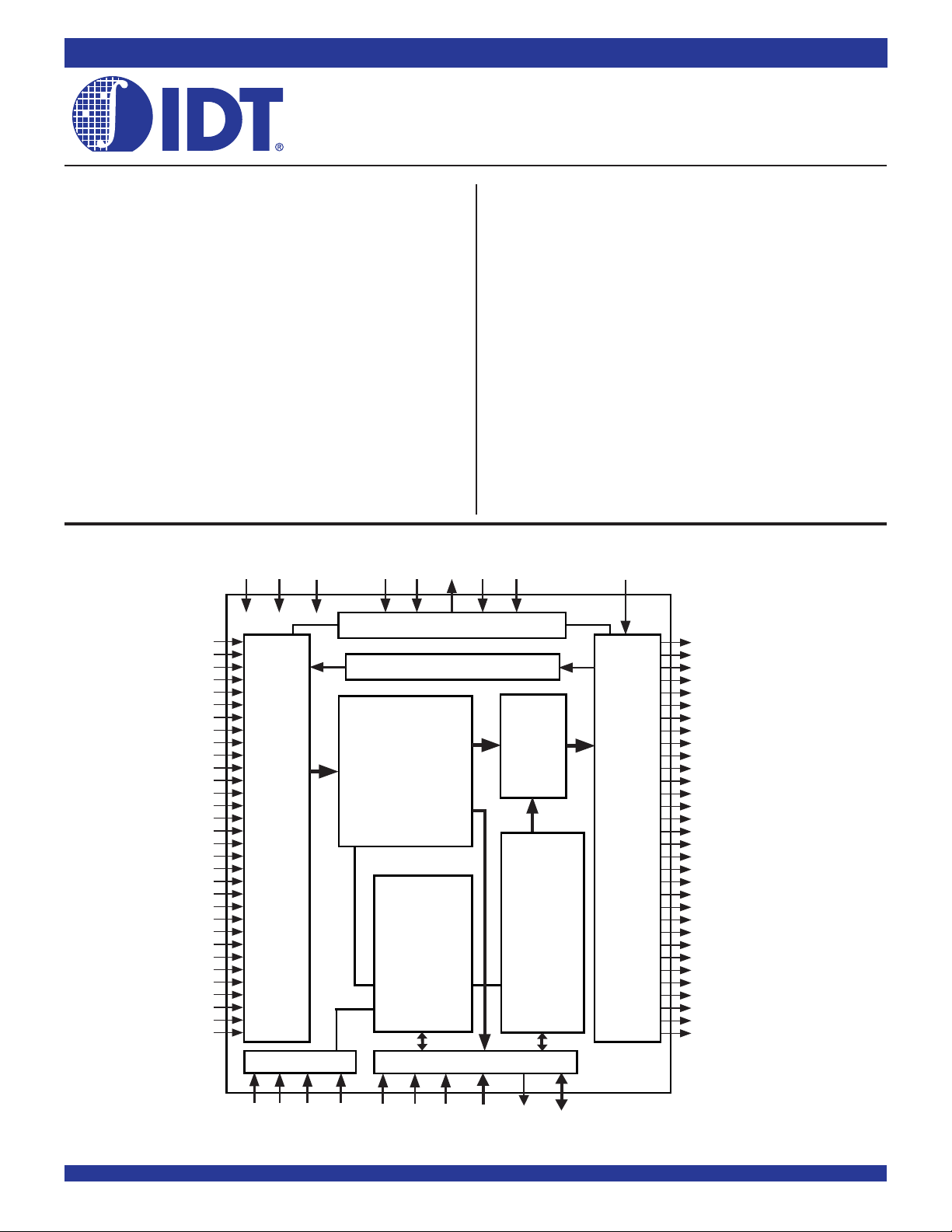

FUNCTIONAL BLOCK DIAGRAM

IDT72V71643

••

•

Internal Loopback for testing

••

••

•

Available in 144-pin Thin Quad Flatpack (TQFP) and

••

144-pin Ball Grid Array (BGA) packages

••

Operating Temperature Range -40

•

••

••

• 3.3V I/O with 5V tolerant inputs and TTL compatible outputs

••

°°

°C to +85

°°

DESCRIPTION:

The IDT72V71643 has a maximum non-blocking switch capacity of

4,096 x 4,096 channels with data rates at 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s

or 16.384 Mb/s. With 32 inputs and 32 outputs, a variety of rate combinations

is supported, under either Mux/Demux mode or Split mode, to allow for

switching between streams of different data rates.

Output enable indications are provided through optional pins (one pin per

output stream, only 16 output streams can be used in this mode) to facilitate

external data bus control.

For applications requiring 32 streams and 32 per-stream Output Enable

indicators, there is also an All Output Enable Feature.

°°

°C

°°

RX0

RX1

RX2

RX3

RX4

RX5

RX6

RX7

RX8

RX9

RX10

RX11

RX12

RX13

RX14

RX15

RX16

RX17

RX18

RX19

RX20

RX21

RX22

RX23

RX24

RX25

RX26

RX27

RX28

RX29

RX30

RX31

Vcc

GND

Receive

Serial Data

Streams

RESET

TDITMS TCKTDO

Loopback

Data Memory

Internal

Registers

Test Port

TRST

Output

MUX

Connection

Memory

ODE

Transmit

Serial Data

Streams

TX0

TX1

TX2

TX3

TX4

TX5

TX6

TX7

TX8

TX9

TX10

TX11

TX12

TX13

TX14

TX15

TX16/OEI0

TX17/OEI1

TX18/OEI2

TX19/OEI3

TX20/OEI4

TX21/OEI5

TX22/OEI6

TX23/OEI7

TX24/OEI8

TX25/OEI9

TX26/OEI10

TX27/OEI11

TX28/OEI12

TX29/OEI13

TX30/OEI14

TX31/OEI15

Microprocessor InterfaceTiming Unit

5902 drw01

CLK FE/

F0i

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. The ST-BUS® is a trademark of Mitel Corp.

HCLK

WFPS

CSDS

R/W A0-A14

DTA

D0-D15

MAY 2002

1

2002 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. DSC-5902/6

IDT72V71643 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 4,096 x 4,096

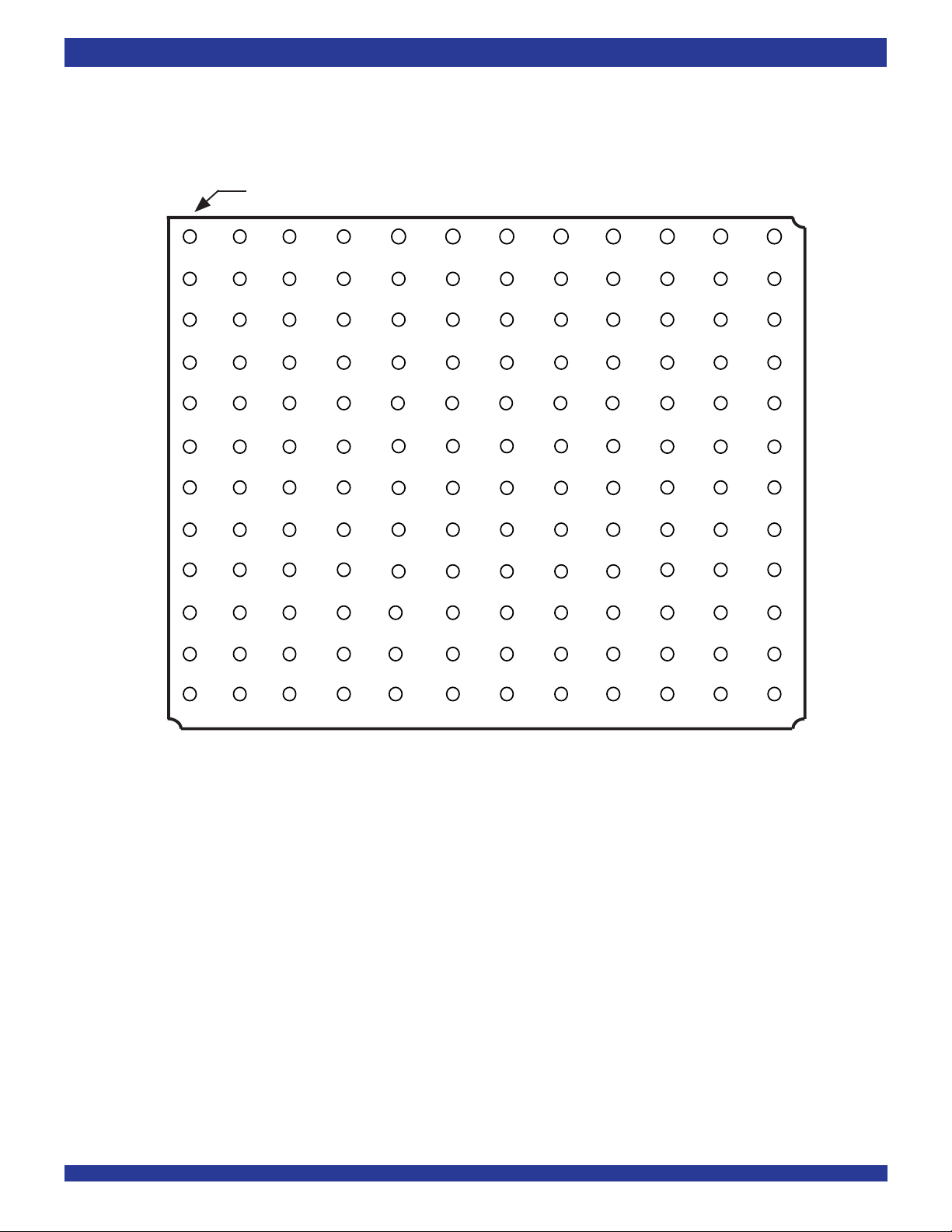

PIN CONFIGURATIONS

A1 BALL PAD CORNER

A

RX0 RX1 RX3 RX6 TX1 TX4 TX7 RX10 RX12 RX15 TX10 TX11

B

CLK ODE RX2 RX5 TX0 TX3 TX6 RX9 RX13 RX14 TX9 TX12

COMMERCIAL TEMPERATURE RANGE

C

FE/HCLK

F0i

D

TMS WFPS TDI VCC VCC VCC VCC VCC VCC TX15 RX16 RX17

RESET

RX4 RX7 TX2 TX5 RX8 RX11 TX8 TX13 TX14

E

TD0 TCK

F

DS CS

G

A0 A1 A2 VCC TX16/

H

A3 A4 A5 A14 TX19/

TRST

R/W VCC RX22 RX23 RX18

VCC RX19 RX20

GND GND GND GND VCC

GND GND GND GND VCC

GND GND GND GND VCC

GND GND GND GND

VCC

OEI10

OEI3

TX17/

OEI1

TX20/

OEI4

J

A6 A7 A8 D15 TX22/

K

A9 A10

L

A11 A12 D12

M

A13 D14 D13 D10 D8 D5 D2

DTA

D9 D6 D3 D0 TX29/

D11 D7

VCC VCC VCC VCC GND

TX26/

OEI10

TX28/

OEI12

D4

D1

OEI13

TX30/

OEI14

TX31/

OEI15

TX27/

OEI11

OEI6

RX27 RX25

TX24/

OEI8

TX25/

OEI9

RX24 TX23/

RX28 RX29

RX31 RX30

123456789101112

RX21

TX18/

OEI2

TX21/

OEI5

OEI7

RX26

5902 drw02

BGA: 1mm pitch, 13mm x 13mm (BC144-1, order code: BC)

NOTES:

1. IC - Internal Connection, tie to Ground for normal operation.

2. All I/O pins are 5V tolerant except for TMS, TDI and TRST.

TOP VIEW

2

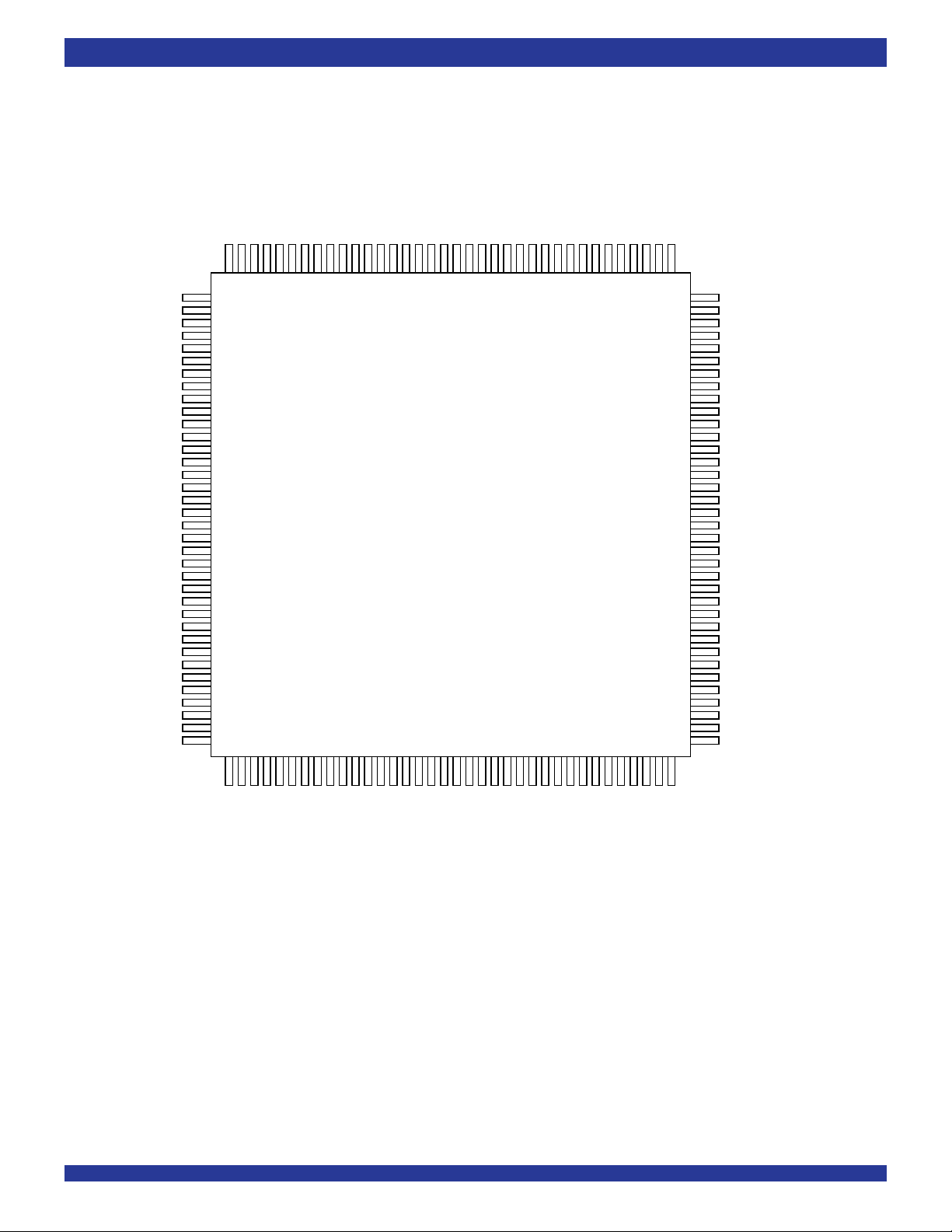

IDT72V71643 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 4,096 x 4,096

PIN CONFIGURATIONS (CONTINUED)

COMMERCIAL TEMPERATURE RANGE

TX11

TX10

GND

TX9

TX8

VCC

RX15

RX14

RX13

RX12

RX11

RX10

RX9

RX8

GND

TX7

TX6

VCC

TX5

TX4

GND

TX3

TX2

VCC

TX1

TX0

GND

RX7

RX6

RX5

RX4

RX3

RX2

RX1

RX0

VCC

TX13

TX12

107

106

GND

105

TX14

104

VCC

108

109

110

111

112

113

114

115

116

117

118

119

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

123456789

TX15

103

VCC

102

RX16

101

RX20

RX18

RX19

RX17

999897969594939291908988878685848382818079787776757473

100

101112131415161718

RX21

RX22

RX23

TX16/OEI0

GND

VCC

TX19/OEI3

TX18/OEI2

TX17/OEI1

2021222324252627282930313233343536

19

TX20/OEI4

GND

VCC

TX22/OEI6

TX21/OEI5

RX24

TX23/OEI7

GND

RX25

RX26

RX27

RX28

RX29

RX30

RX31

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

VCC

TX24/OEI8

TX25/OEI9

GND

TX26/OEI10

TX27/OEI11

VCC

TX28/OEI12

TX29/OEI13

GND

TX30/OEI14

TX31/OEI15

VCC

D0

D1

GND

D2

D3

VCC

D4

D5

GND

D6

D7

VCC

D08

D09

GND

D10

D11

VCC

D12

D13

GND

D14

D15

ODE

GND

RESET

CLK

F0i

FE/HCLK

VCC

WFPS

TMS

TDI

TQFP: 0.50mm pitch, 20mm x 20mm (DA144-1, order code: DA)

NOTES:

1. IC - Internal Connection, tie to Ground for normal operation.

2. All I/O pins are 5V tolerant except for TMS, TDI and TRST.

TDO

TCK

TRST

GND

DS

CS

R/W

A1

A0

VCC

TOP VIEW

3

A3

A4

A2

A5

GND

A9

A7

A8

A6

A10

A11

A12

A13

A14

DTA

VCC

5902 drw03

IDT72V71643 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 4,096 x 4,096

COMMERCIAL TEMPERATURE RANGE

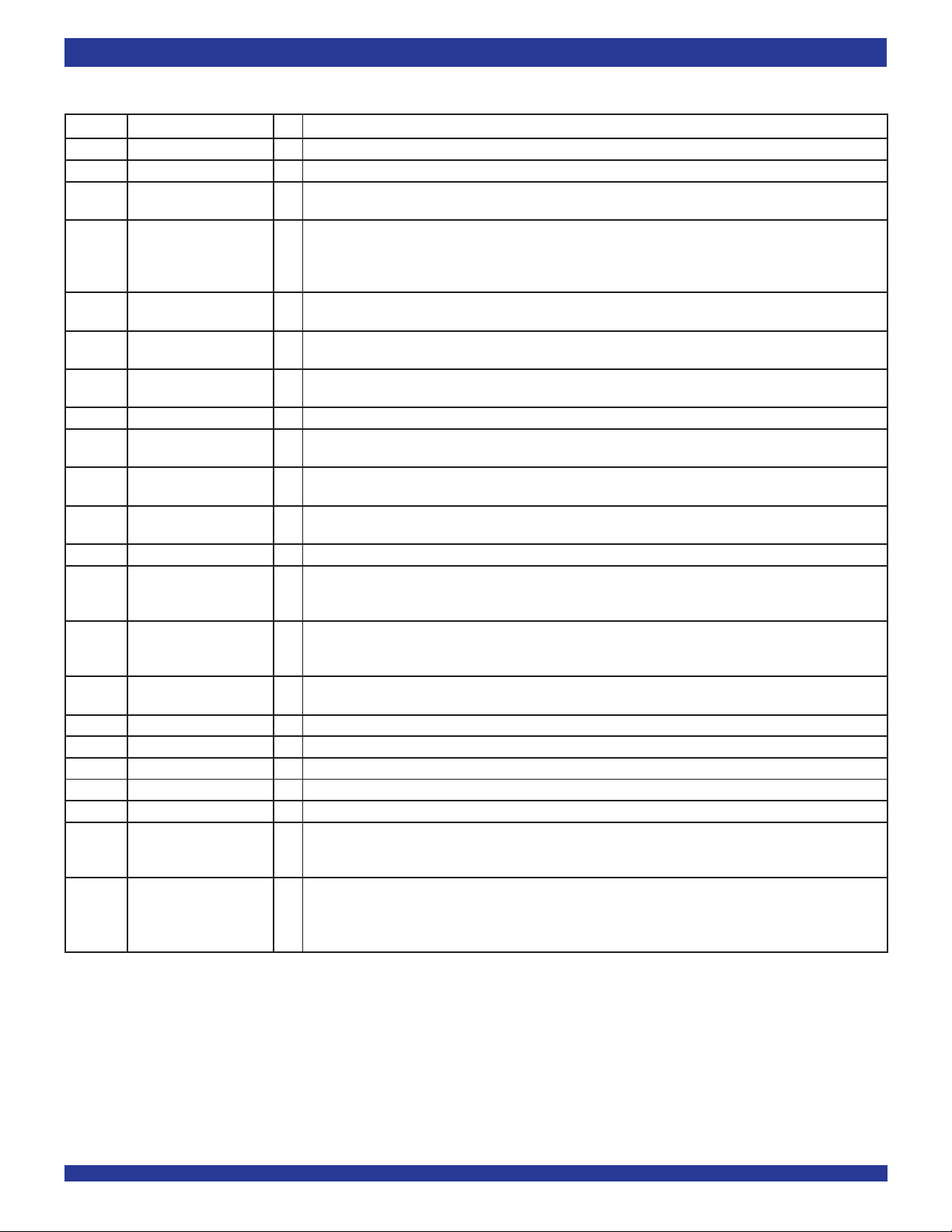

PIN DESCRIPTION

SYMBOL NAME I/O DESCRIPTION

GND Ground. Ground Rail.

Vcc Vcc +3.3 Volt Power Supply.

TX0-15 TX Output 0 to 15 O Serial data output stream. These streams may have a data rate of 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s,

(Three-state Outputs) or 16.384 Mb/s.

TX16-31/ TX Output 16 to 31/ O When all 32 output streams are selected via control register, these pins (TX16-31) are output streams 16 to 31

OEI0-15 Output Enable and may have a data rate of 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s or 16.384 Mb/s. When output enable

Indication 0 to 15 indication function is selected, these pins (OEI 0-15) reflect the active or three-state status for the corresponding,

(Three-state Outputs) (TX0-15) output streams.

RX0-31 RX Input 0 to 31 I Serial data input stream. These streams may have a data rate of 2.048 Mb/s, 4.096 Mb/s, 8.192 Mb/s,

or 16.384 Mb/s.

F0i Frame Pulse I This input accepts and automatically identifies frame synchronization signals formatted according to

ST-BUS® and GCI specifications.

FE/HCLK Frame Evaluation/ I When the WFPS pin is LOW, this pin is the frame measurement input. When the WFPS pin is HIGH, the HCLK

HCLK Clock (4.096 MHZ clock) is required for frame alignment in the wide frame pulse (WFP) mode.

CLK Clock I Serial clock for shifting data in/out on the serial streams (RX/TX 0-31).

TMS Test Mode Select I JTAG signal that controls the state transitions of the TAP controller. This pin is pulled HIGH by an internal

pull-up when not driven.

TDI Test Serial Data In I JTAG serial test instructions and data are shifted in on this pin. This pin is pulled HIGH by an internal pull-up

when not driven.

TDO Test Serial Data Out O JTAG serial data is output on this pin on the falling edge of TCK. This pin is held in high-impedance state when

JTAG scan is not enabled.

TCK Test Clock I Provides the clock to the JTAG test logic.

TRST Test Reset I Asynchronously initializes the JTAG TAP controller by putting it in the Test-Logic-reset state. This pin is pulled

by an internal pull-up when not driven. This pin should be pulsed LOW on power-up, or held LOW, to ensure

that the IDT72V71643 is in the normal functional mode.

RESET Device Reset I This input (active LOW) puts the IDT72V71643 in its reset state that clears the device internal counters, registers

and brings TX0-31 and microport data outputs to a high-impedance state. In normal operation, the RESET

pin must be held LOW for a minimum of 100ns to reset the device.

WFPS Wide Frame Pulse Select I When 1, enables the wide frame pulse (WFP) Frame Alignment interface. When 0, the device operates in

ST-BUS® /GCI mode.

DS Data Strobe I This active LOW input works in conjunction with CS to enable the read and write operations.

R/W Read/Write I This input controls the direction of the data bus lines during a microprocessor access.

CS Chip Select I Active LOW input used by a microprocessor to activate the microprocessor port of IDT72V71643.

A0-14 Address Bus 0 to 14 I These pins allow direct access to Connection Memory, Data Memory and internal control registers.

D0-15 Data Bus 0-15 I/O These pins are the data bits of the microprocessor port.

DTA Data Transfer O This active LOW signal indicates that a data bus transfer is complete. When the bus cycle ends, this pin drives

Acknowledgment HIGH and then goes high-impedance, allowing for faster bus cycles with a weaker pull-up resistor. A pull-up

resistor is required to hold a HIGH level when the pin is in high-impedance.

ODE Output Drive Enable I This is the output enable control for the TX0-31 serial outputs. When ODE input is LOW and the OSB bit of

the IMS register is LOW, TX0-31 are in a high-impedance state. If this input is HIGH, the TX0-31 output

drivers are enabled. However, each channel may still be put into a high-impedance state by using the per

channel control bit in the Connection Memory.

4

IDT72V71643 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 4,096 x 4,096

COMMERCIAL TEMPERATURE RANGE

DESCRIPTION (CONTINUED)

The IDT72V71643 is capable of switching up to 4,096 x 4,096 channels

without blocking. Designed to switch 64 Kbit/s PCM or N x 64 Kbit/s data, the

device maintains frame integrity in data applications and minimizes throughput

delay for voice applications on a per channel basis.

The serial input streams (RX) and serial output streams (TX) of the

IDT72V71643 can be run up to 16.384 Mb/s allowing 256 channels per 125µs

frame. Depending on the input and output data rates the device can support

up to 32 serial streams.

With two main operating modes, Processor mode and Connection Mode,

the IDT72V71643 can easily switch data from incoming serial streams (Data

Memory) or from the controlling microprocessor (Connection Memory). As

control and status information is critical in data transmission, the Processor mode

is especially useful when there are multiple devices sharing the input and output

streams.

With three main configuration modes, Regular, Mux/Demux, and Split mode

the IDT72V71643 is designed to work in a mixed data-rate environment. In

Mux/Demux mode, all of the input streams work at one data rate and the output

streams at another. Depending on the configuration, more or less serial streams

will be available on the inputs or outputs to maintain a non-blocking switch. In

Split Mode, half of the input streams are set at one rate, while the other half are

set to another rate. In this mode, both input and output streams are symmetrical.

With data coming from multiple sources and through different paths, data

entering the device is often delayed. To handle this problem, the IDT72V71643

has a frame evaluation feature to allow individual streams to be offset from the

frame pulse in half clock-cycle intervals up to +4.5 clock cycles for speeds up

to 8 Mb/s or +2.5 clock cycles for 16 Mb/s. (See Table 8 for maximum allowable

skew).

The IDT72V71643 also provides a JTAG test access port, an internal

loopback feature, memory block programming, a simple microprocessor

interface and automatic ST-BUS®/GCI sensing to shorten setup time, aid in

debugging and ease use of the device without sacrificing capabilities.

FUNCTIONAL DESCRIPTION

DATA AND CONNECTION MEMORY

All data that comes in through the RX inputs go through a serial-to-parallel

conversion before being stored into internal Data Memory. The 8 KHz frame

pulse (F0i) is used to mark the 125µs frame boundaries and to sequentially

address the input channels in Data Memory. The Data Memory is only written

by the device from the RX streams and can be read from either the TX streams

or the microprocessor.

Data output on the TX streams may come from either the Serial Input Streams

(Data Memory) or from the microprocessor (Connection Memory). In the case

that RX input data is to be output, the addresses in Connection Memory are used

to specify a stream and channel of the input. The Connection Memory is setup

in such a way that each location corresponds to an output channel for each

particular stream. In that way, more than one channel can output the same data.

In Processor mode, the microprocessor writes data to the Connection Memory

locations corresponding to the stream and channel that is to be output. The lower

byte (8 least significant bits) of the Connection Memory is output every frame

until the microprocessor changes the data or mode of the channel. By using this

Processor mode capability, the microprocessor can access input and output

time-slots on a per channel basis.

The most significant bits of the Connection Memory are used to control per

channel functions such as Processor mode, Constant or Variable Delay mode,

three-state of output drivers, and the Loopback function.

OPERATING MODES

In addition to Regular mode where input and output streams are operating

at the same rate, the IDT72V71643 incorporates a rate matching function in two

different modes: Split mode and Mux/Demux mode. In Split mode some of the

input streams are set at one rate, while others are set to another rate. Both input

and output streams are symmetrical. In Mux/Demux mode, all input streams

are operating at the same rate, while output streams are operating at a different

rate. All configurations are non-blocking. These two modes can be entered

by setting the DR3-0 bits in the Control Register, see Table 5.

OUTPUT IMPEDANCE CONTROL

In order to put all streams in three-state, all per-channel three-state control

bits in the Connection Memory are set (MOD0 and MOD1 = 1) or both the ODE

pin and the OSB bit of the Control Register must be zero. If any combination

other than 0-0, for the ODE pin and the OSB bit, is used, the three-state control

of the streams will be left to the state of the MOD1 and MOD0 bits of the Connection

Memory. The IDT72V71643 incorporates a memory block programming

feature to facilitate three-state control after reset. See Table 1 for Output HighImpedance Control.

SERIAL DATA INTERFACE TIMING

When a 16Mb/s serial data rate is required, the master clock frequency

will be running at 16.384MHz resulting in a single-bit per clock. For all other

cases, 2Mb/s, 4Mb/s, and 8Mb/s, the master clock frequency will be twice the

fastest data rate on the serial streams. Use Table 5 to determine clock speed

and DR3-0 bits in the Control Register to setup the device. The IDT72V71643

provides two different interface timing modes, ST-BUS

®

or GCI. The

IDT72V71643 automatically detects the presence of an input frame pulse and

identifies it as either ST-BUS® or GCI.

In ST-BUS®, when running at 16.384MHz, data is clocked out on the

falling edge and is clocked in on the subsquent rising-edge. At all other data

rates, there are two clock cycles per bit and every second falling edge of the

master clock marks a bit boundary and the data is clocked in on the rising edge

of CLK, three quarters of the way into the bit cell. See Figure 17 for timing.

In GCI format, when running at 16.384MHz, data is clocked out on the

rising edge and is clocked in on the subsquent falling edge. At all other data

rates, there are two clock cycles per bit and every second rising edge of the

master clock marks the bit boundary and data is clocked in on the falling edge

of CLK at three quarters of the way into the bit cell. See Figure 18 for timing.

INPUT FRAME OFFSET SELECTION

Input frame offset selection allows the channel alignment of individual input

streams to be offset with respect to the output stream channel alignment (i.e. F0i).

Although input data is synchronous, delays can be caused by variable path

serial backplanes and variable path lengths, which may be implemented in large

centralized and distributed switching systems. Because data is often delayed

this feature is useful in compensating for the skew between clocks.

Each input stream can have its own delay offset value by programming the

frame input offset registers (FOR, Table 7). The frame offset shown is a function

of the data rate, and can be as large as +4.5 master clock (CLK) periods forward

with a resolution of ½ clock period. To determine the maximum offset allowed

see Table 8.

SERIAL INPUT FRAME ALIGNMENT EVALUATION

The IDT72V71643 provides the frame evaluation (FE) input to determine

different data input delays with respect to the frame pulse F0i. Setting the start

frame evaluation (SFE) bit low for at least one frame starts a measurement cycle.

5

IDT72V71643 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 4,096 x 4,096

COMMERCIAL TEMPERATURE RANGE

When the SFE bit in the Control Register is changed from low to high, the

evaluation starts. Two frames later, the complete frame evaluation (CFE) bit of

the frame alignment register (FAR) changes from low to high to signal that a valid

offset measurement is ready to be read from bits 0 to 11 of the FAR register. The

SFE bit must be set to zero before a new measurement cycle is started.

In ST-BUS

®

mode, the falling edge of the frame measurement signal (FE)

is evaluated against the falling edge of the ST-BUS ® frame pulse. In GCI mode,

the rising edge of FE is evaluated against the rising edge of the GCI frame pulse.

See Table 6 and Figure 6 for the description of the frame alignment register.

MEMORY BLOCK PROGRAMMING

The IDT72V71643 provides users with the capability of initializing the entire

Connection Memory block in two frames. To set bits 15 to 13 of every Connection

Memory location, first program the desired pattern in bits 9 to 7 of the Control

Register.

Setting the memory block program (MBP) bit of the control register high

enables the block programming mode. When the block programming enable

(BPE) bit of the Control Register is set to high, the block programming data will

be loaded into the bits 15 to 13 of every Connection Memory location. The other

Connection Memory bits (bit 12 to bit 0) are loaded with zeros. When the memory

block programming is complete, the device resets the BPE bit to zero.

LOOPBACK CONTROL

The loopback control (LPBK) bit of each Connection Memory location allows

the TX output data to be looped backed internally to the RX input for diagnostic

purposes.

If the LPBK bit is high, the associated TX output channel data is internally

looped back to the RX input channel (i.e., data from TXn channel m routes to

the RXn channel m internally); if the LPBK bit is low, the loopback feature is

disabled. For proper per-channel loopback operation, the contents of frame

delay offset registers must be set to zero and the device must be in regular switch

mode (DR3-0 = 0x0, 0x1 or 0x2).

DELAY THROUGH THE IDT72V71643

The switching of information from the input serial streams to the output serial

streams results in a throughput delay. The device can be programmed to

perform time-slot interchange functions with different throughput delay capabilities on a per-channel basis. For voice applications, Variable throughput delay

is best as it ensures minimum delay between input and output data. In wideband

data applications, Constant throughput delay is best as the frame integrity of the

information is maintained through the switch.

The delay through the device varies according to the type of throughput

delay selected in the MOD1 and MOD0 bits of the Connection Memory.

VARIABLE DELAY MODE (MOD1-0 = 0x0)

In this mode, the delay is dependent only on the combination of source and

destination serial stream speed. Although the minimum delay achievable is

dependent on the input and output serial stream speed, if data is switched

out +3 channels of the slowest data rate, the data will be switched out in the same

frame except if the input and output data rates are both 16 Mb/s (DR3-0 = 0x3).

(See Figure 2 for example).

For example, given the input data rate is 2 Mb/s and the output data rate is

8 Mb/s, input channel CH0 can be switch out by output channel CH12. In the

above example the input streams are slower than the output streams. Also, for

every 2 Mb/s time slot there are four 8 Mb/s time slots, thus a three 2 Mb/s channel

delay equates to 12 output channel time slots. See Figure 2 for this example and

other examples of minimum delay to guarantee transmission in the same frame.

CONSTANT DELAY MODE (MOD1-0 = 0x1)

In this mode, frame integrity is maintained in all switching configurations by

making use of a multiple Data Memory buffer. Input channel data is written into

the Data Memory buffers during frame n will be read out during frame n+2.

Figure 1 shows examples of Constant Delay mode.

MICROPROCESSOR INTERFACE

The IDT72V71643’s microprocessor interface looks like a standard RAM

interface to improve integration into a system. With a 15-bit address bus and a

16-bit data bus, read and writes are mapped directly into Data and Connection

memories and require only one Master Clock cycle to access. By allowing the

internal memories to be randomly accessed in one cycle, the controlling

microprocessor has more time to manage other peripheral devices and can

more easily and quickly gather information and setup the switch paths.

Table 2 shows the mapping of the addresses into internal memory blocks,

Table 3 shows the Control Register information and Figure 13 and Figure 14

shows asynchronous and synchronous microprocessor accesses.

MEMORY MAPPING

The address bus on the microprocessor interface selects the internal

registers and memories of the IDT72V71643. The two most significant bits of the

address select between the registers, Data Memory, and Connection Memory.

If A14 and A13 are HIGH, A12-A0 are used to address the Data Memory (Read

Only). If A14 is HIGH and A13 is LOW, A12-A0 are used to address Connection

Memory (Read/Write). If A14 is LOW and A13 is HIGH A12-A9 are used to select

the Control Register, Frame Alignment Register, and Frame Offset Registers.

See Table 2 for mappings.

CONTROL REGISTER

As explained in the Serial Data Interface Timing and Switching Configurations sections, after system power-up, the Control Register should be programmed immediately to establish the desired switching configuration.

The data in the Control Register consists of the Memory Block Programming

bit (MBP), the Block Programming Data (BPD) bits, the Begin Block Programming Enable (BPE), the Output Stand By (OSB), Start Frame Evaluation (SFE),

and Data Rate Select bits (DR 3-0). As explained in the Memory Block

Programming section, the BPE begins the programming if the MBP bit is enabled.

This allows the entire Connection Memory block to be programmed with the

Block Programming Data bits.

CONNECTION MEMORY CONTROL

If the ODE pin or the OSB bit is high, the MOD1-0 bits of each Connection

Memory location controls the output drivers. See Table 1 for detail. The

Processor Channel (PC) mode is entered by a 1-0 of the MOD1-0 of the

Connection Memory. In Processor Channel Mode, this allows the microprocessor to access TX output channels. Once the MOD1-0 bits are set, the lower 8

bits of the Connection Memory will be output on the TX serial streams. Also

controlled in the Connection Memory is the Variable Delay mode or Constant

Delay mode. Each Connection Memory location allows the per-channel

selection between Variable and Constant throughput Delay modes and

Processor mode.

6

IDT72V71643 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 4,096 x 4,096

COMMERCIAL TEMPERATURE RANGE

If the LPBK bit is high, the associated TX output channel data is internally

looped back to the RX input channel (i.e., RXn channel m data comes from the

TXn channel m). If the LPBK bit is low, the loopback feature is disabled. For

proper per-channel loopback operation, the contents of the frame delay offset

registers must be set to zero and the device must be in regular switch mode

(DR3-0 = 0x0, 0x1 or 0x2).

OUTPUT ENABLE INDICATION

The IDT72V71643 has the capability to indicate the state of the outputs (active

or three-state) by enabling the Output Enable Indication (OEI) in the control

register. In the OEI mode however, only half of the output streams are available.

If this same capability is desired with all 32 streams, this can be accomplished

by using two IDT72V71643 devices. In one device, the All Output Enable (AOE)

bit is set to a one while in the other the AOE is set to zero. In this way, one device

acts as the switch and the other as a three-state control device. See Figure 8.

It is important to note if the TSI device is programmed for AOE and the OEI is

also set, the device will be in the AOE mode not OEI.

INITIALIZATION OF THE IDT72V71643

After power up, the IDT72V71643 should be reset. During reset, the internal

registers are put into their default state and all TX outputs are put into three-state.

After reset however, the state of Connection Memory is unknown. As such, the

outputs should be put in high-impedance by holding the ODE low. While the ODE

is low, the microprocessor can initialize the device, program the active paths,

and disable unused outputs by programming the OE bit in Connection Memory.

Once the device is configured, the ODE pin (or OSB bit depending on

initialization) can be switched.

7

IDT72V71643 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 4,096 x 4,096

COMMERCIAL TEMPERATURE RANGE

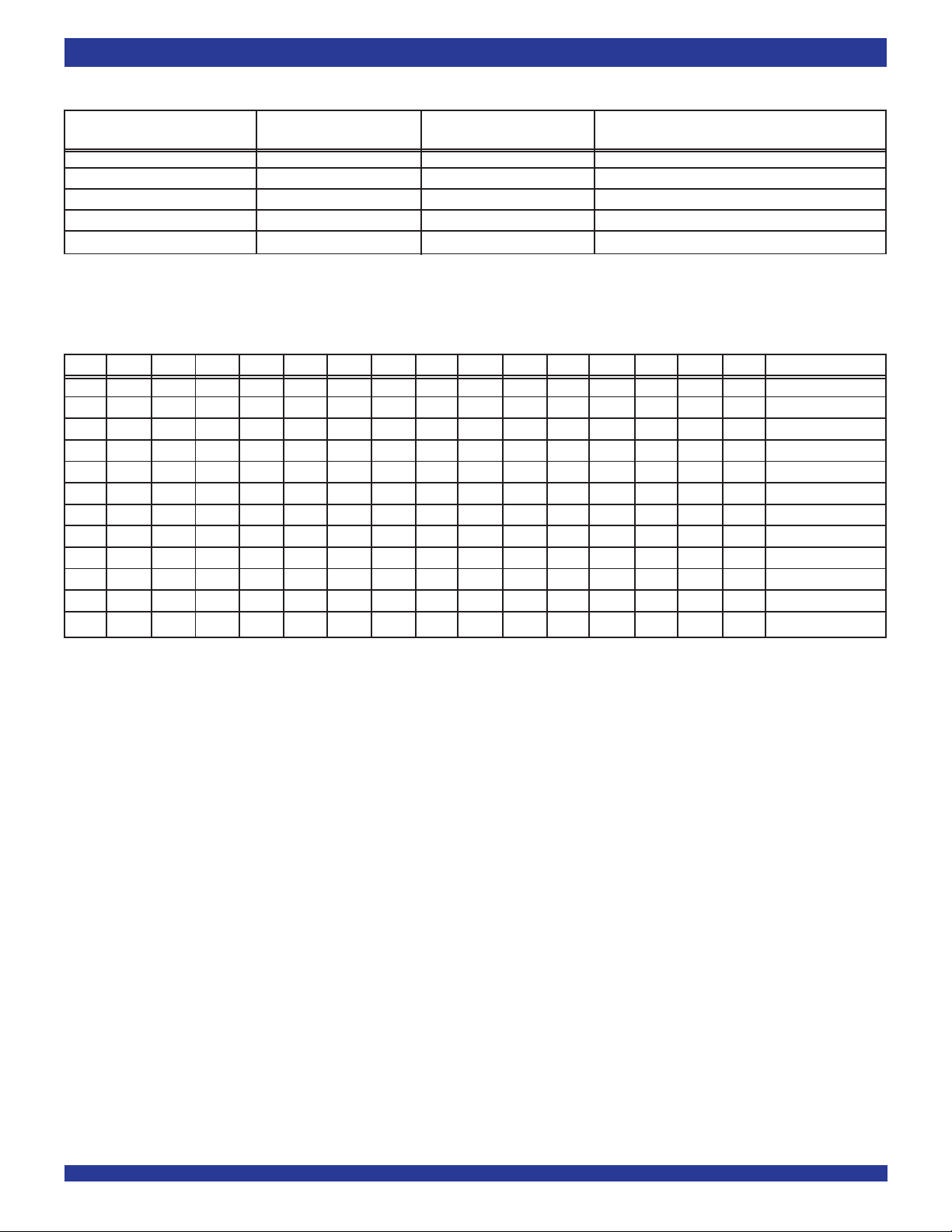

TABLE 1 — OUTPUT HIGH-IMPEDANCE CONTROL

MOD1-0 BITS IN ODE PIN OSB BIT IN CONTROL OUTPUT DRIVER

CONNECTION MEMORY REGISTER STATUS

1 and 1 Don’t Care Don’t Care Per Channel High-Impedance

Any, other than 1 and 1 0 0 High-Impedance

Any, other than 1 and 1 0 1 Enable

Any, other than 1 and 1 1 0 Enable

Any, other than 1 and 1 1 1 Enable

TABLE 2 — INTERNAL REGISTER AND ADDRESS MEMORY MAPPING

A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 R / W Location

1 1 STA4 STA3 STA2 STA1 STA0 CH7 CH6 CH5 CH4 CH3 CH2 CH1 CH0 R Data Memory

1 0 STA4 STA3 STA2 STA1 STA0 CH7 CH6 CH5 CH4 CH3 CH2 CH1 CH0 R/W Connection Memory

0 1 0 0 0 0 x x x x x x x x x R/W Control Register

0 1 0 0 0 1 x x x x x x x x x R Frame Align Register

0 1 0 0 1 0 x x x x x x x x x R/W FOR0

0 1 0 0 1 1 x x x x x x x x x R/W FOR1

0 1 0 1 0 0 x x x x x x x x x R/W FOR2

0 1 0 1 0 1 x x x x x x x x x R/W FOR3

0 1 0 1 1 0 x x x x x x x x x R/W FOR4

0 1 0 1 1 1 x x x x x x x x x R/W FOR5

0 1 1 0 0 0 x x x x x x x x x R/W FOR6

0 1 1 0 0 1 x x x x x x x x x R/W FOR7

8

IDT72V71643 3.3V TIME SLOT INTERCHANGE

DIGITAL SWITCH 4,096 x 4,096

COMMERCIAL TEMPERATURE RANGE

DR3-0 = DH

2 Mb/s → 4 Mb/s

1 Frame (125µsec) 1 Frame (125µsec) 1 Frame (125µsec)

RX 2 Mb/s

TX 4 Mb/s

DR3-0 = 9H

A • • • • Q

• • • •

2 Mb/s → 16 Mb/s

1 Frame (125µsec) 1 Frame (125µsec) 1 Frame (125µsec)

RX 2 Mb/s

TX 16 Mb/s

NOTES:

1. Timeslot Q 2 Frames minimum delay.

2. Timeslot A 3 Frames - 1 output channel period maximum delay.

A • • • • Q

• • • •

Figure 1. Constant Delay Mode Examples

(3)

DR3-0 = 4H

DR3-0 = CH

2 Mb/s → 8 Mb/s

2 Mb/s → 8 Mb/s

1 Channel @ 2 Mb/s

(1)

Q

Q

• • • • A

(1)

• • • • A

(2)

(2)

RX 2 Mb/s

TX 8 Mb/s

DR3-0 = AH

DR3-0 = FH

RX 16 Mb/s

TX 8 Mb/s

DR3-0 = 3H

RX 16 Mb/s

TX 16 Mb/s

ABCDEF

1 Channel @ 8 Mb/s

(1,2)

A

(3)

16 Mb/s → 8 Mb/s

16 Mb/s → 8 Mb/s

1 Channel @ 16 Mb/s

ABC DEF GHI J

1 Channel @ 8 Mb/s

(3,4)

16 Mb/s → 16 Mb/s

A or B

(1,2)

C or D

ABCDEFGH I JKLMNO PQR

ABBBA

NOTES:

1. If data is switched at least +3 channel periods of the slower data rate, the data will transmit out in the same frame except if the input and output data rates are both 16 Mb/s

(DR3-0 = 0x3).

2. Delay is a function of input channel and output channel combinations, and input and output stream data rate.

3. See switching mode table for input and output speed combinations.

4. When the input and output data rates are both 16 Mb/s, the minimum delay achievable is 6 time slots.

Figure 2. Variable Delay Mode Examples

9

Loading...

Loading...