Integrated Device Technology Inc IDT72V36100L10PF, IDT72V36100L15PF, IDT72V36100L15PFI, IDT72V36100L7.5PF, IDT72V36110L10PF Datasheet

...

1

APRIL 2001

DSC-4667/3

2001 Integrated Device Technology, Inc.

3.3 VOLT HIGH-DENSITY SUPERSYNC™ II 36-BIT FIFO

1,024 x 36, 2,048 x 36

4,096 x 36, 8,192 x 36

16,384 x 36, 32,768 x 36

65,536 x36, 131,072 x 36

IDT72V3640, IDT72V3650

IDT72V3660, IDT72V3670

IDT72V3680, IDT72V3690

IDT72V36100, IDT72V36110

The SuperSync II FIFO is a trademark and the IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

FEATURES:

••

••

•

Choose among the following memory organizations:Commercial

IDT72V3640

1,024 x 36

IDT72V3650

2,048 x 36

IDT72V3660

4,096 x 36

IDT72V3670

8,192 x 36

IDT72V3680

16,384 x 36

IDT72V3690

32,768 x 36

IDT72V36100

65,536 x 36

IDT72V36110

131,072 x 36

••

••

•

133 MHz operation (7.5 ns read/write cycle time)

••

••

•

User selectable input and output port bus-sizing

- x36 in to x36 out

- x36 in to x18 out

- x36 in to x9 out

- x18 in to x36 out

- x9 in to x36 out

••

••

•

Big-Endian/Little-Endian user selectable byte representation

••

••

•

5V input tolerant

••

••

•

Fixed, low first word latency

••

••

•

Zero latency retransmit

••

••

•

Auto power down minimizes standby power consumption

••

••

•

Master Reset clears entire FIFO

••

••

•

Partial Reset clears data, but retains programmable settings

••

••

•

Empty, Full and Half-Full flags signal FIFO status

••

••

•

Programmable Almost-Empty and Almost-Full flags, each flag can

default to one of eight preselected offsets

••

••

•

Selectable synchronous/asynchronous timing modes for AlmostEmpty and Almost-Full flags

••

••

•

Program programmable flags by either serial or parallel means

••

••

•

Select IDT Standard timing (using EF and FF flags) or First Word

Fall Through timing (using OR and IR flags)

••

••

•

Output enable puts data outputs into high impedance state

••

••

•

Easily expandable in depth and width

••

••

•

Independent Read and Write Clocks (permit reading and writing

simultaneously)

••

••

•

Available in the 128-pin Thin Quad Flat Pack (TQFP)

••

••

•

High-performance submicron CMOS technology

••

••

•

Industrial temperature range (–40

°°

°°

°C to +85

°°

°°

°C) is available

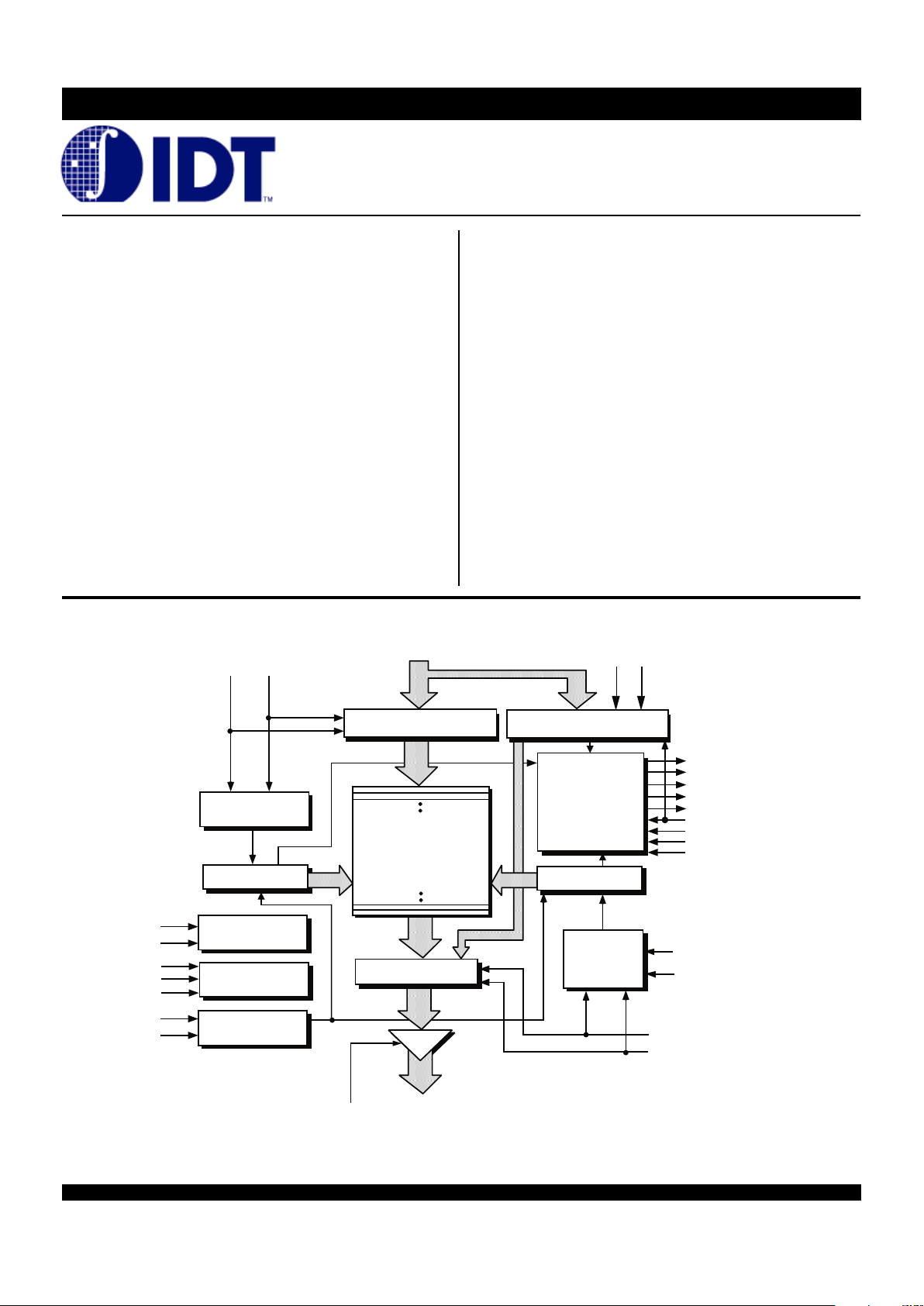

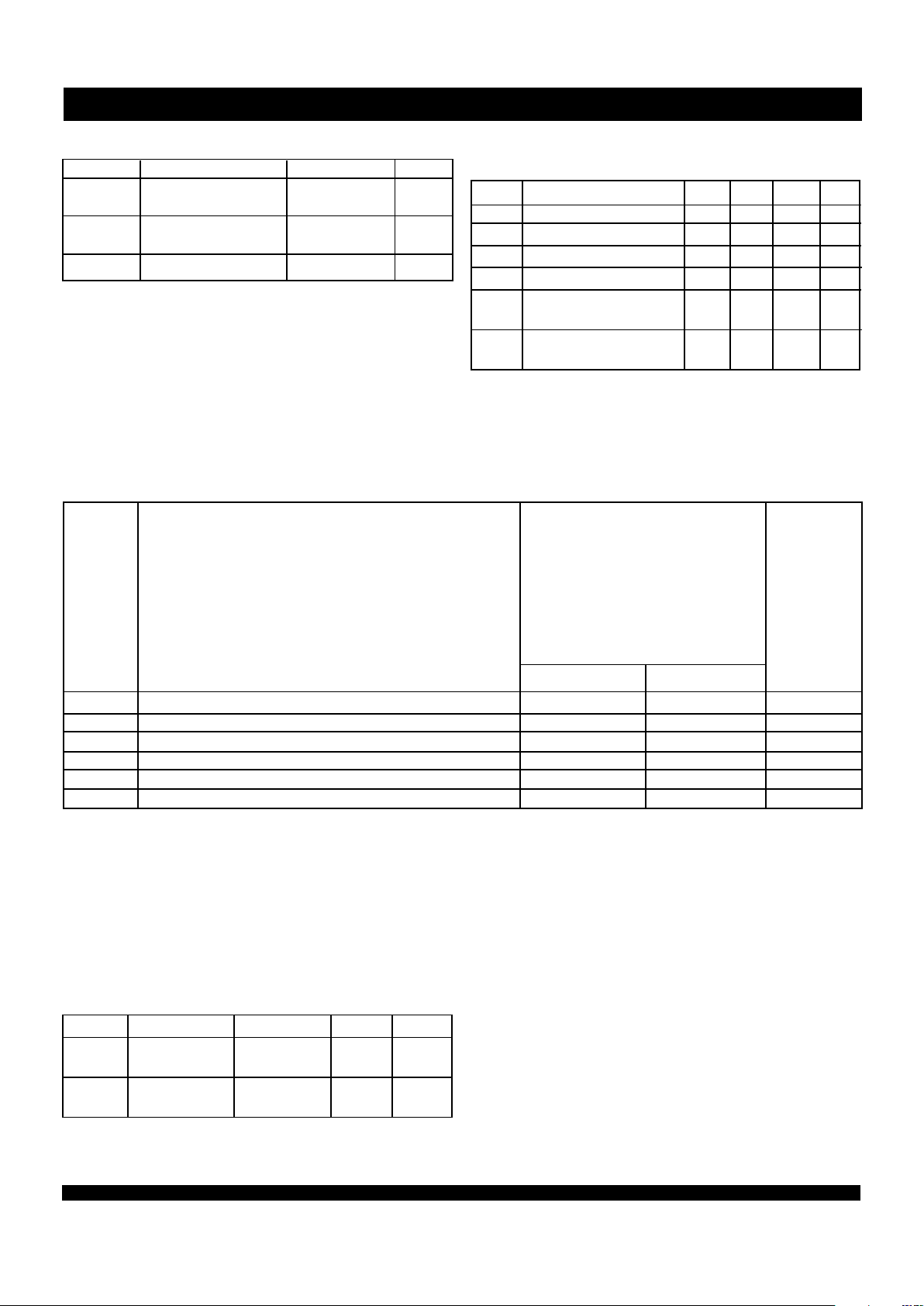

FUNCTIONAL BLOCK DIAGRAM

INPUT REGISTER

OUTPUT REGISTER

RAM ARRAY

1,024 x 36, 2,048 x 36

4,096 x 36, 8,192 x 36

16,384 x 36, 32,768 x 36

65,536 x 36, 131,072 x36

FLAG

LOGIC

FF/IR

PAF

EF/OR

PAE

HF

READ POINTER

READ

CONTROL

LOGIC

WRITE CONTROL

LOGIC

WRITE POINTER

RESET

LOGIC

WEN

WCLK

D

0

-D

n

(x36, x18 or x9)

LD

MRS

REN

RCLK

OE

Q

0

-Qn (x36, x18 or x9)

OFFSET REGISTER

PRS

FWFT/SI

SEN

RT

4667 drw 01

BUS

CONFIGURATION

BM

CONTROL

LOGIC

BE

OW

IP

PFM

FSEL0

FSEL1

IW

RM

2

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

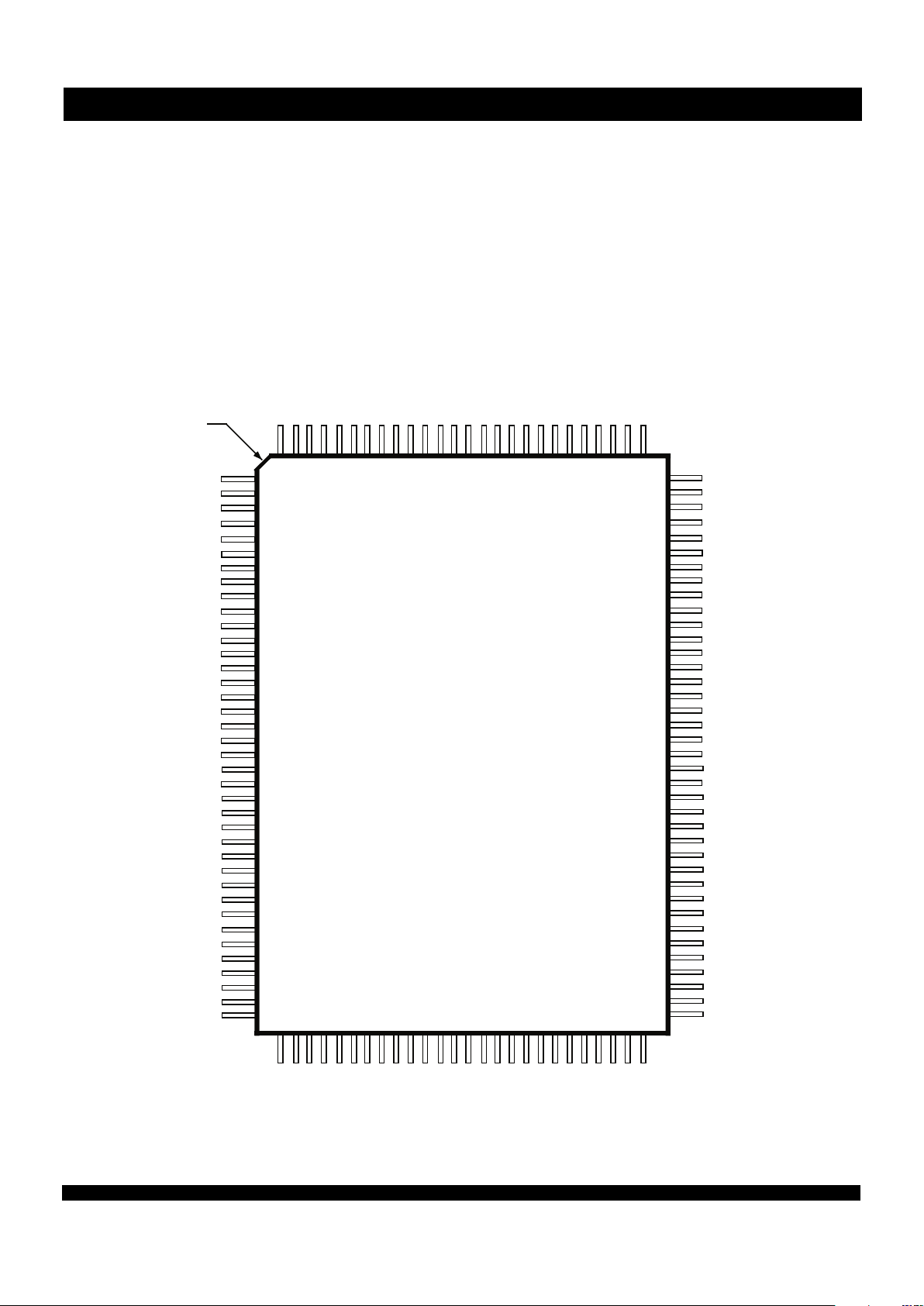

PIN CONFIGURATIONS

TQFP (PK128-1, order code: PF)

TOP VIEW

DESCRIPTION:

The IDT72V3640/72V3650/72V3660/72V3670/72V3680/72V3690/

72V36100/72V36110 are exceptionally deep, high speed, CMOS First-InFirst-Out (FIFO) memories with clocked read and write controls and a flexible

Bus-Matching x36/x18/x9 data flow. These FIFOs offer several key user

benefits:

• Flexible x36/x18/x9 Bus-Matching on both read and write ports

• The period required by the retransmit operation is fixed and short.

• The first word data latency period, from the time the first word is written to an

empty FIFO to the time it can be read, is fixed and short.

• High density offerings up to 4 Mbit

Bus-Matching Sync FIFOs are particularly appropriate for network, video,

telecommunications, data communications and other applications that need to

buffer large amounts of data and match busses of unequal sizes.

Each FIFO has a data input port (D

n) and a data output port (Qn), both of

which can assume either a 36-bit, 18-bit or a 9-bit width as determined by the

state of external control pins Input Width (IW), Output Width (OW), and BusMatching (BM) pin during the Master Reset cycle.

The input port is controlled by a Write Clock (WCLK) input and a Write Enable

(WEN) input. Data is written into the FIFO on every rising edge of WCLK when

WEN is asserted. The output port is controlled by a Read Clock (RCLK) input

and Read Enable (REN) input. Data is read from the FIFO on every rising edge

NOTE:

1. DNC = Do Not Connect.

V

CC

OE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

IW

D35

D34

D33

D32

D31

V

CC

D30

GND

D29

D28

D27

D26

D25

D24

D23

GND

D22

D21

D20

D19

D18

GND

D17

D16

D15

V

CC

D13

D12

GND

D11

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

96

97

98

99

100

102

101

Q35

Q34

Q33

Q32

GND

GND

Q31

Q30

Q29

Q28

Q27

Q26

Q25

Q24

GND

GND

Q23

Q22

Q21

Q20

Q19

Q18

GND

Q17

Q16

Q15

Q14

Q13

Q12

GND

Q11

Q10

INDEX

WEN

SEN

DNC

(1)

D14

V

CC

V

CC

V

CC

V

CC

V

CC

V

CC

4667 drw 02

DNC

(1)

RT

REN

RCLK

PAE

PFM

EF/OR

RM

GND

V

CC

BM

IP

BE

FS1

GND

HF

FS0

OW

GND

PAF

V

CC

FF/IR

FWFT/SI

LD

MRS

PRS

WCLK

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

D10

D9

D8

D7

D6

GND

D5

D4

D2

D1

D0

GND

Q0

Q1

Q2

Q3

Q4

Q5

GND

Q6

Q7

Q9

104

103

Q8

V

CC

V

CC

D3

3

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

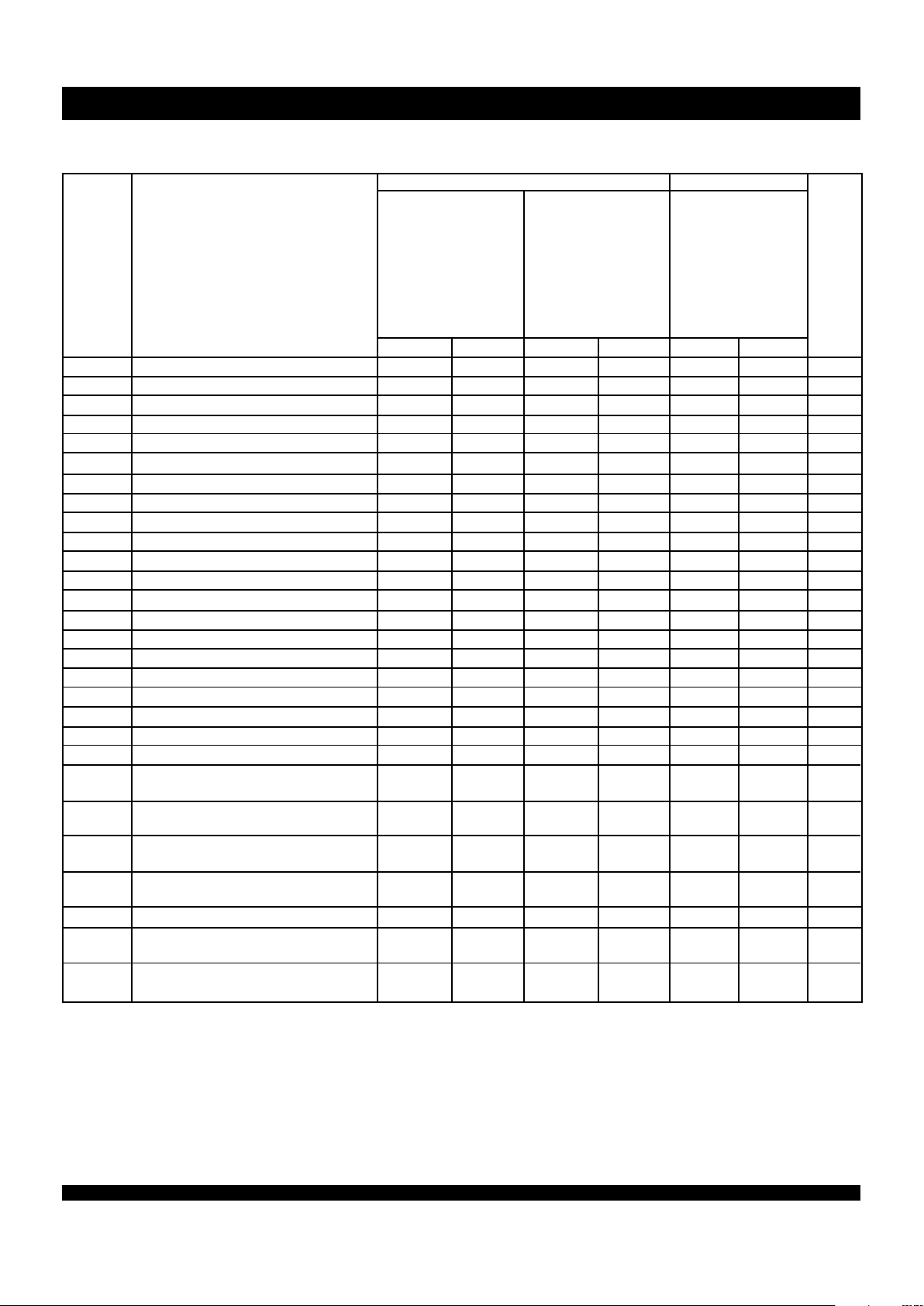

DESCRIPTION (CONTINUED)

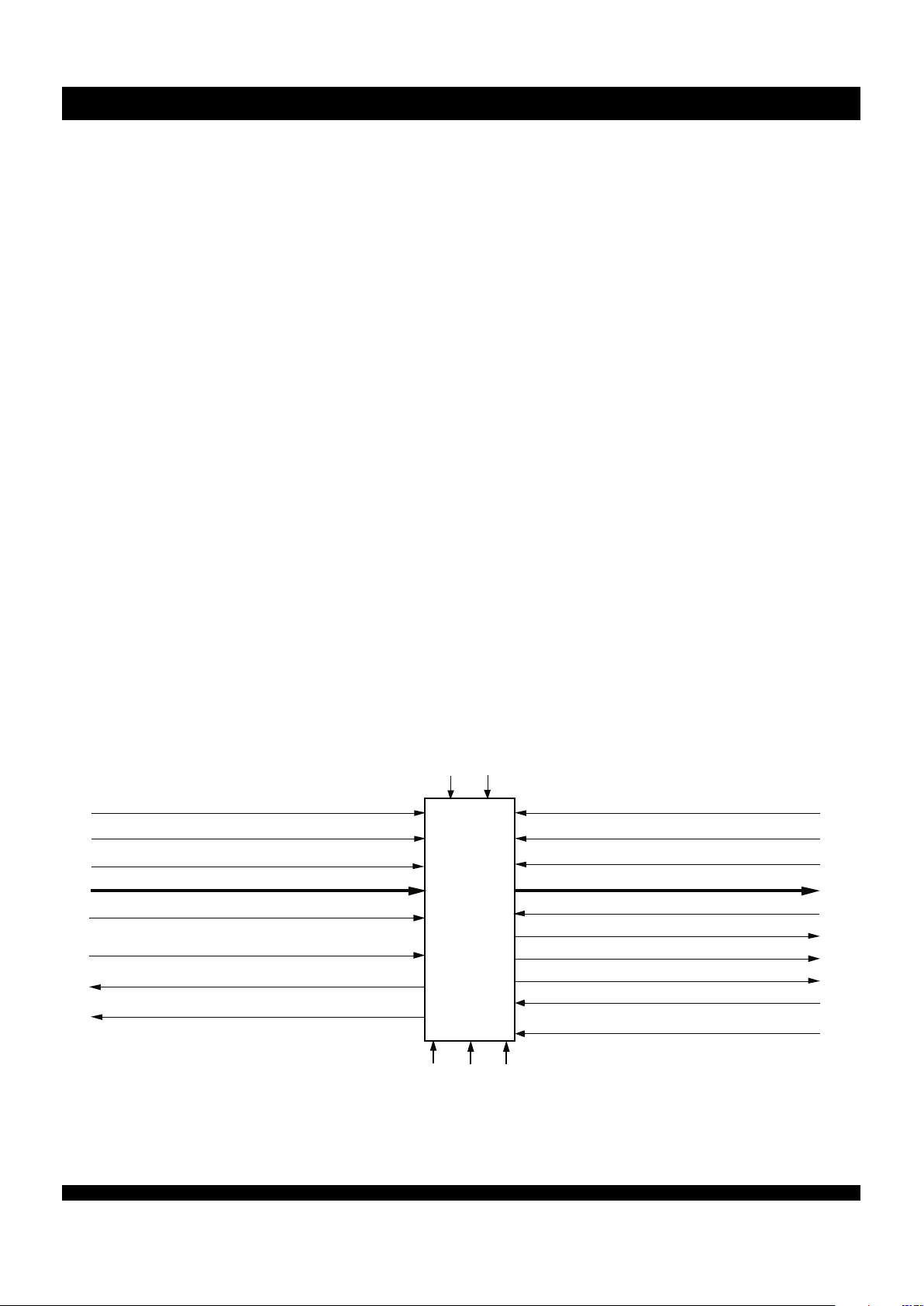

Figure 1. Single Device Configuration Signal Flow Diagram

of RCLK when REN is asserted. An Output Enable (OE) input is provided for

three-state control of the outputs.

The frequencies of both the RCLK and the WCLK signals may vary from 0

to f

MAX with complete independence. There are no restrictions on the frequency

of the one clock input with respect to the other.

There are two possible timing modes of operation with these devices: IDT

Standard mode and First Word Fall Through (FWFT) mode.

In IDT Standard mode, the first word written to an empty FIFO will not appear

on the data output lines unless a specific read operation is performed. A read

operation, which consists of activating REN and enabling a rising RCLK edge,

will shift the word from internal memory to the data output lines.

In FWFT mode, the first word written to an empty FIFO is clocked directly

to the data output lines after three transitions of the RCLK signal. A REN does

not have to be asserted for accessing the first word. However, subsequent

words written to the FIFO do require a LOW on REN for access. The state of

the FWFT/SI input during Master Reset determines the timing mode in use.

For applications requiring more data storage capacity than a single FIFO

can provide, the FWFT timing mode permits depth expansion by chaining FIFOs

in series (i.e. the data outputs of one FIFO are connected to the corresponding

data inputs of the next). No external logic is required.

These FIFOs have five flag pins, EF/OR (Empty Flag or Output Ready),

FF/IR (Full Flag or Input Ready), HF (Half-full Flag), PAE (Programmable

Almost-Empty flag) and PAF (Programmable Almost-Full flag). The EF and FF

functions are selected in IDT Standard mode. The IR and OR functions are

selected in FWFT mode. HF, PAE and PAF are always available for use,

irrespective of timing mode.

PAE and PAF can be programmed independently to switch at any point in

memory. Programmable offsets determine the flag switching threshold and can

be loaded by two methods: parallel or serial. Eight default offset settings are also

provided, so that PAE can be set to switch at a predefined number of locations

from the empty boundary and the PAF threshold can also be set at similar

predefined values from the full boundary. The default offset values are set during

Master Reset by the state of the FSEL0, FSEL1, and LD pins.

For serial programming, SEN together with LD on each rising edge of

WCLK, are used to load the offset registers via the Serial Input (SI). For parallel

programming, WEN together with LD on each rising edge of WCLK, are used

to load the offset registers via D

n. REN together with LD on each rising edge

of RCLK can be used to read the offsets in parallel from Qn regardless of whether

serial or parallel offset loading has been selected.

During Master Reset (MRS) the following events occur: the read and write

pointers are set to the first location of the FIFO. The FWFT pin selects IDT

Standard mode or FWFT mode.

The Partial Reset (PRS) also sets the read and write pointers to the first

location of the memory. However, the timing mode, programmable flag

programming method, and default or programmed offset settings existing before

Partial Reset remain unchanged. The flags are updated according to the timing

mode and offsets in effect. PRS is useful for resetting a device in mid-operation,

when reprogramming programmable flags would be undesirable.

It is also possible to select the timing mode of the PAE (Programmable AlmostEmpty flag) and PAF (Programmable Almost-Full flag) outputs. The timing

modes can be set to be either asynchronous or synchronous for the PAE and

PAF flags.

If asynchronous PAE/PAF configuration is selected, the PAE is asserted

LOW on the LOW-to-HIGH transition of RCLK. PAE is reset to HIGH on the LOWto-HIGH transition of WCLK. Similarly, the PAF is asserted LOW on the LOWto-HIGH transition of WCLK and PAF is reset to HIGH on the LOW-to-HIGH

transition of RCLK.

If synchronous PAE/PAF configuration is selected , the PAE is asserted and

updated on the rising edge of RCLK only and not WCLK. Similarly, PAF is

(x36, x18, x9) DATA OUT (Q0 - Qn)(x36, x18, x9) DATA IN (D0 - Dn)

MASTER RESET (MRS)

READ CLOCK (RCLK)

READ ENABLE (REN)

OUTPUT ENABLE (OE)

EMPTY FLAG/OUTPUT READY (EF/OR)

PROGRAMMABLE ALMOST-EMPTY (PAE)

WRITE CLOCK (WCLK)

WRITE ENABLE (WEN)

LOAD (LD)

FULL FLAG/INPUT READY (FF/IR)

PROGRAMMABLE ALMOST-FULL (PAF)

IDT

72V3640

72V3650

72V3660

72V3670

72V3680

72V3690

72V36100

72V36110

PARTIAL RESET (PRS)

FIRST WORD FALL THROUGH/SERIAL INPUT

(FWFT/SI)

RETRANSMIT (RT)

4667 drw 03

HALF-FULL FLAG (HF)

SERIAL ENABLE(SEN)

INPUT WIDTH (IW)

OUTPUT WIDTH (OW)

BIG-ENDIAN/LITTLE-ENDIAN (BE)

INTERSPERSED/

NON-INTERSPERSED PARITY (IP)

BUS-

MATCHING

(BM)

4

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

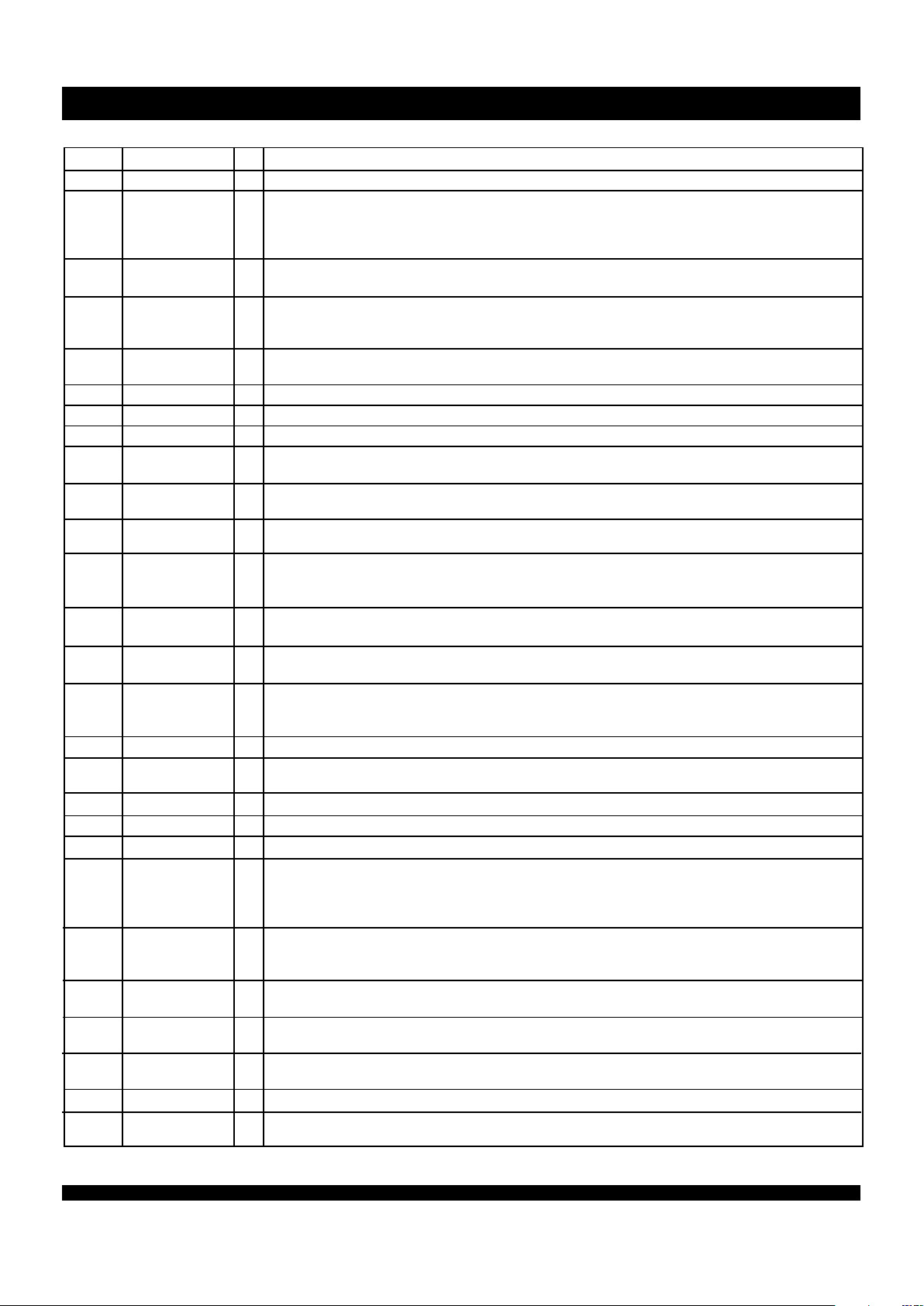

BM IW OW Write Port Width Read Port Width

L L L x36 x36

H L L x36 x18

H L H x36 x9

H H L x18 x36

H H H x9 x36

TABLE 1 BUS-MATCHING CONFIGURATION MODES

asserted and updated on the rising edge of WCLK only and not RCLK. The mode

desired is configured during MasterReset by the state of the Programmable Flag

Mode (PFM) pin.

The Retransmit function allows data to be reread from the FIFO more than

once. A LOW on the RT input during a rising RCLK edge initiates a retransmit

operation by setting the read pointer to the first location of the memory array.

A zero-latency retransmit timing mode can be selected using the Retransmit

timing Mode pin (RM). During Master Reset, a LOW on RM will select zero

latency retransmit. A HIGH on RM during Master Reset will select normal

latency.

If zero latency retransmit operation is selected, the first data word to be

retransmitted will be placed on the output register with respect to the same RCLK

edge that initiated the retransmit based on RT being LOW.

Refer to Figure 11 and 12 for Retransmit Timing with normal latency. Refer

to Figure 13 and 14 for Zero Latency Retransmit Timing.

The device can be configured with different input and output bus widths as

shown in Table 1.

A Big-Endian/Little-Endian data word format is provided. This function is

useful when data is written into the FIFO in long word format (x36/x18) and read

out of the FIFO in small word (x18/x9) format. If Big-Endian mode is selected,

then the most significant byte (word) of the long word written into the FIFO will

be read out of the FIFO first, followed by the least significant byte. If Little-Endian

format is selected, then the least significant byte of the long word written into the

FIFO will be read out first, followed by the most significant byte. The mode desired

is configured during master reset by the state of the Big-Endian (BE) pin. See

Figure 4 for Bus-Matching Byte Arrangement.

The Interspersed/Non-Interspersed Parity (IP) bit function allows the user

to select the parity bit in the word loaded into the parallel port (D

0-Dn) when

programming the flag offsets. If Interspersed Parity mode is selected, then the

FIFO will assume that the parity bit is located in bit positions D8, D17, D26 and

D35 during the parallel programming of the flag offsets. If Non-Interspersed

Parity mode is selected, then D8, D17 and D26 are assumed to be valid bits

and D32, D33, D34 and D35 are ignored. IP mode is selected during Master

Reset by the state of the IP input pin. Interspersed Parity control only has an

effect during parallel programming of the offset registers. It does not effect the data

written to and read from the FIFO.

If, at any time, the FIFO is not actively performing an operation, the chip will

automatically power down. Once in the power down state, the standby supply

current consumption is minimized. Initiating any operation (by activating control

inputs) will immediately take the device out of the power down state.

The IDT72V3640/72V3650/72V3660/72V3670/72V3680/72V3690/

72V36100/72V36110 are fabricated using IDT’s high speed submicron CMOS

technology.

NOTE:

1. Pin status during Master Reset.

5

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

PIN DESCRIPTION

Symbol Name I/O Description

D

0–D35 Data Inputs I Data inputs for a 36-, 18- or 9-bit bus. When in 18- or 9-bit mode, the unused input pins are in a don’t care state.

MRS Master Reset I MRS initializes the read and write pointers to zero and sets the output register to allzeroes. During Master Reset, the

FIFO is configured for either FWFT or IDT Standard mode, Bus-Matching configurations, one of eight programmable

flag default settings, serial or parallel programming of the offset settings, Big-Endian/Little-Endian format, zero

latency timing mode, interspersed parity, and synchronous versus asynchronous programmable flag timing modes.

PRS Partial Reset I PRS initializes the read and write pointers to zero and sets the output register to all zeroes. During Partial Reset, the

existing mode (IDT or FWFT), programming method (serial or parallel), and programmable flag settings are all retained.

RT Retransmit I RT asserted on the rising edge of RCLK initializes the READ pointer to zero, sets the EF flag to LOW (OR to HIGH

in FWFT mode) and does not disturb the write pointer, programming method, existing timing mode or programmable

flag settings. RT is useful to reread data from the first physical location of the FIFO.

FWFT/SI First Word Fall I During Master Reset, selects First Word Fall Through or IDT Standard mode. After Master Reset, this pin

Through/Serial In functions as a serial input for loading offset registers.

OW

(1)

Output Width I This pin, along with IW and BM, selects the bus width of the read port. See Table 1 for bus size configuration.

IW

(1)

Input Width I This pin, along with OW and MB, selects the bus width of the write port. See Table 1 for bus size configuration.

BM

(1)

Bus-Matching I BM works with IW and OW to select the bus sizes for both write and read ports. See Table 1 for bus size configuration.

BE

(1)

Big-Endian/ I During Master Reset, a LOW on BE will select Big-Endian operation. A HIGH on BE during Master Reset

Little-Endian will select Little-Endian format.

RM

(1)

Retransmit Timing I During Master Reset, a LOW on RM will select zero latency Retransmit timing Mode. A HIGH on RM will select

Mode normal latency mode.

PFM

(1)

Programmable I During Master Reset, a LOW on PFM will select Asynchronous Programmable flag timing mode. A HIGH on PFM

Flag Mode will select Synchronous Programmable flag timing mode.

IP

(1)

Interspersed Parity I During Master Reset, a LOW on IP will select Non-Interspersed Parity mode. A HIGH will select Interspersed Parity

mode. Interspersed Parity control only has an effect during parallel programming of the offset registers. It does not effect

the data written to and read from the FIFO.

FSEL0

(1)

Flag Select Bit 0 I During Master Reset, this input along with FSEL1 and the LD pin, will select the default offset values for the programmable

flags PAE and PAF. There are up to eight possible settings available.

FSEL1

(1)

Flag Select Bit 1 I During Master Reset, this input along with FSEL0 and the LD pin will select the default offset values for the programmable

flags PAE and PAF. There are up to eight possible settings available.

WCLK Write Clock I When enabled by WEN, the rising edge of WCLK writes data into the FIFO and offsets into the programmable registers

for parallel programming, and when enabled by SEN, the rising edge of WCLK writes one bit of data into the

programmable register for serial programming.

WEN Write Enable I WEN enables WCLK for writing data into the FIFO memory and offset registers.

RCLK Read Clock I When enabled by REN, the rising edge of RCLK reads data from the FIFO memory and offsets from the programmable

registers.

REN Read Enable I REN enables RCLK for reading data from the FIFO memory and offset registers.

OE Output Enable I OE controls the output impedance of Q

n.

SEN Serial Enable I SEN enables serial loading of programmable flag offsets.

LD Load I This is a dual purpose pin. During Master Reset, the state of the LD input along with FSEL0 and FSEL1, determines

one of eight default offset values for the PAE and PAF flags, along with the method by which these offset registers can

be programmed, parallel or serial (see Table 2). After Master Reset, this pin enables writing to and reading from the

offset registers.

FF/IR Full Flag/ O In the IDT Standard mode, the FF function is selected. FF indicates whether or Input Ready not the FIFO memory

is full. In the FWFT mode, the IR function is selected. IR indicates whether or not there is space available for writing

to the FIFO memory.

EF/OR Empty Flag/ O In the IDT Standard mode, the EF function is selected. EF indicates whether or not the FIFO memory is empty.

Output Ready In FWFT mode, the OR function is selected. OR indicates whether or not there is valid data available at the outputs.

PAF Programmable O PAF goes HIGH if the number of free locations in the FIFO memory is more than offset m, which is stored in the

Almost-Full Flag Full Offset register. PAF goes LOW if the number of free locations in the FIFO memory is less than or equal to m.

PAE Programmable O PAE goes LOW if the number of words in the FIFO memory is less than offset n, which is stored in the Empty Offset

Almost-Empty Flag register. PAE goes HIGH if the number of words in the FIFO memory is greater than or equal to offset n.

HF Half-Full Flag O HF indicates whether the FIFO memory is more or less than half-full.

Q

0–Q35 Data Outputs O Data outputs for an 36-, 18- or 9-bit bus. When in 18- or 9-bit mode, the unused output pins are in a don’t care

state. Outputs are not 5V tolerant regardless of the state of OE.

NOTE:

1. Inputs should not change state after Master Reset.

6

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

ABSOLUTE MAXIMUM RATINGS

Symbol Rating Com’l & Ind’l Unit

V

TERM

(2)

Terminal Voltage –0.5 to +4.5 V

with respect to GND

T

STG Storage –55 to +125 °C

Temperature

I

OUT DC Output Current –50 to +50 mA

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation of

the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

2. V

CC terminal only.

NOTES:

1. With output deselected, (OE ≥ V

IH).

2. Characterized values, not currently tested.

DC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 3.3V ± 0.15V, TA = 0°C to +70°C;Industrial: VCC = 3.3V ± 0.15V, TA = -40°C to +85°C; JEDEC JESD8-A compliant)

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter

(1)

Conditions Max. Unit

C

IN

(2)

Input VIN = 0V 10 pF

Capacitance

C

OUT

(1,2)

Output VOUT = 0V 10 pF

Capacitance

Symbol Parameter Min. Typ. Max. Unit

V

CC

(1)

Supply Voltage Com’l/Ind’l 3.15 3.3 3.45 V

GND Supply Voltage Com’l/Ind’l 0 0 0 V

V

IH

(2)

Input High Voltage Com’l/Ind’l 2 .0 — 5 .5 V

V

IL

(3)

Input Low Voltage Com’l/Ind’l — — 0.8 V

T

A Operating Temperature 0 — 70 °C

Commercial

T

A Operating Temperature -40 — 85 °C

Industrial

NOTES:

1. V

CC = 3.3V ± 0.15V, JEDEC JESD8-A compliant.

2. Outputs are not 5V tolerant.

3. 1.5V undershoots are allowed for 10ns once per cycle.

IDT72V3640L

IDT72V3650L

IDT72V3660L

IDT72V3670L

IDT72V3680L

IDT72V3690L

IDT72V36100L

IDT72V36110L

Commercial and Industrial

(1)

tCLK = 7.5, 10, 15 ns

Symbol Parameter Min. Max. Unit

I

LI

(2)

Input Leakage Current –1 1 µ A

I

LO

(3)

Output Leakage Current –1 0 10 µA

V

OH Output Logic “1” Voltage, IOH = –2 mA 2.4 — V

V

OL Output Logic “0” Voltage, IOL = 8 mA — 0.4 V

I

CC1

(4,5,6)

Active Power Supply Current — 4 0 mA

I

CC2

(4,7)

Standby Current — 15 mA

NOTES:

1. Industrial temperature range product for the 15ns speed grade is available as a standard device. All other speed grades are available by special order.

2. Measurements with 0.4 ≤ V

IN ≤ VCC.

3. OE

≥ VIH, 0.4 ≤ VOUT ≤ VCC.

4. Tested with outputs open (IOUT = 0).

5. RCLK and WCLK toggle at 20 MHz and data inputs switch at 10 MHz.

6. Typical I

CC1 = 4.2 + 1.4*fS + 0.02*CL*fS (in mA) with VCC = 3.3V, tA = 25°C, fS = WCLK frequency = RCLK frequency (in MHz, using TTL levels), data switching at fS/2,

C

L = capacitive load (in pF).

7. All Inputs = V

CC - 0.2V or GND + 0.2V, except RCLK and WCLK, which toggle at 20 MHz.

RECOMMENDED DC OPERATING

CONDITIONS

7

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

AC ELECTRICAL CHARACTERISTICS

(1)

(Commercial: VCC = 3.3V ± 0.15V, TA = 0°C to +70°C;Industrial: VCC = 3.3V ± 0.15V, TA = -40°C to +85°C; JEDEC JESD8-A compliant)

Commercial Com’l & Ind’l

(2)

IDT72V3640L7.5 IDT72V3640L10 IDT72V3640L15

IDT72V3650L7.5 IDT72V3650L10 IDT72V3650L15

IDT72V3660L7.5 IDT72V3660L10 IDT72V3660L15

IDT72V3670L7.5 IDT72V3670L10 IDT72V3670L15

IDT72V3680L7.5 IDT72V3680L10 IDT72V3680L15

IDT72V3690L7.5 IDT72V3690L10 IDT72V3690L15

IDT72V36100L7.5 IDT72V36100L10 IDT72V36100L15

IDT72V36110L7.5 IDT72V36110L10 IDT72V36110L15

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit

f

S Clock Cycle Frequency — 133.3 — 100 — 66.7 MHz

t

A Data Access Time 2 5 2 6.5 2 1 0 ns

t

CLK Clock Cycle Time 7.5 — 10 — 15 — ns

t

CLKH Clock High Time 3.5 — 4.5 — 6 — ns

t

CLKL Clock Low Time 3.5 — 4.5 — 6 — ns

t

DS Data Setup Time 2.5 — 3.5 — 4 — ns

t

DH Data Hold Time 0.5 — 0.5 — 1 — ns

t

ENS Enable Setup Time 2.5 — 3.5 — 4 — ns

t

ENH Enable Hold Time 0.5 — 0.5 — 1 — ns

t

LDS Load Setup Time 3.5 — 3.5 — 4 — ns

t

LDH Load Hold Time 0.5 — 0.5 — 1 — ns

t

RS Reset Pulse Width

(3)

10 — 10 — 15 — ns

t

RSS Reset Setup Time 15 — 15 — 1 5 — ns

t

RSR Reset Recovery Time 1 0 — 10 — 1 5 — ns

t

RSF Reset to Flag and Output Time — 1 5 — 15 — 15 ns

t

RTS Retransmit Setup Time 3.5 — 3.5 — 4 — ns

t

OLZ Output Enable to Output in Low Z

(4)

0— 0 —0—ns

t

OE Output Enable to Output Valid 2 6 2 6 2 8 ns

t

OHZ Output Enable to Output in High Z

(4)

26 2 628ns

t

WFF Write Clock to FF or IR —5 —6.5—10ns

t

REF Read Clock to EF or OR —5 —6.5—10ns

t

PAFA Clock to Asynchronous Programmable — 12.5 — 16 — 20 ns

Almost-Full Flag

t

PAFS Write Clock to Synchronous Programmable — 5 — 6.5 — 1 0 ns

Almost-Full Flag

t

PAEA Clock to Asynchronous Programmable — 12.5 — 16 — 20 ns

Almost-Empty Flag

t

PAES Read Clock to Synchronous Programmable — 5 — 6.5 — 1 0 ns

Almost-Empty Flag

t

HF Clock to HF — 12.5 — 16 — 20 ns

t

SKEW1 Skew time between RCLK and WCLK for 5 — 7 — 9 — ns

EF/OR and FF/IR

t

SKEW2 Skew time between RCLK and WCLK for 7 — 10 — 14 — ns

PAE and PAF

NOTES:

1. All AC timings apply to both Standard IDT mode and First Word Fall Through mode.

2. Industrial temperature range is available by special order for speed grades faster than 15ns.

3. Pulse widths less than minimum values are not allowed.

4. Values guaranteed by design, not currently tested.

8

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

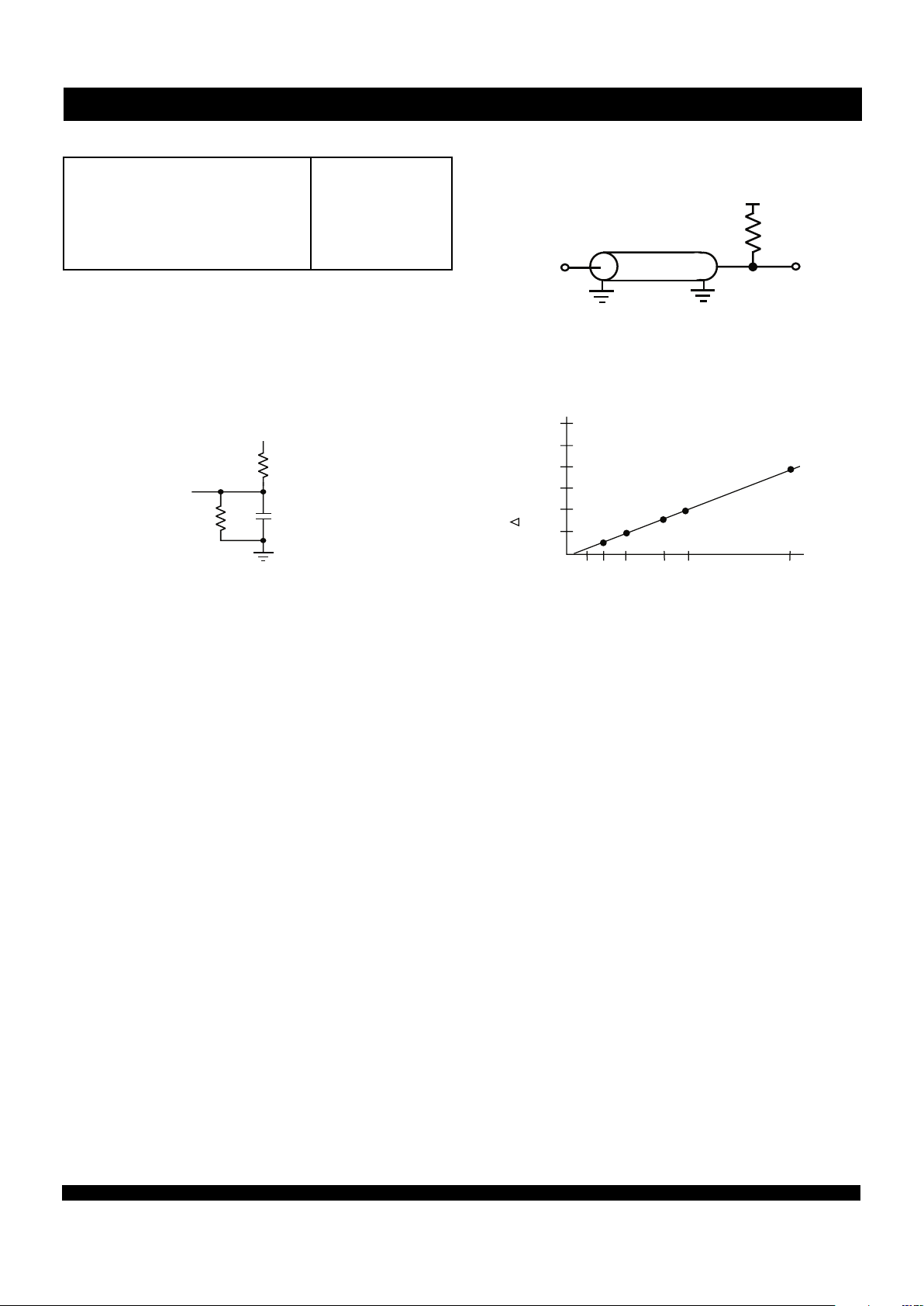

4667 drw04

330Ω

30pF*

510Ω

3.3V

D.U.T.

Input Pulse Levels GND to 3.0V

Input Rise/Fall Times 3ns

(1)

Input Timing Reference Levels 1.5V

Output Reference Levels 1.5V

Output Load for t

CLK = 10ns, 15 ns See Figure 2a

Output Load for t

CLK = 7.5ns See Figure 2b & 2c

AC TEST CONDITIONS

Figure 2b. AC Test Load

Figure 2c. Lumped Capacitive Load, Typical Derating

AC TEST LOADS - 7.5ns Speed Grade

Figure 2a. Output Load

* Includes jig and scope capacitances.

AC TEST LOADS - 10ns, 15ns Speed Grades

NOTE:

1. For 133MHz operation input rise/fall times are 1.5ns.

4667 drw04a

50

Ω

1.5V

I/O

Z0 = 50

Ω

4667 drw04b

6

5

4

3

2

1

20 30 50 80 100 200

Capacitance (pF)

tCD

(Typical, ns)

9

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

writes for the IDT72V36100 and 131,072 writes for the IDT72V36110,

respectively.

If the FIFO is full, the first read operation will cause FF to go HIGH.

Subsequent read operations will cause PAF and HF to go HIGH at the conditions

described in Table 3. If further read operations occur, without write operations,

PAE will go LOW when there are n words in the FIFO, where n is the empty

offset value. Continuing read operations will cause the FIFO to become empty.

When the last word has been read from the FIFO, the EF will go LOW inhibiting

further read operations. REN is ignored when the FIFO is empty.

When configured in IDT Standard mode, the EF and FF outputs are double

register-buffered outputs.

Relevant timing diagrams for IDT Standard mode can be found in Figure

7,8,11 and 13.

FIRST WORD FALL THROUGH MODE (FWFT)

In this mode, the status flags, IR, PAF, HF, PAE, and OR operate in the

manner outlined in Table 4. To write data into to the FIFO, WEN must be LOW.

Data presented to the DATA IN lines will be clocked into the FIFO on subsequent

transitions of WCLK. After the first write is performed, the Output Ready (OR)

flag will go LOW. Subsequent writes will continue to fill up the FIFO. PAE will go

HIGH after n + 2 words have been loaded into the FIFO, where n is the empty

offset value. The default setting for these values are stated in the footnote of Table

2. This parameter is also user programmable. See section on Programmable

Flag Offset Loading.

If one continued to write data into the FIFO, and we assumed no read

operations were taking place, the HF would toggle to LOW once the 514th word

for the IDT72V3640, 1,026th word for the IDT72V3650, 2,050th word for the

IDT72V3660, 4,098th word for the IDT72V3670, 8,194th word for the

IDT72V3680, 16,386th word for the IDT72V3690, 32,770th word for the

IDT72V36100 and 65,538th word for the IDT72V36110, respectively was

written into the FIFO. Continuing to write data into the FIFO will cause the PAF

to go LOW. Again, if no reads are performed, the PAF will goLOW after (1,025-m)

writes for the IDT72V3640, (2,049-m) writes for the IDT72V3650, (4,097-m)

writes for the IDT72V3660 and (8,193-m) writes for the IDT72V3670, 16,385

writes for the IDT72V3680, 32,769 writes for the IDT72V3690, 65,537 writes

for the IDT72V36100 and 131,073 writes for the IDT72V36110, where m is the

full offset value. The default setting for these values are stated in the footnote

of Table 2.

When the FIFO is full, the Input Ready (IR) flag will go HIGH, inhibiting further

write operations. If no reads are performed after a reset, IR will go HIGH after

D writes to the FIFO. D = 1,025 writes for the IDT72V3640, 2,049 writes for

the IDT72V3650, 4,097 writes for the IDT72V3660 and 8,193 writes for the

IDT72V3670,16,385 writes for the IDT72V3680, 32,769 writes for the

IDT72V3690, 65,537 writes for the IDT72V36100 and 131,073 writes for the

IDT72V36110, respectively. Note that the additional word in FWFT mode is due

to the capacity of the memory plus output register.

If the FIFO is full, the first read operation will cause the IR flag to go LOW.

Subsequent read operations will cause the PAF and HF to go HIGH at the

conditions described in Table 4. If further read operations occur, without write

operations, the PAE will go LOW when there are n + 1 words in the FIFO, where

n is the empty offset value. Continuing read operations will cause the FIFO to

become empty. When the last word has been read from the FIFO, OR will go

HIGH inhibiting further read operations. REN is ignored when the FIFO is empty.

When configured in FWFT mode, the OR flag output is triple registerbuffered, and the IR flag output is double register-buffered.

Relevant timing diagrams for FWFT mode can be found in Figure 9, 10, 12,

and 14.

FUNCTIONAL DESCRIPTION

TIMING MODES: IDT STANDARD vs FIRST WORD FALL THROUGH

(FWFT) MODE

The IDT72V3640/72V3650/72V3660/72V3670/72V3680/72V3690/

72V36100/72V36110 support two different timing modes of operation: IDT

Standard mode or First Word Fall Through (FWFT) mode. The selection of

which mode will operate is determined during Master Reset, by the state of the

FWFT/SI input.

If, at the time of Master Reset, FWFT/SI is LOW, then IDT Standard mode

will be selected. This mode uses the Empty Flag (EF) to indicate whether or

not there are any words present in the FIFO. It also uses the Full Flag function

(FF) to indicate whether or not the FIFO has any free space for writing. In IDT

Standard mode, every word read from the FIFO, including the first, must be

requested using the Read Enable (REN) and RCLK.

If, at the time of Master Reset, FWFT/SI is HIGH, then FWFT mode will be

selected. This mode uses Output Ready (OR) to indicate whether or not there

is valid data at the data outputs (Qn). It also uses Input Ready (IR) to indicate

whether or not the FIFO has any free space for writing. In the FWFT mode,

the first word written to an empty FIFO goes directly to Qn after three RCLK rising

edges, REN = LOW is not necessary. Subsequent words must be accessed

using the Read Enable (REN) and RCLK.

Various signals, both input and output signals operate differently depending

on which timing mode is in effect.

IDT STANDARD MODE

In this mode, the status flags, FF, PAF, HF, PAE, and EF operate in the

manner outlined in Table 3. To write data into to the FIFO, Write Enable (WEN)

must be LOW. Data presented to the DATA IN lines will be clocked into the FIFO

on subsequent transitions of the Write Clock (WCLK). After the first write is

performed, the Empty Flag (EF) will go HIGH. Subsequent writes will continue

to fill up the FIFO. The Programmable Almost-Empty flag (PAE) will go HIGH

after n + 1 words have been loaded into the FIFO, where n is the empty offset

value. The default setting for these values are stated in the footnote of Table 2.

This parameter is also user programmable. See section on Programmable Flag

Offset Loading.

If one continued to write data into the FIFO, and we assumed no read

operations were taking place, the Half-Full flag (HF) would toggle to LOW once

the 513rd word for IDT72V3640, 1,025th word for IDT72V3650, 2,049th word

for IDT72V3660, 4,097th word for IDT72V3670, 8,193th word for the

IDT72V3680, 16,385th word for the IDT72V3690, 32,769th word for the

IDT72V36100 and 65,537th word for the IDT72V36110, respectively was

written into the FIFO. Continuing to write data into the FIFO will cause the

Programmable Almost-Full flag (PAF) to go LOW. Again, if no reads are

performed, the PAF will go LOW after (1,024-m) writes for the IDT72V3640,

(2,048-m) writes for the IDT72V3650, (4,096-m) writes for the IDT72V3660,

(8,192-m) writes for the IDT72V3670, (16,384-m) writes for the IDT72V3680,

(32,768-m) writes for the IDT72V3690, (65,536-m) writes for the IDT72V36100

and (131,072-m) writes for the IDT72V36110. The offset “m” is the full offset

value. The default setting for these values are stated in the footnote of Table 2.

This parameter is also user programmable. See section on Programmable Flag

Offset Loading.

When the FIFO is full, the Full Flag (FF) will go LOW, inhibiting further write

operations. If no reads are performed after a reset, FF will go LOW after D writes

to the FIFO. D = 1,024 writes for the IDT72V3640, 2,048 writes for the

IDT72V3650, 4,096 writes for the IDT72V3660, 8,192 writes for the IDT72V3670,

16,384 writes for the IDT72V3680, 32,768 writes for the IDT72V3690, 65,536

10

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

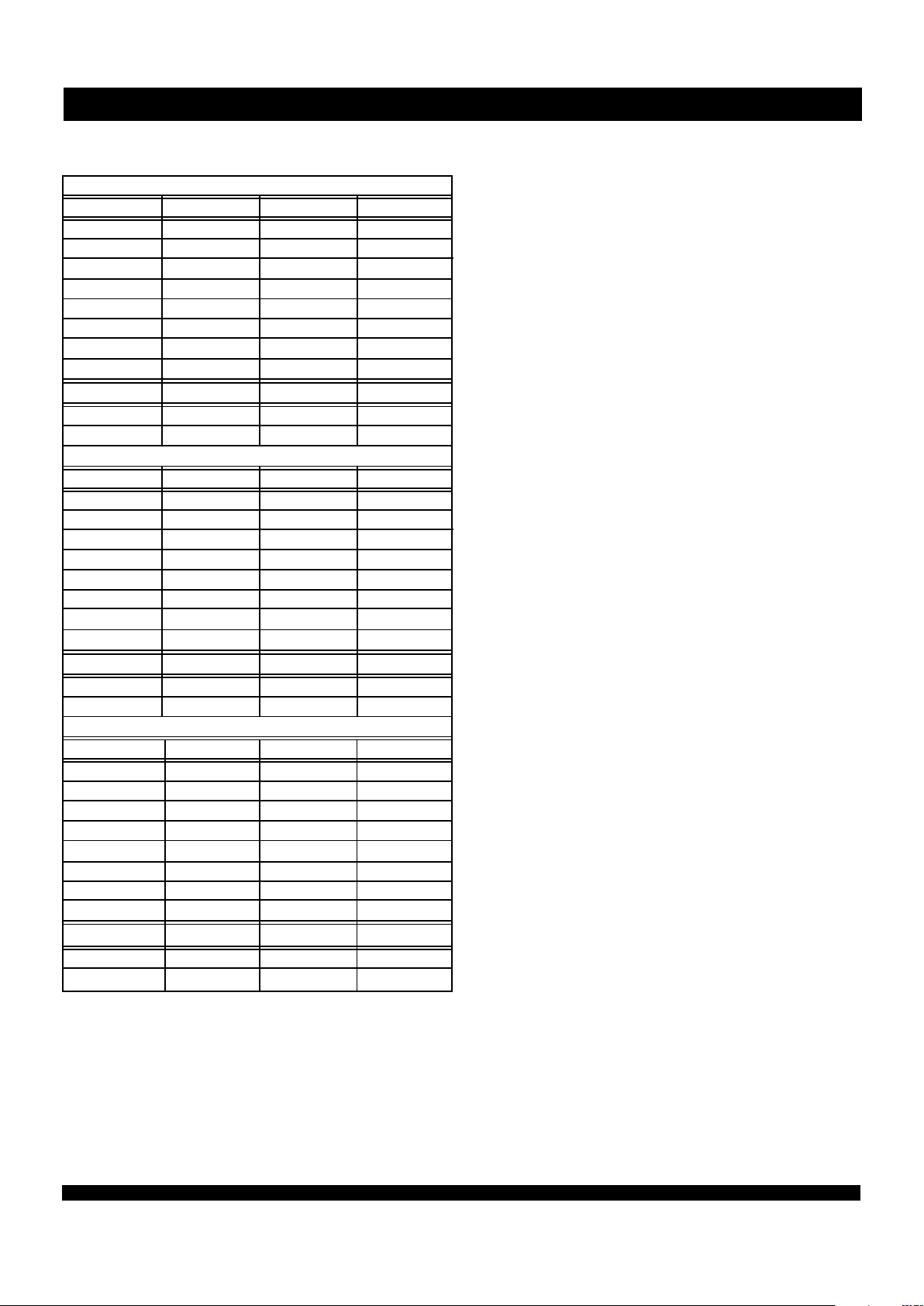

PROGRAMMING FLAG OFFSETS

Full and Empty Flag offset values are user programmable. The IDT72V3640/

72V3650/72V3660/72V3670/72V3680/72V3690/72V36100/72V36110 have

internal registers for these offsets. There are eight default offset values selectable

during Master Reset. These offset values are shown in Table 2. Offset values

can also be programmed into the FIFO in one of two ways; serial or parallel

loading method. The selection of the loading method is done using the LD (Load)

pin. During Master Reset, the state of the LD input determines whether serial

or parallel flag offset programming is enabled. A HIGH on LD during Master

Reset selects serial loading of offset values. A LOW on LD during Master Reset

selects parallel loading of offset values.

In addition to loading offset values into the FIFO, it is also possible to read

the current offset values. Offset values can be read via the parallel output port

Q0-Qn, regardless of the programming mode selected (serial or parallel). It is

not possible to read the offset values in serial fashion.

Figure 3, Programmable Flag Offset Programming Sequence, summaries

the control pins and sequence for both serial and parallel programming modes.

For a more detailed description, see discussion that follows.

The offset registers may be programmed (and reprogrammed) any time after

Master Reset, regardless of whether serial or parallel programming has been

selected. Valid programming ranges are from 0 to D-1.

SYNCHRONOUS vs ASYNCHRONOUS PROGRAMMABLE FLAG TIMING SELECTION

The IDT72V3640/72V3650/72V3660/72V3670/72V3680/72V3690/

72V36100/72V36110 can be configured during the Master Reset cycle with

either synchronous or asynchronous timing for PAF and PAE flags by use of

the PFM pin.

If synchronous PAF/PAE configuration is selected (PFM, HIGH during

MRS), the PAF is asserted and updated on the rising edge of WCLK only and

not RCLK. Similarly, PAE is asserted and updated on the rising edge of RCLK

only and not WCLK. For detail timing diagrams, see Figure 17 for synchronous

PAF timing and Figure 18 for synchronous PAE timing.

If asynchronous PAF/PAE configuration is selected (PFM, LOW during

MRS), the PAF is asserted LOW on the LOW-to-HIGH transition of WCLK and

PAF is reset to HIGH on the LOW-to-HIGH transition of RCLK. Similarly, PAE

is asserted LOW on the LOW-to-HIGH transition of RCLK. PAE is reset to HIGH

on the LOW-to-HIGH transition of WCLK. For detail timing diagrams, see Figure

19 for asynchronous PAF timing and Figure 20 for asynchronous PAE timing.

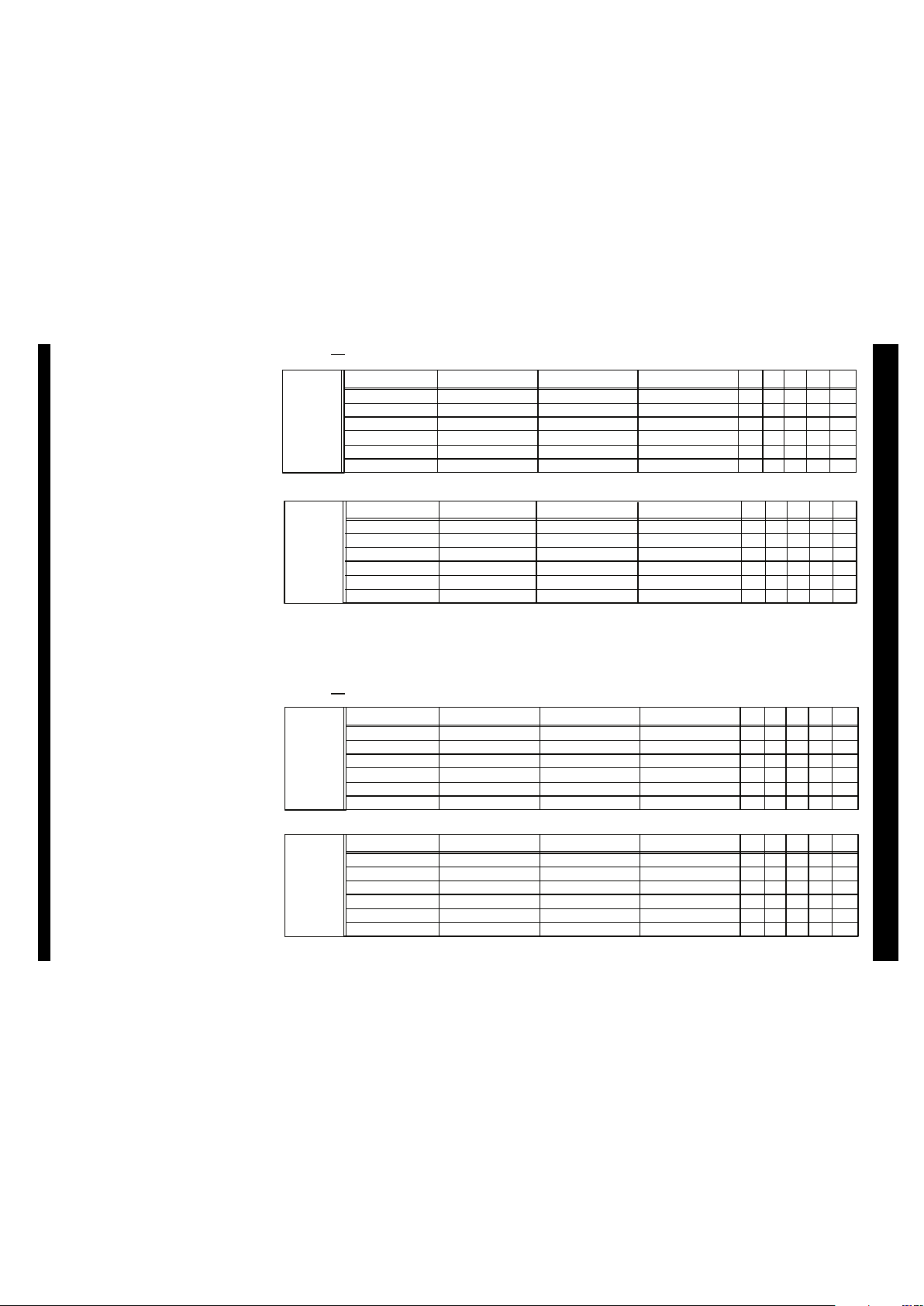

IDT72V3640, 72V3650

LD FSEL1 FSEL0 Offsets n,m

LH L511

L L H 255

L L L 127

LHH63

HL L31

HH L15

HLH7

HH H3

LD FSEL1 FSEL0 Program Mode

H X X Serial

(3)

L X X Parallel

(4)

IDT72V3660, 72V3670, 72V3680, 72V3690

LD FSEL1 FSEL0 Offsets n,m

H L L 1,023

LH L511

L L H 255

L L L 127

LHH63

HH L31

HLH15

HH H7

LD FSEL1 FSEL0 Program Mode

H X X Serial

(3)

L X X Parallel

(4)

IDT72V36100, 72V36110

LD FSEL1 FSEL0 Offsets n,m

L H L 16,383

L L H 8,191

L H H 4,095

H H L 2,047

H L L 1,023

HLH511

HHH255

LLL127

LD FSEL1 FSEL0 Program Mode

H X X Serial

(3)

L X X Parallel

(4)

TABLE 2 DEFAULT PROGRAMMABLE

FLAG OFFSETS

NOTES:

1. n = empty offset for PAE.

2. m = full offset for PAF.

3. As well as selecting serial programming mode, one of the default values will also

be loaded depending on the state of FSEL0 & FSEL1.

4. As well as selecting parallel programming mode, one of the default values will

also be loaded depending on the state of FSEL0 & FSEL1.

11

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

IDT72V3640/50/60/70/80/90/110 3.3V HIGH DENSITY SUPERSYNC II

TM

36-BIT FIFO

1,024 x 36, 2,048 x 36, 4,096 x 36, 8,192 x 36, 16,384 x 36, 32,768 x 36, 65,536 x 36, 131,072 x 36

IDT72V3640 IDT72V3650

0

1 to n

(1)

(n+1) to 1,024

1,025 to (2048-(m+1))

(2048-m)

to 2,047

2,048

0

1 to n

(1)

(n+1) to 512

513 to (1,024-(m+1))

(1024-m) to 1,023

1,024

IDT72V3660

IDT72V3670

0

1 to n

(1)

(n+1) to 4,096

4,097 to (8,192-(m+1))

(8,192-m)

to 8,191

8,192

0

1 to n

(1)

(n+1) to 2,048

2,049 to (4,096-(m+1))

(4,096-m) to 4,095

4,096

TABLE 3 STATUS FLAGS FOR IDT STANDARD MODE

IDT72V3640 IDT72V3650

000

1 to n+1

1 to n+1

1 to n+1

(n+2) to 1,025 (n+2) to 2,049 (n+2) to 4,097

1,026 to (2,049-(m+1)) 2,050 to (4,097-(m+1))

4,098 to (8,193-(m+1))

(2,049-m) to 2,048

(4,097-m)

to 4,096

(8,193-m)

to 8,192

2,049 4,097 8,193

IDT72V3660

IDT72V3670

0

1 to n+1

(n+2) to 513

514 to (1,025-(m+1))

(1,025-m)

to 1,024

1,025

IR PAFHFPAE OR

LH

HL H

LH

HL

L

LHHHL

LHLHL

L

L

LHL

HL

LHL

Number of

Words in

FIFO

TABLE 4 STATUS FLAGS FOR FWFT MODE

00

1 to n

(

1)

1 to n

(1)

(n+1) to 8,192 (n+1) to 16,384

8,193 to (16,384-(m+1))

16,385 to (32,768-(m+1))

(16,384-m)

to 16,383

(32,768-m) to 32,767

16,384 32,768

00

1 to n

(1)

1 to n

(1)

(n+1) to 32,768 (n+1) to 65,536

32,769 to (65,536-(m+1)) 65,537 to (131,072-(m+1))

(65,536-m)

to 65,535

(131,072-m)

to 131,071

65,536 131,072

IDT72V3680 IDT72V3690

IDT72V36100

IDT72V36110

FF PAFHFPAE EF

HH

HL L

HH

HL

H

HHHHH

HHLHH

H

L

LHH

LL

LHH

Number of

Words in

FIFO

4667 drw 05

00

1 to n+1

1 to n+1

(n+2) to 8,193 (n+2) to 16,385

8,194 to (16,385-(m+1))

16,386 to (32,769-(m+1))

(16,385-m)

to 16,384

(32,769-m)

to 32,768

16,385 32,769

00

1 to n+1 1 to n+1

(n+2) to 32,769 (n+2) to 65,537

32,770 to (65,537-(m+1)) 65,538 to (131,073-(m+1))

(65,537-m) to 65,536 (131,073-m) to 131,072

65,537 131,073

IDT72V3680

IDT72V3690

IDT72V36100

IDT72V36110

IR PAFHFPAE OR

LH

HL H

LH

HL

L

LHHHL

LHLHL

L

L

LHL

HL

LHL

Number of

Words in

FIFO

FF PAFHFPAE EF

HH

HL L

HH

HL

H

HHHHH

HHLH H

H

L

LHH

LL

LHH

Number of

Words in

FIFO

NOTE:

1. See table 2 for values for n, m.

NOTE:

1. See table 2 for values for n, m.

Loading...

Loading...