IDT IDT72805LB, IDT72815LB, IDT72825LB, IDT72835LB, IDT72845LB User Manual

CMOS DUAL SyncFIFO™

DUAL 256 x 18, DUAL 512 x 18,

DUAL 1,024 x 18, DUAL 2,048 x 18

and DUAL 4,096 x 18

FEATURES:

••

The IDT72805LB is equivalent to two IDT72205LB 256 x 18 FIFOs

•

••

••

• The IDT72815LB is equivalent to two IDT72215LB 512 x 18 FIFOs

••

••

• The IDT72825LB is equivalent to two IDT72225LB 1,024 x 18 FIFOs

••

••

• The IDT72835LB is equivalent to two IDT72235LB 2,048 x 18 FIFOs

••

••

• The IDT72845LB is equivalent to two IDT72245LB 4,096 x 18 FIFOs

••

••

Offers optimal combination of large capacity (8K), high speed,

•

••

design flexibility, and small footprint

••

• Ideal for the following applications:

••

- Network switching

- Two level prioritization of parallel data

- Bidirectional data transfer

- Bus-matching between 18-bit and 36-bit data paths

- Width expansion to 36-bit per package

- Depth expansion to 8,192 words per package

••

• 10ns read/write cycle time, 6.5ns access time

••

••

• IDT Standard or First Word Fall Through timing

••

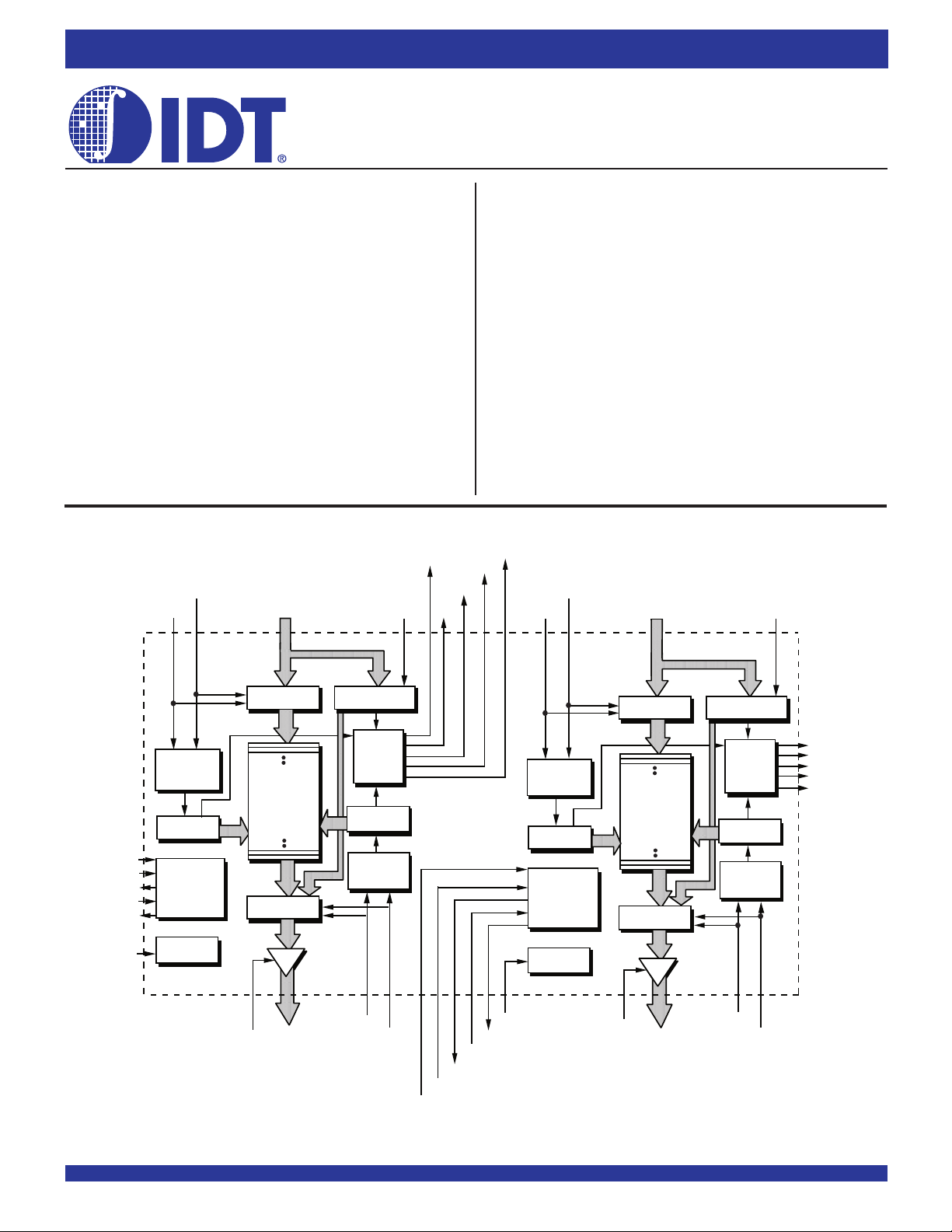

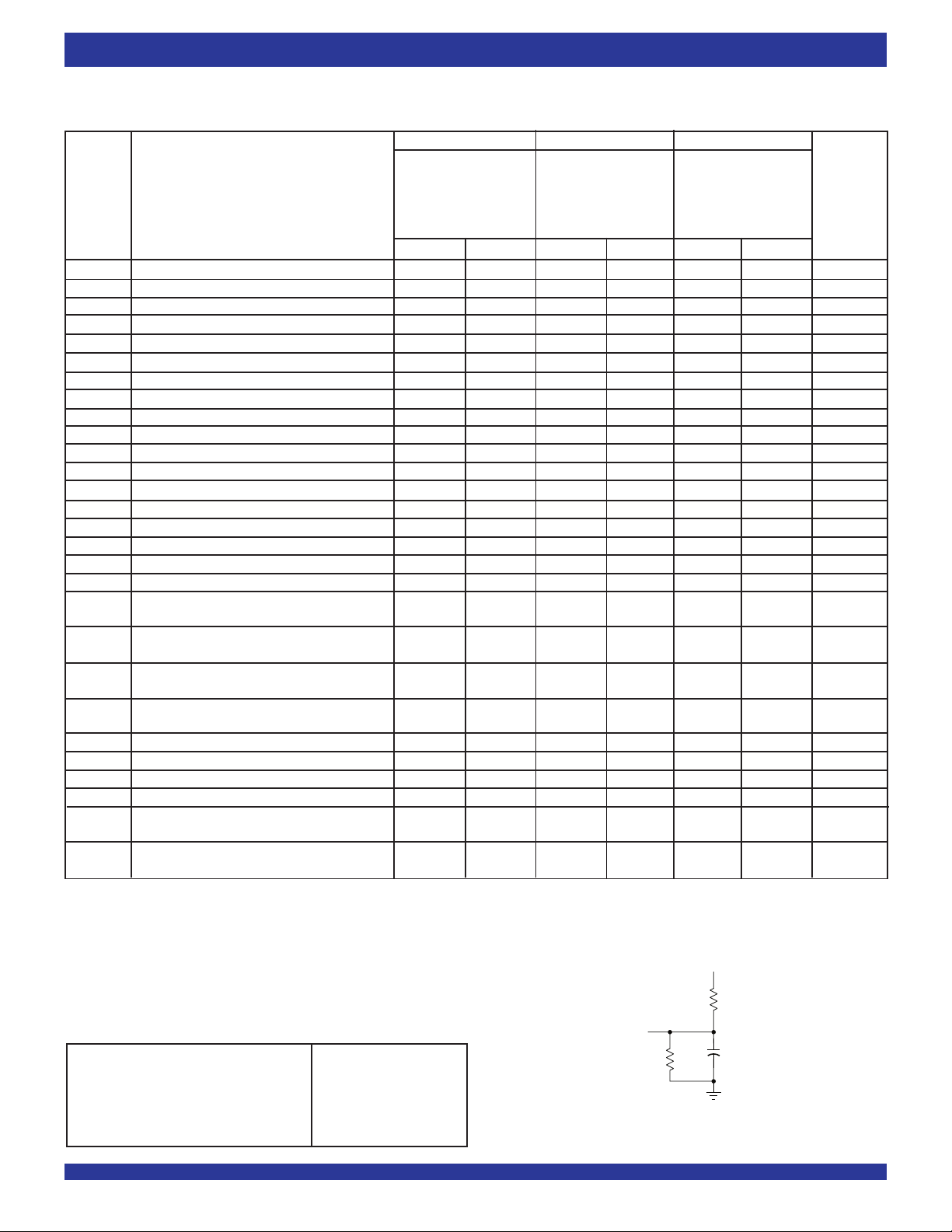

FUNCTIONAL BLOCK DIAGRAM

IDT72805LB

IDT72815LB

IDT72825LB

IDT72835LB

IDT72845LB

••

• Single or double register-buffered Empty and Full Flags

••

••

• Easily expandable in depth and width

••

••

• Asynchronous or coincident Read and Write clocks

••

••

• Asynchronous or synchronous programmable Almost-Empty

••

and Almost-Full flags with default settings

••

Half-Full flag capability

•

••

••

• Output Enable puts output data bus in high-impedance state

••

••

• High-performance submicron CMOS technology

••

••

•

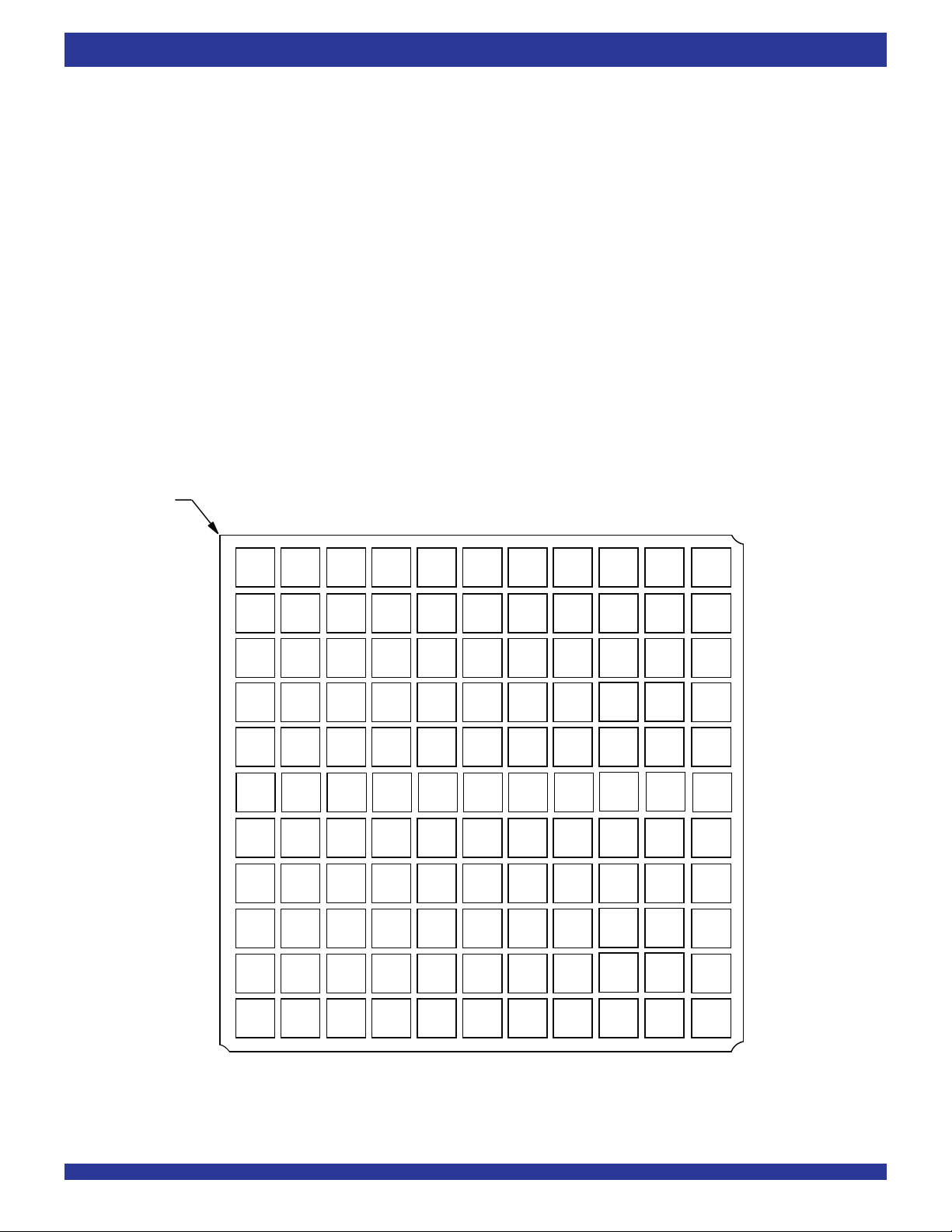

Available in the 128-pin Thin Quad Flatpack (TQFP). Also

••

available for the IDT72805LB/72815LB/72825LB, in the 121-lead,

16 x 16 mm plastic Ball Grid Array (PBGA)

••

Industrial temperature range (–40

•

••

°°

°C to +85

°°

°°

°C) is available

°°

DESCRIPTION:

The IDT72805LB/72815LB/72825LB/72835LB/72845LB are dual 18-bit-wide

synchronous (clocked) First-in, First-out (FIFO) memories. One dual IDT72805LB/

72815LB/72825LB/72835LB/72845LB device is functionally equivalent to two

FLA

WXIA

(HFA)/WXOA

RXIA

RXOA

RSA

WCLKA

WENA

WRITE

CONTROL

LOGIC

WRITE

POINTER

EXPANSION

LOGIC

RESET

LOGIC

0

-DA

17

DA

INPUT

REGISTER

RAM

ARRAY

256 x 18

512 x 18

1,024 x 18

2,048 x 18

4,096 x 18

OUTPUT

REGISTER

OFFSET

REGISTER

FLAG

LOGIC

READ

POINTER

READ

CONTROL

LOGIC

FFA/IRA

LDA

PAFA

HFA/(WXOA)

PAEA

EFA/

ORA

WCLKB

WENB

WRITE

CONTROL

LOGIC

WRITE

POINTER

EXPANSION

LOGIC

RESET

LOGIC

DB0-DB17

INPUT

REGISTER

RAM

ARRAY

256 x 18

512 x 18

1,024 x 18

2,048 x 18

4,096 x 18

OUTPUT

REGISTER

LDB

OFFSET

REGISTER

FLAG

LOGIC

READ

POINTER

READ

CONTROL

LOGIC

FFB/IRB

PAFB

EFB/ORB

PAEB

HFB/(WXOB)

0

-QA

QA

OEA

IDT and the IDT logo are registered trademarks. The SyncFIFO is a trademark of Integrated Device Technology, Inc.

RCLKA

17

RENA

(HFB)/WXOB

WXIB

FLB

RSB

RXOB

RXIB

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

OEB

QB

0

-QB

RCLKB

17

RENB

FEBRUARY 2003

3139 drw 01

1

2003 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice. DSC-3139/4

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFO

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

TM

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

DESCRIPTION (Continued)

IDT72205LB/72215LB/72225LB/72235LB/72245LB FIFOs in a single package

with all associated control, data, and flag lines assigned to independent

pins. These devices are very high-speed, low-power First-In, First-Out

(FIFO) memories with clocked read and write controls. These FIFOs are

applicable for a wide variety of data buffering needs, such as optical disk

controllers, Local Area Networks (LANs), and interprocessor communication.

Each of the two FIFOs contained in these devices has an 18-bit input and

output port. Each input port is controlled by a free-running clock (WCLK), and

an input enable pin (WEN). Data is read into the synchronous FIFO on every

clock when WEN is asserted. The output port of each FIFO bank is controlled

by another clock pin (RCLK) and another enable pin (REN). The Read Clock

can be tied to the Write Clock for single clock operation or the two clocks can

run asynchronous of one another for dual-clock operation. An Output Enable

pin (OE) is provided on the read port of each FIFO for three-state control of the

output.

The synchronous FIFOs have two fixed flags, Empty Flag/Output Ready

(EF/OR) and Full Flag/Input Ready (FF/IR), and two programmable flags,

Almost-Empty (PAE) and Almost-Full (PAF). The offset loading of the program-

PIN CONFIGURATIONS

PIN 1

mable flags is controlled by a simple state machine, and is initiated by asserting

the Load pin (LD). A Half-Full flag (HF) is available for each FIFO that is

implemented as a single device configuration.

There are two possible timing modes of operation with these devices: IDT

Standard mode and First Word Fall Through (FWFT) mode.

In IDT Standard Mode, the first word written to an empty FIFO will not

appear on the data output lines unless a specific read operation is performed.

A read operation, which consists of activating REN and enabling a rising RCLK

edge, will shift the word from internal memory to the data output lines.

In FWFT mode, the first word written to an empty FIFO is clocked directly

to the data output lines after three transitions of the RCLK signal. A REN does

not have to be asserted for accessing the first word.

These devices are depth expandable using a daisy-chain technique or First

Word Fall Through (FWFT) mode. The XI and XO pins are used to expand the

FIFOs. In depth expansion configuration, FL is grounded on the first device and

set to HIGH for all other devices in the Daisy Chain.

The IDT72805LB/72815LB/72825LB/72835LB/72845LB are fabricated

using IDT’s high-speed submicron CMOS technology.

A

WCLKA DA3 DA1 DA0 DB13 DB16 RCLKB

PAFA

B

C

D

G

FFA RXIA WXIA

RXOA

E

QA1 QA4 QA3

F

QA5 QA6 GND VCC GND GND GND VCC GND QB6 QB5

QA7 QA9 VCC VCC DA6 DA9

H

QA8 QA10 QA12 VCC DA7 DA10 DA8

J

QA11 QA13 GND DA17 GND DA11 DA14 DB5

K

QA14 QA15

WENA

DA4

QA2QA0

EFA OEA RENA

DA2 DB12 DB15

DA5 DB14 DB11 GND DB17 GND QB13 QB11

FLA

WXOA/

HFA

PAEA

RENB OEB EFB

DB9 DB6 VCC VCC QB9 QB7

PAEB

DA15 DA12 DB2

LDB RSB

WXOB/

HFB

FLB

QB3 QB4 QB1

QB2 QB0

WXIB RXIB FFB

WENB

QB17 QB16

QB15 QB14

QB8QB10QB12VCCDB7DB10DB8

RXOB

PAFB

DB4

L

QA16 QA17

1234567891011

RSA LDA

RCKLA DA16 DA13 DB0 DB1 DB3 WCLKB

PBGA (BG121-1, order code: BG)

NOTE:

1. The PBGA is only available for the IDT72805LB/72815LB/72825LB in the 15 or 25 ns speed grade.

TOP VIEW

2

3139 drw 02

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFO

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

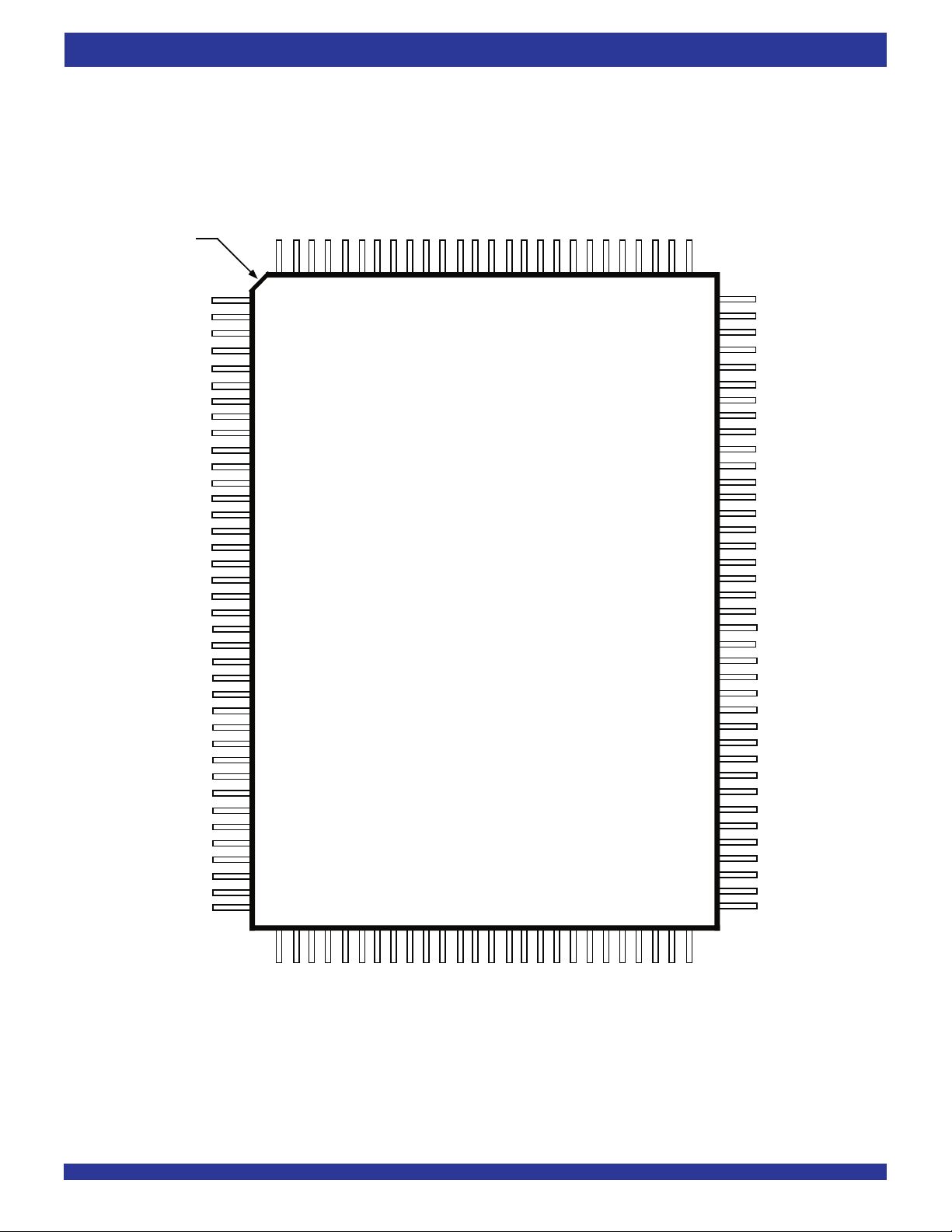

PIN CONFIGURATIONS (Continued)

PAEA

DA0

INDEX

WXIA

WENA

WCLKA

FLA

DA1

DA2

DA3

DA4

DA5

DA6

DA7

DA8

TM

DA9

DA11

DA10

DA13

DA12

DA15

DA14

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

GND

DA17

RCLKA

RENA

DA16

V

CC

PAFA

RXIA

FFA

WXOA/HFA

RXOA

QA0

QA1

GND

QA2

QA3

V

CC

QA4

GND

QA5

QA6

QA7

QA8

GND

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

PAEB

FLB

WCLKB

WENB

WXIB

V

CC

PAFB

RXIB

FFB

WXOB/HFB

RXOB

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

128

39

127

40

126

41

125

42

124

43

123

44

122

45

121

46

120

47

119

48

118

49

117

50

116

51

115

52

114

112

113

535455

111

56

110

57

109

58

108

59

107

60

106

61

105

62

104

63

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

LDA

OEA

RSA

V

CC

GND

EFA

QA17

QA16

GND

QA15

V

CC

QA14

QA13

GND

QA12

QA11

V

CC

QA10

QA9

DB8

DB9

DB10

DB11

DB12

DB13

DB14

DB15

DB16

DB17

GND

RCLKB

RENB

LDB

OEB

RSB

V

CC

GND

EFB

QB0

QB1

GND

QB13

QB14

CC

V

GND

QB15

QB16

QB17

3139 drw 02a

CC

QB4

V

QB3

QB2

GND

QB5

QB6

QB7

QB8

GND

QB9

CC

V

QB10

QB11

QB12

GND

TQFP (PK128-1, order code: PF)

TOP VIEW

3

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFO

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

TM

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

PIN DESCRIPTION

Symbol Name I/O Description

DA

0–DA17 Data Inputs I Data inputs for an 18-bit bus.

0-DB17

DB

RSA Reset I When RS is set LOW, internal read and write pointers are set to the first location of the RAM array, FF and

RSB PAF go HIGH, and PAE and EF go LOW. A reset is required before an initial WRITE after power-up.

WCLKA Write Clock I When WEN is LOW, data is written into the FIFO on a LOW-to-HIGH transition of WCLK, if the FIFO is not full.

WCLKB

WENA Write Enable I When WEN is LOW, data is written into the FIFO on every LOW-to-HIGH transition of WCLK. When WEN is

WENB HIGH, the FIFO holds the previous data. Data will not be written into the FIFO if the FF is LOW.

RCLKA Read Clock I When REN is LOW, data is read from the FIFO on a LOW-to-HIGH transition of RCLK, if the FIFO is not empty.

RCLKB

RENA Read Enable I When REN is LOW, data is read from the FIFO on every LOW-to-HIGH transition of RCLK. When REN is HIGH,

RENB the output register holds the previous data. Data will not be read from the FIFO if the EF is LOW.

OEA Output Enable I When OE is LOW, the data output bus is active. If OE is HIGH, the output data bus will be in a high-impedance

OEB state.

LDA Load I When LD is LOW, data on the inputs D0–D11 is written to the offset and depth registers on the LOW-to-HIGH

LDB transition of the WCLK, when WEN is LOW. When LD is LOW, data on the outputs Q0–Q11 is read from the

offset and depth registers on the LOW-to-HIGH transition of the RCLK, when REN is LOW.

FLA First Load I In the single device or width expansion configuration, FL together with WXI and RXI determine if the mode is

FLB IDT Standard mode or First Word Fall Through (FWFT) mode, as well as whether the PAE/PAF flags are

synchronous or asynchronous. (See Table I.) In the Daisy Chain Depth Expansion configuration, FL is grounded

on the first device (first load device) and set to HIGH for all other devices in the Daisy Chain.

WXIA Write Expansion I In the single device or width expansion configuration, WXI together with FL and RXI determine if the mode is

WXIB Input IDT Standard mode or FWFT mode, as well as whether the PAE/PAF flags are synchronous or asynchronous.

(See Table 1.) In the Daisy Chain Depth Expansion configuration, WXI is connected to WXO (Write Expansion

Out) of the previous device.

RXIA Read Expansion I In the single device or width expansion configuration, RXI together with FL and WXI, determine if the mode is

RXIB Input IDT Standard mode or FWFT mode, as well as whether the PAE/PAF flags are synchronous or asynchronous.

(See Table 1.) In the Daisy Chain Depth Expansion configuration, RXI is connected to RXO (Read Expansion

Out) of the previous device.

FFA/IRA Full Flag/ O In the IDT Standard mode, the FF function is selected FF indicates whether or not the FIFO memory is full. In

FFB/IRB Input Ready the FWFT mode, the IR function is selected. IR indicates whether or not there is space available for writing to

the FIFO memory.

EFA/ORA Empty Flag/ O In the IDT Standard mode, the EF function is selected. EF indicates whether or not the FIFO memory is empty.

EFB/ORB Output Ready In FWFT mode, the OR function is selected. OR indicates whether or not there is valid data available at the

outputs.

PAEA Programmable O When PAE is LOW, the FIFO is almost-empty based on the offset programmed into the FIFO. The default

PAEB Almost-Empty flag offset at reset is 31 from empty for IDT72805LB, 63 from empty for IDT72815LB, and 127 from empty for

IDT72825LB/72835LB/72845LB.

PAFA Programmable O When PAF is LOW, the FIFO is almost-full based on the offset programmed into the FIFO. The default offset

PAFB Almost-Full flag at reset is 31 from full for IDT72805LB, 63 from full for IDT72815LB, and 127 from full for IDT72825LB/72835LB/

72845LB.

WXOA/HFA Write Expansion O In the single device or width expansion configuration, the device is more than half full when HF is LOW. In the

WXOB/HFB Out/Half-Full Flag depth expansion configuration, a pulse is sent from WXO to WXI of the next device when the last location in

the FIFO is written.

RXOA Read Expansion O In the depth expansion configuration, a pulse is sent from RXO to RXI of the next device when the last location

RXOB Out in the FIFO is read.

0–QA17 Data Outputs O Data outputs for an 18-bit bus.

QA

0-QB17

QB

VCC Power +5V power supply pins.

GND Ground Ground pins.

4

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFO

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

TM

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

ABSOLUTE MAXIMUM RATINGS

Symbol Rating Commercial Unit

TERM Terminal Voltage –0.5 to +7.0 V

V

with respect to GND

STG Storage –55 to +125 °C

T

Temperature

OUT DC Output Current –50 to +50 mA

I

NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS maycause

permanent damage to the device. This is a stress rating only and functional operation of

the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

RECOMMENDED DC OPERATING

CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

V

CC Supply Voltage (Com’l/Ind’l) 4.5 5.0 5.5 V

GND Supply Voltage (Com’l/Ind’l) 0 0 0 V

V

IH Input High Voltage (Com’l/Ind’l) 2.0 V

(1)

V

IL

Input Low Voltage (Com’l/Ind’l) 0.8 V

T

A Operating Temperature 0 70 °C

Commercial

A Operating Temperature 0 85 °C

T

Industrial

NOTE:

1. 1.5V undershoots are allowed for 10ns once per cycle.

DC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V ± 10%, TA = 0°C to +70°C; Industrial: VCC = 5V ± 10%, TA = -40°C to +85°C)

IDT72805LB

IDT72815LB

IDT72825LB

IDT72835LB

IDT72845LB

Com’l & Ind’l

tCLK = 10, 15, 25 ns

Symbol Parameter Min. Typ. Max. Unit

(2)

I

LI

(3)

I

LO

V

OH Output Logic “1” Voltage, IOH = –2 mA 2.4 — — V

V

OL Output Logic “0” Voltage, IOL = 8 mA — — 0.4 V

(4,5,6)

I

CC1

(4,7)

I

CC2

NOTES:

1. Industrial Temperature Range Product for the 15ns speed grade is available as a standard device.

2. Measurements with 0.4 ≤ V

3. OE ≥ V

4. Tested with outputs open (I

4. RCLK and WCLK toggle at 20 MHZ and data inputs switch at 10 MHz.

5. For the IDT72805LB/72815LB/72825LB the typical I

for the IDT72835LB/72845LB the typical I

These equations are valid under the following conditions:

CC = 5V, TA = 25°C, fS = WCLK frequency = RCLK frequency (in MHz, using TTL levels), data switching at fS/2, CL = capacitive load (in pF).

V

7. All Inputs = V

Input Leakage Current (any input) –1 — 1 µA

Output Leakage Current –10 — 10 µA

Active Power Supply Current — — 100 mA

Standby Current — — 10 mA

IN ≤ VCC.

IH, 0.4 ≤ VOUT ≤ VCC.

OUT = 0).

CC1 = 2[1.81 + 1.12*fS + 0.02*CL*fS] (in mA);

CC1 = 2[2.85 + 1.30*fS + 0.02*CL*fS] (in mA).

CC - 0.2V or GND + 0.2V, except RCLK and WCLK, which toggle at 20 MHz.

(1)

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter

(2)

IN

C

Input VIN = 0V 10 pF

Capacitance

(1,2)

OUT

C

Output VOUT = 0V 10 pF

Capacitance

NOTES:

1. With output deselected, (OE ≥ V

2. Characterized values, not currently tested.

(1)

Conditions Max. Unit

IH).

5

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFO

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

TM

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

AC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V ± 10%, TA = 0°C to +70°C; Industrial: VCC = 5V ± 10%, TA = -40°C + 85°C)

Commercial Com’l & Ind’l

IDT72805LB10 IDT72805LB15 IDT72805LB25

IDT72815LB10 IDT72815LB15 IDT72815LB25

IDT72825LB10 IDT72825LB15 IDT72825LB25

IDT72835LB10 IDT72835LB15 IDT72835LB25

IDT72845LB10 IDT72845LB15 IDT72845LB25

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit

f

S Clock Cycle Frequency — 100 — 66.7 — 40 MHz

t

A Data Access Time 2 6.5 2 10 3 15 ns

t

CLK Clock Cycle Time 10 — 15 — 25 — ns

t

CLKH Clock HIGH Time 4.5 — 6 — 10 — ns

t

CLKL Clock LOW Time 4.5 — 6 — 10 — ns

t

DS Data Setup Time 3 — 4 — 6 — ns

t

DH Data Hold Time 0 — 1 — 1 — ns

t

ENS Enable Setup Time 3 — 4 — 6 — ns

t

ENH Enable Hold Time 0 — 1 — 1 — ns

t

RS Reset Pulse Width

t

RSS Reset Setup Time 8 — 10 — 15 — ns

t

RSR Reset Recovery Time 8 — 10 — 15 — ns

t

RSF Reset to Flag and Output Time — 15 — 15 — 25 ns

t

OLZ Output Enable to Output in Low-Z

t

OE Output Enable to Output Valid — 6 — 8 — 12 ns

t

OHZ Output Enable to Output in High-Z

t

WFF Write Clock to Full Flag — 6.5 — 10 — 15 ns

t

REF Read Clock to Empty Flag — 6.5 — 10 — 15 ns

t

PAFA Clock to Asynchronous Programmable — 17 — 20 — 35 ns

(2)

(3)

(3)

10 — 15 — 25 — ns

0—0—0—ns

1618112ns

Almost-Full Flag

t

PAFS Write Clock to Synchronous — 8 — 10 — 12 ns

Programmable Almost-Full Flag

t

PAEA Clock to Asynchronous Programmable — 17 — 20 — 35 ns

Almost-Empty Flag

t

PAES Read Clock to Synchronous — 8 — 10 — 12 ns

Programmable Almost-Empty Flag

t

HF Clock to Half-Full flag — 17 — 20 — 35 ns

t

XO Clock to Expansion Out — 6.5 — 10 — 15 ns

t

XI Expansion In Pulse Width 3 — 6.5 — 10 — ns

t

XIS Expansion In Setup Time 3 — 5 — 10 — ns

t

SKEW1 Skew time between Read Clock & 5 — 6 — 10 — ns

Write Clock for FF/IR and EF/OR

(4)

t

SKEW2

Skew time between Read Clock & 12 — 15 — 17 — ns

Write Clock for PAE and PAF

NOTES:

1. Industrial Temperature Range Product for the 15ns speed grade is available as a standard device.

2. Pulse widths less than minimum values are not allowed.

3. Values guaranteed by design, not currently tested.

4. tSKEW2 applies to synchronous PAE and synchronous PAF only.

(1)

Commercial

5V

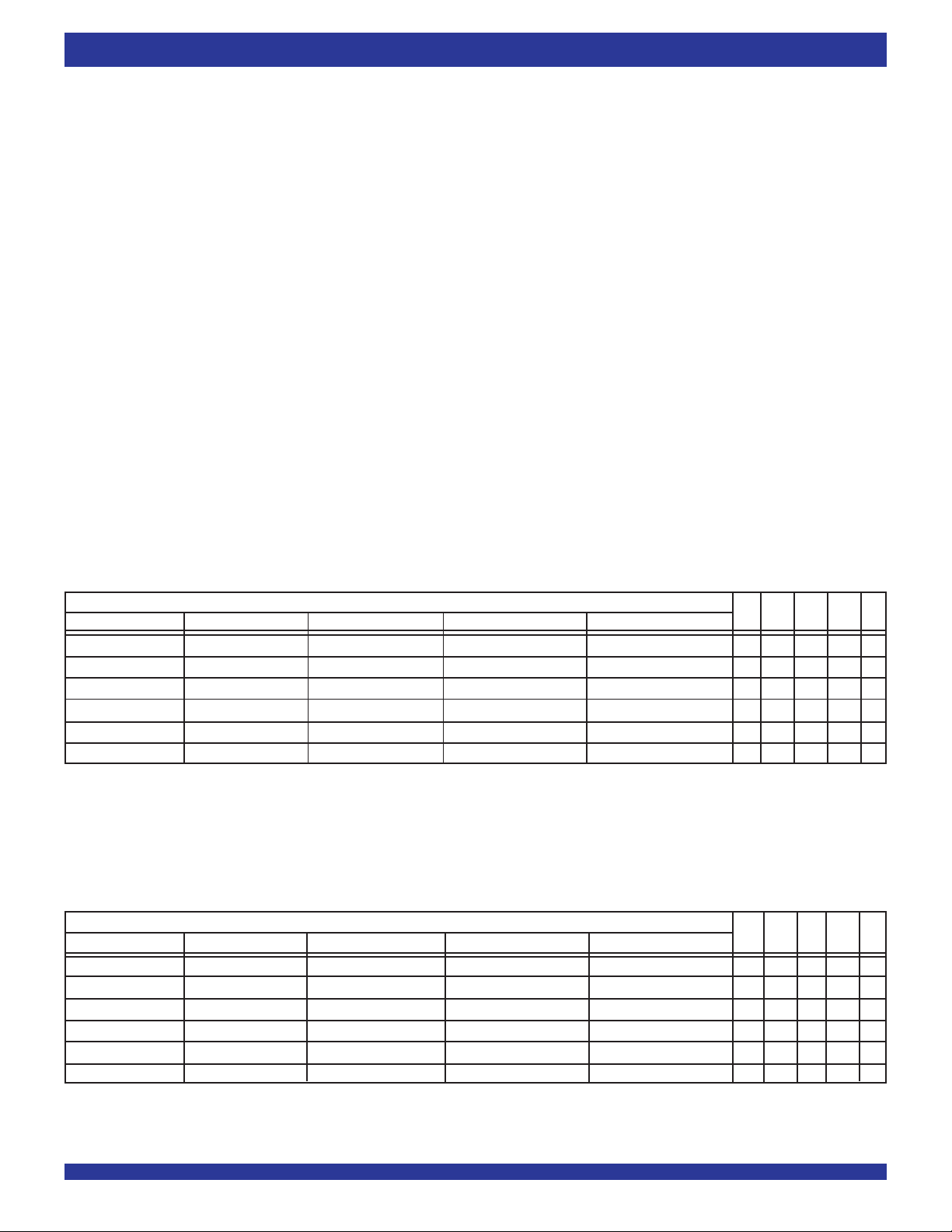

AC TEST CONDITIONS

Input Pulse Levels GND to 3.0V

Input Rise/Fall Times 3ns

Input Timing Reference Levels 1.5V

Output Reference Levels 1.5V

Output Load See Figure 1

1.1K

D.U.T.

680Ω

30pF*

3139 drw 03

Figure 1. Output Load

* Includes jig and scope capacitances.

6

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFO

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

TM

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

FUNCTIONAL DESCRIPTION

TIMING MODES: IDT STANDARD vs FIRST WORD FALL THROUGH

(FWFT) MODE

The IDT72805LB/72815LB/72825LB/72835LB/72845LB support two

different timing modes of operation. The selection of which mode will

operate is determined during configuration at Reset (RS). During a RS

operation, the First Load (FL), Read Expansion Input ( RXI) and Write

Expansion Input (WXI) pins are used to select the timing mode per the truth

table shown in Table 3. In IDT Standard Mode, the first word written to an

empty FIFO will not appear on the data output lines unless a specific read

operation is performed. A read operation, which consists of activating Read

Enable (REN) and enabling a rising Read Clock (RCLK) edge, will shift the

word from internal memory to the data output lines. In FWFT mode, the first

word written to an empty FIFO is clocked directly to the data output lines

after three transitions of the RCLK signal. A REN does not have to be

asserted for accessing the first word.

Various signals, both input and output signals operate differently depending on which timing mode is in effect.

IDT STANDARD MODE

In this mode, the status flags, FF, PAF, HF, PAE and EF operate in the

manner outlined in Table 1. To write data into to the FIFO, Write Enable

(WEN) must be LOW. Data presented to the DATA IN lines will be clocked

into the FIFO on subsequent transitions of the Write Clock (WCLK). After the

first write is performed, the Empty Flag (EF) will go HIGH. Subsequent

writes will continue to fill up the FIFO. The Programmable Almost-Empty

flag (PAE) will go HIGH after n + 1 words have been loaded into the FIFO,

where n is the Empty offset value. The default setting for this value is stated

in the footnote of Table 1. This parameter is also user programmable. See

section on Programmable Flag Offset Loading.

If one continued to write data into the FIFO, and we assumed no read

operations were taking place, the Half-Full flag (HF) would toggle to LOW

once the 129th (IDT72805LB), 257th (IDT72815LB), 513th (IDT72825LB),

1,025th (IDT72835LB), and 2,049th (IDT72845LB) word respectively was

written into the FIFO. Continuing to write data into the FIFO will cause the

Programmable Almost-Full flag (PAF) to go LOW. Again, if no reads are

performed, the PAF will go LOW after (256-m) writes for the IDT72805LB,

(512-m) writes for the IDT72815LB, (1,024-m) writes for the IDT72825LB,

(2,048–m) writes for the IDT72835LB and (4,096–m) writes for the

IDT72845LB. The offset “m” is the Full offset value. This parameter is also

user programmable. See section on Programmable Flag Offset Loading. If

there is no Full offset specified, the PAF will be LOW when the device is 31

away from completely full for IDT72805LB, 63 away from completely full for

IDT72815LB, and 127 away from completely full for the IDT72825LB/

72835LB/72845LB.

When the FIFO is full, the Full Flag (FF) will go LOW, inhibiting further

write operations. If no reads are performed after a reset, FF will go LOW

after D writes to the FIFO. D = 256 writes for the IDT72805LB, 512 for the

IDT72815LB, 1,024 for the IDT72825LB, 2,048 for the IDT72835LB and

4,096 for the IDT72845LB, respectively.

If the FIFO is full, the first read operation will cause FF to go HIGH.

Subsequent read operations will cause PAF and the Half-Full flag (HF) to

go HIGH at the conditions described in Table 1. If further read operations

occur, without write operations, the Programmable Almost-Empty flag

(PAE) will go LOW when there are n words in the FIFO, where n is the Empty

offset value. If there is no Empty offset specified, the PAE will be LOW when

the device is 31 away from completely empty for IDT72805LB, 63 away from

completely empty for IDT72815LB, and 127 away from completely empty

for IDT72825LB/72835LB/72845LB. Continuing read operations will cause

the FIFO to be empty. When the last word has been read from the FIFO, the

EF will go LOW inhibiting further read operations. REN is ignored when the

FIFO is empty.

FIRST WORD FALL THROUGH MODE (FWFT)

In this mode, the status flags, IR, PAF, HF, PAE and OR operate in the

manner outlined in Table 2. To write data into to the FIFO, WEN must be

LOW. Data presented to the DATA IN lines will be clocked into the FIFO on

subsequent transitions of WCLK. After the first write is performed, the

Output Ready (OR) flag will go LOW. Subsequent writes will continue to fill

up the FIFO. PAE will go HIGH after n + 2 words have been loaded into the

FIFO, where n is the Empty offset value. The default setting for this value

is stated in the footnote of Table 2. This parameter is also user programmable. See section on Programmable Flag Offset Loading.

If one continued to write data into the FIFO, and we assumed no read

operations were taking place, the HF would toggle to LOW once the 130th

(72805LB), 258th (72815LB), 514th (72825LB), 1,026th (72835LB), and

2,050th (72845LB) word respectively was written into the FIFO. Continuing

to write data into the FIFO will cause the PAF to go LOW. Again, if no reads

are performed, the PAF will go LOW after (257-m) writes for the IDT72805LB,

(513-m) writes for the IDT72815LB, (1,025-m) writes for the IDT72825LB,

(2,049–m) writes for the IDT72835LB and (4,097–m) writes for the

IDT72845LB, where m is the Full offset value. The default setting for this

value is stated in the footnote of Table 2.

When the FIFO is full, the Input Ready (IR) flag will go HIGH, inhibiting

further write operations. If no reads are performed after a reset, IR will go

HIGH after D writes to the FIFO. D = 257 writes for the IDT72805LB, 513

for the IDT72815LB, 1,025 for the IDT72825LB, 2,049 for the IDT72835LB

and 4,097 for the IDT72845LB. Note that the additional word in FWFT mode

is due to the capacity of the memory plus output register.

If the FIFO is full, the first read operation will cause the IR flag to go LOW.

Subsequent read operations will cause the PAF and HF to go HIGH at the

conditions described in Table 2. If further read operations occur, without

write operations, the PAE will go LOW when there are n + 1 words in the

FIFO, where n is the Empty offset value. If there is no Empty offset specified,

the PAE will be LOW when the device is 32 away from completely empty for

IDT72805LB, 64 away from completely empty for IDT72815LB, and 128

away from completely empty for IDT72825LB/72835LB/72845LB. Continuing read operations will cause the FIFO to be empty. When the last word has

been read from the FIFO, OR will go HIGH inhibiting further read operations.

REN is ignored when the FIFO is empty.

PROGRAMMABLE FLAG LOADING

Full and Empty flag Offset values can be user programmable. The

IDT72805LB/72815LB/72825LB/72835LB/72845LB has internal registers

for these offsets. Default settings are stated in the footnotes of Table 1 and

Table 2. Offset values are loaded into the FIFO using the data input lines D

D11. To load the offset registers, the Load (LD) pin and WEN pin must be

held LOW. Data present on D0-D11 will be transferred in to the Empty Offset

register on the first LOW-to-HIGH transition of WCLK. By continuing to hold

the LD and WEN pin low, data present on D0-D11 will be transferred into the

Full Offset register on the next transition of the WCLK. The third transition

again writes to the Empty Offset register. Writing all offset registers does not

have to occur at one time. One or two offset registers can be written and then

0-

7

IDT72805LB/72815LB/72825LB/72835LB/72845LB CMOS Dual SyncFIFO

256 x 18, 512 x 18, 1,024 x 18, 2,048 x 18 and 4,096 x 18

TM

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

by bringing the LD pin HIGH, the FIFO is returned to normal read/write

operation. When the LD pin and WEN are again set LOW, the next offset

register in sequence is written.

The contents of the offset registers can be read on the data output lines

0-Q11 when the LD pin is set LOW and REN is set LOW. Data can then be

Q

read on the next LOW-to-HIGH transition of RCLK. The first transition of

RCLK will present the Empty Offset value to the data output lines. The next

transition of RCLK will present the Full offset value. Offset register content

can be read out in the IDT Standard mode only. It cannot be read in the

FWFT mode.

SYNCHRONOUS vs ASYNCHRONOUS PROGRAMMABLE FLAG TIMING SELECTION

The IDT72805LB/72815LB/72825LB/72835LB/72845LB can be configured during the "Configuration at Reset" cycle described in Table 3 with

either asynchronous or synchronous timing for PAE and PAF flags.

If asynchronous PAE/PAF configuration is selected (as per Table 3), the

PAE is asserted LOW on the LOW-to-HIGH transition of RCLK. PAE is reset

to HIGH on the LOW-to-HIGH transition of WCLK. Similarly, the PAF is

asserted LOW on the LOW-to-HIGH transition of WCLK and PAF is reset

to HIGH on the LOW-to-HIGH transition of RCLK. For detail timing dia-

grams, see Figure 13 for asynchronous PAE timing and Figure 14 for

asynchronous PAF timing.

If synchronous PAE/PAF configuration is selected, the PAE is asserted

and updated on the rising edge of RCLK only and not WCLK. Similarly, PAF

is asserted and updated on the rising edge of WCLK only and not RCLK. For

detail timing diagrams, see Figure 22 for synchronous PAE timing and

Figure 23 for synchronous PAF timing.

REGISTER-BUFFERED FLAG OUTPUT SELECTION

The IDT72805LB/72815LB/72825LB/72835LB/72845LB can be configured during the "Configuration at Reset" cycle described in Table 4 with

single, double or triple register-buffered flag output signals. The various

combinations available are described in Table 4 and Table 5. In general,

going from single to double or triple buffered flag outputs removes the

possibility of metastable flag indications on boundary states (i.e, empty or

full conditions). The trade-off is the addition of clock cycle delays for the

respective flag to be asserted. Not all combinations of register-buffered flag

outputs are supported. Register-buffered outputs apply to the Empty Flag

and Full Flag only. Partial flags are not effected. Table 4 and Table 5

summarize the options available.

TABLE 1 — STATUS FLAGS FOR IDT STANDARD MODE

Number of Words in FIFO

IDT72805LB IDT72815LB IDT72825LB IDT72835LB IDT72845LB FF PAF HF PAE EF

00 0 0 0HHHLL

1 to n

(1)

1 to n

(1)

1 to n

(1)

1 to n

(1)

1 to n

(1)

HH H LH

(n + 1) to 128 (n + 1) to 256 (n + 1) to 512 (n + 1) to 1,024 (n + 1) to 2,048 H H H H H

129 to (256-(m+1))

(2)

257 to (512-(m+1))

(256-m) to 255 (512-m)

(2)

513 to (1,024-(m+1))

to 511 (1,024-m) to 1,023 (2,048-m) to 2,047 (4,096-m) to 4,095 H L L H H

(2)

1,025 to (2,048-(m+1))

(2)

2,049 to (4,096-(m+1))

(2)

HHLHH

256 512 1,024 2,048 4,096 L L L H H

NOTES:

1. n = Empty offset (Default Values : IDT72805LB n=31, IDT72815LB n = 63, IDT72825LB/72835LB/72845LB n = 127)

2. m = Full offset (Default Values : IDT72805LB m=31, IDT72815LB m = 63, IDT72825LB/72835LB/72845LB m = 127)

TABLE 2 — STATUS FLAGS FOR FWFT MODE

Number of Words in FIFO

IDT72805LB IDT72815LB IDT72825LB IDT72835LB IDT72845LB IR PAF HF PAE OR

00 0 0 0LHHLH

1 to (n + 1)

(1)

1 to (n + 1)

(n + 2) to 129 (n + 2) to 257 (n + 2) to 513 (n + 2) to 1,025 (n + 2) to 2,049 L H H H L

130 to (257-(m+1))

(2)

258 to (513-(m+1))

(257-m) to 256 (513-m) to 512 (1,025-m) to 1,024 (2,049-m) to 2,048 (4,097-m) to 4,096

257 513 1,025 2,049 4,097 H L L H L

NOTES:

1. n = Empty offset (Default Values : IDT72805LB n = 31, IDT72815LB n = 63, IDT72825LB/72835LB/72845LB n = 127)

2. m = Full Offset (Default Values : IDT72805LB m = 31, IDT72815LB m = 63, IDT72825LB/72835LB/72845LB m = 127)

(1)

(2)

1 to (n + 1)

514 to (1,025-(m+1))

(1)

(2)

1 to (n + 1)

1,026 to (2,049-(m+1))

(1)

(2)

1 to (n + 1)

2,050 to (4,097-(m+1))

(1)

LHHLL

(2)

LHLHL

LLLHL

8

Loading...

Loading...