Integrated Device Technology Inc IDT72413L25D, IDT72413L25DB, IDT72413L25P, IDT72413L25PB, IDT72413L25SO Datasheet

...

Integrated Device Technology, Inc.

CMOS PARALLEL

64 x 5-BIT FIFO

WITH FLAGS

IDT72413

FEATURES:

• First-ln/First-Out Dual-Port memory—45MHz

• 64 x 5 organization

• Low-power consumption

— Active: 200mW (typical)

• RAM-based internal structure allows for fast fall-through

time

• Asynchronous and simultaneous read and write

• Expandable by bit width

• Cascadable by word depth

• Half-Full and Almost-Full/Empty status flags

• IDT72413 is pin and functionally compatible with the

MMI67413

• High-speed data communications applications

• Bidirectional and rate buffer applications

• High-performance CMOS technology

• Available in plastic DIP, CERDIP and SOIC

• Military product compliant to MIL-STD-883, Class B

• Industrial temperature range (-40

o

C to +85oC) is avail-

able, tested to military electrical specifications

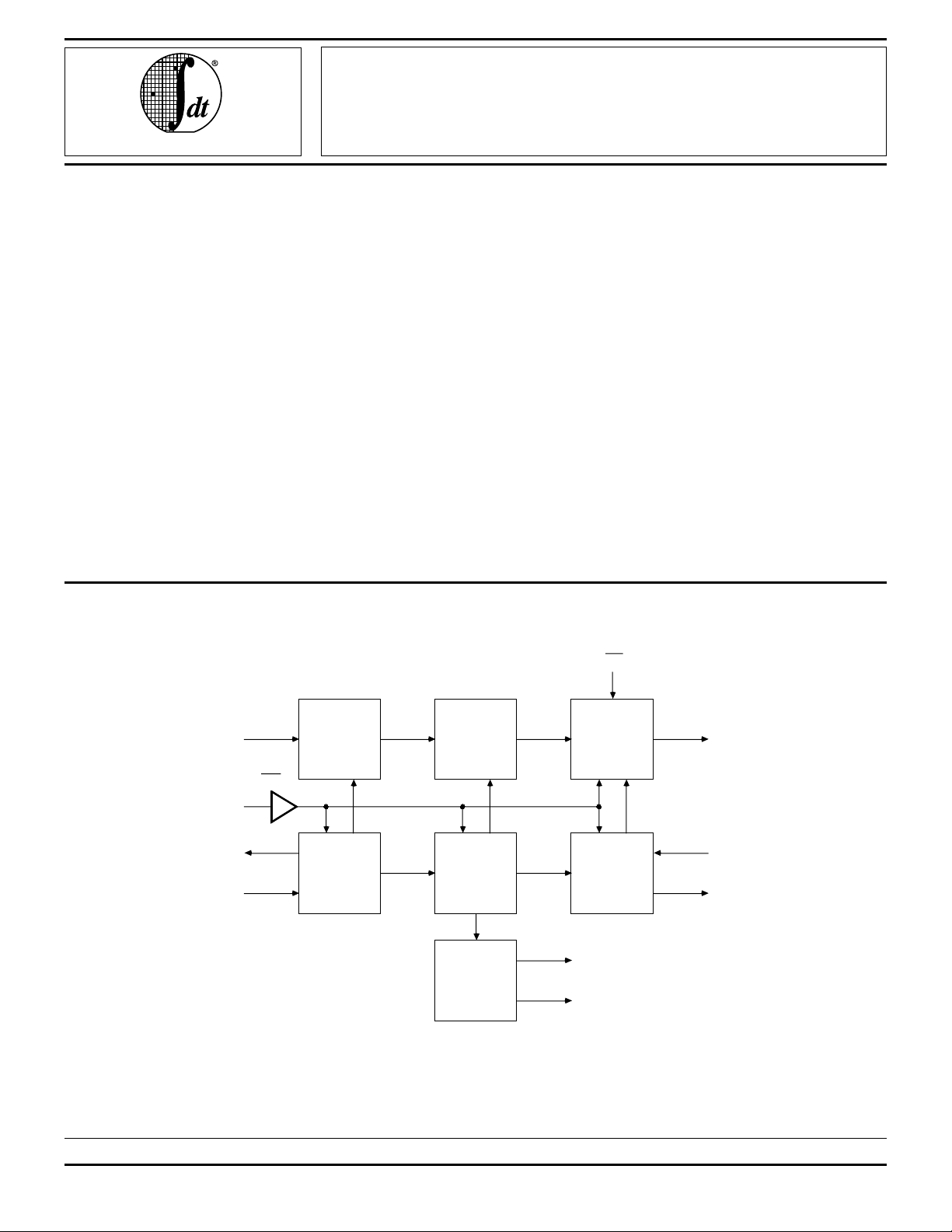

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION:

The IDT72413 is a 64 x 5, high-speed First-In/First-Out

(FIFO) that loads and empties data on a first-in-first-out basis.

It is expandable in bit width. All speed versions are cascadable in depth.

The FIFO has a Half-Full Flag, which signals when it has 32

or more words in memory. The Almost-Full/Empty Flag is

active when there are 56 or more words in memory or when

there are 8 or less words in memory.

The IDT72413 is pin and functionally compatible to the

MMI67413. It operates at a shift rate of 45MHz. This makes it

ideal for use in high-speed data buffering applications. The

IDT72413 can be used as a rate buffer, between two digital

systems of varying data rates, in high-speed tape drivers, hard

disk controllers, data communications controllers and

graphics controllers.

The IDT72413 is fabricated using IDTs high-performance

CMOS process. This process maintains the speed and high

output drive capability of TTL circuits in low-power CMOS.

Military grade product is manufactured in compliance with

the latest revision of MIL-STD-883, Class B.

OUPUT ENABLE

(OE)

DATA

IN

(D

0-4

)

(MR)

MASTER

RESET

IN

(IR)

(SI)

INPUT

READY

SHIFT

The IDT logo is a registered trademark of Integrated Device Technology,Inc.

FAST is a trademark of National Semiconductor, Inc.

FIFO

INPUT

STAGE

INPUT

CONTROL

LOGIC

64 x 5

MEMORY

ARRAY

REGISTER

CONTROL

LOGIC

FLAG

CONTROL

LOGIC

FIFO

OUTPUT

STAGE

OUTPUT

CONTROL

LOGIC

HALF-FULL (HF)

ALMOST-FULL/

EMPTY (AF/E)

(SO)

(OR)

DATA

(Q

0-4

SHIFT

OUT

OUPUT

READY

2748 drw 01

OUT

)

MILITARY AND COMMERCIAL TEMPERATURE RANGES DECEMBER 1996

1996 Integrated Device Technology, Inc. DSC-2748/7

For latest information contact IDT's web site at www.idt.com or fax-on-demand at 408-492-8391.

5.02 1

IDT72413

CMOS PARALLEL 64 x 5-BIT FIFO WITH FLAGS MILITARY AND COMMERCIAL TEMPERATURE RANGES

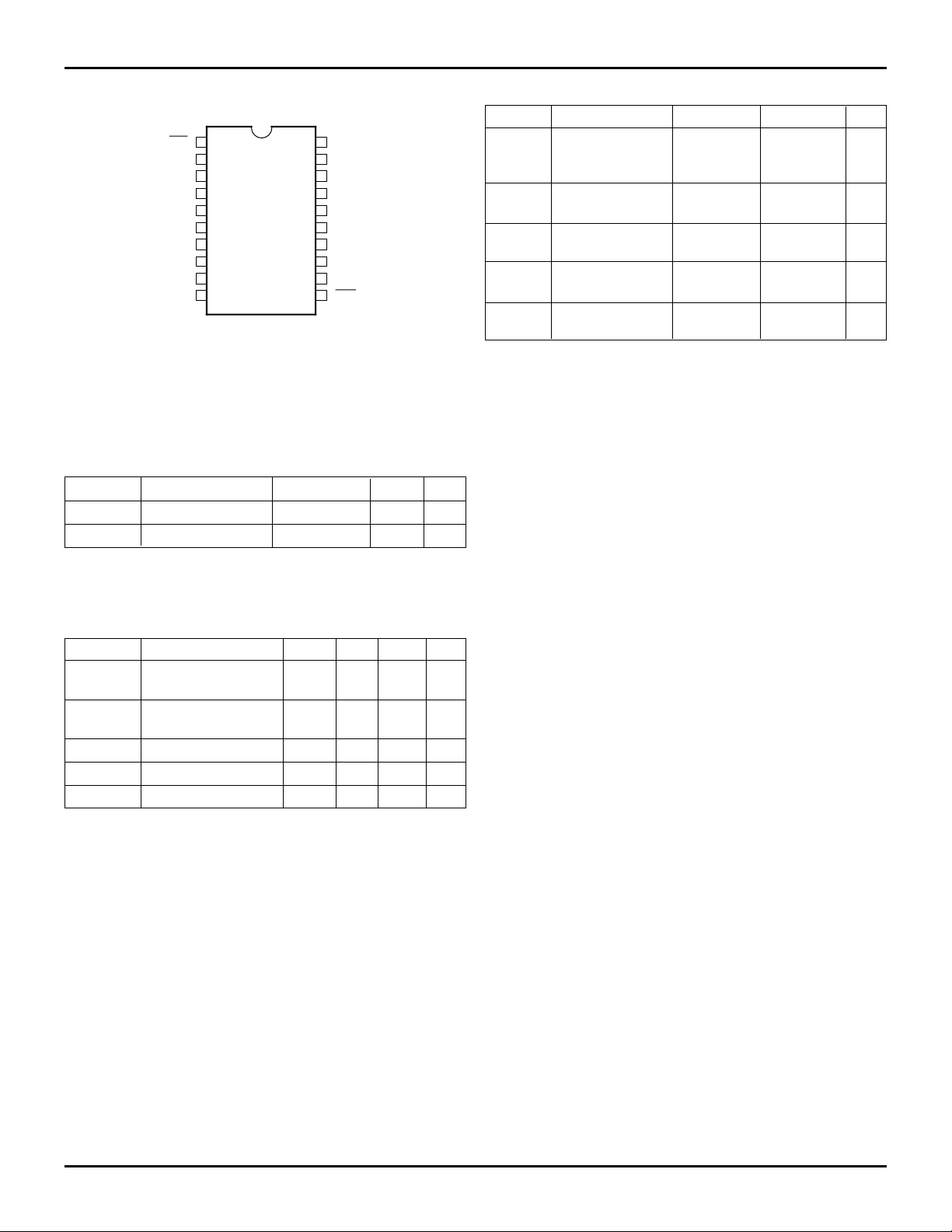

PIN CONFIGURATION

OE

HF

IR

SI

D

D

D

D

D

GND

1

2

3

4

P20-1,

C20-1,

5

0

6

1

2

3

4

7

8

9

10

SO20-2

DIP/SOIC

TOP VIEW

20

Vcc

19

AF/E

18

SO

17

OR

16

Q

&

15

14

13

12

11

0

1

Q

Q

2

Q

3

Q

4

MR

2748 drw 02

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter

IN Input Capacitance VIN = 0V 5 pF

C

OUT Output Capacitance VOUT = 0V 7 pF

C

NOTE: 2748 tbl 02

1. This parameter is sampled and not 100% tested.

2. Characterized values, not currently listed.

(1)

Conditions Max. Unit

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Rating Commercial Military Unit

V

TERM Terminal Voltage -0.5 to +7.0 -0.5 to +7.0 V

with Respect

to GND

T

A Operating 0 to +70 -55 to +125 °C

Temperature

T

BIAS Temperature -55 to +125 -65 to +135 °C

Under Bias

T

STG Storage -55 to +125 -65 to +150 °C

Temperature

OUT DC Output 50 50 mA

I

Current

NOTE: 2748 tbl 01

1. Stresses greater than those listed under ABSOLUTE MAXIMUM

RATINGS may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

CC Military Supply 4.5 5.0 5.5 V

V

Voltage

CC Commercial Supply 4.5 5.0 5.5 V

V

Voltage

GND Supply Voltage 0 0 0 V

IH Input High Voltage 2.0 — — V

V

(1)

IL

V

NOTE: 2748 tbl 03

1. 1.5V undershoots are allowed for 10ns once per cycle.

Input Low Voltage — — 0.8 V

5.02 2

IDT72413

CMOS PARALLEL 64 x 5-BIT FIFO WITH FLAGS MILITARY AND COMMERCIAL TEMPERATURE RANGES

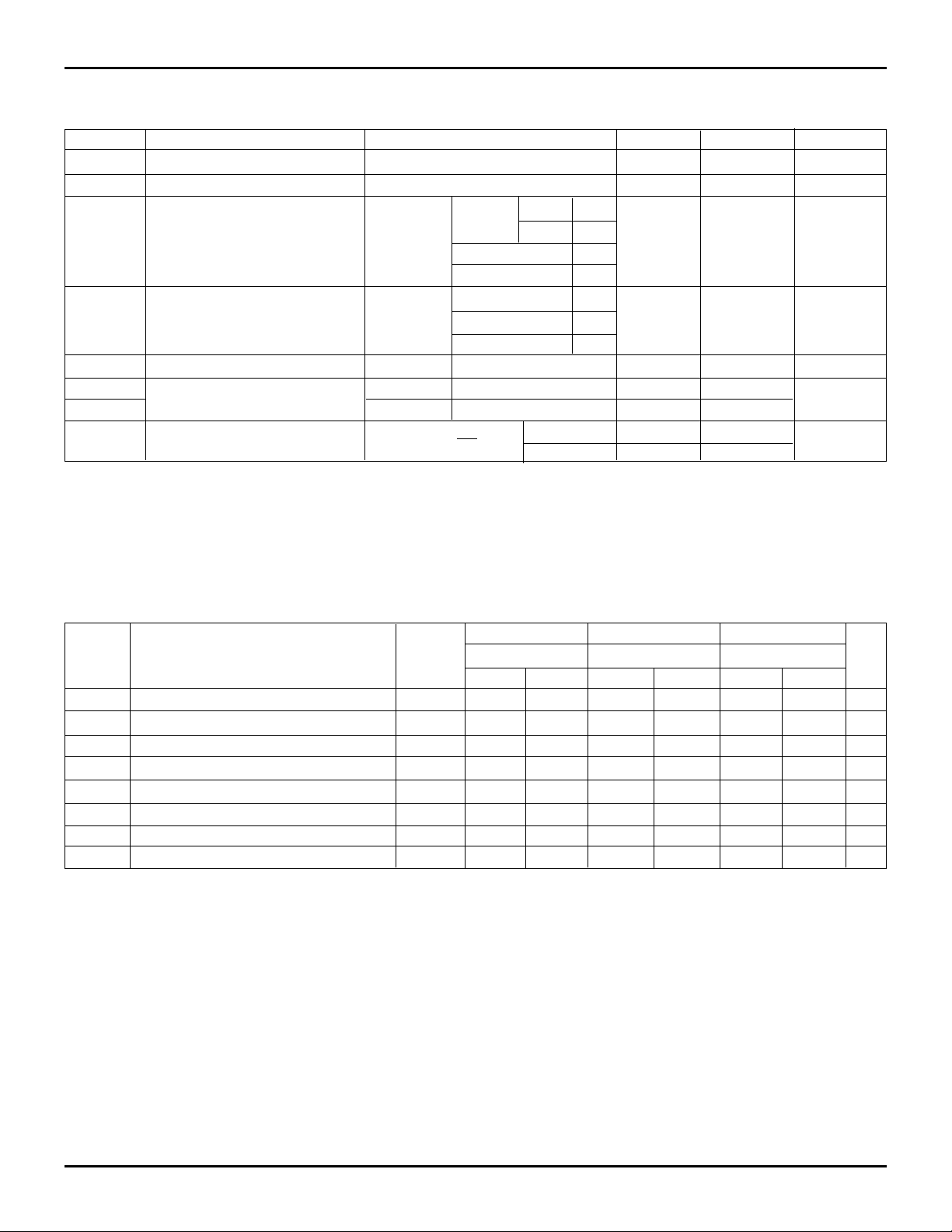

DC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5.0V ± 10%, TA = 0°C to +70°C; Military: VCC = 5.0V ± 10%, TA = –55°C to +125°C)

Symbol Parameter Test Conditions Min. Max. Unit

IL Low-Level Input Current VCC = Max., GND ≤ VI ≤ VCC -10 — µA

I

IH High-Level Input Current VCC = Max., GND ≤ VI ≤ VCC —10 µA

I

OL Low-Level Output Current VCC = Min. IOL (Q0-4) Mil. 12mA — 0.4 V

V

Com'l. 24mA

OL (IR, OR)

I

OL (HF, AF/E) 8mA

I

OH High-Level Output Current VCC = Min. IOH (Q0-4) –4mA 2.4 — V

V

OH (IR, OR) –4mA

I

OH (HF, AF/E) –4mA

I

(2)

OS

I

HZ Off-State Output Current VCC = Max. VO = 2.4V — 20 µA

I

LZ VCC = Max. VO = 0.4V -20 —

I

(3)

CC

I

Output Short-Circuit Current VCC = Max. VO = 0V -20 -110 mA

Supply Current VCC = Max., OE=HIGH Mil. — 70 mA

Inputs LOW, f=25MHz Com'l. — 60

NOTES: 2748 tbl 04

1. Care should be taken to minimize as much as possible the DC and capactive load on IR and OR when operating at frequencies above 25mHz.

2. Not more than one output should be shorted at a time and duration of the short circuit should not exceed one second. Guaranteed by design, but not

currently tested.

3. For frequencies greater than 25MHz, I

CC = 60mA + (1.5mA x [f - 25MHz]) commercial and ICC = 70mA + (1.5mA x [f - 25MHz]) military.

(1)

8mA

OPERATING CONDITIONS

(Commercial: VCC = 5.0V ± 10%, TA = 0°C to +70°C; Military: VCC = 5.0V ± 10%, TA = –55°C to +125°C)

Commercial Military & Commercial Military & Commercial

IDT72413L45 IDT72413L35 IDT72413L25

Symbol Parameters Figure Min. Max. Min. Max. Min. Max. Unit

(1)

SIH

t

SIL

t

IDS Input Data Set-up 2 0 — 0 — 0 — ns

t

IDH Input Data Hold Time 2 13 — 15 — 25 — ns

t

SOH

t

SOL Shift Out LOW Time 5 11 — 17 — 20 — ns

t

MRW Master Reset Pulse 8 20 — 30 — 35 — ns

t

MRS Master Reset Pulse to SI 8 20 — 35 — 35 — ns

t

NOTE: 2748 tbl 05

1. Since the FIFO is a very high-speed device, care must be excercised in the design of the hardware and timing utilized within the design. Device grounding

and decoupling are crucial to correct operation as the FIFO will respond to very small glitches due to long reflective lines, high capacitances and/or poor

supply decoupling and grounding. A monolithic ceramic capacitor of 0.1µF directly between VCC and GND with very short lead length is recommended.

Shift in HIGH Time 2 9 — 9 — 16 — ns

(1)

Shift in LOW TIme 2 11 — 17 — 20 — ns

(1)

Shift Out HIGH Time 5 9 — 9 — 16 — ns

5.02 3

IDT72413

CMOS PARALLEL 64 x 5-BIT FIFO WITH FLAGS MILITARY AND COMMERCIAL TEMPERATURE RANGES

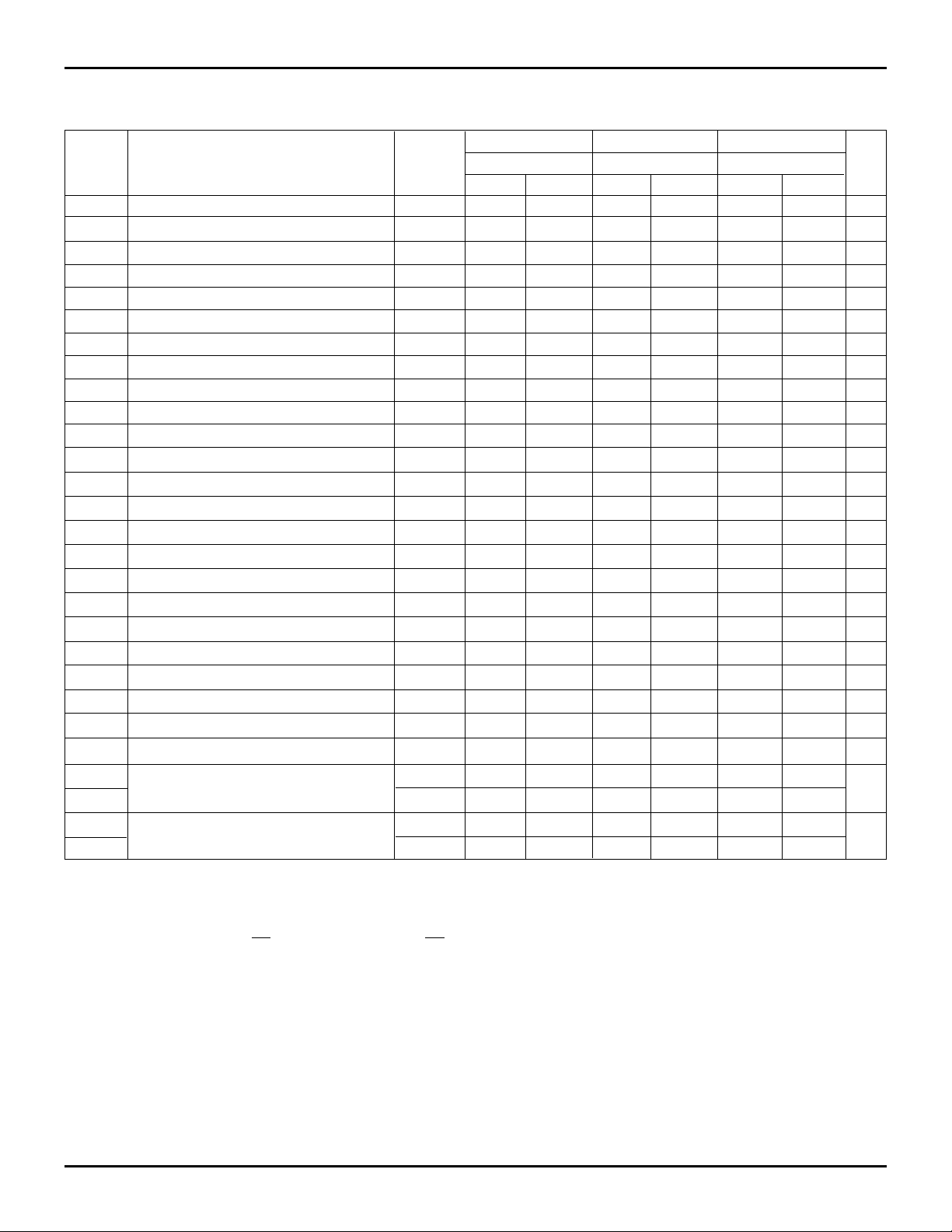

AC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5.0V ± 10%, TA = 0°C to +70°C; Military: VCC = 5.0V ± 10%, TA = –55°C to +125°C)

Commercial Mil. & Com'l Mil. & Com'l

IDT72413L45 IDT72413L35 IDT72413L25

Symbol Parameters Figure Min. Max. Min. Max. Min. Max. Unit

IN Shift In Rate 2 — 45 — 35 — 25 MHz

f

(1)

IRL

t

t

IRH

OUT Shift Out Rate 5 — 45 — 35 — 25 MHz

f

ORL

t

t

ORH

ODH

t

ODS Output Data Shift Next Word 5 — 19 — 20 — 20 ns

t

PT Data Throughput or "Fall-Through" 4, 7 — 25 — 28 — 40 ns

t

t

MRORL Master Reset ↓ to Output Ready LOW 8 — 25 — 28 — 30 ns

MRIRH

t

MRIRL

t

t

MRQ Master Reset ↓ to Outputs LOW 8 — 20 — 25 — 35 ns

MRHF Master Reset ↓ to Half-Full Flag 8 — 25 — 28 — 40 ns

t

MRAFE Master Reset ↓ to AF/E Flag 8 — 25 — 28 — 40 ns

t

IPH

t

OPH

t

ORD

t

AEH Shift Out ↑ to AF/E HIGH 9 — 28 — 28 — 40 ns

t

AEL Shift In ↑ to AF/E 9 — 28 — 28 — 40 ns

t

AFL Shift Out ↑ to AF/E LOW 10 — 28 — 28 — 40 ns

t

AFH Shift In ↑ to AF/E HIGH 10 — 28 — 28 — 40 ns

t

HFH Shift In ↑ to HF HIGH 11 — 28 — 28 — 40 ns

t

HFL Shif Out ↑ to HF LOW 11 — 28 — 28 — 40 ns

t

PHZ

t

PLZ

t

PLZ

t

PHZ

t

NOTES: 2748 tbl 06

1. Since the FIFO is a very high-speed device, care must be taken in the design of the hardware and the timing utilized within the design. Device grounding

and decoupling are crucial to correct operation as the FIFO will respond to very small glitches due to long reflective lines, high capacitances and/or poor

supply decoupling and grounding. A monolithic ceramic capacitor of 0.1µF directly between VCC and GND with very short lead length is recommended.

2. If the FIFO is full, (IR = HIGH),

3. Guaranteed by design but not currently tested.

Shift In ↑ to Input Ready LOW 2 — 18 — 18 — 28 ns

(1)

Shift In ↓ to Input Ready HIGH 2 — 18 — 20 — 25 ns

(1)

Shift Out ↓ to Output Ready LOW 5 — 18 — 18 — 28 ns

(1)

Shift Out ↓ to Output Ready HIGH 5 — 19 — 20 — 25 ns

(1)

Output Data Hold Previous Word 5 5 — 5 — 5 — ns

(3)

Master Reset ↑ to Input Ready HIGH 8 — 25 — 28 — 30 ns

(2)

Master Reset ↓ to Input Ready LOW 8 — 25 — 28 — 30 ns

(3)

Input Ready Pulse HIGH 4 5 — 5 — 5 — ns

(3)

Ouput Ready Pulse HIGH 7 5 — 5 — 5 — ns

(3)

Output Ready ↑ HIGH to Valid Data 5 — 5 — 5 — 7 ns

(3)

Output Disable Delay 12 — 12 — 12 — 15 ns

(3)

(3)

Output Enable Delay 12 — 15 — 15 — 20 ns

(3)

MR ↓ forces IR to go LOW, and MR ↑ causes IR to go HIGH.

12 — 12 — 12 — 15

12 — 15 — 15 — 20

5.02 4

Loading...

Loading...