Integrated Device Technology Inc IDT723631L15PF, IDT723631L15PQF, IDT723631L20PF, IDT723631L20PQF, IDT723631L30PF Datasheet

...

Integrated Device Technology, Inc.

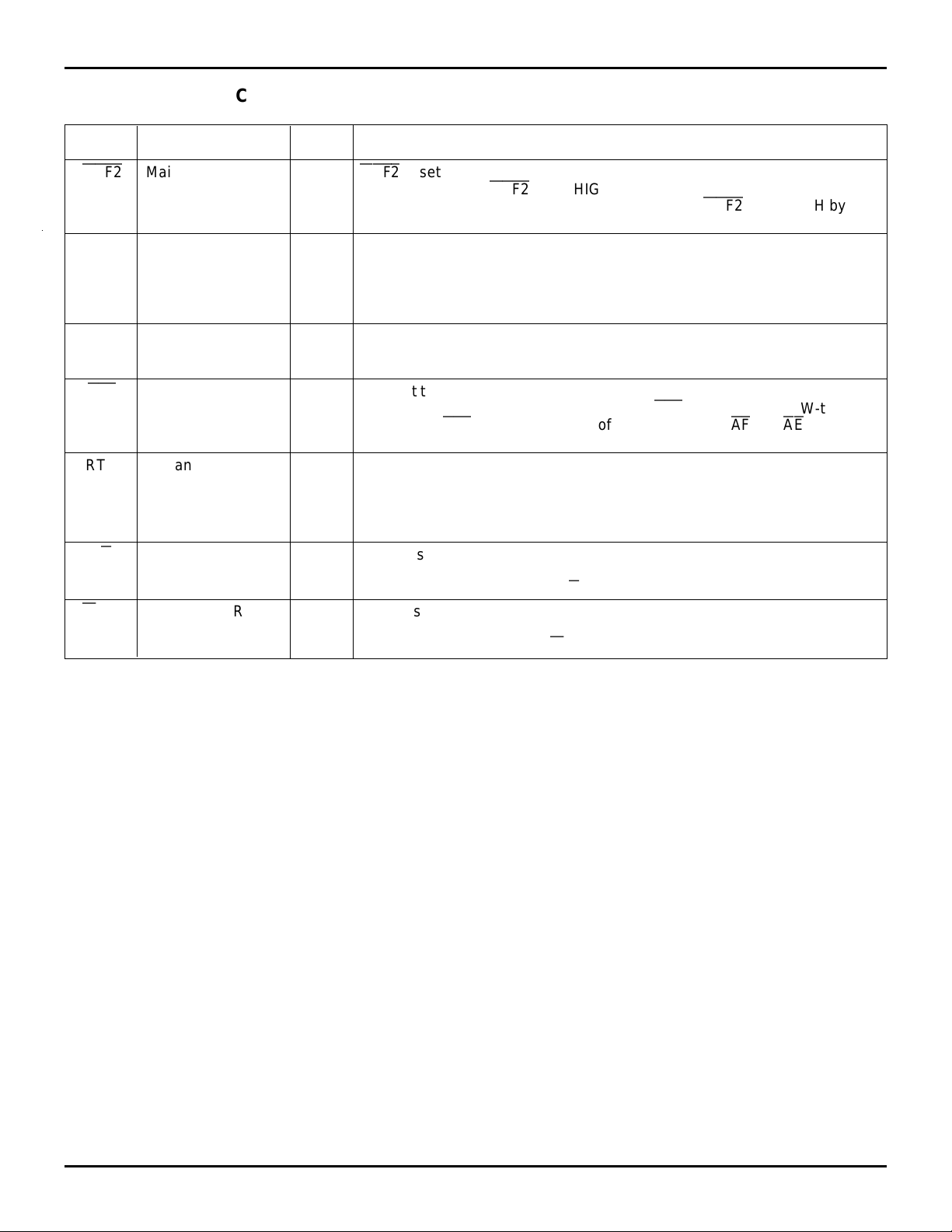

MBF1

CMOS SyncFIFO

512 x 36, 1024 x 36,

2048 x 36

IDT723631

IDT723641

IDT723651

FEATURES:

• Free-running CLKA and CLKB can be asynchronous or

coincident (permits simultaneous reading and writing of

data on a single clock edge)

• Clocked FIFO buffering data from Port A to Port B

• Storage capacity: IDT723631 - 512 x 36

IDT723641 - 1024 x 36

IDT723651 - 2048 x 36

• Synchronous read retransmit capability

• Mailbox register in each direction

• Programmable Almost-Full and Almost-Empty flags

• Microprocessor interface control logic

• Input-Ready (IR) and Almost-Full (AF) flags synchronized

by CLKA

• Output-Ready (OR) and Almost-Empty (AE) flags synchronized by CLKB

• Low-power 0.8-micron advanced CMOS technology

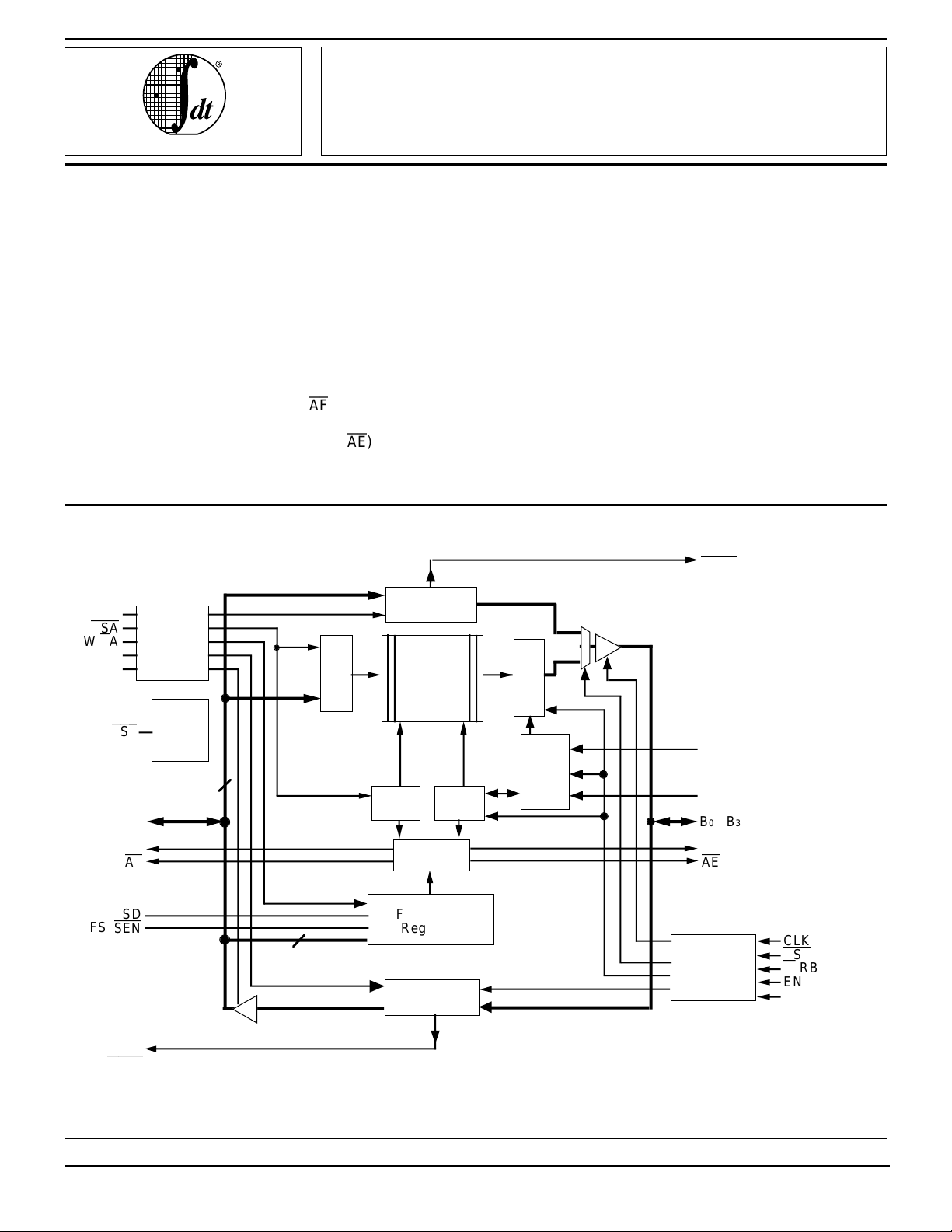

FUNCTIONAL BLOCK DIAGRAM

Mail 1

CLKA

CSA

W/RA

ENA

MBA

RST

Port-A

Control

Logic

Reset

Logic

Input

Register

Register

512 x 36

1024 x 36

2048 x 36

SRAM

• Supports clock frequencies up to 67 MHz

• Fast access times of 11 ns

• Available in 132-pin plastic quad flat package (PQF) or

space-saving 120-pin thin quad flat package (TQFP)

• Industrial temperature range (-40°C to +85°C) is available, tested to military electrical specifications

DESCRIPTION:

The IDT723631/723641/723651 is a monolithic highspeed, low-power, CMOS clocked FIFO memory. It supports

clock frequencies up to 67 MHz and has read access times as

fast as 12ns. The 512/1024/2048 x 36 dual-port SRAM FIFO

buffers data from port A to Port B. The FIFO memory has

retransmit capability, which allows previously read data to be

accessed again. The FIFO has flags to indicate empty and full

conditions and two programmable flags (almost full and almost empty) to indicate when a selected number of words is

Output

Register

RTM

36

A0 - A35

IR

AF

0/SD

FS

FS

1/

SEN

MBF2

The IDT logo is a registered trademark and SyncFIFO is a trademark of Integrated Device Technology, Inc.

10

Write

Pointer

Read

Pointer

Status Flag

Logic

Flag Offset

Registers

Mail 2

Register

Sync

Logic

Retransmit

RFM

B0 - B35

OR

AE

Port-B

Control

Logic

CLKB

CSB

W

/RB

ENB

MBB

3023 drw 01

COMMERCIAL TEMPERATURE RANGE MAY 1997

1997 Integrated Device Technology, Inc. DSC-3023/3

For latest information contact IDT's web site at www.idt.com or fax-on-demand at 408-492-8391.

1

IDT723631/723641/723651 CMOS SyncFIFO

N

512 x 36, 1024 x 36, 2048 x 36 COMMERCIAL TEMPERATURE RANGE

DESCRIPTION (CONTINUED)

stored in memory. Communication between each port may

take place with two 36-bit mailbox registers. Each mailbox

register has a flag to signal when new mail has been stored.

Two or more devices may be used in parallel to create wider

data paths. Expansion is also possible in word depth.

The IDT723631/723641/723651 is a clocked FIFO, which

means each port employs a synchronous interface. All data

transfers through a port are gated to the LOW-to-HIGH

transition of a continuous (free-running) port clock by enable

signals. The continuous clocks for each port are independent

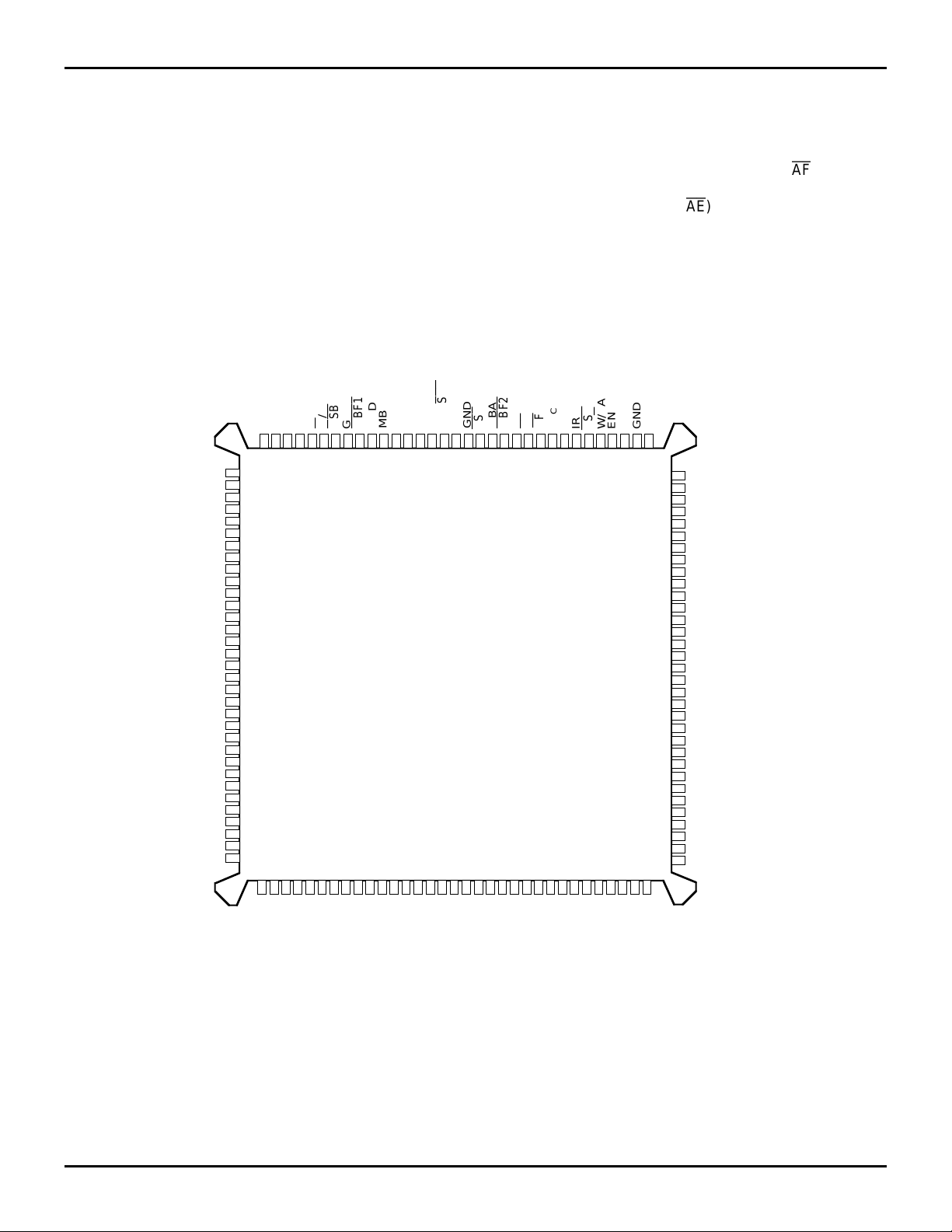

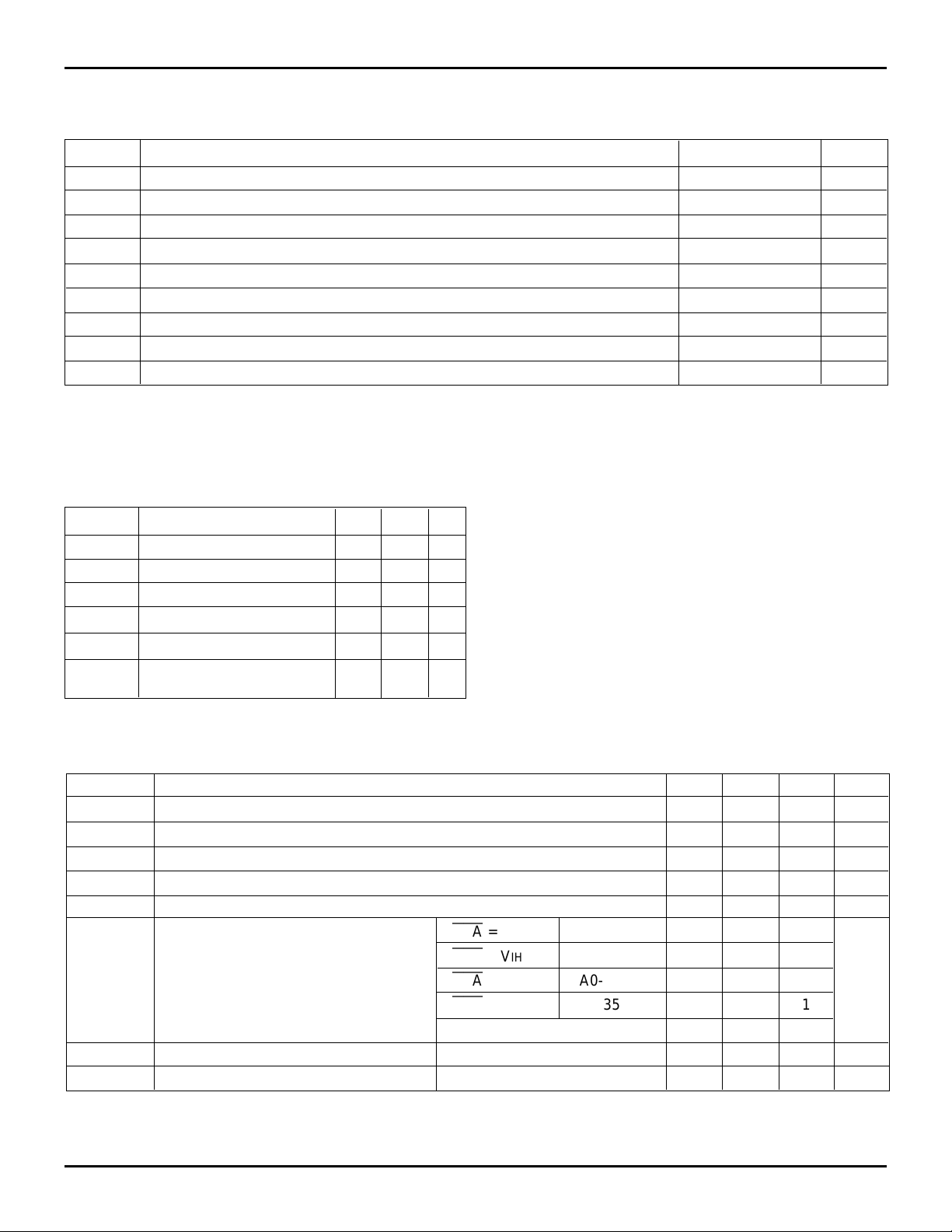

PIN CONFIGURATION

CC

V

RFM

RTM

SE

FS1/

*

NC

B

B

B

B

GND

B

B

B

B

B

B

V

CC

B

B

GND

B

B

B

B

B

B

GND

B

B

V

CC

B

B

B

B

GND

NC

NC

/RB

CC

V

ENB

CLKB

CSB

NC

W

GND

NC

17161514131211

18

35

19

34

20

33

21

32

22

23

31

24

30

25

29

26

28

27

27

28

26

29

30

25

31

24

32

33

23

34

22

35

21

36

20

37

19

38

18

39

40

17

41

16

42

43

15

44

14

45

13

46

12

47

48

49

50

NC

MBF1

MBB

GND

987654321

10

515253545556575859606162636465666768697071727374757677787980818283

of one another and can be asynchronous or coincident. The

enables for each port are arranged to provide a simple

interface between microprocessors and/or buses with synchronous control.

The input-ready (IR) flag and almost-full (AF) flag of the

FIFO are two-stage synchronized to CLKA. The output-ready

(OR) flag and almost-empty (AE) flag of the FIFO are twostage synchronized to CLKB. Offset values for the almost-full

and almost empty flags of the FIFO can be programmed from

port A or through a serial input.

A

GND

FS0/SD

RST

132

131

MBF2

MBA

130

129

CC

V

128

AE

127

AF

126

CC

V

125

OR

124

IR

123

CSA

122

R

W/

121

ENA

120

119

CLKA

GND

118

NC

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

NC

NC

A

35

A

34

A

33

A

32

V

CC

A

31

A

30

GND

A

29

A

28

A

27

A

26

A

25

A

24

A

23

GND

A

22

V

CC

A

21

A

20

A

19

A

18

GND

A

17

A

16

A

15

A

14

A

13

V

CC

A

12

NC

NC

11

B9B7B8

B10

B

VCC

B6

5

B

GND

B4B3B2B1B0

GND

*Electrical pin 1 in center of beveled edge. Pin 1 identifier in corner.

PQFP (PQ132-1, order code: PQF)

TOP VIEW

Notes:

1. NC – No internal connection

2. Uses Yamaichi socket IC51-1324-828

0

A1

A2

VCC

A3A4A5

A

6

A

GND

A7A8A9

NC

NC

A11

A10

GND

3023 drw 02

2

IDT723631/723641/723651 CMOS SyncFIFO

N

512 x 36, 1024 x 36, 2048 x 36 COMMERCIAL TEMPERATURE RANGE

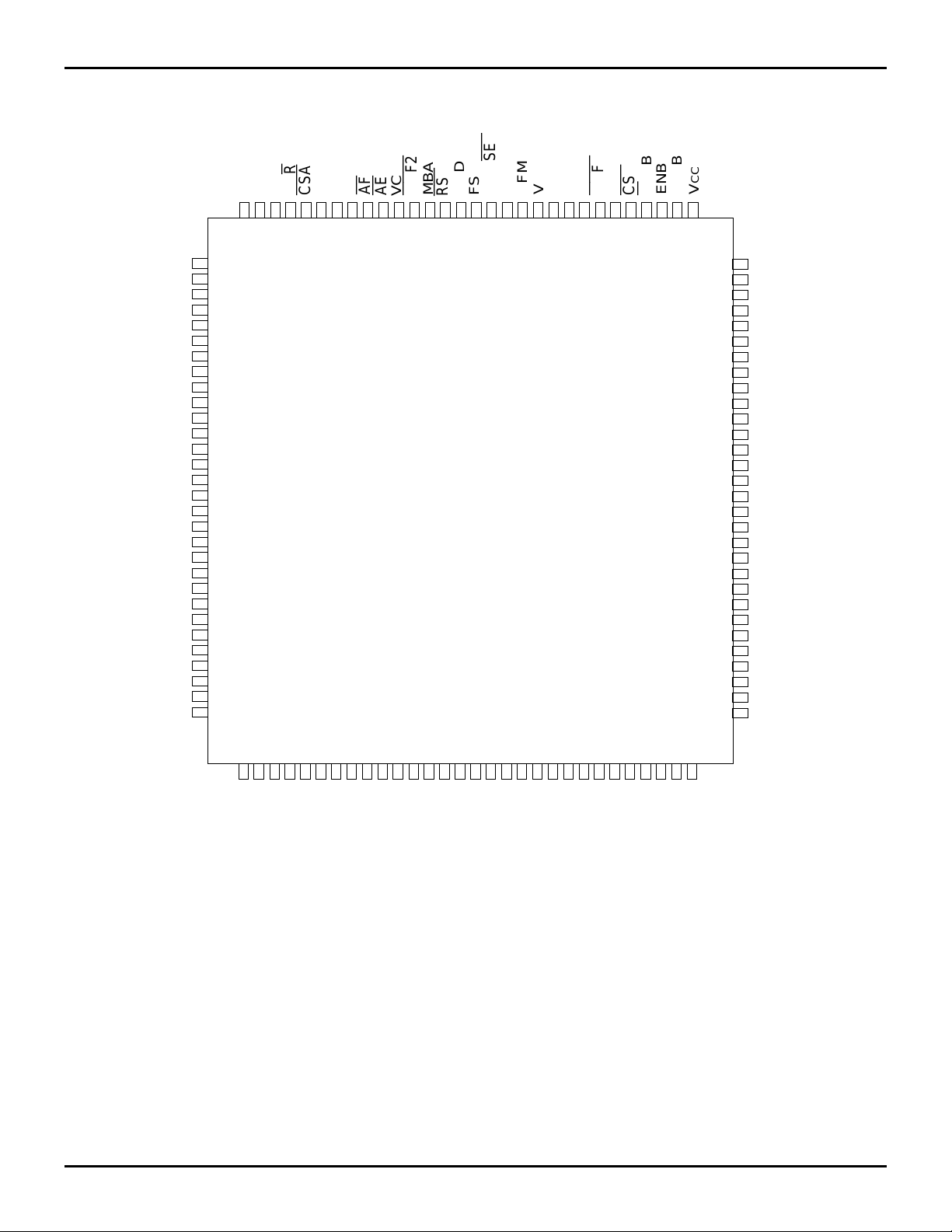

PIN CONFIGURATION (CONTINUED)

A35

A34

A33

A32

VCC

A31

A30

GND

29

A

A28

A27

A26

A25

A24

A23

GND

22

A

VCC

A21

A20

A19

A18

GND

17

A

A16

A15

A14

A13

VCC

A12

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

GND

CLKA

120

119

A

R

ENA

W/

118

117

IR

CSA

116

OR

115

CC

V

114

AF

113

AE

112

VCC

111

MBF2

110

109

MBA

RST

108

107

FS0/SD

GND

106

105

SE

FS1/

RTM

104

103

CC

V

RFM

102

101

NC

MBB

GND

MBF1

GND

99

98979695949392

100

/RB

W

CSB

ENB

CLKB

CC

V

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

64

63

62

61

B35

B34

B33

B32

GND

31

B

B30

B29

B28

B27

B26

VCC

B25

B24

GND

23

B

B22

B21

B20

B19

B18

GND

17

B

B16

VCC

B15

B14

B13

B12

GND

313233

GND

Note:

1. NC – No internal connection

11

A

A10

34

353637

A9A8A7

39

40

38

41

4243444546

A5

A6

GND

A3A4A2

VCC

TQFP (PN120-1, order code: PF)

TOP VIEW

47

0

A1

B0B1B2

A

GND

GND

484950

B3B4B5

51

52

53545556575859

B6

GND

CC

V

60

B7

B8

B11B9B10

3023 drw 03

3

IDT723631/723641/723651 CMOS SyncFIFO

512 x 36, 1024 x 36, 2048 x 36 COMMERCIAL TEMPERATURE RANGE

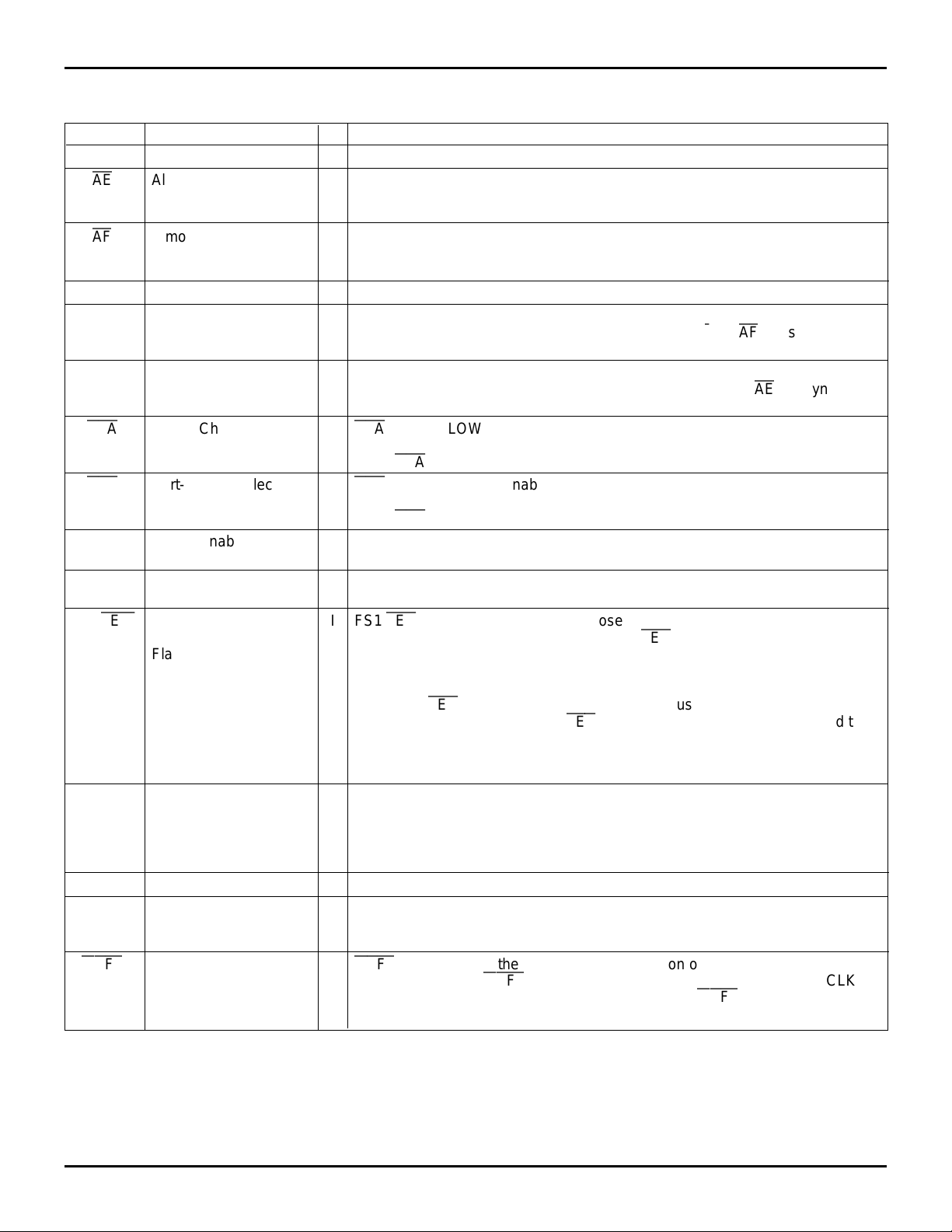

PIN DESCRIPTION

Symbol Name I/O Description

A0-A35 Port-A Data I/O 36-bit bidirectional data port for side A.

AE

AF

B0-B35 Port-B Data. I/O 36-bit bidirectional data port for side B.

CLKA Port-A Clock I CLKA is a continuous clock that synchronizes all data transfers through port-A

CLKB Port-B Clock I CLKB is a continuous clock that synchronizes all data transfers through port-B

CSA

CSB

ENA Port-A Enable I ENA must be HIGH to enable a LOW-to-HIGH transition of CLKA to read or

ENB Port-B Enable I ENB must be HIGH to enable a LOW-to-HIGH transition of CLKB to read or

FS1/

SEN,

FS0/SD Serial Enable, programming. During a device reset, FS1/

IR Input-Ready Flag O IR is synchronized to the LOW-to-HIGH transition of CLKA. When IR is LOW,

MBA Port-A Mailbox Select I A HIGH level chooses a mailbox register for a port-A read or write operation.

MBB Port-B Mailbox Select I A HIGH level chooses a mailbox register for a port-B read or write operation.

MBF1

Almost-Empty Flag O Programmable flag synchronized to CLKB. It is LOW when the number of

words in the FIFO is less than or equal to the value in the almost-empty

register (X).

Almost-Full Flag. O Programmable flag synchronized to CLKA. It is LOW when the number of

empty locations in the FIFO is less than or equal to the value in the almost-full

offset register (Y).

and may be aynchronous or coincident to CLKB. IR and AF are synchronous

to the LOW-to-HIGH transition of CLKA.

and may be asynchronous or coincident to CLKA. OR and AE are synchro

nous to the LOW-to-HIGH transition of CLKB.

Port-A Chip Select I

CSA

must be LOW to enable a LOW-to-HIGH transition of CLKA to read or

write data on port-A. The A0-A35 outputs are in the high-impedance state

when

CSA

is HIGH.

Port-B Chip Select I

CSB

must be LOW to enable a LOW-to-HIGH transition of CLKB to read or

write data on port-B. The B0-B35 outputs are in the high-impedance state

when

CSB

is HIGH.

write data on port-A.

write data on port-B.

Flag-Offset Select 1/ I FS1/

SEN

and FS0/SD are dual-purpose inputs used for flag offset register

SEN

and FS0/SD selects the flag

Flag Offset 0/ offset programming method. Three offset register programming methods are

Serial Data available: automatically load one of two preset values, parallel load from port

A, and serial load. When serial load is selected for flag offset register programming, FS1/

transition of CLKA. When FS1/

SEN

is used as an enable synchronous to the LOW-to-HIGH

SEN

is LOW, a rising edge on CLKA load the

bit present on FS0/SD into the X and Y registers. The number of bit writes

required to program the offset registers is 18/20/22. The first bit write stores

the Y-register MSB and the last bit write stores the X-register LSB.

the FIFO is full and writes to its array are disabled. When the FIFO is in

retransmit mode, IR indicates when the memory has been filled to the point of

the retransmit data and prevents further writes. IR is set LOW during reset

and is set HIGH after reset.

When the B0-B35 outputs are active, a HIGH level on MBB selects data from

the mail1 register for output and a LOW level selects FIFO data for output.

Mail1 Register Flag O

MBF1

is set LOW by the LOW-to-HIGH transition of CLKA that writes data to

the mail1 register.

when a port-B read is selected and MBB is HIGH.

MBF1

is set HIGH by a LOW-to-HIGH transition of CLKB

MBF1

is set HIGH by a

reset.

3023 tbl 01

4

IDT723631/723641/723651 CMOS SyncFIFO

512 x 36, 1024 x 36, 2048 x 36 COMMERCIAL TEMPERATURE RANGE

PIN DESCRIPTION (CONTINUED)

Symbol Name I/O Description

MBF2

OR Output-Ready Flag O OR is synchronized to the LOW-to-HIGH transition of CLKB. When OR is

RFM Read From Mark I When the FIFO is in retransmit mode, a HIGH on RFM enables a LOW-to-

RST

RTM Retransmit Mode I When RTM is HIGH and valid data is present in the FIFO output register (OR

W/RA Port-A Write/Read I A HIGH selects a write operation and a LOW selects a read operation on

W

/RB Port-B Write/Read I A LOW selects a write operation and a HIGH selects a read operation on

Mail2 Register Flag O

MBF2

is set LOW by the LOW-to-HIGH transition of CLKB that writes data to

the mail2 register.

when a port-A read is selected and MBA is HIGH.

MBF2

is set HIGH by a LOW-to-HIGH transition of CLKA

MBF2

is set HIGH by a

reset.

LOW, the FIFO is empty and reads are disabled. Ready data is present in the

output register of the FIFO when OR is HIGH. OR is forced LOW during the

reset and goes HIGH on the third LOW-to-HIGH transition of CLKB after a

word is loaded to empty memory.

HIGH transition of CLKB to reset the read pointer to the beginning retransmit

location and output the first selected retransmit data.

Reset I To reset the device, four LOW-to-HIGH transitions of CLKA and four LOW-to-

HIGH transitions of CLKB must occur while

transition of

RST

latches the status of FS0 and FS1 for AF and AE offset

RST

is LOW. The LOW-to-HIGH

selection.

is HIGH), a LOW-to-HIGH transition of CLKB selects the data for the beginning of a retransmit and puts the FIFO in retransmit mode. The selected word

remains the initial retransmit point until a LOW-to-HIGH transition of CLKB

occurs while RTM is LOW, taking the FIFO out of retransmit mode.

Select port A for a LOW-to-HIGH transition of CLKA. The A0-A35 outputs are in the

high-impedance state when W/RA is HIGH.

Select port B for a LOW-to-HIGH transition of CLKB. The B0-B35 outputs are in the

high-impedance state when W/RB is LOW.

3023 tbl 02

5

IDT723631/723641/723651 CMOS SyncFIFO

512 x 36, 1024 x 36, 2048 x 36 COMMERCIAL TEMPERATURE RANGE

ABSOLUTE MAXIMUM RATINGS OVER OPERATING FREE-AIR TEMPERATURE RANGE

(UNLESS OTHERWISE NOTED)

Symbol Rating Commercial Unit

CC Supply Voltage Range -0.5 to 7 V

V

(2)

V

I

O

V

IK Input Clamp Current, (VI < 0 or VI > VCC) ±20 mA

I

I

OK Output Clamp Current, (VO = < 0 or VO > VCC) ±50 mA

OUT Continuous Output Current, (VO = 0 to VCC) ±50 mA

I

I

CC Continuous Current Through VCC or GND ±400 mA

A Operating Free Air Temperature Range 0 to 70 °C

T

STG Storage Temperature Range -65 to 150 °C

T

NOTES:

1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional

operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure

to absolute-maximum-rated conditions for extended periods may affect device reliability.

2. The input and output voltage ratings may be exceeded provided the input and output current ratings are observed.

Input Voltage Range -0.5 to VCC+0.5 V

(2)

Output Voltage Range -0.5 to VCC+0.5 V

(2)

3023 tbl 03

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min. Max. Unit

VCC Supply Voltage 4.5 5.5 V

VIH HIGH Level Input Voltage 2 – V

VIL LOW-Level Input Voltage – 0.8 V

IOH HIGH-Level Output Current – -4 mA

IOL LOW-Level Output Current – 8 mA

TA Operating Free-air 0 70 °C

Temperature

3023 tbl 04

ELECTRICAL CHARACTERISTICS OVER RECOMMENDED OPERATING FREE-AIR TEMPERATURE RANGE (UNLESS OTHERWISE NOTED)

Parameter Test Conditions Min. Typ.

OH VCC = 4.5V, IOH = -4 mA 2.4 V

V

V

OL VCC = 4.5 V, IOL = 8 mA 0.5 V

LI VCC = 5.5 V, VI = VCC or 0 ±5 µA

I

I

LO VCC = 5.5 V, VO = VCC or 0 ±5 µA

CC VCC = 5.5 V, VI = VCC -0.2 V or 0 400 µA

I

(2)

∆I

CC

VCC = 5.5 V, One Input at 3.4 V,

Other Inputs at V

CC or GND

CSA

= VIH A0-A35 0 mA

CSB

= VIH B0-B35 0

CSA

CSB

IL A0-A35 1

= V

IL B0-35 1

= V

All Other Inputs 1

C

IN VI = 0, f = 1 MHz 4 pF

C

OUT VO = 0, f = 1 MHZ 8 pF

NOTES:

1. All typical values are at VCC = 5 V, TA = 25°C.

2. This is the supply current when each input is at least one of the specified TTL voltage levels rather than 0 V or VCC.

(1)

Max. Unit

3023 tbl 05

6

IDT723631/723641/723651 CMOS SyncFIFO

512 x 36, 1024 x 36, 2048 x 36 COMMERCIAL TEMPERATURE RANGE

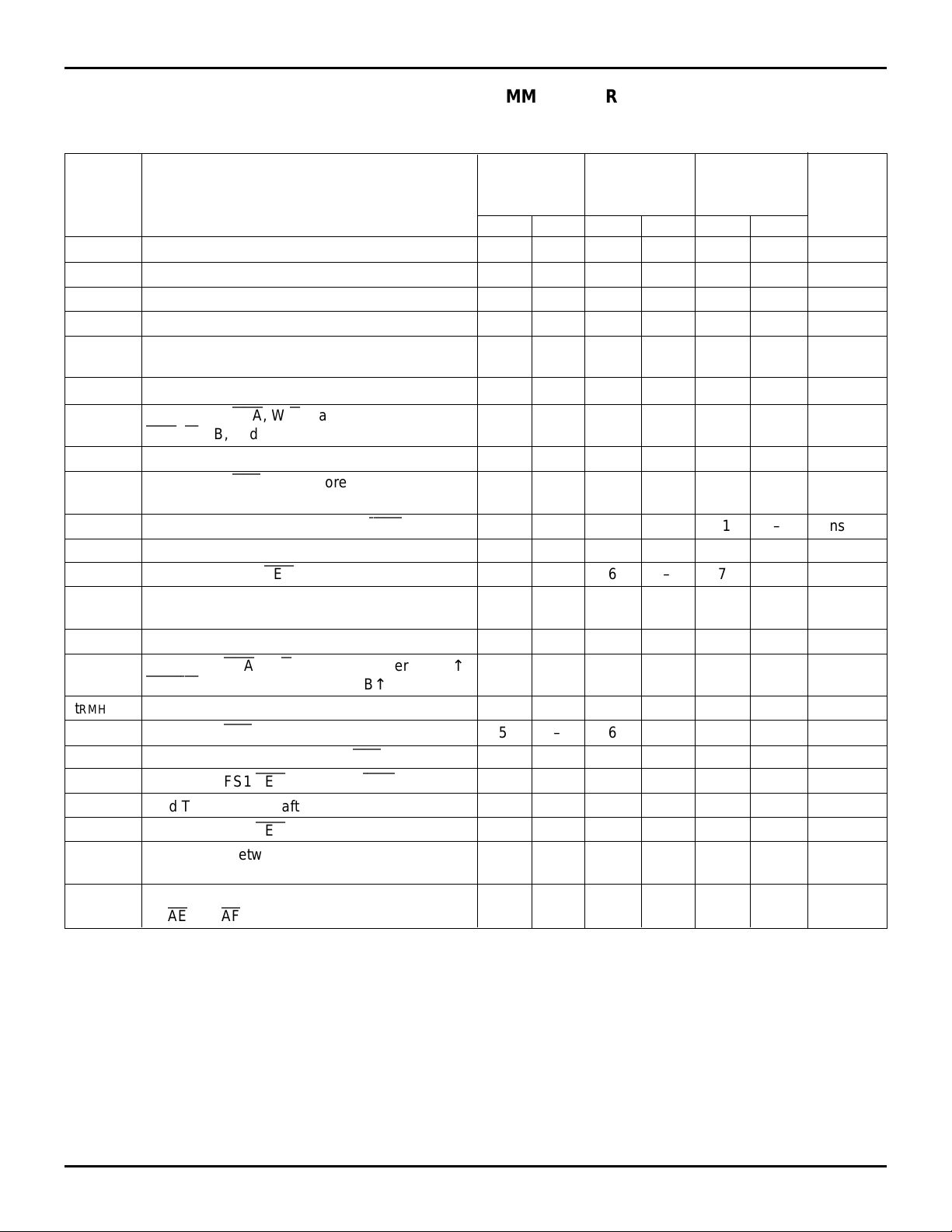

AC ELECTRICAL CHARACTERISTICS OVER RECOMMENDED RANGES OF SUPPLY VOLTAGE

AND OPERATING FREE-AIR TEMPERATURE

IDT723631L15 IDT723631L20 IDT723631L30

IDT723641L15 IDT723641L20 IDT723641L30

IDT723651L15 IDT723651L20 IDT723651L30

Symbol Parameter Min. Max. Min. Max. Min. Max. Unit

f

S Clock Frequency, CLKA or CLKB – 66.7 – 50 – 33.4 MHz

t

CLK Clock Cycle Time, CLKA or CLKB 15 – 20 – 30 – ns

CLKH Pulse Duration, CLKA or CLKB HIGH 6–8–12–ns

t

CLKL Pulse Duration, CLKA or CLKB LOW 6–8–12–ns

t

t

DS Setup Time, A0-A35 before CLKA↑ and B0-B35 5–6–7–ns

before CLKB↑

ENS1 Setup Time, ENA to CLKA↑; ENB to CLKB↑ 5–6–7–ns

t

t

ENS2 Setup Time,

CSB, W

RMS Setup Time, RTM and RFM to CLKB↑ 6–6.5–7–ns

t

RSTS Setup Time,

t

or CLKB↑

tFSS Setup Time, FS0 and FS1 before

(2)

SDS

t

t

SENS

DH Hold Time, A0-A35 after CLKA↑ and B0-B35 0–0–0–ns

t

Setup Time, FS0/SD before CLKA↑ 5–6–7–ns

(2)

Setup Time, FS1/

after CLKB↑

ENH1 Hold Time, ENA after CLKA↑; ENB after CLKB↑ 0–0–0–ns

t

t

ENH2 Hold Time,

CSB, W

RMH Hold Time, RTM and RFM after CLKB↑ 0–0–0–ns

t

t

RSTH Hold Time,

FSH Hold Time, FS0 and FS1 after

t

(2)

SPH

t

t

SDH

SENH

t

t

SKEW1

Hold Time, FS1/

(2)

Hold Time, FS0/SD after CLKA↑ 0–0–0–ns

(2)

Hold Time, FS1/

(3)

Skew Time, between CLKA↑ and CLKB↑ 9–11–13–ns

for OR and IR

(3)

SKEW2

t

Skew Time, between CLKA↑ and CLKB↑ 12 – 16 – 20 – ns

for AE and

NOTES:

1. Requirement to count the clock edge as one of at least four needed to reset a FIFO.

2. Only applies when serial load method is used to program flag offset registers.

3. Skew time is not a timimg constraint for proper device operation and is only included to illustrate the timing relationship between CLKA cycle and CLKB

cycle.

CSA

, W/RA, and MBA to CLKA↑; 7–7.5–8–ns

/RB, and MBB to CLKB↑

RST

(1)

LOW before CLKA↑ 5–6–7–ns

RST

SEN

before CLKA↑ 5–6–7–ns

CSA

, W/RA, and MBA after CLKA↑;0–0–0–ns

/RB, and MBB after CLKB↑

RST

LOW after CLKA↑ or CLKB↑

RST

SEN

HIGH after

SEN

after CLKA↑ 0–0–0–ns

RST

AF

HIGH 9 – 10 – 11 – ns

(1)

5–6–7–ns

HIGH 0–0–0–ns

HIGH 0–0–0–ns

3023 tbl 06

7

Loading...

Loading...