Integrated Device Technology Inc IDT72200L12TC, IDT72200L12TP, IDT72200L15TC, IDT72200L15TP, IDT72200L20TC Datasheet

...

Integrated Device Technology, Inc.

CMOS SyncFIFO

64 x 8, 256 x 8, 512 x 8,

1024 x 8, 2048 x 8 and 4096 x 8

IDT72420

IDT72200

IDT72210

IDT72220

IDT72230

IDT72240

FEATURES:

• 64 x 8-bit organization (IDT72420)

• 256 x 8-bit organization (IDT72200)

• 512 x 8-bit organization (IDT72210)

• 1024 x 8-bit organization (IDT72220)

• 2048 x 8-bit organization (IDT72230)

• 4096 x 8-bit organization (IDT72240)

• 12 ns read/write cycle time (IDT72420/72200/72210)

• 15 ns read/write cycle time (IDT72220/72230/72240)

• Read and write clocks can be asynchronous or

coincidental

• Dual-Ported zero fall-through time architecture

• Empty and Full flags signal FIFO status

• Almost-empty and almost-full flags set to Empty+7 and

Full-7, respectively

• Output enable puts output data bus in high-impedance

state

• Produced with advanced submicron CMOS technology

• Available in 28-pin 300 mil plastic DIP and 300 mil

ceramic DIP

• For surface mount product please see the IDT72421/

72201/72211/72221/72231/72241 data sheet

• Military product compliant to MIL-STD-883, Class B

• Industrial temperature range (-40

available, tested to military electrical specifications

O

C to +85OC) is

DESCRIPTION:

The IDT72420/72200/72210/72220/72230/72240

SyncFIFO are very high-speed, low-power First-In, FirstOut (FIFO) memories with clocked read and write controls.

The IDT72420/72200/72210/72220/72230/72240 have a 64,

256, 512, 1024, 2048, and 4096 x 8-bit memory array, respectively. These FIFOs are applicable for a wide variety of data

buffering needs, such as graphics, Local Area Networks

(LANs), and interprocessor communication.

These FIFOs have 8-bit input and output ports. The input

port is controlled by a free-running clock (WCLK), and a write

enable pin (WEN). Data is written into the Synchronous FIFO

on every clock when WEN is asserted. The output port is

controlled by another clock pin (RCLK) and a read enable pin

(REN). The read clock can be tied to the write clock for single

clock operation or the two clocks can run asynchronous of one

another for dual clock operation. An output enable pin (OE) is

provided on the read port for three-state control of the output.

These Synchronous FIFOs have two end-point flags, Empty

(EF) and Full (FF). Two partial flags, Almost-Empty (AE) and

Almost-Full (AF), are provided for improved system control.

The partial ( AE) flags are set to Empty+7 and Full-7 for AE and

AF respectively.

The IDT72420/72200/72210/72220/72230/72240 are fabricated using IDT’s high-speed submicron CMOS technology.

Military grade product is manufactured in compliance with the

latest revision of MIL-STD-883, Class B.

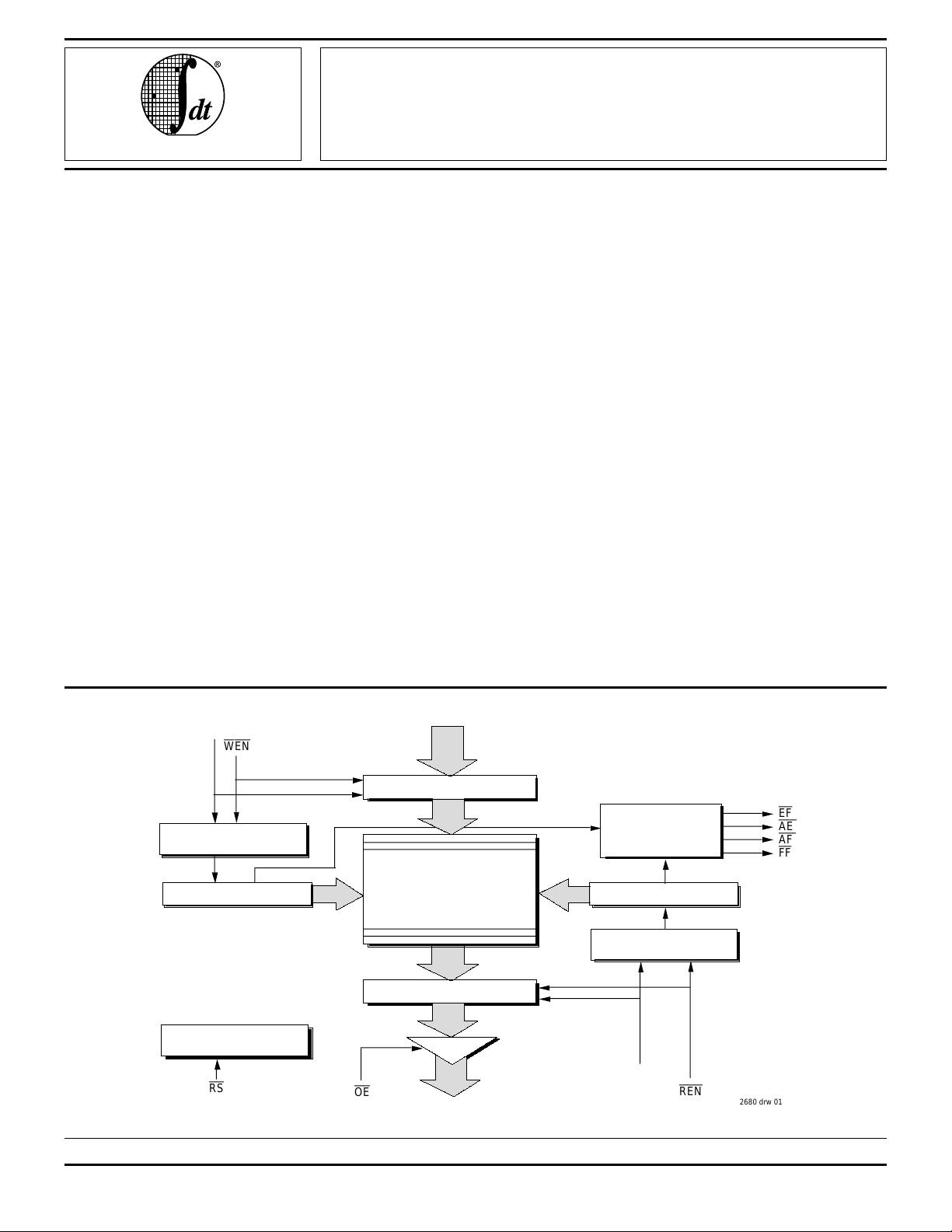

FUNCTIONAL BLOCK DIAGRAM

WCLK

WEN

•

•

WRITE CONTROL

LOGIC

WRITE POINTER

RESET LOGIC

RS

The IDT logo is a registered trademark and SyncFIFO is a trademark of Integrated Device Technology, Inc.

OE

D0 - D7

INPUT REGISTER

•

•

RAM ARRAY

64 x 8

256 x 8

512 x 8

•

•

OUTPUT REGISTER

Q0 - Q7

FLAG

LOGIC

READ POINTER

READ CONTROL

LOGIC

•

RCLK

REN

EF

AE

AF

FF

2680 drw 01

MILITARY AND COMMERCIAL TEMPERATURE RANGES NOVEMBER 1996

1996 Integrated Device Technology, Inc. DSC-2680/6

For latest information contact IDT's web site at www.idt.com or fax-on-demand at 408-492-8391.

5.12 1

IDT72420/72200/72210/72220/72230/72240 CMOS SyncFIFO

64 X 8, 256 X 8, 512 X 8, 1024 X 8, 2048 X 8 and 4096 X 8 MILITARY AND COMMERCIAL TEMPERATURE RANGES

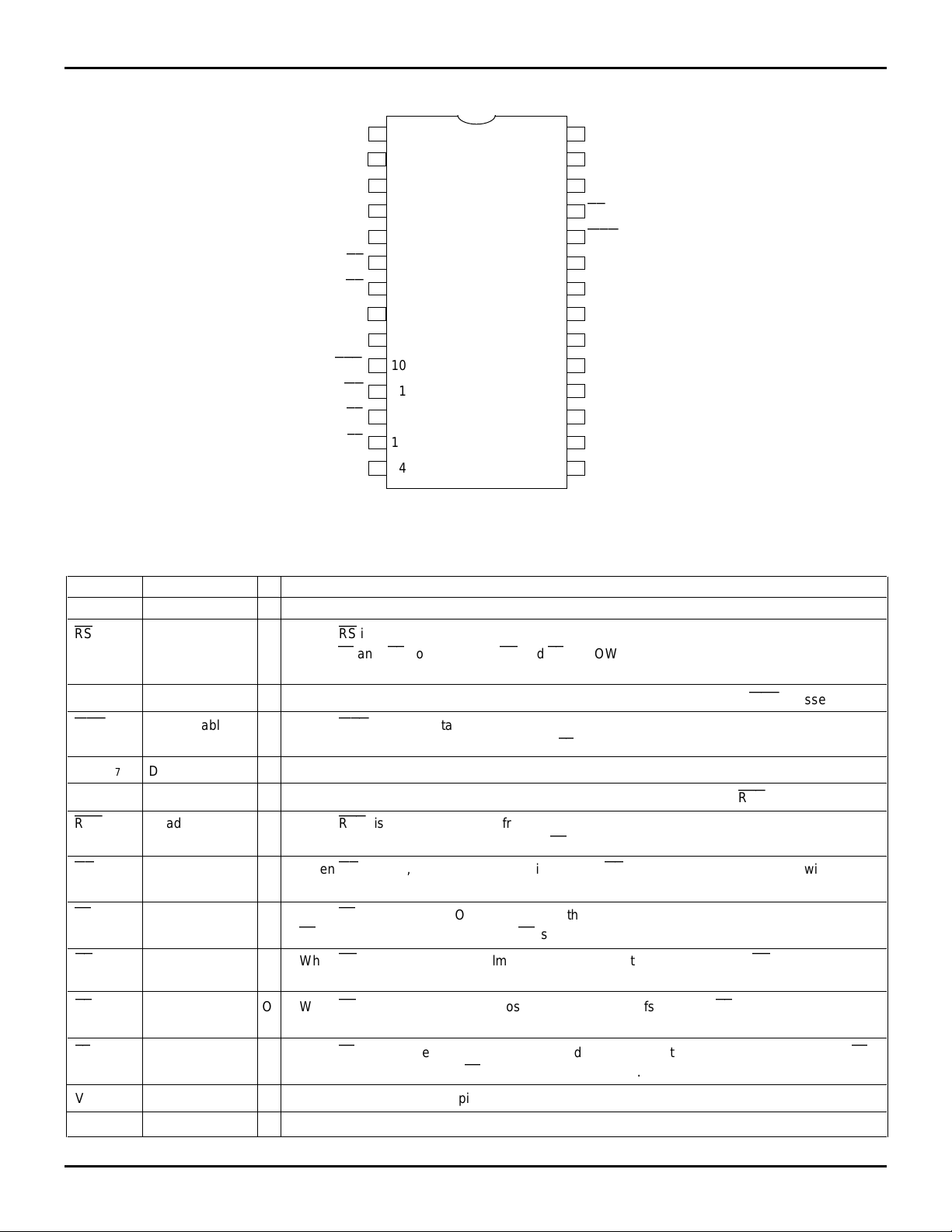

PIN CONFIGURATION

D4

D3

D2

D1

D0

AF

AE

GND

RCLK

REN

OE

EF

FF

Q0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

P28-2

C28-1

DIP TOP

VIEW

28

27

26

25

24

23

22

21

20

19

18

17

16

15

D5

D6

D7

RS

WEN

WCLK

VCC

Q7

Q6

Q5

Q4

Q3

Q2

Q1

2680 drw 02

PIN DESCRIPTIONS

Symbol Name I/O Description

D

0 - D7 Data Inputs I Data inputs for a 8-bit bus.

RS

WCLK Write Clock I Data is written into the FIFO on a LOW-to-HIGH transition of WCLK when

WEN

0 - Q7 Data Outputs O Data outputs for a 8-bit bus.

Q

RCLK Read Clock I Data is read from the FIFO on a LOW-to-HIGH transition of RCLK when

REN

OE

EF

AE

AF

FF

CC Power One +5 volt power supply pin.

V

GND Ground One 0 volt ground pin.

Reset I When RS is set LOW, internal read and write pointers are set to the first location of the RAM

array, FF and AF go HIGH, and AE and EF go LOW. A reset is required before an initial WRITE

after power-up.

Write Enable I When

WEN

is LOW, data is written into the FIFO on every LOW-to-HIGH transition of WCLK.

Data will not be written into the FIFO if the FF is LOW.

Read Enable I When

REN

is LOW, data is read from the FIFO on every LOW-to-HIGH transition of RCLK.

Data will not be read from the FIFO if the EF is LOW.

Output Enable I When OE is LOW, the data output bus is active. If OE is HIGH, the output data bus will be in a

high-impedance state.

Empty Flag O When EF is LOW, the FIFO is empty and further data reads from the output are inhibited. When

EF

is HIGH, the FIFO is not empty. EF is synchronized to RCLK.

Almost-Empty O When AE is LOW, the FIFO is almost empty based on the offset Empty+7. AE is synchronized

Flag to RCLK.

Almost-Full Flag O When AF is LOW, the FIFO is almost full based on the offset Full-7. AF is synchronized to

WCLK.

Full Flag O When FF is LOW, the FIFO is full and further data writes into the input are inhibited. When FF is

HIGH, the FIFO is not full. FF is synchronized to WCLK.

WEN

REN

is asserted.

is asserted.

2680 tbl 01

5.12 2

IDT72420/72200/72210/72220/72230/72240 CMOS SyncFIFO

64 X 8, 256 X 8, 512 X 8, 1024 X 8, 2048 X 8 and 4096 X 8 MILITARY AND COMMERCIAL TEMPERATURE RANGES

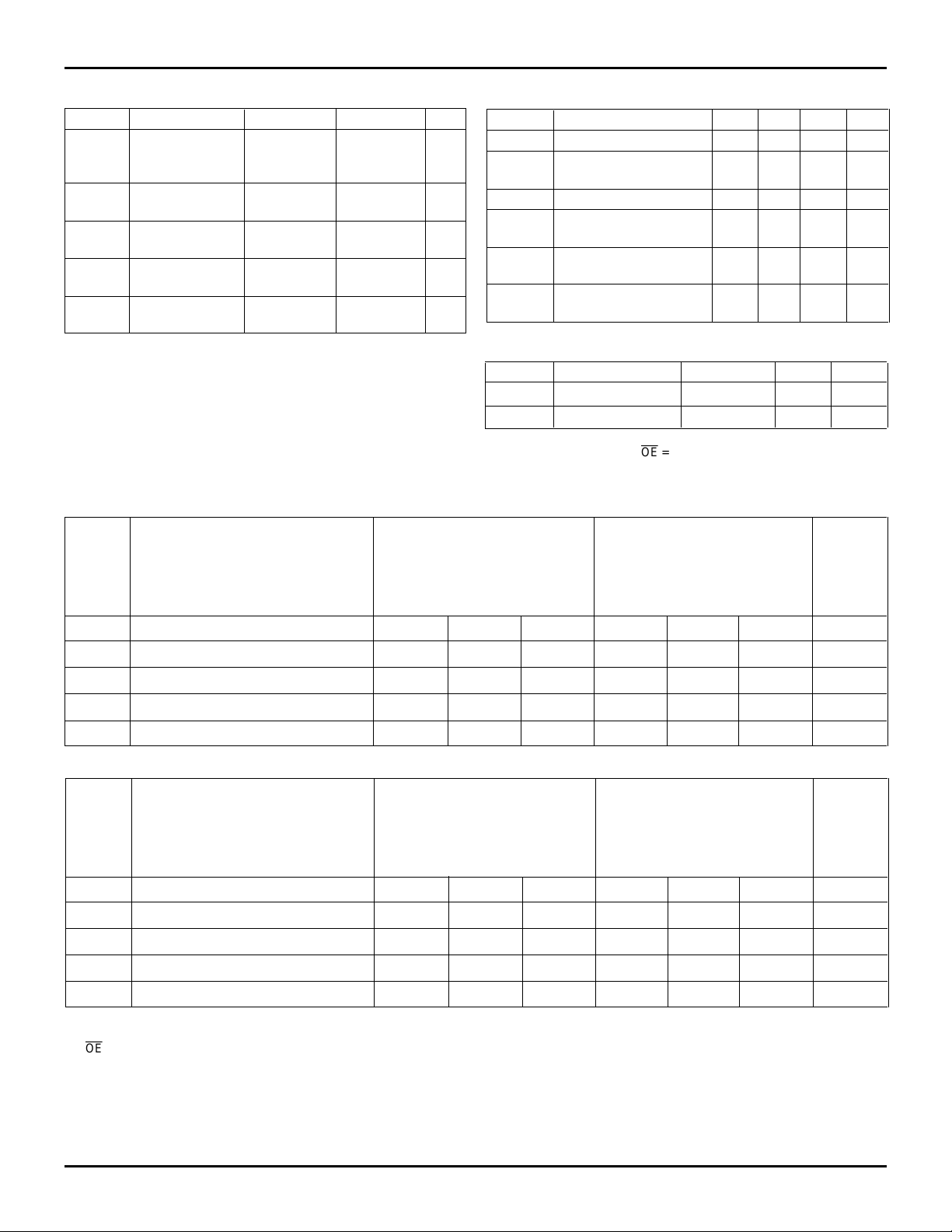

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Rating Commercial Military Unit

TERM Terminal Voltage –0.5 to + 7.0 –0.5 to + 7.0 V

V

with Respect to

GND

T

A Operating 0 to + 70 –55 to + 125 °C

Temperature

BIAS Temperature –55 to + 125 –65 to + 135 °C

T

Under Bias

T

STG Storage –55 to + 125 –65 to + 135 °C

Temperature

OUT DC Output 50 50 mA

I

Current

NOTE:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only

and functional operation of the device at these or any other conditions

above those indicated in the operational sections of this specification is

not implied. Exposure to absolute maximum rating conditions for extended

periods may affect reliability.

2680 tbl 02

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

CCM Military Supply Voltage 4.5 5.0 5.5 V

V

CCC Commercial Supply 4.5 5.0 5.5 V

V

Voltage

GND Supply Voltage 0 0 0 V

IH Input High Voltage 2.0 — — V

V

Commercial

V

IH Input High Voltage 2.2 — — V

Military

IL Input Low Voltage — — 0.8 V

V

Commercial & Military

CAPACITANCE (TA = +25°C, f = 1.0 MHz)

Symbol Parameter Conditions Max. Unit

(2)

IN Input Capacitance V IN = 0V 10 pF

C

(1, 2)

OUT Output Capacitance VOUT = 0V 10 pF

C

NOTES:

1. With output deselected. (OE = HIGH)

2. Characterized values, not currently tested.

DC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V ± 10%, TA = 0°C to +70°C; Military: VCC = 5V ± 10%, TA = –55°C to +125 °C)

IDT72420 IDT72420

IDT72200 IDT72200

IDT72210 IDT72210

CLK = 12, 15, 20, 25, 35, 50 ns tCLK = 20, 25,35, 50 ns

t

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Units

(1)

I

LI

I

LO

Input Leakage Current (any input) –1 — 1 –10 — 10 µA

(2)

Output Leakage Current –10 — 10 –10 — 10 µA

Commercial Military

2680 tbl 03

2680 tbl 04

OH Output Logic “1” Voltage, IOH = –2 mA 2.4 — — 2.4 — — V

V

V

OL Output Logic “0” Voltage, IOL = 8 mA — — 0.4 — — 0.4 V

(3)

CC1

I

Active Power Supply Current — — 80 — — 100 mA

IDT72220 IDT72220

IDT72230 IDT72230

IDT72240 IDT72240

Commercial Military

CLK = 15, 20, 25, 35, 50 ns tCLK = 25, 35, 50 ns

t

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Units

(1)

LI

I

I

LO

OH Output Logic “1” Voltage, IOH = –2 mA 2.4 — — 2.4 — — V

V

V

OL Output Logic “0” Voltage, IOL = 8 mA — — 0.4 — — 0.4 V

CC1

I

NOTES:

1. Measurements with 0.4 ≤ V

2.OE ≥ V

3 & 4. Measurements are made with outputs unloaded. Tested at f

Input Leakage Current (any input) –1 — 1 –10 — 10 µA

(2)

Output Leakage Current –10 — 10 –10 — 10 µA

(4)

Active Power Supply Current — — 80 — — 100 mA

IH, 0.4 ≤ VOUT ≤ VCC.

(3) Typical I

(4) Typical I

CLK = 1 / tCLK

f

CL = external capacitive load (30 pF typical)

CC1 = 30 + (fCLK*0.5/MHz) + (fCLK*CL*0.02/MHz-pF) mA

CC1 = 32 + (fCLK*0.6/MHz) + (fCLK*CL*0.02/MHz-pF) mA

IN ≤ VCC.

CLK = 20 MHZ.

2680 tbl 05

2680 tbl 06

5.12 3

IDT72420/72200/72210/72220/72230/72240 CMOS SyncFIFO

64 X 8, 256 X 8, 512 X 8, 1024 X 8, 2048 X 8 and 4096 X 8 MILITARY AND COMMERCIAL TEMPERATURE RANGES

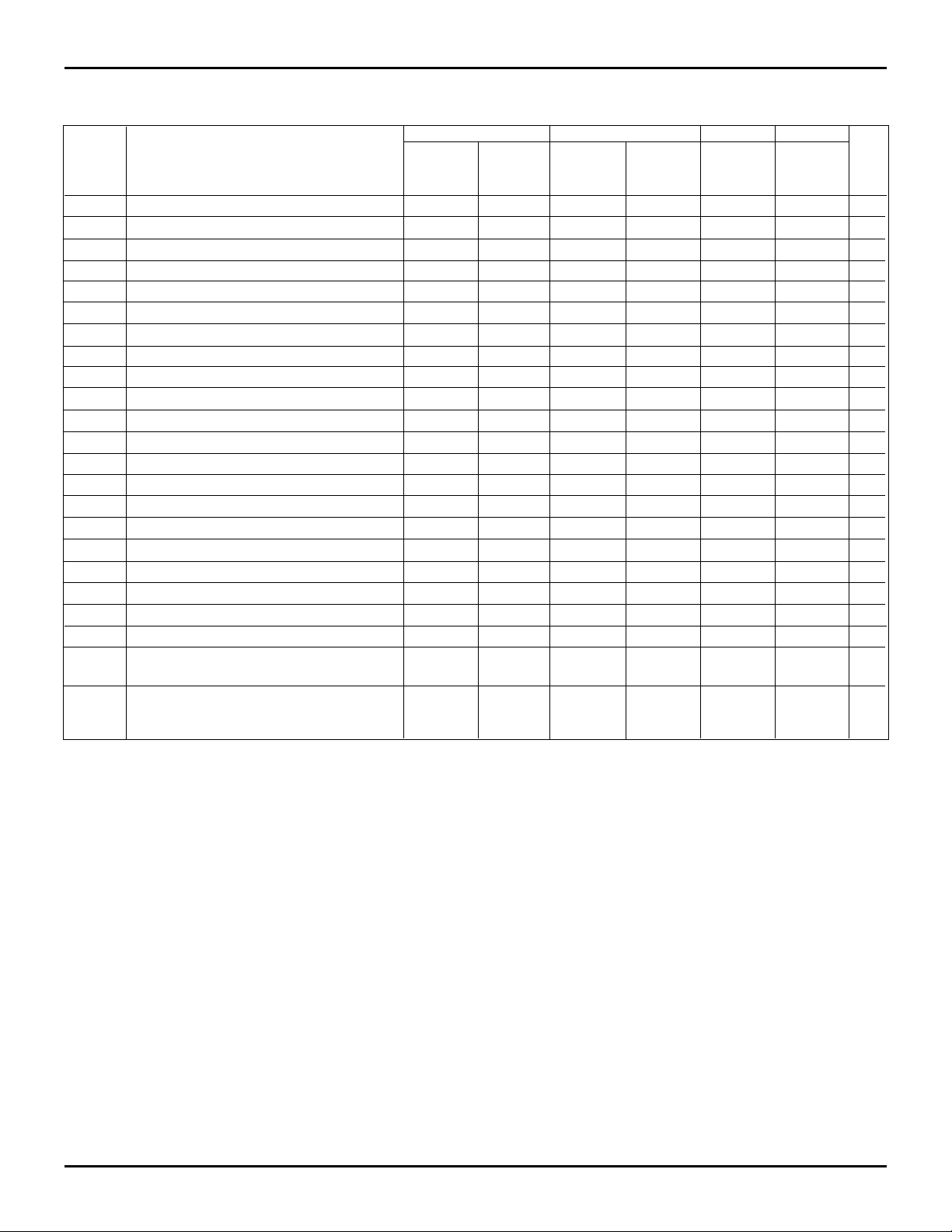

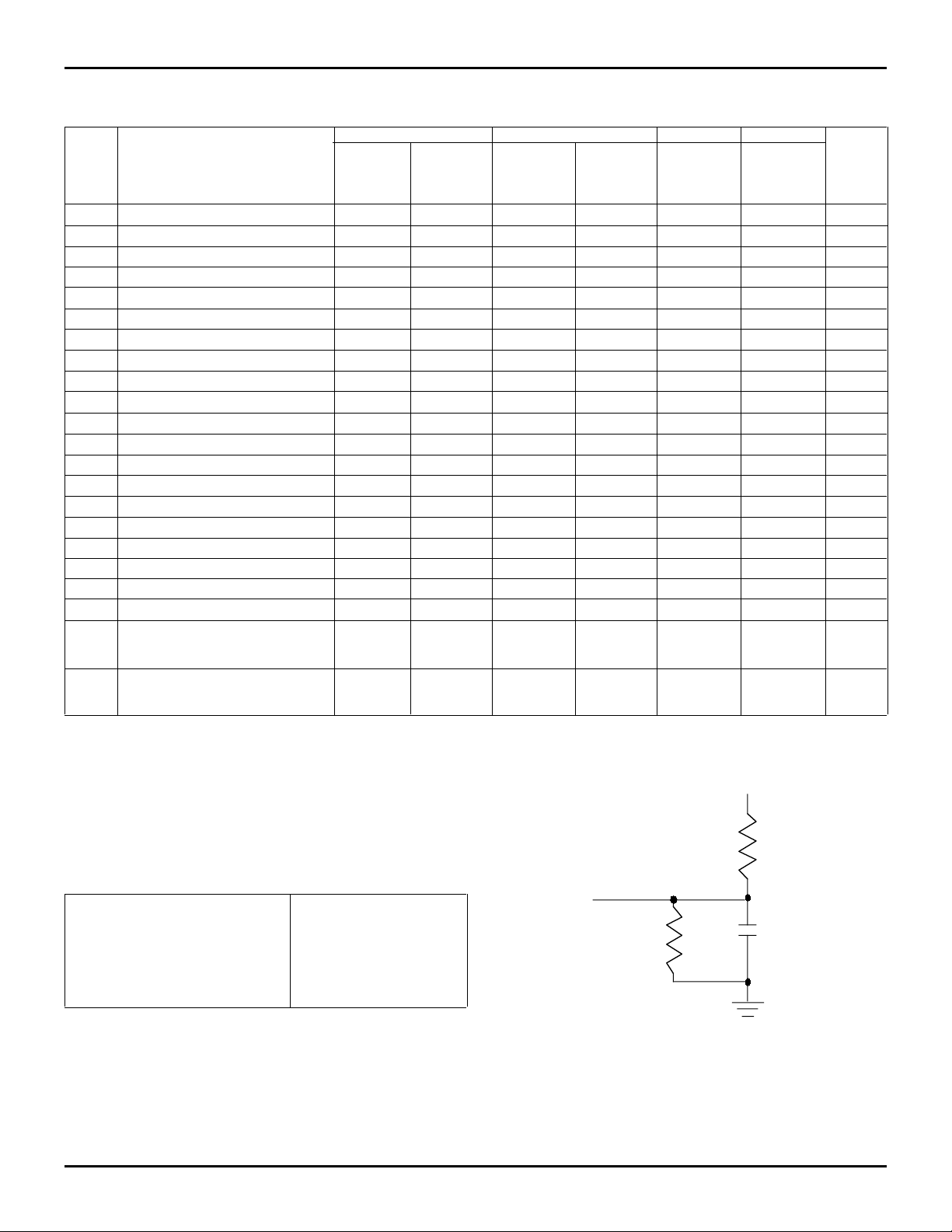

AC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V ± 10%, TA = 0°C to + 70°C; Military: VCC = 5V ± 10%, TA = –55°C to +125°C)

Commercial Comm. & Mil. Comm. Comm/Mil

72200L12 72200L15 72200L20 72200L25 72200L35 72200L50

72210L12 72210L15 72210L20 72210L25 72210L35 72210L50

72420L12 72420L15 72420L20 72420L25 72420L35 72420L50

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Min.Max. Unit

S Clock Cycle Frequency — 83.3 — 66.7 — 50 — 40 — 28.6 — 20 MHz

f

t

A Data Access Time 2 8 2 10 2 12 3 15 3 20 3 25 ns

t

CLK Clock Cycle Time 12 — 15 — 20 — 25 — 35 — 50 — ns

t

CLKH Clock High Time 5 — 6 — 8 — 10 — 14 — 20 — ns

t

CLKL Clock Low Time 5 — 6 — 8 — 10 — 14 — 20 — ns

t

DS Data Set-up Time 3 — 4 — 5 — 6 — 8 — 10 — ns

t

DH Data Hold Time 0.5 — 1 — 1 — 1 — 2 — 2 — ns

t

ENS Enable Set-up Time 3 — 4 — 5 — 6 — 8 — 10 — ns

t

ENH Enable Hold Time 0.5 — 1 — 1 — 1 — 2 — 2 — ns

t

RS Reset Pulse Width

t

RSS Reset Set-up Time 12 — 15 — 20 — 25 — 35 — 50 — ns

t

RSR Reset Recovery Time 12 — 15 — 20 — 25 — 35 — 50 — ns

t

RSF Reset to Flag and Output Time — 12 — 15 — 20 — 25 — 35 — 50 ns

t

OLZ Output Enable to Output in Low-Z

t

OE Output Enable to Output Valid 3 7 3 8 3 10 3 13 3 15 3 28 ns

t

OHZ Output Enable to Output in High-Z

t

WFF Write Clock to Full Flag — 8 — 10 — 12 — 15 — 20 — 30 ns

t

REF Read Clock to Empty Flag — 8 — 10 — 12 — 15 — 20 — 30 ns

t

AF Write Clock to Almost-Full Flag — 8 — 10 — 12 — 15 — 20 — 30 ns

t

AE Read Clock to Almost-Empty Flag — 8 — 10 — 12 — 15 — 20 — 30 ns

t

SKEW1 Skew time between Read Clock & 5 — 6 — 8 — 10 — 12 — 15 — ns

Write Clock for Empty Flag & Full Flag

t

SKEW2 Skew time between Read Clock & 22 — 28 — 35 — 40 — 42 — 45 — ns

Write Clock for Almost-Empty Flag &

Almost-Full Flag

NOTES: 2680 tbl 07

1. Pulse widths less than minimum values are not allowed.

2. Values guaranteed by design, not currently tested.

(1)

(2)

(2)

12 — 15 — 20 — 25 — 35 — 50 — ns

0— 0— 0 — 0— 0— 0— ns

3 7 3 8 3 10 3 13 3 15 3 28 ns

5.12 4

IDT72420/72200/72210/72220/72230/72240 CMOS SyncFIFO

64 X 8, 256 X 8, 512 X 8, 1024 X 8, 2048 X 8 and 4096 X 8 MILITARY AND COMMERCIAL TEMPERATURE RANGES

AC ELECTRICAL CHARACTERISTICS

(Commercial: VCC = 5V ± 10%, TA = 0°C to + 70°C; Military: VCC = 5V ± 10%, TA = –55°C to +125°C)

Commercial Commercial & Military Comm. Comm./Mil.

72220L12 72220L15 72220L20 72220L25 72220L35 72220L50

72230L12 72230L15 72230L20 72230L25 72230L35 72230L50

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

fS Clock Cycle Frequency — 83.3 — 66.7 — 50 — 40 — 28.6 — 20 MHz

tA Data Access Time 2 8 2 10 2 12 3 15 3 20 3 25 ns

tCLK Clock Cycle Time 12 — 15 — 20 — 25 — 35 — 50 — ns

tCLKH Clock High Time 5 — 6 — 8 — 10 — 1 4 — 20 — ns

tCLKL Clock Low Time 5 — 6 — 8 — 10 — 14 — 20 — ns

tDS Data Set-up Time 3 — 4 — 5 — 6 — 8 — 10 — ns

tDH Data Hold Time .5 — 1 — 1 — 1 — 2 — 2 — ns

tENS Enable Set-up Time 3 — 4 — 5 — 6 — 8 — 10 — ns

tENH Enable Hold Time .5 — 1 — 1 — 1 — 2 — 2 — ns

tRS Reset Pulse Width

tRSS Reset Set-up Time 12 — 15 — 20 — 25 — 35 — 50 — ns

tRSR Reset Recovery Time 12 — 15 — 20 — 25 — 35 — 50 — ns

tRSF Reset to Flag and Output Time — 12 — 15 — 20 — 25 — 35 — 50 ns

tOLZ Output Enable to Output in Low-Z

tOE Output Enable to Output Valid 3 7 3 8 3 10 3 13 3 15 3 23 ns

tOHZ Output Enable to Output in High-Z

tWFF Write Clock to Full Flag — 8 — 10 — 12 — 15 — 20 — 30 ns

tREF Read Clock to Empty Flag — 8 — 10 — 12 — 15 — 20 — 30 ns

tAF Write Clock to Almost-Full Flag — 8 — 10 — 12 — 15 — 20 — 3 0 ns

tAE Read Clock to Almost-Empty Flag — 8 — 10 — 12 — 15 — 20 — 30 ns

tSKEW1 Skew time between Read Clock 5 — 6 — 8 — 10 — 12 — 15 — ns

& Write Clock for Empty Flag &

Full Flag

tSKEW2 Skew time between Read Clock & 22 — 28 — 35 — 40 — 42 — 45 — ns

Write Clock for Almost-Empty Flag

& Almost-Full Flag

NOTES:

1. Pulse widths less than minimum values are not allowed.

2. Values guaranteed by design, not currently tested.

(1)

72240L12 72240L15 72240L20 72240L25 72240L35 72240L50

12 — 15 — 20 — 25 — 35 — 50 — ns

(2)

0—0—0—0—0—0— ns

(2)

3738310313315323ns

5V

2680 tbl 08

AC TEST CONDITIONS

Input Pulse Levels GND to 3.0V

Input Rise/Fall Times 3ns

Input Timing Reference Levels 1.5V

Output Reference Levels 1.5V

Output Load See Figure 1

1.1K

D.U.T.

30pF*

2680 drw 03

2680 tbl 09

680

Ω

or equivalent circuit

Figure 1. Output Load

*Includes jig and scope capacitances.

5.12 5

Ω

Loading...

Loading...