Integrated Device Technology Inc. IDT71T016 User Manual

W

查询IDT7203L120D供应商

CMOS ASYNCHRONOUS FIFO

2048 x 9, 4096 x 9,

8192 x 9 and 16384 x 9

Integrated Device Technology, Inc.

FEATURES:

• First-In/First-Out Dual-Port memory

• 2048 x 9 organization (IDT7203)

• 4096 x 9 organization (IDT7204)

• 8192 x 9 organization (IDT7205)

• 16384 x 9 organization (IDT7206)

• High-speed: 12ns access time

• Low power consumption

— Active: 770mW (max.)

— Power-down: 44mW (max.)

• Asynchronous and simultaneous read and write

• Fully expandable in both word depth and width

• Pin and functionally compatible with IDT720X family

• Status Flags: Empty, Half-Full, Full

• Retransmit capability

• High-performance CMOS technology

• Military product compliant to MIL-STD-883, Class B

• Standard Military Drawing for #5962-88669 (IDT7203),

5962-89567 (IDT7203), and 5962-89568 (IDT7204) are

listed on this function

• Industrial temperature range (-40

able, tested to military electrical specifications

.

o

C to +85oC) is avail-

IDT7203

IDT7204

IDT7205

IDT7206

DESCRIPTION:

The IDT7203/7204/7205/7206 are dual-port memory buffers with internal pointers that load and empty data on a firstin/first-out basis. The device uses Full and Empty flags to

prevent data overflow and underflow and expansion logic to

allow for unlimited expansion capability in both word size and

depth.

Data is toggled in and out of the device through the use of

the Write (W) and Read (R) pins.

The devices 9-bit width provides a bit for a control or parity

at the user’s option. It also features a Retransmit (RT) capability that allows the read pointer to be reset to its initial position

when RT is pulsed LOW. A Half-Full Flag is available in the

single device and width expansion modes.

The IDT7203/7204/7205/7206 are fabricated using IDT’s

high-speed CMOS technology. They are designed for applications requiring asynchronous and simultaneous read/writes

in multiprocessing, rate buffering, and other applications.

Military grade product is manufactured in compliance with

the latest revision of MIL-STD-883, Class B.

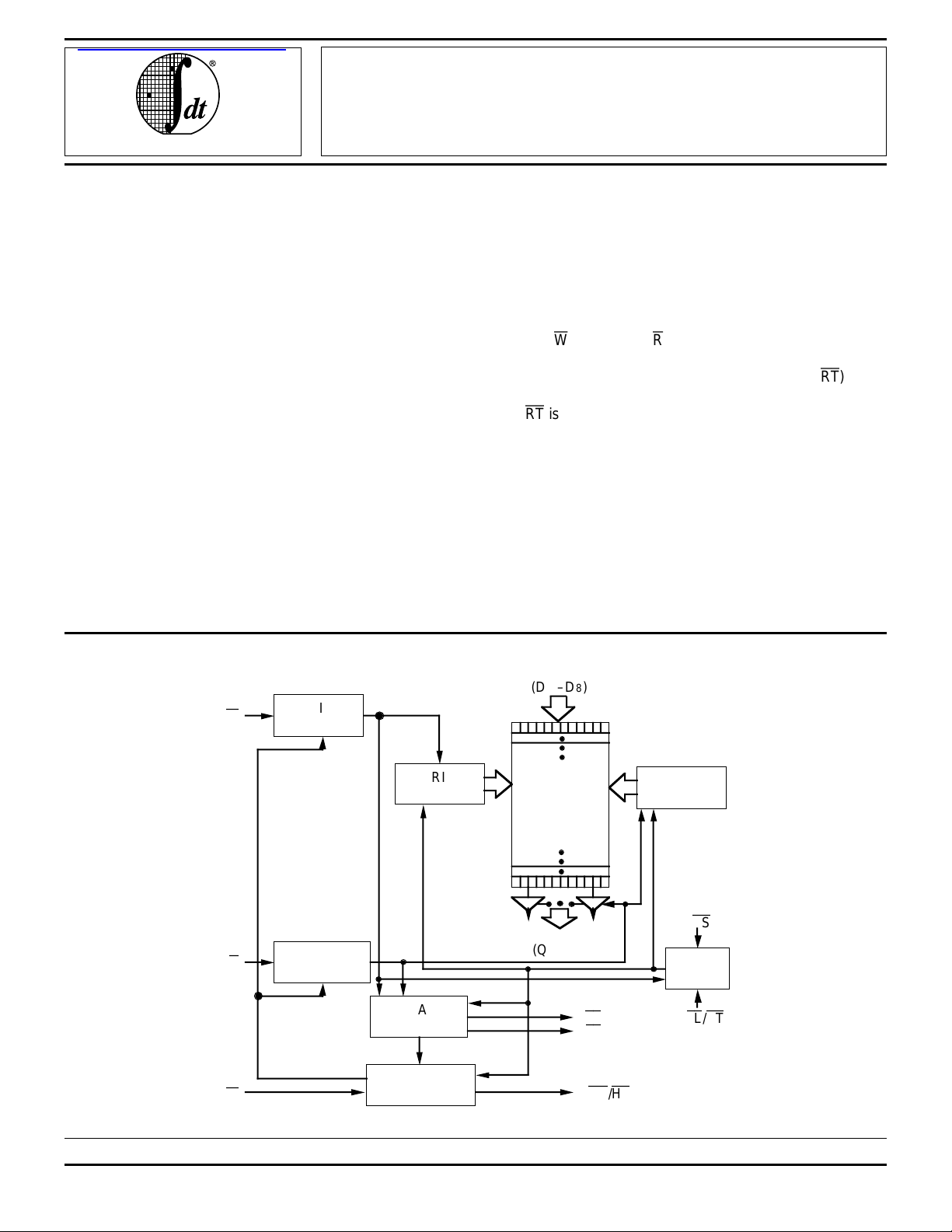

FUNCTIONAL BLOCK DIAGRAM

DATA INPUTS

0(D –D8)

WRITE

CONTROL

WRITE

POINTER

THREESTATE

BUFFERS

R

XI

READ

CONTROL

FLAG

LOGIC

EXPANSION

LOGIC

RAM ARRAY

2048 x 9

4096 x 9

8192 x 9

16384 x 9

DATA OUTPUTS

0(Q –Q8)

EF

FF

XO/HF

READ

POINTER

RS

RESET

LOGIC

FL/RT

2661 drw 01

The IDT logo is a registered trademark of Integrated Device Techology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES DECEMBER 1996

1996 Integrated Device Technology, Inc. DSC-2661/9

For latest information contact IDT's web site at www.idt.com or fax-on-demand at 408-492-8391.

5.04 1

IDT7203/7204/7205/7206 CMOS ASYNCHRONOUS FIFO

2048 x 9, 4096 x 9, 8192 x 9 and 16384 x 9 MILITARY AND COMMERCIAL TEMPERATURE RANGES

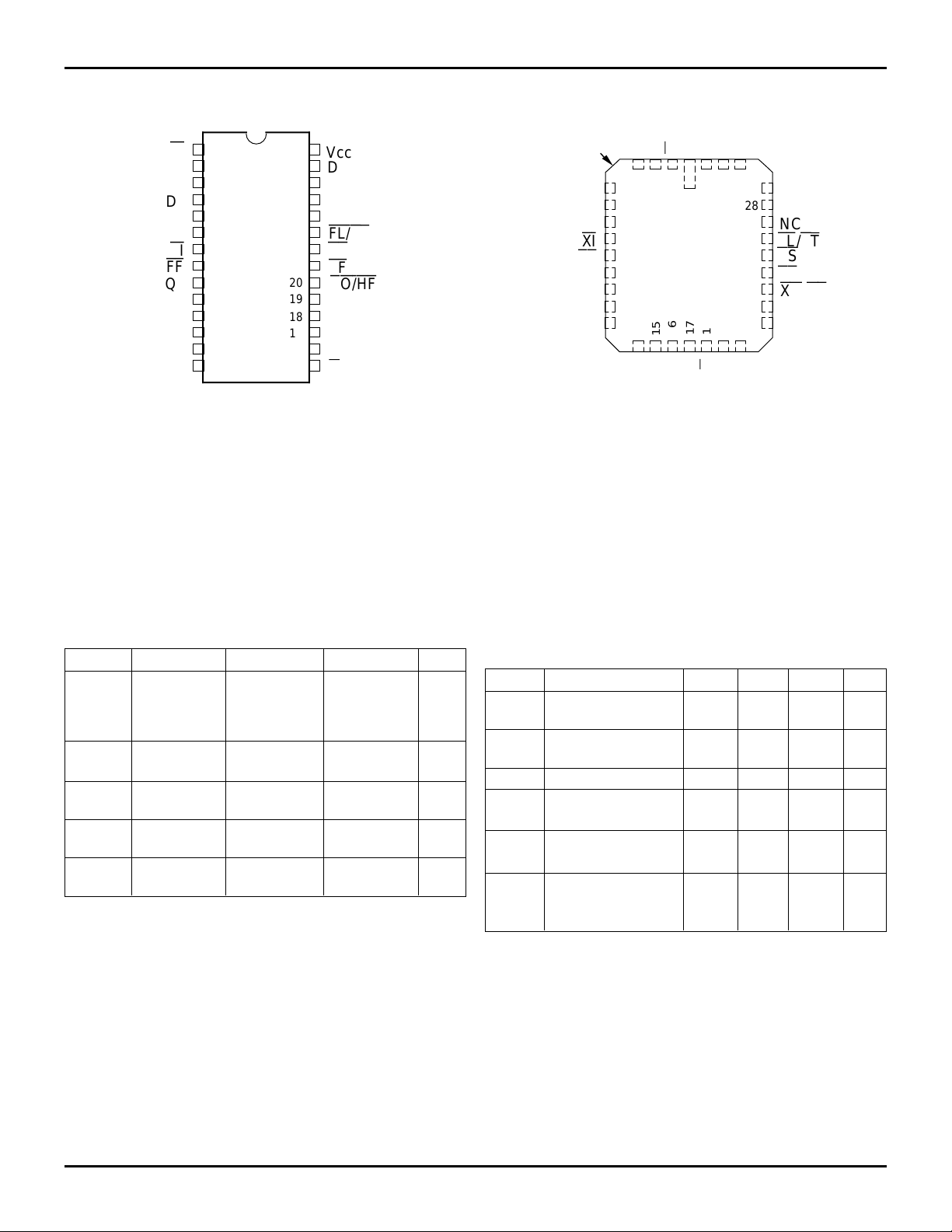

PIN CONFIGURATIONS

W

D

D

D

D

D

XI

FF

Q

Q

Q

Q

Q

GND

1

2

8

3

3

4

2

1

0

0

1

2

3

8

5

6

7

8

9

10

11

12

13

14

P28-1

P28-2

D28-1

D28-3

SO28-3

28

27

26

25

24

23

22

21

20

19

18

17

16

15

2661 drw 02a

Vcc

D

4

D

5

6

D

D

7

FL/RT

RS

EF

XO/HF

Q

7

6

Q

5

Q

Q

4

R

DIP

TOP VIEW

NOTES:

1. The THINDIPs P28-2 and D28-3 are only available for the 7203/7204/

7205.

2. The small outline package SO28-3 is only available for the 7204.

3. Consult factory for CERPACK pinout.

INDEX

2

D

D

1

0

D

XI

FF

Q

0

1

Q

NC

Q

2

8

D3D

432

5

6

7

8

9

10

11

12

13

1415161718

3

8

Q

Q

PLCC/LCC

TOP VIEW

NC

W

1

J32-1

&

L32-1

GND

NC

Vcc

32

R

4

D

31

19

Q

4

5

D

30

29

28

27

26

25

24

23

22

21

20

5

Q

2661 drw 02b

D

6

D

7

NC

FL/RT

RS

EF

XO/HF

Q

7

Q

6

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Rating Commercial Military Unit

V

TERM Terminal –0.5 to + 7.0 –0.5 to +7.0 V

Voltage with

Respect to

GND

T

A Operating 0 to +70 –55 to +125 ° C

Temperature

T

BIAS Temperature –55 to +125 –65 to +135 ° C

Under Bias

T

STG Storage –55 to + 125 –65 to +155 ° C

Temperature

I

OUT DC Output 50 50 mA

Current

NOTE: 2661 tbl 01

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions

above those indicated in the operational sections of this specification is not

implied. Exposure to absolute maximum rating conditions for extended

periods may affect reliability.

RECOMMENDED DC OPERATING

CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

V

CCM Military Supply 4.5 5.0 5.5 V

Voltage

CCC Commercial Supply 4.5 5.0 5.5 V

V

Voltage

GND Supply Voltage 0 0 0 V

(1)

V

IH

V

IH

V

IL

NOTE: 2661 tbl 02

1. 1.5V undershoots are allowed for 10ns once per cycle.

Input High Voltage 2.0 — — V

Commercial

(1)

Input High Voltage 2.2 — — V

Military

(1)

Input Low Voltage — — 0.8 V

Commercial and

Military

5.04 2

IDT7203/7204/7205/7206 CMOS ASYNCHRONOUS FIFO

2048 x 9, 4096 x 9, 8192 x 9 and 16384 x 9 MILITARY AND COMMERCIAL TEMPERATURE RANGES

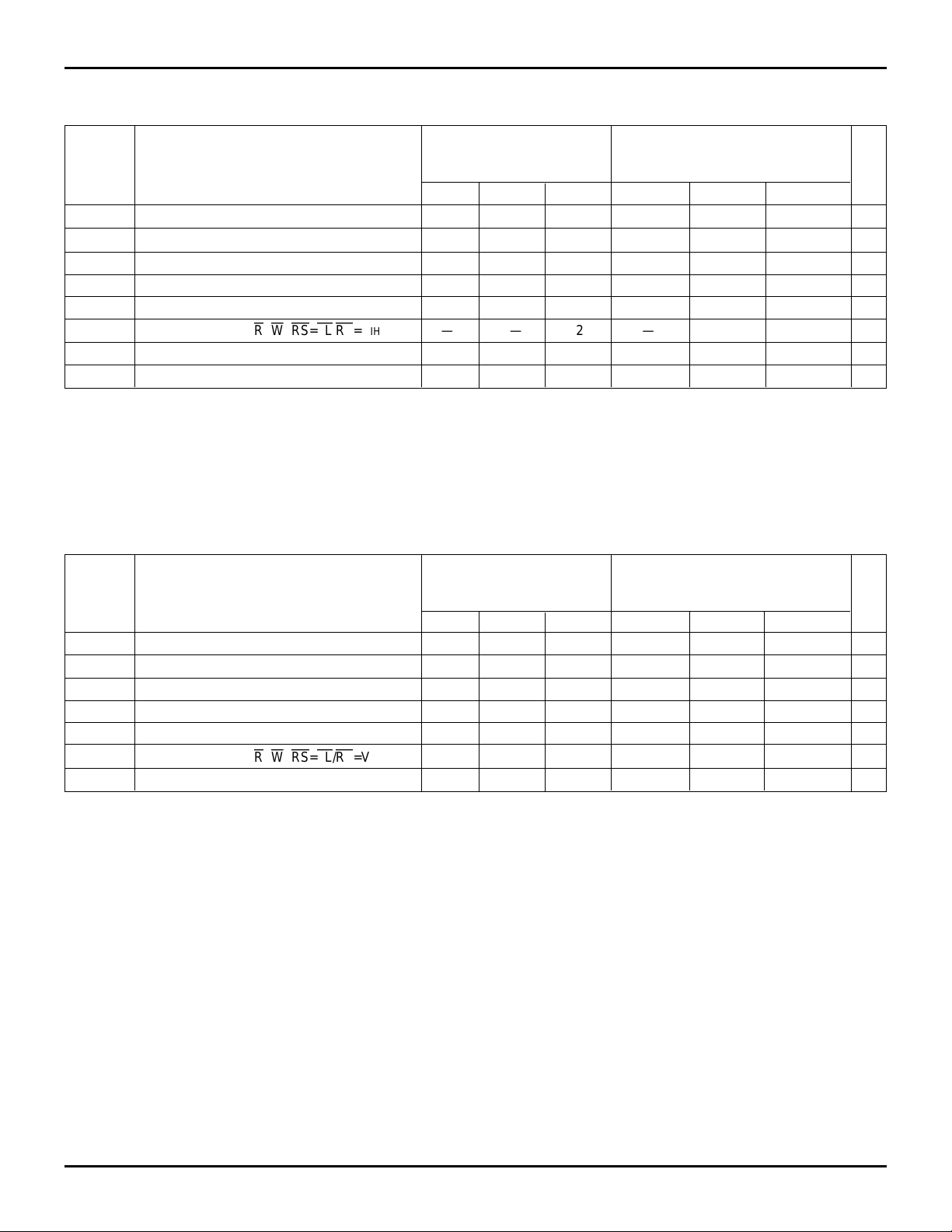

DC ELECTRICAL CHARACTERISTICS FOR THE 7203 AND 7204

(Commercial: VCC = 5.0V±10%, TA = 0°C to +70°C; Military: VCC = 5.0V±10%, TA = –55°C to +125°C)

IDT7203/7204 IDT7203/7204

Commercial Military

tA = 12, 15, 20, 25, 35, 50 ns tA = 20, 30, 40, 50, 65, 80, 120 ns

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Unit

(2)

LI

I

(3)

LO

I

OH Output Logic “1” Voltage IOH = –2mA 2.4 — — 2.4 — — V

V

OL Output Logic “0” Voltage IOL = 8mA — — 0.4 — — 0.4 V

V

(4)

CC1

I

(4)

CC2

I

CC3(L)

I

CC3(S)

I

NOTES: 2661 tbl 03

1. Speed grades 65, 80, and 120ns are only available in the ceramic DIP.

2. Measurements with 0.4 ≤ V

3. R ≥ V

CC measurements are made with outputs open (only capacitive loading).

4. I

5. Tested at f = 20MHz.

Input Leakage Current (Any Input) –1 — 1 –1 — 1 µA

Output Leakage Current –10 — 10 –10 — 10 µA

Active Power Supply Current — — 120

(5)

— — 150

Standby Current (R=W=RS=FL/RT=VIH)——12— —25mA

(4)

Power Down Current (All Input = VCC - 0.2V) — — 2 — — 4 mA

(4)

Power Down Current (All Input = VCC - 0.2V) — — 8 — — 12 mA

IH, 0.4 ≤ VOUT ≤ VCC.

IN ≤ VCC.

(1)

(5)

mA

DC ELECTRICAL CHARACTERISTICS FOR THE 7205 AND 7206

(Commercial: VCC = 5.0V±10%, TA = 0°C to +70°C; Military: VCC = 5.0V±10%, TA = –55°C to +125°C)

IDT7205/7206 IDT7205/7206

Commercial Military

t

A = 15, 20, 25, 35, 50 ns tA = 20, 30, 50 ns

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Unit

(1)

LI

I

(2)

LO

I

OH Output Logic “1” Voltage IOH = –2mA 2.4 — — 2.4 — — V

V

OL Output Logic “0” Voltage IOL = 8mA — — 0.4 — — 0.4 V

V

(3)

CC1

I

(3)

CC2

I

CC3(L)

I

NOTES: 2661 tbl 04

1. Measurements with 0.4 ≤ VIN ≤ VCC.

2. R ≥ V

CC measurements are made with outputs open (only capacitive loading).

3. I

4. Tested at f = 20MHz.

Input Leakage Current (Any Input) –1 — 1 –1 — 1 µA

Output Leakage Current –10 — 10 –10 — 10 µA

Active Power Supply Current — — 120

(4)

— — 150

(4)

Standby Current (R=W=RS=FL/RT=VIH)——12— —25mA

(3)

Power Down Current (All Input = VCC - 0.2V) — — 8 — — 12 mA

IH, 0.4 ≤ VOUT ≤ VCC.

mA

5.04 3

IDT7203/7204/7205/7206 CMOS ASYNCHRONOUS FIFO

2048 x 9, 4096 x 9, 8192 x 9 and 16384 x 9 MILITARY AND COMMERCIAL TEMPERATURE RANGES

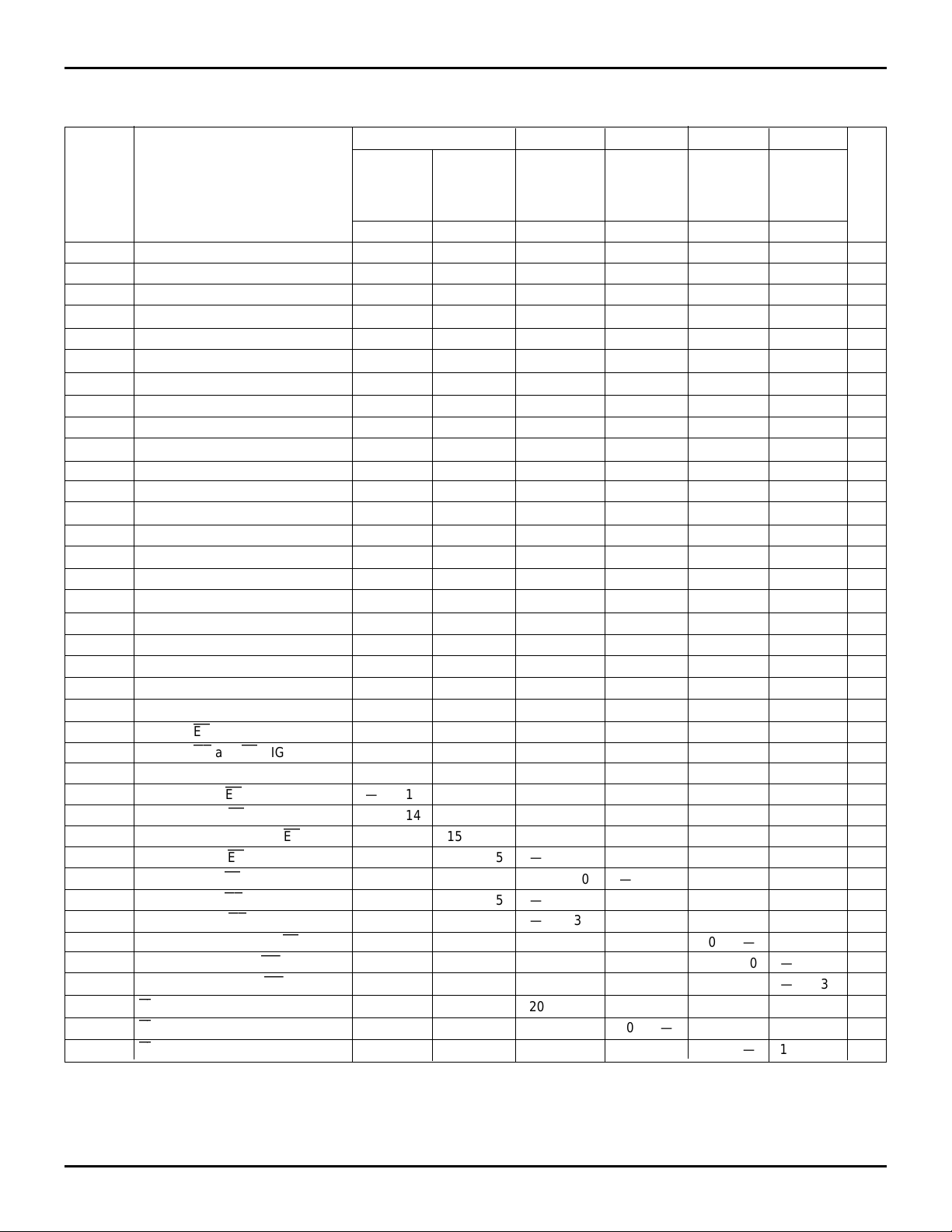

AC ELECTRICAL CHARACTERISTICS

(1)

(Commercial: VCC = 5V ± 10%, TA = 0°C to +70°C; Military: VCC = 5V ± 10%, TA = –55°C to +125°C)

Commercial Com'l & Mil. Com'l Military Com'l

7203S/L12 7203S/L15 7203S/L20 7203S/L25 7203S/L30 7203S/L35

7204S/L12 7204S/L15 7204S/L20 7204S/L25 7204S/L30 7204S/L35

7205L15 7205L20 7205L25 7205L30 7205L35

7206L15 7206L20 7206L25 7206L30 7206L35

Symbol Parameters Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

f

S Shift Frequency — 50 — 40 — 33.3 — 28.5 — 25 — 22.2 MHz

RC Read Cycle Time 20 — 25 — 30 — 35 — 40 — 45 — ns

t

A Access Time — 12 — 15 — 20 — 25 — 30 — 35 ns

t

t

RR Read Recovery Time 8 — 10 — 10 — 10 — 10 — 10 — ns

RPW Read Pulse Width

t

t

RLZ Read LOW to Data Bus LOW

WLZ Write HIGH to Data Bus Low-Z

t

t

DV Data Valid from Read HIGH 5 — 5 — 5 — 5 — 5 — 5 — ns

RHZ Read HIGH to Data Bus High-Z

t

t

WC Write Cycle Time 20 — 25 — 30 — 35 — 40 — 45 — ns

WPW Write Pulse Width

t

t

WR Write Recovery Time 8 — 10 — 10 — 10 — 10 — 10 — ns

DS Data Set-up Time 9 — 11 — 12 — 15 — 18 — 18 — ns

t

DH Data Hold Time 0 — 0 — 0 — 0 — 0 — 0 — ns

t

t

RSC Reset Cycle Time 20 — 25 — 30 — 35 — 40 — 45 — ns

RS Reset Pulse Width

t

t

RSS Reset Set-up Time

t

RTR Reset Recovery Time 8 — 10 — 10 — 10 — 10 — 10 — ns

RTC Retransmit Cycle Time 20 — 25 — 30 — 35 — 40 — 45 — ns

t

RT Retransmit Pulse Width

t

RTS Retransmit Set-up Time

t

t

RSR Retransmit Recovery Time 8 — 10 — 10 — 10 — 10 — 10 — ns

t

EFL Reset to

HFH, tFFH Reset to

t

RTF Retransmit LOW to Flags Valid — 20 — 25 — 30 — 35 — 40 — 45 ns

t

t

REF Read LOW to

RFF Read HIGH to

t

t

RPE Read Pulse Width after

WEF Write HIGH to

t

t

WFF Write LOW to

WHF Write LOW to

t

RHF Read HIGH to

t

t

WPF Write Pulse Width after

XOL Read/Write LOW to

t

t

XOH Read/Write HIGH to

XI

t

t

XIR

t

XIS

NOTES: 2661 tbl 05

1. Timings referenced as in AC Test Conditions.

2. Pulse widths less than minimum are not allowed.

3. Values guaranteed by design, not currently tested.

4. Only applies to read data flow-through mode.

XI

XI

XI

EF

HF

Pulse Width

Recovery Time 8 — 10 — 10 — 10 — 10 — 10 — ns

Set-up Time 8 — 10 — 10 — 10 — 10 — 15 — ns

(2)

(3)

(2)

(2)

(3)

(2)

(3)

12 — 15 — 20 — 25 — 30 — 35 — ns

3—5—5 — 5—5—5—ns

(3, 4)

3—5—5 — 5—5—10—ns

(3)

— 12 — 15 — 15 — 18 — 20 — 20 ns

12 — 15 — 20 — 25 — 30 — 35 — ns

12 — 15 — 20 — 25 — 30 — 35 — ns

12 — 15 — 20 — 25 — 30 — 35 — ns

12 — 15 — 20 — 25 — 30 — 35 — ns

12 — 15 — 20 — 25 — 30 — 35 — ns

LOW — 12 — 25 — 30 — 35 — 40 — 45 ns

and FF HIGH — 17 — 25 — 30 — 35 — 40 — 45 ns

EF

LOW — 12 — 15 — 20 — 25 — 30 — 30 ns

FF

HIGH — 14 — 15 — 20 — 25 — 30 — 30 ns

EF

HIGH 12 — 15 — 20 — 25 — 30 — 35 — ns

EF

HIGH — 12 — 15 — 20 — 25 — 30 — 30 ns

FF

LOW — 14 — 15 — 20 — 25 — 30 — 30 ns

HF

Flag LOW — 17 — 25 — 30 — 35 — 40 — 45 ns

HF

Flag HIGH — 17 — 25 — 30 — 35 — 40 — 45 ns

FF

HIGH 12 — 15 — 20 — 25 — 30 — 35 — ns

XO

LOW — 12 — 15 — 20 — 25 — 30 — 35 ns

XO

HIGH — 12 — 15 — 20 — 25 — 30 — 35 ns

(2)

12 — 15 — 20 — 25 — 30 — 35 — ns

5.04 4

IDT7203/7204/7205/7206 CMOS ASYNCHRONOUS FIFO

2048 x 9, 4096 x 9, 8192 x 9 and 16384 x 9 MILITARY AND COMMERCIAL TEMPERATURE RANGES

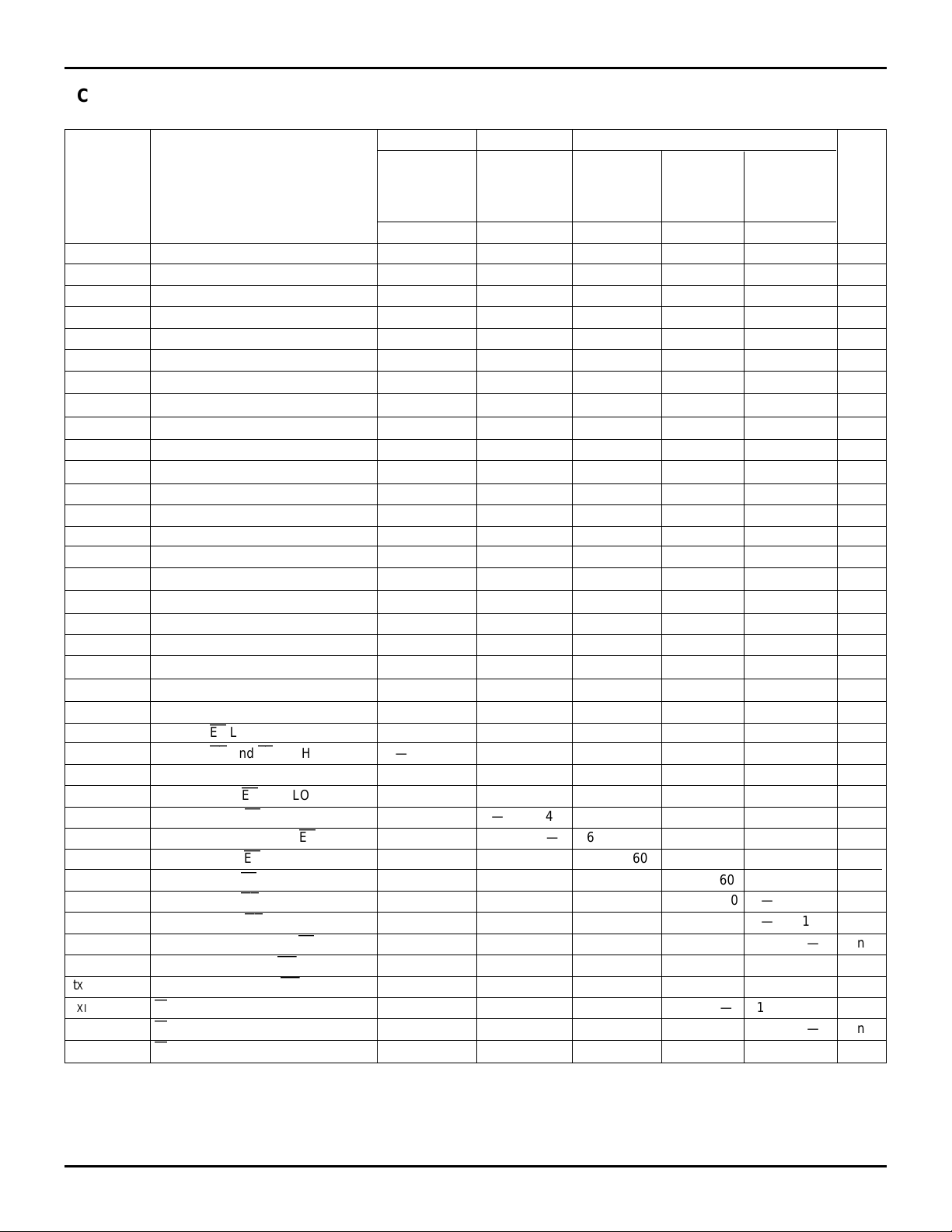

AC ELECTRICAL CHARACTERISTICS

(1)

(Continued)

(Commercial: VCC = 5V ± 10%, TA = 0°C to +70°C; Military: VCC = 5V ± 10%, TA = –55°C to +125°C)

Military Com'l & Mil. Military

7203S/L40 7203S/L50 7203S/L65 7203S/L80 7203S/L120

7204S/L40 7204S/L50 7204S/L65 7204S/L80 7204S/L120

7205L50

7206L50

Symbol Parameters Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

f

S Shift Frequency — 20 — 15 — 12.5 — 10 — 7 MHz

RC Read Cycle Time 50 — 65 — 80 — 100 — 140 — ns

t

t

A Access Time — 40 — 50 — 65 — 80 — 120 ns

RR Read Recovery Time 10 — 15 — 15 — 20 — 20 — ns

t

RPW Read Pulse Width

t

t

RLZ Read LOW to Data Bus LOW

WLZ Write HIGH to Data Bus Low-Z

t

t

DV Data Valid from Read HIGH 5 — 5 — 5 — 5 — 5 — ns

RHZ Read HIGH to Data Bus High-Z

t

t

WC Write Cycle Time 50 — 65 — 80 — 100 — 140 — ns

WPW Write Pulse Width

t

t

WR Write Recovery Time 10 — 15 — 15 — 20 — 20 — ns

DS Data Set-up Time 20 — 30 — 30 — 40 — 40 — ns

t

DH Data Hold Time 0 — 5 — 10 — 10 — 10 — ns

t

t

RSC Reset Cycle Time 50 — 65 — 80 — 100 — 140 — ns

RS Reset Pulse Width

t

t

RSS Reset Set-up Time

t

RSR Reset Recovery Time 10 — 15 — 15 — 20 — 20 — ns

RTC Retransmit Cycle Time 50 — 65 — 80 — 100 — 140 — ns

t

RT Retransmit Pulse Width

t

RTS Retransmit Set-up Time

t

t

RSR Retransmit Recovery Time 10 — 15 — 15 — 20 — 20 — ns

t

EFL Reset to

HFH, tFFH Reset to

t

t

RTF Retransmit LOW to Flags Valid — 50 — 65 — 80 — 100 — 140 ns

REF Read LOW to

t

RFF Read HIGH to

t

t

RPE Read Pulse Width after

WEF Write HIGH to

t

t

WFF Write LOW to

WHF Write LOW to

t

RHF Read HIGH to

t

t

WPF Write Pulse Width after

XOL Read/Write LOW to

t

t

XOH Read/Write HIGH to

XI

t

t

XIR

t

XIS

NOTES: 2661 tbl 06

1. Timings referenced as in AC Test Conditions.

2. Speed grades 65, 80, and 120ns are only available in the ceramic DIP.

3. Pulse widths less than minimum are not allowed.

4. Values guaranteed by design, not currently tested.

5. Only applies to read data flow-through mode.

XI

XI

XI

EF

HF

Pulse Width

Recovery Time 10 — 10 — 10 — 10 — 10 — ns

Set-up Time 15 — 15 — 15 — 15 — 15 — ns

(3)

(4)

(4, 5)

(4)

(3)

(3)

(4)

(3)

(4)

40 — 50 — 65 — 80 — 120 — ns

5 — 10 — 10 — 10 — 10 — ns

10 — 15 — 15 — 20 — 20 — ns

— 25 — 30 — 30 — 30 — 35 ns

40 — 50 — 65 — 80 — 120 — ns

40 — 50 — 65 — 80 — 120 — ns

40 — 50 — 65 — 80 — 120 — ns

40 — 50 — 65 — 80 — 120 — ns

40 — 50 — 65 — 80 — 120 — ns

LOW — 50 — 65 — 80 — 100 — 140 ns

and FF HIGH — 50 — 65 — 80 — 100 — 140 ns

EF

Flag LOW — 35 — 45 — 60 — 60 — 60 ns

FF

HIGH — 35 — 45 — 60 — 60 — 60 ns

EF

HIGH 40 — 50 — 65 — 80 — 120 — ns

EF

HIGH — 35 — 45 — 60 — 60 — 60 ns

FF

LOW — 35 — 45 — 60 — 60 — 60 ns

HF

LOW — 50 — 65 — 80 — 100 — 140 ns

HF

HIGH — 50 — 65 — 80 — 100 — 140 ns

FF

HIGH 40 — 50 — 65 — 80 — 120 — ns

XO

LOW — 40 — 50 — 65 — 80 — 120 ns

XO

HIGH — 40 — 50 — 65 — 80 — 120 ns

(3)

40 — 50 — 65 — 80 — 120 — ns

(2)

5.04 5

Loading...

Loading...