Integrated Device Technology Inc IDT71B74S12TP, IDT71B74S12Y, IDT71B74S15TP, IDT71B74S15Y, IDT71B74S20TP Datasheet

...

Integrated Device Technology, Inc.

BiCMOS STATIC RAM

64K (8K x 8-BIT)

CACHE-TAG RAM

IDT71B74

FEATURES:

• High-speed address to MATCH comparison time

— Commercial: 8/10/12/15/20ns (max.)

• High-speed address access time

— Commercial: 8/10/12/15/20ns (max.)

• High-speed chip select access time

— Commercial: 6/7/8/10ns (max.)

• Power-ON Reset Capability

• Low power consumption

— 830mW (typ.) for 12ns parts

— 880mW (typ.) for 10ns parts

— 920mW (typ.) for 8ns parts

• Produced with advanced BiCMOS high-performance

technology

• Input and output directly TTL-compatible

• Standard 28-pin plastic DIP and 28-pin SOJ (300 mil)

DESCRIPTION:

The IDT71B74 is a high-speed cache address comparator

subsystem consisting of a 65,536-bit static RAM organized as

8K x 8 and an 8-bit comparator. A single IDT71B74 can map

8K cache words into a 2 megabyte address space by using the

21 bits of address organized with the 13 LSBs for the cache

address bits and the 8 higher bits for cache data bits. Two

IDT71B74s can be combined to provide 29 bits of address

comparison, etc. The IDT71B74 also provides a single RAM

clear control, which clears all words in the internal RAM to zero

when activated. This allows the tag bits for all locations to be

cleared at power-on or system-reset, a requirement for cache

comparator systems. The IDT71B74 can also be used as a

resettable 8K x 8 high-speed static RAM.

The IDT71B74 is fabricated using IDT’s high-performance,

high-reliability BiCMOS technology. Address access times as

fast as 8ns, chip select times of 6ns and address-to-match

times of 8ns are available.

The MATCH pin of several IDT71B74s can be wired-ORed

together to provide enabling or acknowledging signals to the

data cache or processor, thus eliminating logic delays and

increasing system throughput.

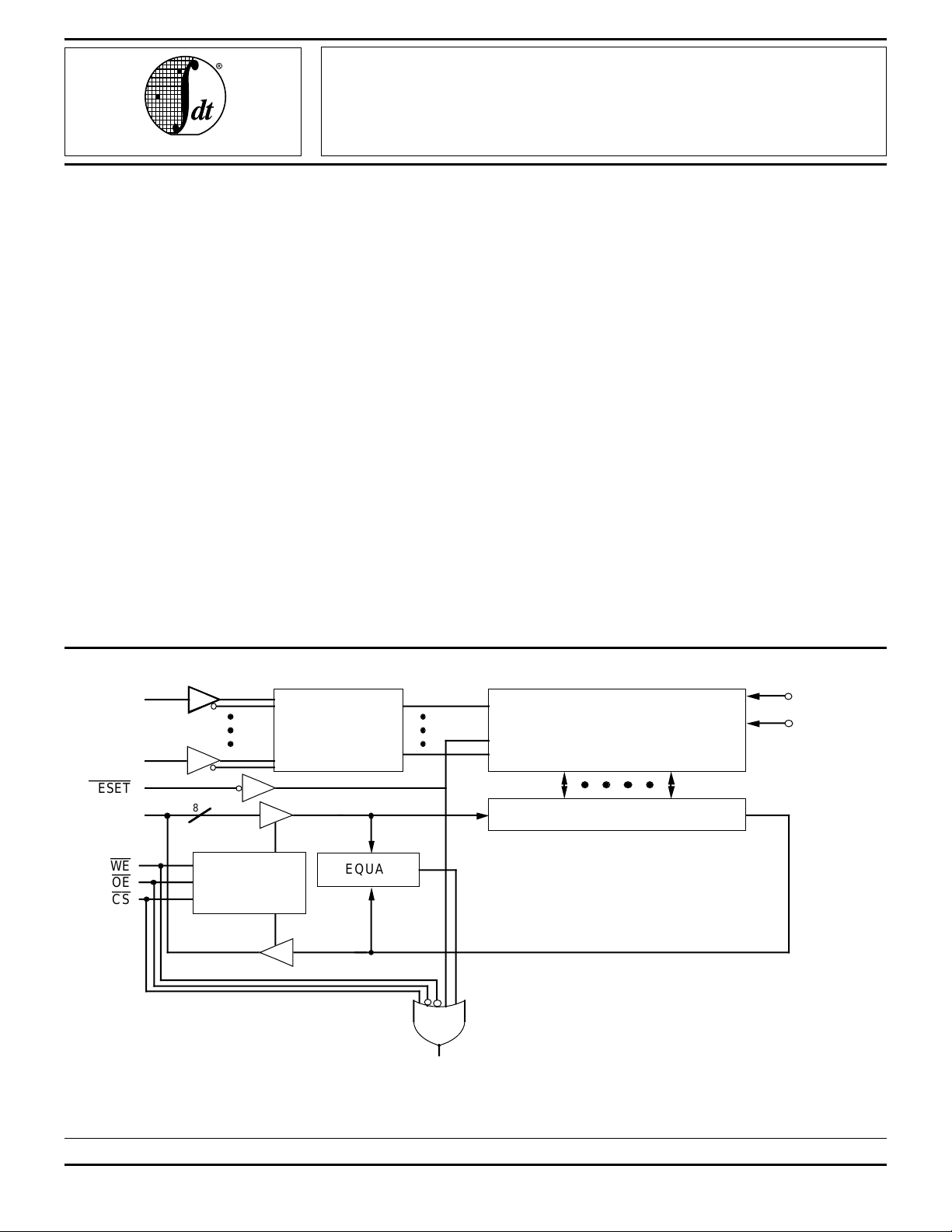

FUNCTIONAL BLOCK DIAGRAM

A0

ADDRESS

DECODER

A12

RESET

I/O0 - 7

WE

OE

CS

8

CONTROL

LOGIC

EQUAL

MATCH (OPEN DRAIN)

65,536-BIT

MEMORY ARRAY

I/O CONTROL

VCC

GND

3013 drw 01

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGE AUGUST 1996

1996 Integrated Device Technology, Inc. DSC-3013/4

14.1

1

IDT71B74

BiCMOS STATIC RAM 64K (8K x 8-BIT) CACHE-TAG RAM COMMERCIAL TEMPERATURE RANGE

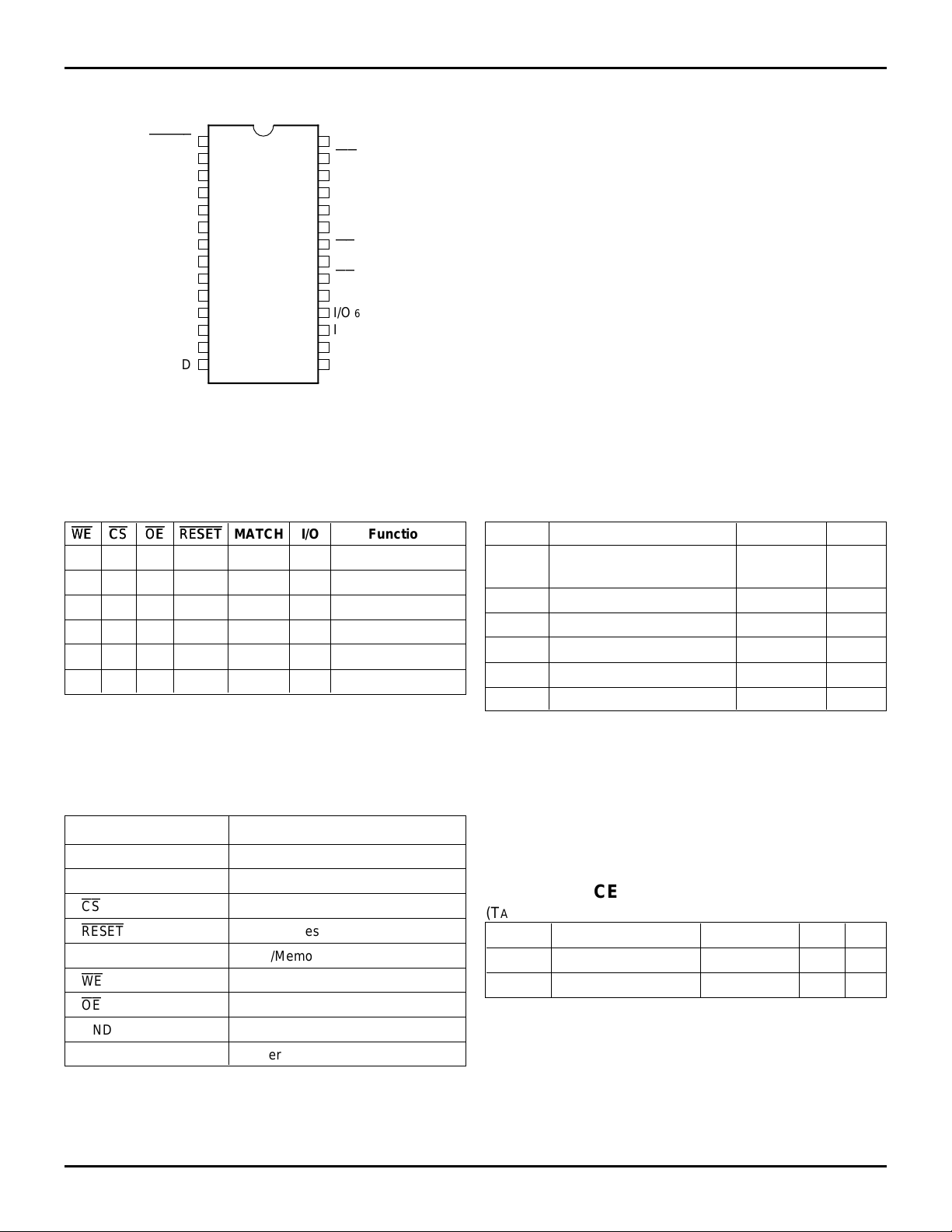

PIN CONFIGURATION

RESET

A

A

A

A

A

A

A

A

A

I/O

I/O

I/O

GND

1

2

12

3

7

4

6

5

5

4

3

2

1

0

0

1

2

6

7

8

9

10

11

12

13

14

P28-2

SO28-5

DIP/SOJ

V

CC

28

WE

27

MATCH

26

A

8

25

24

A

9

A

23

11

22

OE

A

10

21

20

CS

I/O

I/O

I/O

I/O

I/O

7

6

5

4

3

3013 drw 02

19

18

17

16

15

TOP VIEW

TRUTH TABLE

WEWECSCSOEOERESET

(1, 2)

RESET

MATCH I/O Function

X X X L HIGH — Reset all bits to LOW

X H X H HIGH Hi-Z Deselect chip

H L H H LOW DIN No MATCH

H L H H HIGH DIN MATCH

H L L H HIGH DOUT Read

L L X H HIGH D

NOTES: 3013 tbl 01

1. H = VIH, L = VIL, X = DON'T CARE

2. HIGH = High-Z (pulled up by an external resistor), and LOW = V

IN Write

OL.

PIN DESCRIPTIONS

Pin Names Description

A0–12 Address

I/O0-7 Data Input/Output

CS

RESET

MATCH Data/Memory Match (Open Drain)

WE

OE

GND Ground

V

CC Power

Chip Select

Memory Reset

Write Enable

Output Enable

3013 tbl 02

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Rating Com’l. Unit

(2)

V

TERM

Terminal Voltage with –0.5 to +7.0 V

Respect to GND

TA Operating Temperature 0 to +70 °C

TBIAS Temperature Under Bias –55 to +125 ° C

TSTG Storage Temperature –55 to +125 °C

PT Power Dissipation 1.0 W

OUT DC Output Current 50 mA

I

NOTES: 3013 tbl 03

1. Stresses greater than those listed under ABSOLUTE MAXIMUM

RATINGS may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

TERM must not exceed VCC + 0.5V.

2. V

CAPACITANCE

(TA = +25°C, f = 1.0MHz, SOJ Package)

Symbol Parameter

CIN Input Capacitance VIN = 3dV 6 pF

OUT Output Capacitance VOUT = 3dV 7 pF

C

NOTE: 3013 tbl 04

1. This parameter is determined by device characterization, but is not

production tested.

(1)

Conditions Max. Unit

14.1 2

IDT71B74

BiCMOS STATIC RAM 64K (8K x 8-BIT) CACHE-TAG RAM COMMERCIAL TEMPERATURE RANGE

RECOMMENDED DC OPERATING

CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

VCC Supply Voltage 4.5 5.0 5.5 V

GND Supply Voltage 0 0 0 V

VIH Input HIGH Voltage

VIHR

V

IL Input LOW Voltage –0.5

NOTES: 3013 tbl 05

1. All inputs except

2. When using bipolar devices to drive the

1kΩ–10kΩ is usually required to assure this voltage.

3. V

IL (min.) = –1.5V for pulse width less than 10ns, once per cycle.

TERM must not exceed VCC + 0.5V.

4. V

RESET

Input Voltage 2.5

RESET

.

(1)

2.2 — 6.0

(2)

(3)

RESET

— 6.0 V

— 0.8 V

input, a pullup resistor of

DC ELECTRICAL CHARACTERISTICS

(4)

(1)

RECOMMENDED OPERATING

TEMPERATURE AND SUPPLY VOLTAGE

Grade Ambient Temperature GND VCC

Commercial 0°C to +70°C 0V 5V ± 10%

3013 tbl 06

V

(VCC = 5.0V ± 10%, VLC = 0.2V, VHC = VCC – 0.2V)

Symbol Parameter 71B74S8 71B74S10 71B74S12 71B74S15 71B74S20 Unit

CC Dynamic Operating Current

I

Outputs Open, VCC = Max., f = fMAX

NOTES: 3013 tbl 07

1. All values are maximum guaranteed values.

MAX = 1/tRC, only input addresses are cycling at fMAX.

2. f

WE

= VLC 230 210 200 190 180 mA

(2)

WE

= VHC 210 200 170 160 150 mA

DC ELECTRICAL CHARACTERISTICS OVER THE OPERATING TEMPERATURE

AND SUPPLY VOLTAGE

Symbol Parameter Test Condition Min. Max. Unit

|I

LI| Input Leakage Current VCC = Max., VIN = GND to VCC —5µA

LO| Output Leakage Current VCC = Max.,

|I

VOL Output LOW Voltage IOL = 22mA MATCH — 0.5 V

OH Output HIGH Voltage IOH = –4mA, VCC = Min. (Except MATCH) 2.4 — V

V

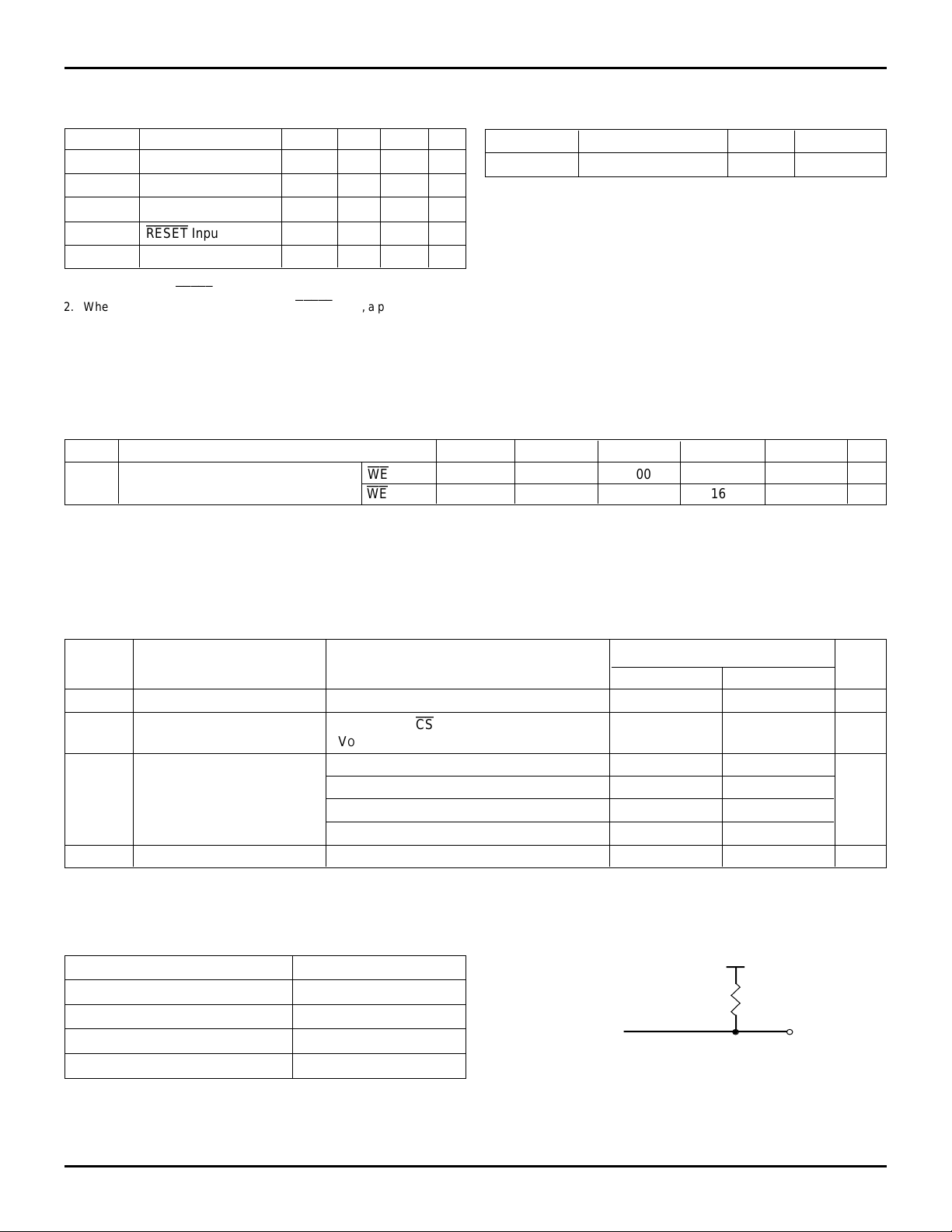

AC TEST CONDITIONS

Input Pulse Levels GND to 3.0V

Input Rise/Fall Times 3ns

Input Timing Reference Levels 1.5V

Output Reference Levels 1.5V

AC Test Load See Figures 1, 2, and 3

(VCC = 5.0V ± 10%)

VOUT = GND to VCC

OL = 18mA MATCH — 0.4

I

OL = 10mA, VCC = Min. (Except MATCH) — 0.5

I

IOL = 8mA, VCC = Min. (Except MATCH) — 0.4

IDT71B74S

CS

= VIH,—5µA

3013 tbl 08

1.5V

50

Ω

DATA

OUT

3013 drw 03

3013 tbl 09

Figure 1. AC Test Load

14.1 3

Loading...

Loading...