Integrated Device Technology Inc. IDT71B74 User Manual

查询IDT72021L25D供应商

CMOS ASYNCHRONOUS FIFO WITH

RETRANSMIT

1K x 9, 2K x 9, 4K x 9

Integrated Device Technology, Inc.

FEATURES:

• First-In/First-Out Dual-Port memory

• Bit organization

– IDT72021—1K x 9

– IDT72031—2K x 9

– IDT72041—4K x 9

• Ultra high speed

– IDT72021—25ns access time

– IDT72031—35ns access time

– IDT72041—35ns access time

• Easily expandable in word depth and/or width

• Asynchronous and simultaneous read and write

• Functionally equivalent to IDT7202/03/04 with Output

Enable (OE) and Almost Empty/Almost Full Flag (

• Four status flags: Full, Empty, Half-Full (single device

mode), and Almost Empty/Almost Full (7/8 empty or 7/8

full in single device mode)

• Output Enable controls the data output port

• Auto-retransmit capability

• Available in 32-pin DIP and PLCC

• Military product compliant to MIL-STD-883, Class B

• Industrial temperature range (-40

o

C to +85oC) is avail

able, tested to military electrical specifications

AEF

DESCRIPTION:

IDT72021/031/041s are high-speed, low-power, dual-port

memory devices commonly known as FIFOs (First-In/FirstOut). Data can be written into and read from the memory at

independent rates. The order of information stored and extracted does not change, but the rate of data entering the FIFO

might be different than the rate leaving the FIFO. Unlike a

Static RAM, no address information is required because the

read and write pointers advance sequentially. The IDT72021/

031/041s can perform asynchronous and simultaneous read

and write operations. There are four status flags, (HF, FF, EF,

AEF

) to monitor data overflow and underflow. Output Enable

(OE) is provided to control the flow of data through the output

)

port. Additional key features are Write (W), Read (R), Retransmit (RT), First Load (FL), Expansion In (XI) and Expansion Out

(XO). The IDT72021/031/041s are designed for those applications requiring data control flags and Output Enable (OE) in

multiprocessing and rate buffer applications.

The IDT72021/031/041s are fabricated using IDT’s CMOS

technology. Military grade product is manufactured in compliance with the latest version of MIL-STD-883, Class B, for high

reliability systems.

IDT72021

IDT72031

IDT72041

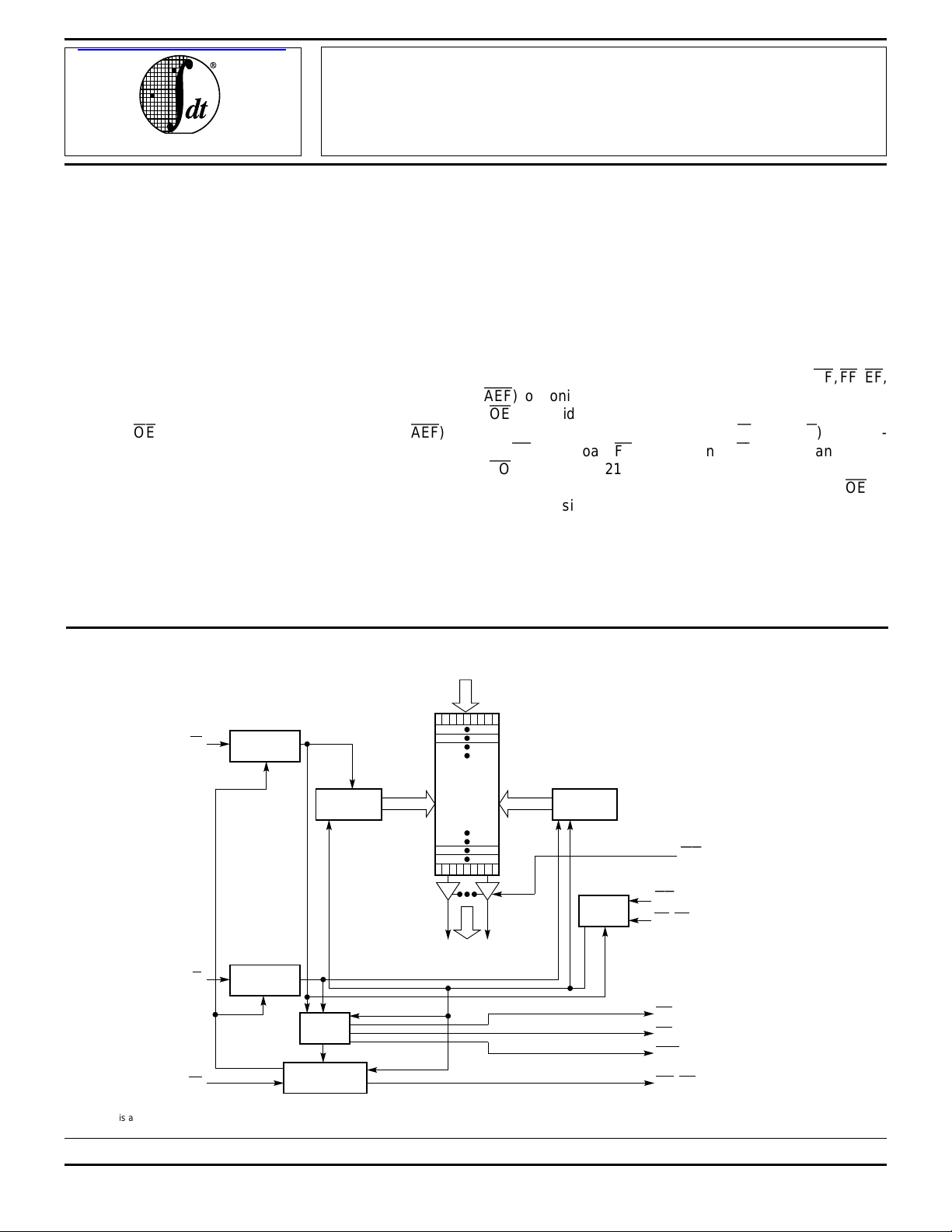

FUNCTIONAL BLOCK DIAGRAM

W

R

XI

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

FAST is a trademark of National Semiconductor Co.

WRITE

CONTROL

WRITE

POINTER

READ

CONTROL

FLAG

LOGIC

EXPANSION

LOGIC

THREE-

BUFFERS

DATA INPUT

1

2

1024/

2048/

4096

STATE

DATA OUTPUTS

0–D8)

(D

RAM

ARRAY

1024 x 9

2048 x 9

4096 x 9

0–Q8)

(Q

READ

POINTER

RESET

LOGIC

OE

RS

FL/RT

EF

FF

AEF

XO/HF

2677 drw 01

MILITARY AND COMMERCIAL TEMPERATURE RANGES DECEMBER 1996

1996 Integrated Device Technology, Inc. DSC-2677/7

For latest information contact IDT's web site at www.idt.com or fax-on-demand at 408-492-8391.

5.09 1

IDT72021, IDT72031, IDT72041

CMOS ASYNCHRONOUS FIFO WITH RETRANSMIT 1K x 9, 2K x 9, 4K x 9

MILITARY AND COMMERCIAL TEMPERATURE RANGES

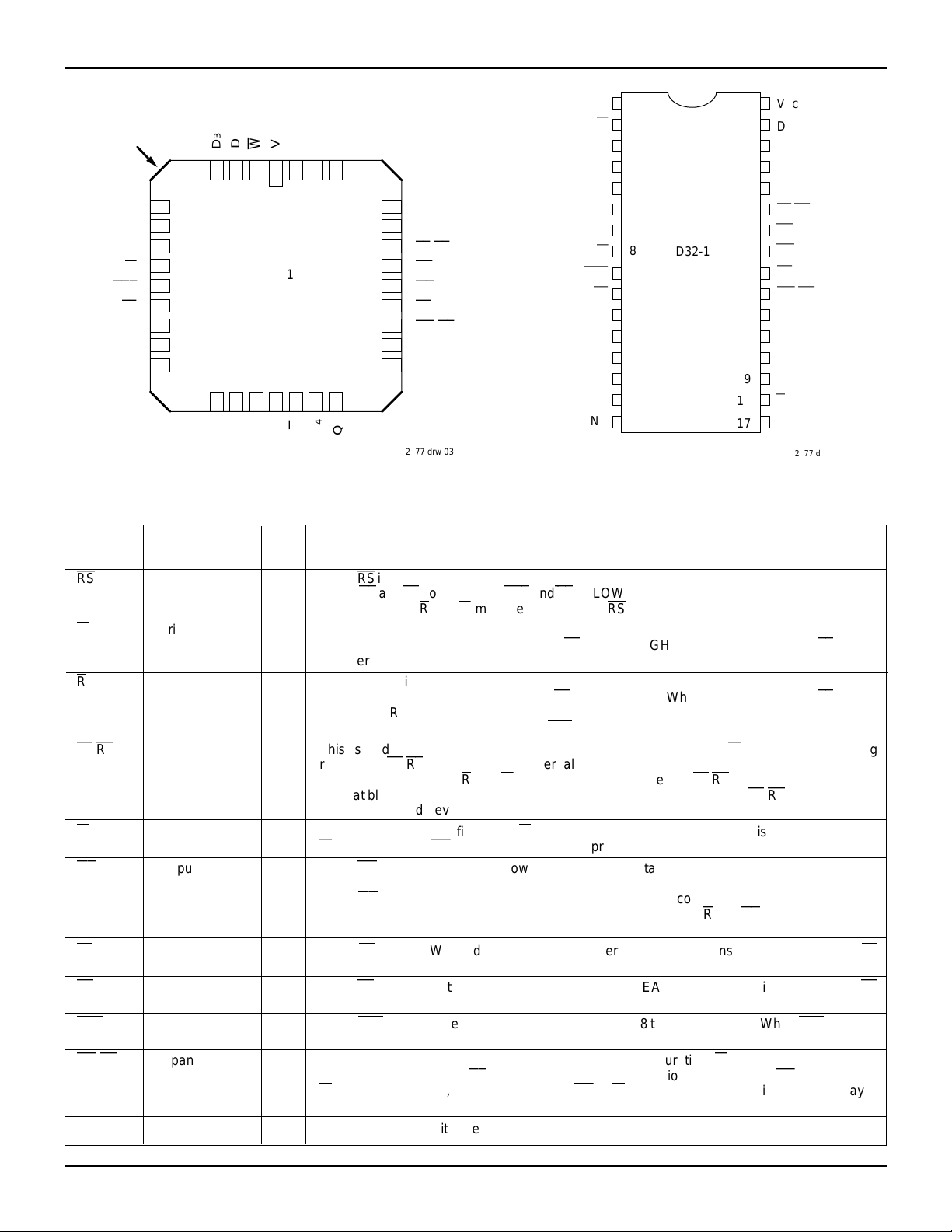

PIN CONFIGURATIONS

INDEX

D

2

1

D

0

D

XI

AEF

FF

0

Q

1

Q

2

Q

D3

4

5

6

7

8

9

10

11

12

13

14 15 16 17 18 19 20

Q3

PLCC TOP VIEW

CC

D8

V

W

VCCD4D5

3 2132 31 30

J32-1

4

GND

GND

R

Q

Q8

D

29

28

27

26

25

24

23

22

21

Q5

6

D

7

FL/RT

RS

OE

EF

XO/HF

7

Q

Q

6

2677 drw 03

GND

PIN DESCRIPTIONS

Symbol Name I/O Description

D

0–D8 Inputs I Data inputs for 9-bit wide data.

RS

W

R

FL/RT

XI

OE

FF

EF

AEF

XO/HF

0–Q8 Outputs O Data outputs for 9-bit wide data.

Q

Reset I When RS is set LOW, internal READ and WRITE pointers are set to the first location of the RAM

array. HF and FF go HIGH, and

AEF

and

EF

go LOW. A reset is required before an initial WRITE

after power-up. R and W must be HIGH during RS cycle.

Write I When WRITE is LOW, data can be written into the RAM array sequentially, independent of

READ. In order for WRITE to be active, FF must be HIGH. When the FIFO is full (FF-LOW),

the internal WRITE operation is blocked.

Read I When READ is LOW, data can be read from the RAM array sequentially, independent of

WRITE. In order for READ to be active, EF must be HIGH. When the FIFO is empty (EF-LOW),

the internal READ operation is blocked. The three-state output buffer is controlled by the read

signal and the external output control

(OE

).

First Load/ I This is a dual-purpose input. In the single device configuration (XI grounded), activating

retransmit (FL/RT-LOW) will set the internal READ pointer to the first location. There is no effect

Retransmit

on the WRITE pointer. R and W must be HIGH before setting FL/RT LOW. Retransmit is not

compatible with depth expansion. In the depth expansion configuration, FL/RT-LOW indicates

the first activated device.

Expansion In I In the single device configuration, XI is grounded. In depth expansion or daisy chain expansion,

XI

is connected to XO (expansion out) of the previous device.

Output Enable I When OE is set HIGH, the data flow through the three-state output buffer is inhibited regardless

of an active READ operation. A read operation does increment the read pointer in this situation.

When OE is set LOW, Q

0-Q8 are still in a HIGH impedance condition if no READ occurs. For

a complete READ operation with data appearing on Q

LOW.

Full Flag O When FF goes LOW, the device is full and further WRITE operations are inhibited. When

is HIGH, the device is not full.

Empty Flag O When EF goes LOW, the device is empty and further READ operations are inhibited. When

is HIGH, the device is not empty.

Almost-Empty/ O When

Almost-Full Flag

AEF

is LOW, the device is empty to 1/8 full or 7/8 to completely full. When

the device is greater than 1/8 full, but less than 7/8 full.

Expansion Out/ O This is a dual purpose output. In the single device configuration (XI grounded), the device is

Half-Full Flag

more than half full when HF is LOW. In the depth expansion configuration (XO connected to

XI

of the next device), a pulse is sent from XO to XI when the last location in the RAM array is

filled.

V

CC

D

D3

D2

D1

D0

AEF

FF

Q

Q1

Q2

Q3

Q8

W

8

XI

0

1

2

3

4

5

6

7

8

D32-1

9

10

11

12

13

14

15

16

DIP TOP VIEW

0-Q8, both

32

VCC

D4

31

30

D5

29

D6

D7

28

27

FL/RT

26

RS

OE

25

EF

24

XO/HF

23

7

Q

22

Q6

21

Q5

20

19

Q4

18

R

GND

17

2677 drw 02

R

and OE should be asserted

AEF

is HIGH,

2677 tbl 01

FF

EF

5.09 2

IDT72021, IDT72031, IDT72041

CMOS ASYNCHRONOUS FIFO WITH RETRANSMIT 1K x 9, 2K x 9, 4K x 9

MILITARY AND COMMERCIAL TEMPERATURE RANGES

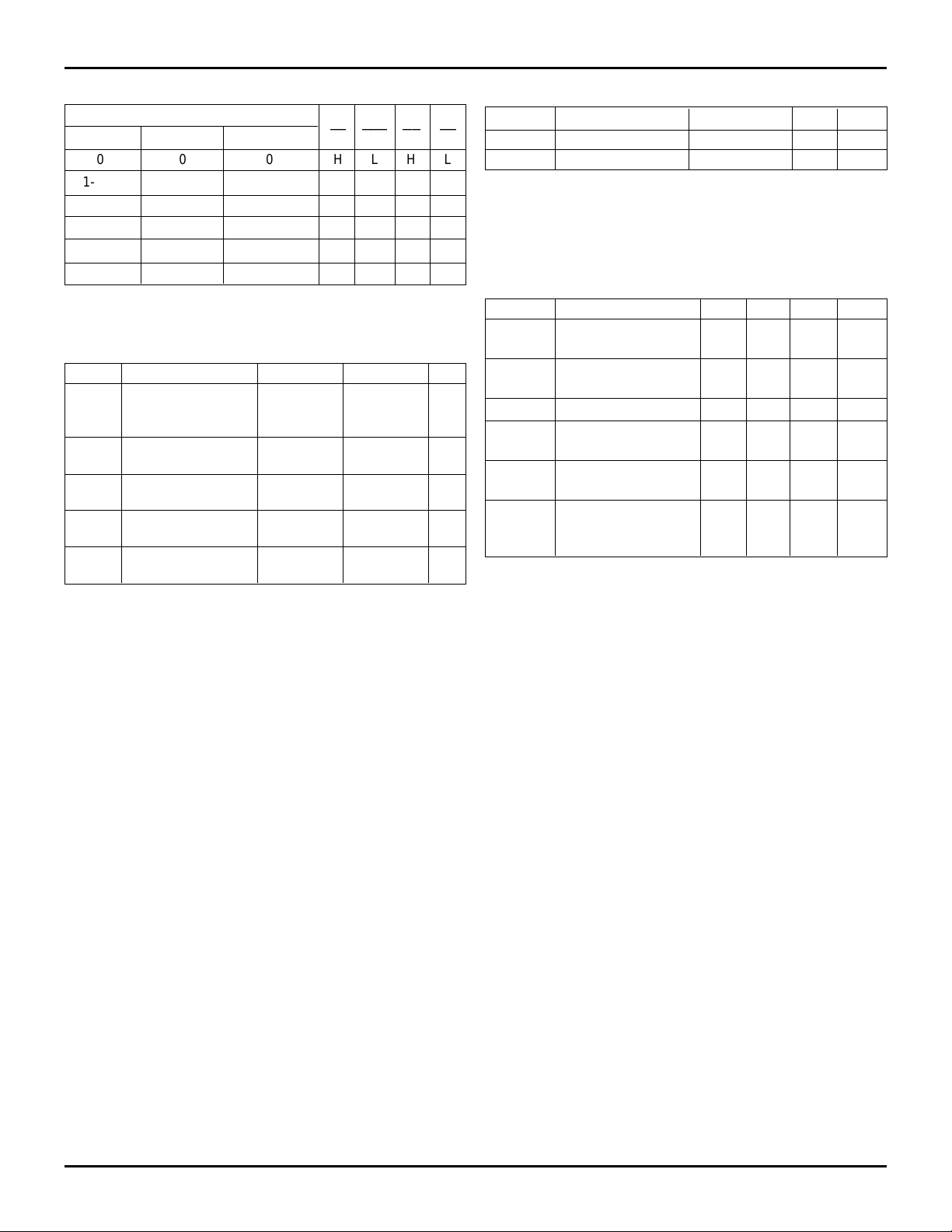

STATUS FLAG

Number of Words in FIFO

1K 2K 4K

00 0HLHL

1-127 1-255 1-511 H L H H

128-512 256-1024 512-2048 HHHH

513-896 1025-1792 2049-3584 H H L H

897-1023 1793-2047 3585-4095 H L L H

1024 2048 4096 L L L H

ABSOLUTE MAXIMUM RATINGS

Symbol Rating Com’l. Mil. Unit

TERM Terminal Voltage –0.5 to +7.0 –0.5 to +7.0 V

V

with Respect

to GND

T

A Operating 0 to +70 –55 to +125 °C

Temperature

T

BIAS Temperature –55 to +125 –65 to +135 °C

Under Bias

T

STG Storage –55 to +125 –65 to +155 °C

Temperature

I

OUT DC Output 50 50 mA

Current

NOTE: 2677 tbl 04

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS

may cause permanent damage to the device. This is a stress rating only

and functional operation of the device at these or any other conditions

above those indicated in the operational sections of this specification is not

implied. Exposure to absolute maximum rating conditions for extended

periods may affect reliabilty.

FF AEF HF EF

2677 tbl l 02

(1)

CAPACITANCE (TA = +25°C, f = 1.0 MHz)

Symbol Parameter

IN Input Capacitance VIN = 0V 10 pF

C

OUT Output Capacitance VOUT = 0V 10 pF

C

NOTE: 2677 tbl 03

1. These parameters are sampled and not 100% tested.

(1)

Condition Max. Unit

RECOMMENDED DC

OPERATING CONDITIONS

Symbol Parameter Min. Typ. Max. Unit

CCM Military Supply 4.5 5.0 5.5 V

V

Voltage

CCC Commercial 4.5 5.0 5.5 V

V

Supply Voltage

GND Supply Voltage 0 0 0 V

IH Input High Voltage 2.0 — — V

V

Commercial

V

IH Input High Voltage 2.2 — — V

Military

(1)

V

IL

NOTE: 2677 tbl 05

1. 1.5V undershoots are allowed for 10ns once per cycle.

Input Low Voltage — — 0.8 V

Commercial and

Military

5.09 3

IDT72021, IDT72031, IDT72041

CMOS ASYNCHRONOUS FIFO WITH RETRANSMIT 1K x 9, 2K x 9, 4K x 9

MILITARY AND COMMERCIAL TEMPERATURE RANGES

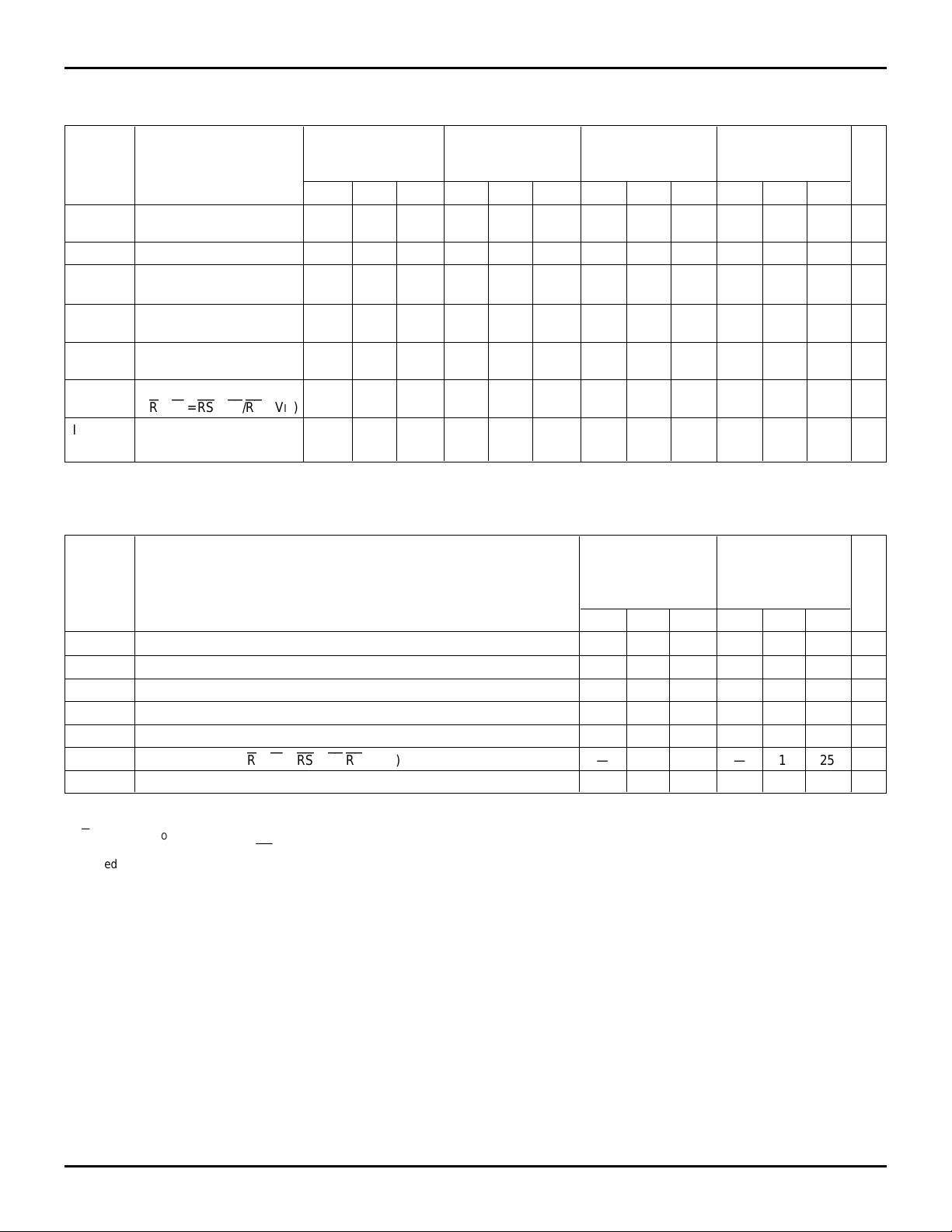

DC ELECTRICAL CHARACTERISTICS — IDT72021

(Commercial: VCC = 5.0V±10%, TA = 0°C to +70°C; Military: V CC = 5V±10%, TA = –55°C to +125°C)

IDT72021 IDT72021 IDT72021 IDT72021

Commercial Military Commercial Military

t

A =25,35ns tA =30,40ns tA =50ns tA =50ns

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Min. Typ. Max. Unit

(1)

LI

I

(2)

I

LO

OH Output Logic “1” Voltage 2.4 — — 2.4 — — 2.4 — — 2.4 — — V

V

OL Output Logic “0” Voltage — — 0.4 — — 0.4 — — 0.4 — — 0.4 V

V

(3,4)

CC1

I

(3)

I

CC2

(3)

CC3

I

Input Leakage Current –1 — 1 –10 — 10 –1 — 1 –10 — 10 µA

(Any Input)

Output Leakage Current –10 — 10 –10 — 10 –10 — 10 –10 — 10 µA

I

OH = –2mA

I

OL = 8mA

Active Power Supply — — 120 — — 140 — 50 80 — 70 100 mA

Current

Standby Current — — 12 — — 20 — 5 8 — 8 15 mA

(R = W = RS = FL/RT = V

IH)

Power Down Current — — 500 — — 900 — — 500 — — 900 µA

(All Input = V

CC – 0.2V)

2677 tbl 06

DC ELECTRICAL CHARACTERISTICS — IDT72031, IDT72041

(Commercial: VCC = 5.0V±10%, TA = 0°C to +70°C; Military: VCC = 5V±10%, TA = –55°C to +125°C)

IDT72031 IDT72031

IDT72041 IDT72041

Commercial Military

t

A =35,50ns tA =40,50ns

Symbol Parameter Min. Typ. Max. Min. Typ. Max. Unit

(1)

LI

I

(2)

I

LO

V

OH Output Logic “1” Voltage IOUT = –2mA 2.4 — — 2.4 — — V

V

OL Output Logic “0” Voltage IOUT = 8mA — — 0.4 — — 0.4 V

(3,5)

I

CC1

(3)

I

CC2

(3)

I

CC3

NOTES: 2677 tbl 07

1. Measurements with 0.4 ≤ VIN ≤ VCC.

2.R ≥ V

CC measurements are made with

3. I

4. Tested at f = 20MHz.

5. Tested at f = 15.3 MHz.

Input Leakage Current (Any Input) –1 — 1 –10 — 10 µA

Output Leakage Current –10 — 10 –10 — 10 µA

Active Power Supply Current — 75 120 — 100 150 mA

Standby Current (R = W = RS = FL/RT = VIH)—812—1225mA

Power Down Current (All Input = VCC – 0.2V) — — 2 — — 4 mA

IH, 0.4 ≤ VOUT ≤ VCC.

OE

= HIGH.

5.09 4

IDT72021, IDT72031, IDT72041

CMOS ASYNCHRONOUS FIFO WITH RETRANSMIT 1K x 9, 2K x 9, 4K x 9

MILITARY AND COMMERCIAL TEMPERATURE RANGES

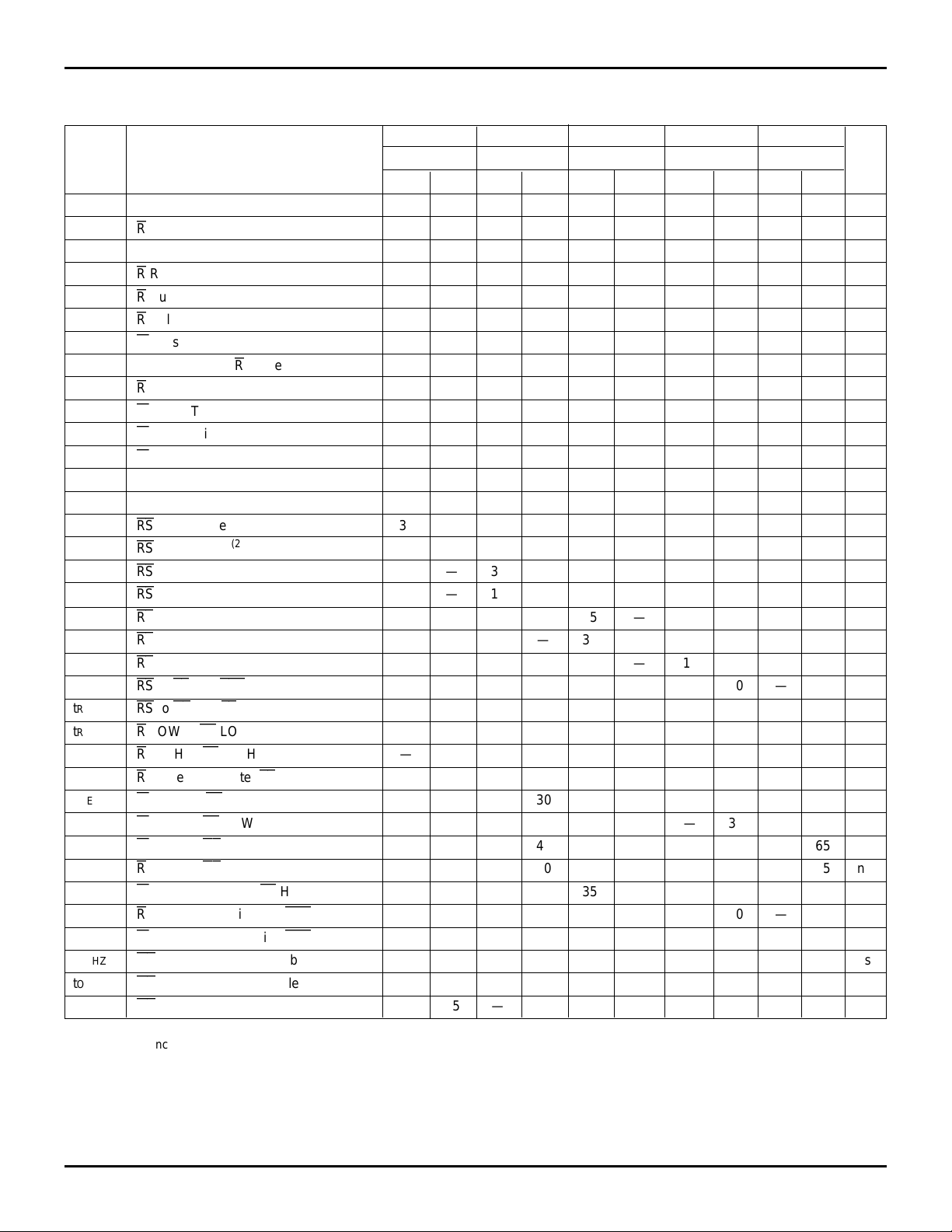

AC ELECTRICAL CHARACTERISTICS — IDT72021

(1)

(Commercial: VCC = 5.0V±10%, TA = 0°C to +70°C; Military: VCC = 5V±10%, TA = –55°C to +125°C)

Com’l Mil. Com’l Mil. Com’l & Mil.

72021L25 72021L30 72021L35 72021L40 72021L50

Symbol Parameter Min. Max. Min. Max. Min. Max. Min. Max. Min. Max. Unit

S Shift Frequency — 28.5 — 25 — 22.2 — 20 — 15 MHz

f

t

RC

A Access Time — 25 — 30 — 35 — 40 — 50 ns

t

RR

t

t

RPW

RLZ

t

WLZ

t

t

DV Data Valid from

RHZ

t

WC

t

WPW

t

t

WR

DS Data Set-up Time 15 — 18 — 18 — 20 — 30 — ns

t

DH Data Hold Time 0 — 0 — 0 — 0 — 5 — ns

t

t

RSC

RS

t

RSS

t

t

RSR

RTC

t

RT

t

t

RTR

RSF1

t

RSF2

t

REF

t

t

RFF

RPE

t

WEF

t

t

WFF

WHF

t

RHF

t

t

WPF

RF

t

WF

t

t

OEHZ

OELZ

t

AOE

t

NOTES: 2677 tbl 08

1. Timings referenced as in AC Test Conditions.

2. Pulse widths less than minimum value are not allowed.

3. Values guaranteed by design, not currently tested.

4. Only applies to read data flow-through mode.

R

Cycle Time 35 — 40 — 45 — 50 — 65 — ns

R

Recovery Time 10 — 10 — 10 — 10 — 15 — ns

R

Pulse Width

R

Pulse LOW to Data Bus at Low-Z

W

Pulse HIGH to Data Bus at Low-Z

R

Pulse HIGH to Data Bus at High-Z

W

Cycle Time 35 — 40 — 45 — 50 — 65 — ns

W

Pulse Width

W

Recovery Time 10 — 10 — 10 — 10 — 15 — ns

RS

Cycle Time 35 — 40 — 45 — 50 — 65 — n s

RS

Pulse Width

RS

Set-up Time 25 — 30 — 35 — 40 — 50 — ns

RS

Recovery Time 10 — 10 — 10 — 10 — 15 — ns

RT

Cycle Time 35 — 40 — 45 — 50 — 65 — ns

RT

Pulse Width

RT

Recovery Time 10 — 10 — 10 — 10 — 15 — ns

RS

to EF and

RS

to HF and FF HIGH — 35 — 40 — 45 — 50 — 65 ns

R

LOW to EF LOW — 25 — 30 — 30 — 35 — 45 ns

R

HIGH to FF HIGH — 25 — 30 — 30 — 35 — 45 ns

R

Pulse Width After EF HIGH 25 — 30 — 35 — 40 — 50 — ns

W

HIGH to EF HIGH — 25 — 30 — 30 — 35 — 45 ns

W

LOW to EF LOW — 25 — 30 — 30 — 35 — 45 ns

W

LOW to HF LOW — 35 — 40 — 45 — 50 — 65 ns

R

HIGH to HF HIGH — 35 — 40 — 45 — 50 — 65 ns

W

Pulse Width after FF HIGH 25 — 30 — 35 — 40 — 50 — ns

R

HIGH to Transitioning

W

LOW to Transitioning

OE

HIGH to High-Z (Disable)

OE

LOW to Low-Z (Enable)

OE

LOW Data Valid (Q0–Q8) — 15 — 18 — 20 — 25 — 30 ns

(2)

(3)

R

Pulse HIGH 5 — 5 — 5 — 5 — 5 — ns

(2)

(2)

(2)

AEF

LOW — 35 — 40 — 45 — 50 — 65 ns

AEF

AEF

(3)

(3)

25 — 30 — 35 — 40 — 50 — ns

5—5—5 — 5—10—ns

(3,4)

5—5—5 — 5—5—ns

(3)

— 18 — 20 — 20 — 25 — 30 ns

25 — 30 — 35 — 40 — 50 — ns

25 — 30 — 35 — 40 — 50 — ns

25 — 30 — 35 — 40 — 50 — ns

— 35 — 40 — 45 — 50 — 65 ns

— 35 — 40 — 45 — 50 — 65 ns

0 12 0 15 0 17 0 20 0 25 ns

0 12 0 15 0 17 0 20 0 25 ns

5.09 5

Loading...

Loading...