Integrated Device Technology Inc IDT29FCT520ADB, IDT29FCT520AE, IDT29FCT520AEB, IDT29FCT520AL, IDT29FCT520ALB Datasheet

...

Integrated Device Technology, Inc.

MULTILEVEL

PIPELINE REGISTER

IDT29FCT520A

IDT29FCT520B

IDT29FCT520C

FEATURES:

• Equivalent to AMD’s Am29520 bipolar Multilevel Pipeline

Register in pinout/function, speed and output drive over

full temperature and voltage supply extremes

• Four 8-bit high-speed registers

• Dual two-level or single four-level push-only stack

operation

• All registers available at multiplexed output

• Hold, transfer and load instructions

• Provides temporary address or data storage

•I

OL = 48mA (commercial), 32mA (military)

• CMOS power levels (1mW typ. static)

• Substantially lower input current levels than AMD’s

bipolar (5µA typ.)

• TTL input and output level compatible

• CMOS output level compatible

• Manufactured using advanced CMOS processing

• Available in 300 mil plastic and hermetic DIP, as well as

LCC, SOIC and CERPACK

• Product available in Radiation Tolerant and Radiation

Enhanced versions

• Military product compliant to MIL-STD-883, Class B

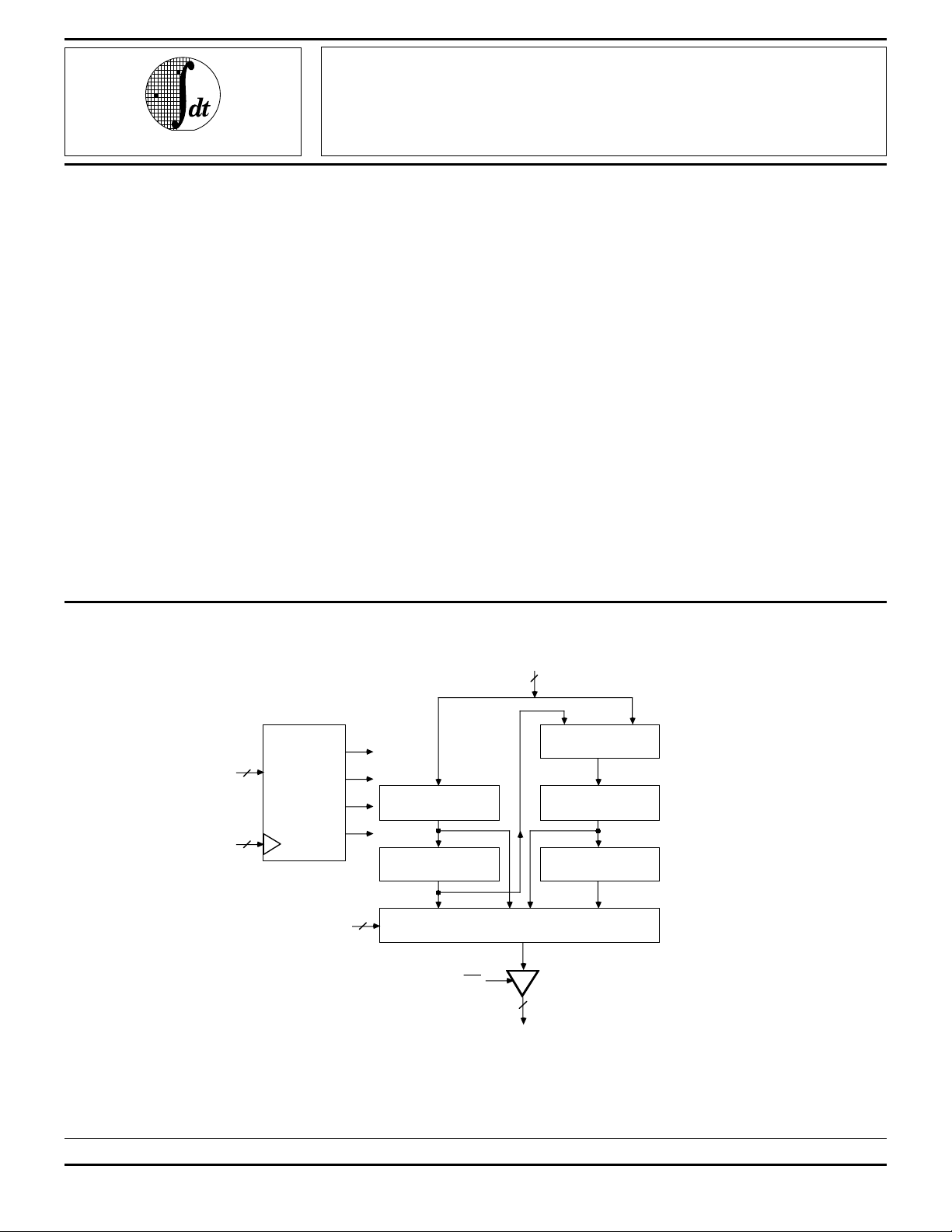

FUNCTIONAL BLOCK DIAGRAMS

DESCRIPTION:

The IDT29FCT520A/B/C contains four 8-bit positive edgetriggered registers. These may be operated as a dual 2-level

or as a single 4-level pipeline. A single 8-bit input is provided

and any of the four registers is available at the 8-bit, 3-state

output.

In the IDT29FCT520A/B/C when data is entered into the

first level (I = 2 or I = 1), the existing data in the first level is

moved to the second level. Transfer of data to the second

level is achieved using the 4-level shift instruction (I = 0). This

transfer also causes the first level to change.

I ,I10

CLK

2

1

REGISTER

CONTROL

S ,S10

OCTAL REG. A1

OCTAL REG. A2

2

OE

D -D70

8

MUX

8

Y -Y70

MUX

OCTAL REG. B1

OCTAL REG. B2

2620 drw 01

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

MILITARY AND COMMERCIAL TEMPERATURE RANGES MAY 1992

1992 Integrated Device Technology, Inc. 7.2 DSC-4608/2

1

IDT29FCT520A/B/C

MULTILEVEL PIPELINE REGISTER MILITARY AND COMMERCIAL TEMPERATURE RANGES

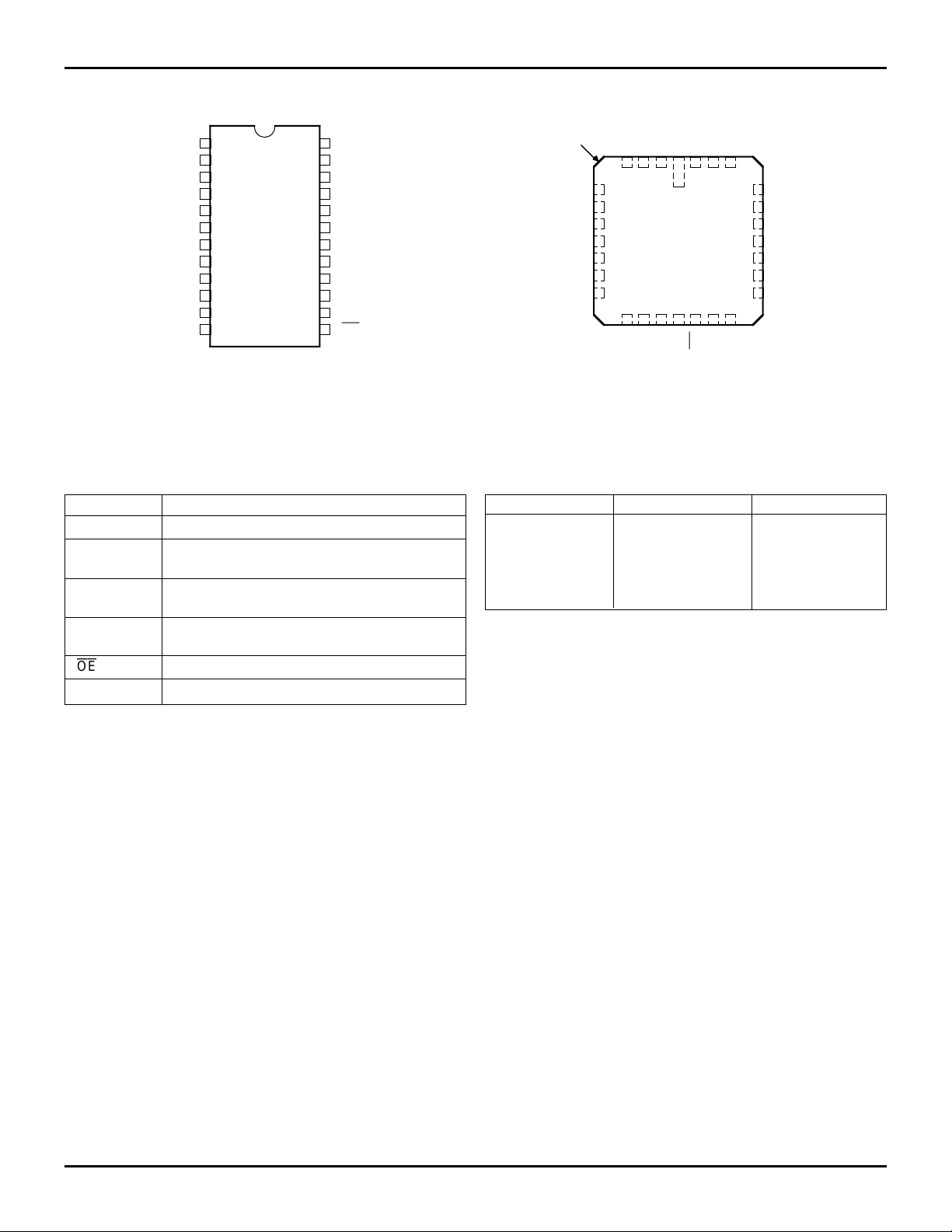

PIN CONFIGURATIONS

0

I

D

D

D

D

D

D

D

D

CLK

GND

1

I

1

2

0

3

1

2

3

4

5

6

7

4

5

6

7

8

9

10

11

12

P24-1,

D24-1,

E24-1

SO24-2

24

Vcc

23

22

21

20

19

&

18

17

16

15

14

13

S

S

Y

Y

Y

Y

Y

Y

Y

Y

OE

0

1

0

1

2

3

4

5

6

7

DIP/CERPACK/SOIC

TOP VIEW

DEFINITION OF FUNCTIONAL TERMS

Pin Names Description

n Register input port.

D

CLK Clock input. Enter data into registers on LOW-

to-HIGH transitions.

0, I1 Instruction inputs. See Figure 1 and In-

I

struction Control Tables.

S

0, S1 Multiplexer select. Inputs either register A1, A2,

B

1 or B2 data to be available at the output port.

OE

n Register output port.

Y

Output enable for 3-state output port

INDEX

D

1

D

2

D

3

NC

D

4

D

5

D

6

0

0

1

I

I

D

432128 27 26

5

6

7

8

9

10

11

L28-1

12 13 14 15 16 17 18

7

D

CLK

GND

LCC

TOP VIEW

REGISTER SELECTION

S1 S0 Register

00B

01B1

10A2

11A1

NC

NC

Vcc

OE

0S1

S

25

0

Y

Y

1

24

Y

2

23

NC

22

21

Y

3

Y

4

20

19

Y

5

6Y7

2620 drw 02

Y

2

2620 tbl 02

2620 tbl 01

7.2 2

IDT29FCT520A/B/C

MULTILEVEL PIPELINE REGISTER MILITARY AND COMMERCIAL TEMPERATURE RANGES

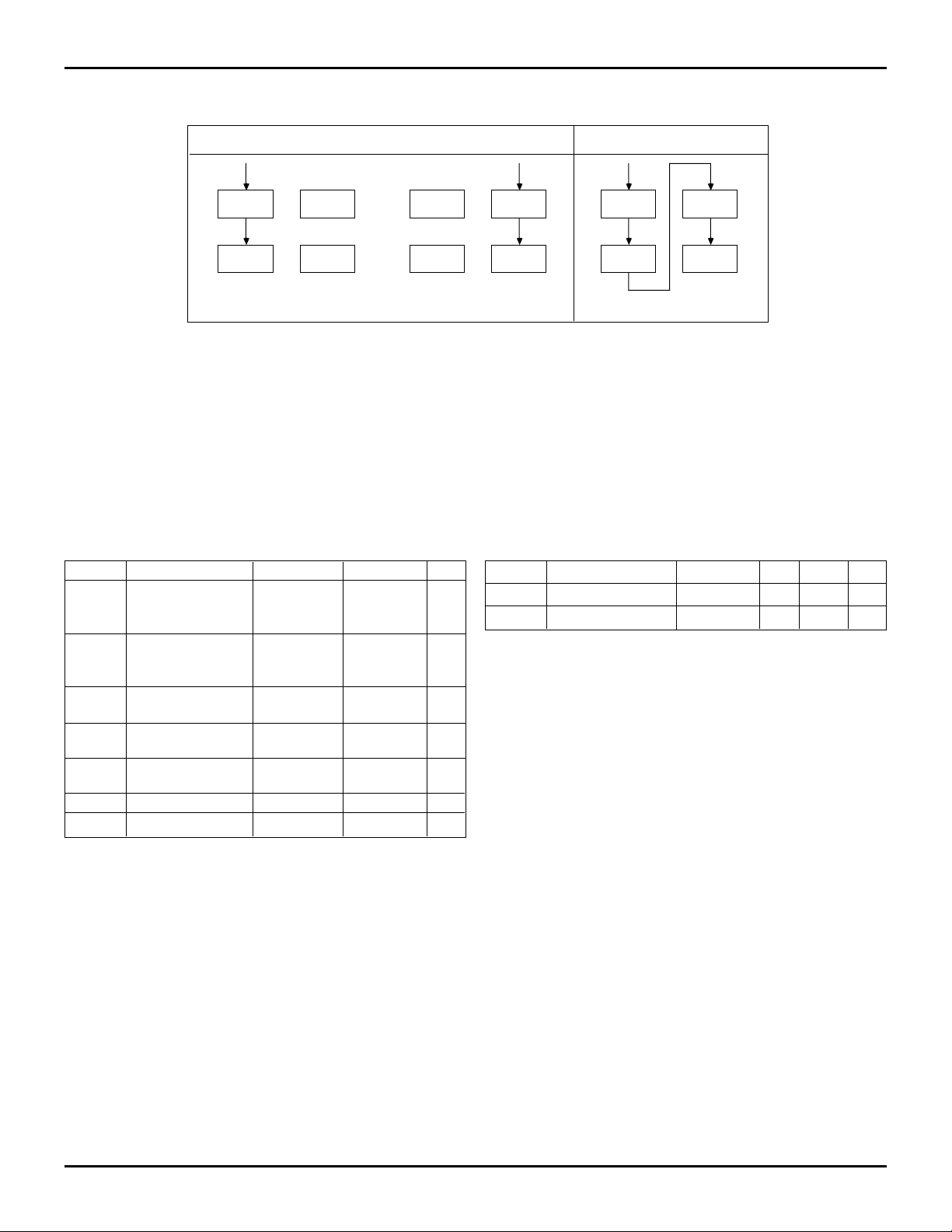

DUAL 2-LEVEL SINGLE 4-LEVEL

A1

A2

B1

B2

A1

A2

I = 2 I = 1

NOTE:

1. I = 3 for hold.

Figure 1. Data Loading in 2-Level Operation

ABSOLUTE MAXIMUM RATINGS

(1)

Symbol Rating Commercial Military Unit

(2)

V

TERM

Terminal Voltage –0.5 to +7.0 –0.5 to +7.0 V

with Respect

to GND

(3)

V

TERM

Terminal Voltage –0.5 to VCC –0.5 to VCC V

with Respect

to GND

T

A Operating 0 to +70 –55 to +125 °C

Temperature

T

BIAS Temperature –55 to +125 –65 to +135 °C

Under Bias

T

STG Storage –55 to +125 –65 to +150 °C

Temperature

P

T Power Dissipation 0.5 0.5 W

I

OUT DC Output Current 120 120 mA

NOTES: 2620 tbl 03

1. Stresses greater than those listed under ABSOLUTE MAXIMUM

RATINGS may cause permanent damage to the device. This is a stress

rating only and functional operation of the device at these or any other

conditions above those indicated in the operational sections of this

specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability. No terminal voltage

may exceed V

2. Inputs and V

3. Outputs and I/O terminals.

CC by +0.5V unless otherwise noted.

CC terminals.

B1

B2

A

A2

1

B1

B2

I = 0

2620 drw 03

CAPACITANCE (TA = +25°C, f = 1.0MHz)

Symbol Parameter

IN Input Capacitance VIN = 0V 6 10 pF

C

OUT Output Capacitance VOUT = 0V 8 12 pF

C

NOTE: 2620 tbl 04

1. This parameter is measured at characterization data but not tested.

(1)

Conditions Typ. Max. Unit

7.2 3

Loading...

Loading...