Page 1

®

IDT™ 89EB-LOGAN-19

Evaluation Board Manual

(Evaluation Board: 18-692-000)

February 2011

6024 Silver Creek Valley Road, San Jose, California 95138

Telephone: (800) 345-7015 • (408) 284-8200 • FAX: (408) 284-2775

©2011 Integrated Device Technology, Inc.

Printed in U.S.A.

Page 2

Integrated Device Technology, Inc. reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance

and to supply the best possible product. IDT does not assume any responsibility for use of any circuitry described other than the circuitry embodied in an IDT product. The

Company makes no representations that circuitry described herein is free from patent infringement or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent, patent rights or other rights, of Integrated Device Technology, Inc.

DISCLAIMER

Boards that fail to function should be returned to IDT for replacement. Credit will not be given for the failed boards nor will a

Failure Analysis be performed.

Integrated Device Technology's products are not authorized for use as critical components in life support devices or systems unless a specific written agreement pertaining to

such intended use is executed between the manufacturer and an officer of IDT.

1. Life support devices or systems are devices or systems which (a) are intended for surgical implant into the body or (b) support or sustain life and whose failure to perform,

when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

2. A critical component is any components of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device

or system, or to affect its safety or effectiveness.

IDT, the IDT logo, and Integrated Device Technology are trademarks or registered trademarks of Integrated Device Technology, Inc.

LIFE SUPPORT POLICY

Page 3

Table of Contents

®

Notes

Description of the EB-LOGAN-19 Evaluation Board

Introduction.....................................................................................................................................1-1

Board Features...............................................................................................................................1-2

Hardware................................................................................................................................1-2

Software..................................................................................................................................1-2

Other.......................................................................................................................................1-2

Revision History..............................................................................................................................1-2

Installation of the EB-LOGAN-19 Evaluation Board

EB-LOGAN-19 Installation..............................................................................................................2-1

PCI Express Mezzanine and Edge Adapters..................................................................................2-1

Hardware Description.....................................................................................................................2-3

Reference Clocks............................................................................................................................2-4

Global Reference Input Clocks...............................................................................................2-4

Local Port Input Clocks...........................................................................................................2-6

Power Sources.......................................................................................................................2-7

PCI Express Analog Power Voltage Regulator.......................................................................2-8

PCI Express Digital Power Voltage Converter........................................................................2-8

PCI Express Transmitter Analog Voltage Converter..............................................................2-8

Core Logic Voltage Converter................................................................................................2-8

3.3V I/O Voltage Regulator.....................................................................................................2-8

Power-up Sequence for PES24NT24G2................................................................................2-8

Heatsink Requirement....................................................................................................................2-8

Reset...............................................................................................................................................2-9

Fundamental Reset................................................................................................................2-9

Downstream Reset.................................................................................................................2-9

Stack Configuration................................................................................................................2-9

Boot Configuration Vector.............................................................................................................2-10

SMBus Interfaces..........................................................................................................................2-11

SMBus Slave Interface.........................................................................................................2-11

SMBus Master Interface.......................................................................................................2-12

JTAG Header................................................................................................................................2-12

PCI Express Connectors...............................................................................................................2-13

EB-LOGAN-19 Board Figure........................................................................................................2-15

Software for the EB-LOGAN-19 Eval Board

Introduction.....................................................................................................................................3-1

Device Management Software........................................................................................................3-1

Device Drivers.................................................................................................................................3-1

Schematics

Schematics.....................................................................................................................................4-1

89EB-LOGAN-19 Evaluation Board i February 16, 2011

Page 4

IDT Table of Contents

Notes

89EB-LOGAN-19 Evaluation Board ii February 16, 2011

Page 5

List of Tables

®

Notes

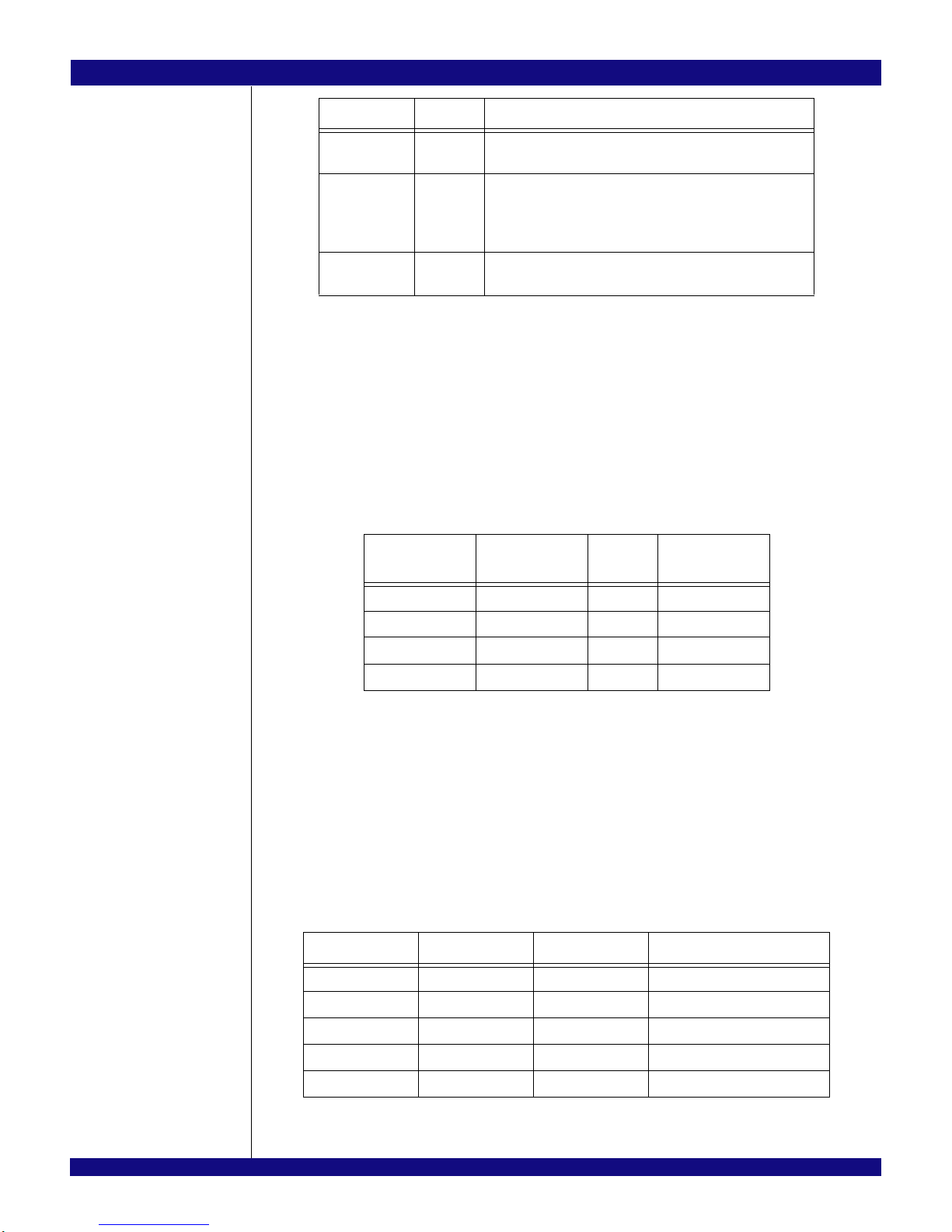

Table 2.1 EB-LOGAN-19 Global Clock Select ....................................................................................2-4

Table 2.2 Clock Buffer Input Sources .................................................................................................2-5

Table 2.3 Global Reference Input Clock Frequency Select ................................................................2-5

Table 2.4 Onboard Clock Generator Frequency Select ......................................................................2-6

Table 2.5 Onboard Reference Clock Generator Access Points .........................................................2-6

Table 2.6 EB24NT24G2 Port Clock Select .........................................................................................2-6

Table 2.7 EB-LOGAN-19 Slot Clock Select ........................................................................................2-6

Table 2.8 CLKMODE Selection PES24NT24G2 ................................................................................2-7

Table 2.9 EPS12V 24-pin Power Connector - J6 ...............................................................................2-7

Table 2.10 EPS12V 8-Pin Connector - J5 ............................................................................................2-8

Table 2.11 Ports in Each Stack ..........................................................................................................2-10

Table 2.12 Boot Configuration Vector Signals ....................................................................................2-10

Table 2.13 Boot Configuration Vector Switches S5, SW8 - SW10 .....................................................2-10

Table 2.14 Slave SMBus Interface Connector ....................................................................................2-11

Table 2.15 SMBus Slave Interface Address Configuration .................................................................2-12

Table 2.16 JTAG Connector Pin Out ..................................................................................................2-12

Table 2.17 PCI Express x8 Connector Pinout ....................................................................................2-13

89EB-LOGAN-19 Evaluation Board iii February 16, 2011

Page 6

IDT List of Tables

Notes

89EB-LOGAN-19 Evaluation Board iv February 16, 2011

Page 7

List of Figures

®

Notes

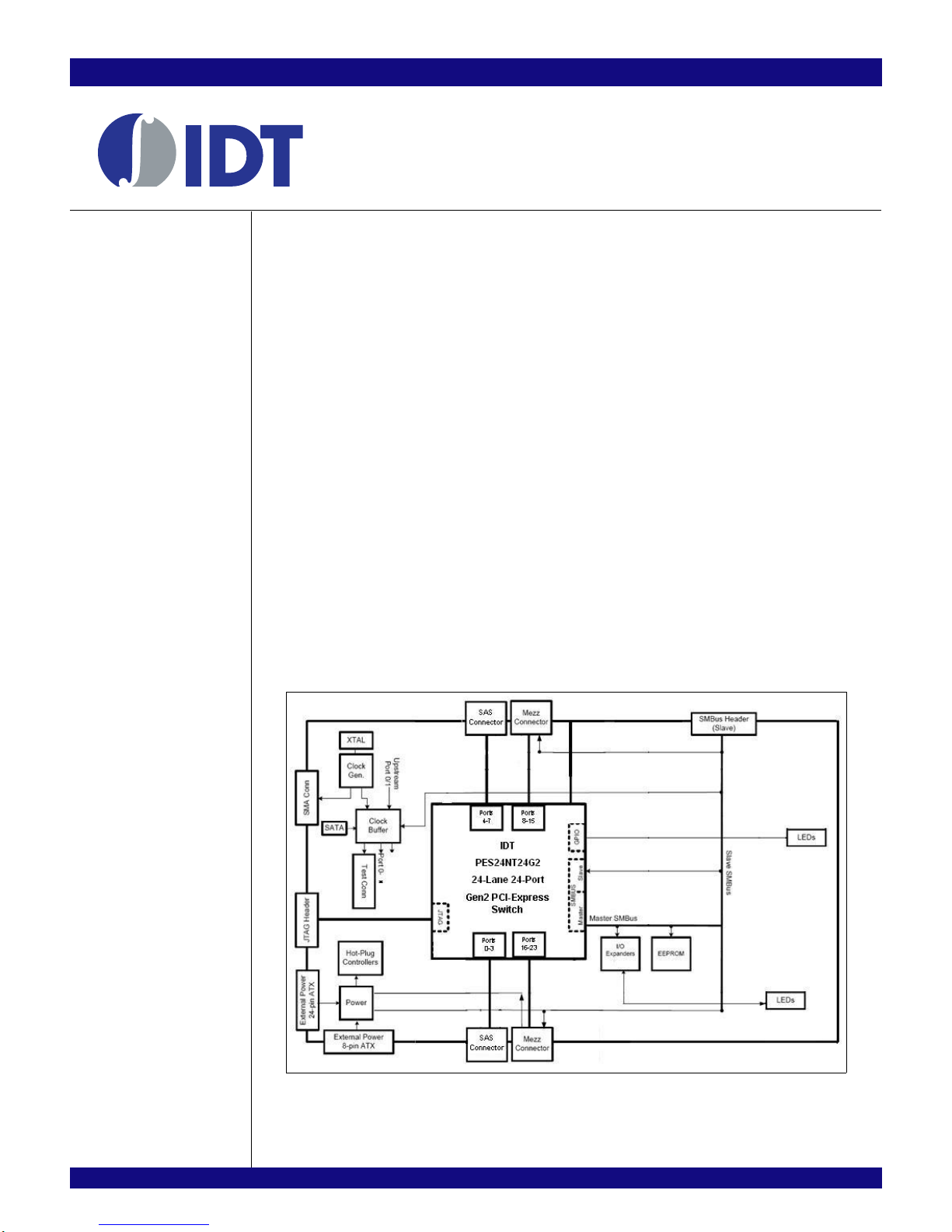

Figure 1.1 Function Block Diagram of the EB-LOGAN-19 Evaluation Board ......................................1-1

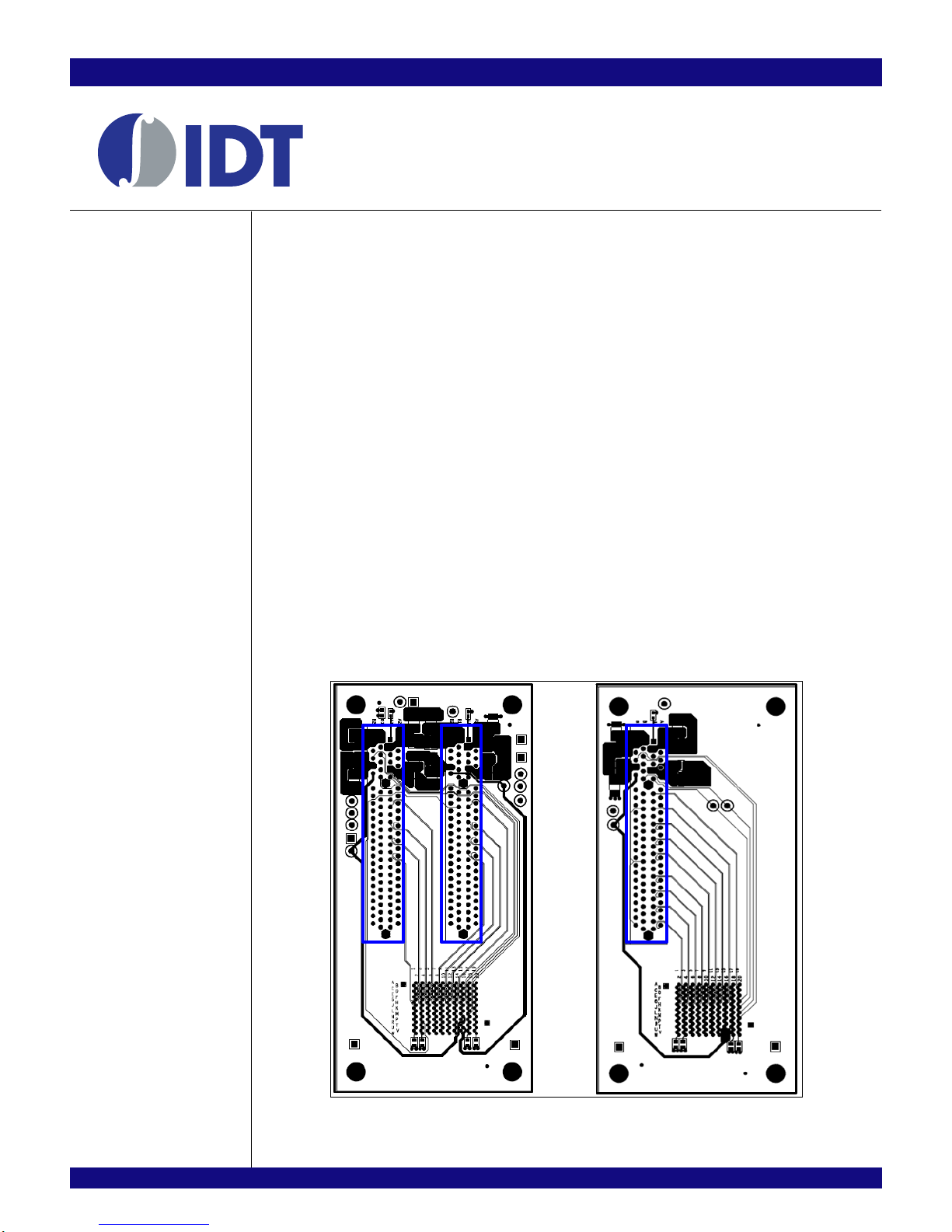

Figure 2.1 Bifurcated and Merged Mezzanine Cards ..........................................................................2-1

Figure 2.2 MiniSAS Mezzanine Adapter ............................................................................................2-2

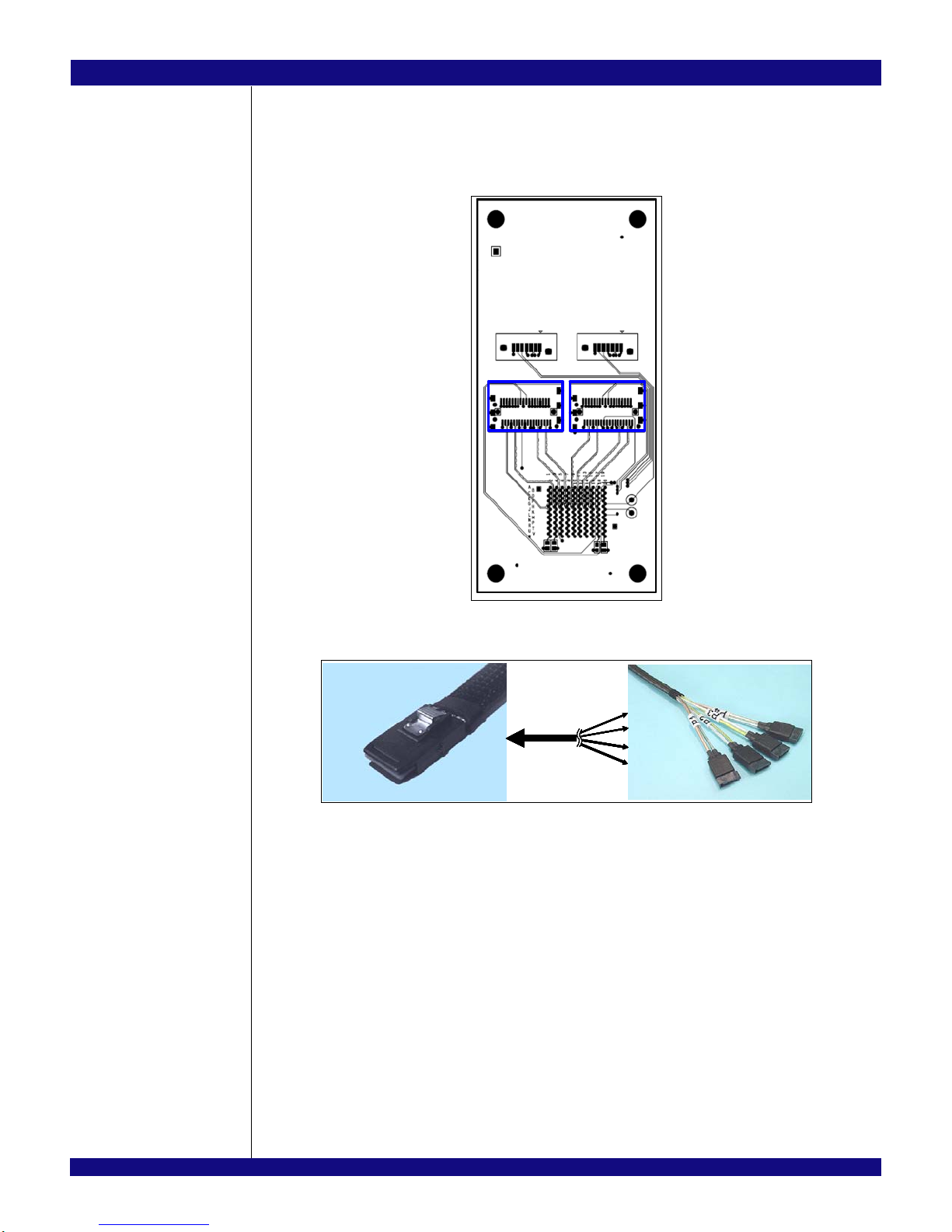

Figure 2.3 EB-LOGAN-19 iSAS-to-SATA Breakout Cable ..................................................................2-2

Figure 2.4 PCIe x1 Edge-to-SATA Adapter ........................................................................................2-3

Figure 2.5 EB-LOGAN-19 Evaluation Main Board ..............................................................................2-3

Figure 2.6 12PACK PCIe Slots Breakout Daughter Board .................................................................2-4

Figure 2.7 Differential Jumper Arrangement .......................................................................................2-4

Figure 2.8 Reference Clock Configuration ..........................................................................................2-5

Figure 2.9 EB24NT24G2 Evaluation Board ......................................................................................2-15

89EB-LOGAN-19 Evaluation Board v February 16, 2011

Page 8

IDT List of Figures

Notes

89EB-LOGAN-19 Evaluation Board vi February 16, 2011

Page 9

Chapter 1

Description of the EB-LOGAN-19

Evaluation Board

®

Notes

Introduction

The 89HPES24NT24G2 switch is a member of the IDT PCI Express® Inter-Domain Switch family of

products. It is a PCIe® Base Specification 2.1 compliant (Gen2) 24-lane, 24-port switch. The EB-LOGAN19 Evaluation Board provides an evaluation platform for the PES24NT24G2 switch and for other members

of this switch family including PES16NT16G2 and PES12NT12G2.

Detailed information related to configuration of number of ports and lanes in the switch device can be

found in the Device User Manual and the Device Datasheet. The evaluation board, along with additional

adapters and daughter boards provided by IDT, can be configured to test every possible combination of the

number of lanes and ports offered by the switch. Advanced capabilities such as switch partitioning, NTB,

DMA and local port clocking can be evaluated with the evaluation board.

The EB-LOGAN-19 brings out all 24 lanes of the device to two Mezzanine connectors and two SAS

connectors (see

of daughter cards (provided by IDT) can then be plugged into the Mezzanine connectors to facilitate

connectivity to one x8 or two x4 or four x2 or eight x1 link partners. Link partners may be plugged directly

into these daughter cards or they can be connected to these daughter cards via SAS or SATA cables and a

different board with PCIe slots known as the 12-PACK board (provided by IDT). Given that majority of the

hosts / servers offer PCIe standard slots, IDT provides the necessary adapter cards that may be plugged

into these host / server slots as well as the cables that connect such adapters to the daughter cards which

in turn are plugged into the main evaluation board on which the IDT PCIe switch device is populated.

The EB-LOGAN-19 is also used by IDT to reproduce system-level hardware or software issues reported

by customers.

LOGAN-19 board.

Figure 1.1) located close to the device - one connector per stack of 4 lanes. Various types

Figure 1.1 illustrates the functional block diagram representing the main parts of the EB-

89EB-LOGAN-19 Evaluation Board 1 - 1 February 16, 2011

Figure 1.1 Function Block Diagram of the EB-LOGAN-19 Evaluation Board

Page 10

IDT Description of the EB-LOGAN-19 Evaluation Board

Notes

Board Features

Hardware

PES24NT24G2 PCIe 24-port switch

– Twenty four ports (each x1) - for port 8 and higher, adjacent ports may be combined to create x2,

x4 or x8 ports

– PCIe Base Specification Revision 2.1 compliant (Gen2 SerDes speeds of 5 GT/S)

– Up to 2048 byte maximum Payload Size

– Automatic lane reversal and polarity inversion supported on all lanes

– Automatic per port link width negotiation to x8, x4, x2, x1

– Power on reconfiguration via optional serial EEPROM connected to the SMBUS Master interface

Upstream, Downstream Ports

– The EB-LOGAN-19 has minimum of one port configured as upstream port to be plugged into a

host slot through an adaptor and a cable.

– Up to 23 ports can be configured as downstream ports, for PCIe endpoint add-on cards to be

plugged in. The slot connectors can be configured to be x1, x2, x4 or x8, but are mechanically

open-ended on one side to allow card widths greater than x8 (e.g. x16) to be populated.

– When used in multi-partition mode, the device can be programmed through the serial EEPROM

to generate the appropriate number of upstream and downstream ports per partition.

Numerous user selectable configurations set using onboard jumpers and DIP-switches

– Source of clock - host clock or onboard clock generator

– Two clock rates (100/125 MHz) from an onboard clock generator

– Flexible clocking modes

• Common clock

• Non-common clock

• Local port clocking on ports that support this feature

– Boot mode selection

SMBUS Slave Interface (4 pin header)

SMBUS Master Interface connected to the Serial EEPROMs through I/O expander

Push button for Warm Reset

Many LEDs to display status, reset, power, hotplug, etc.

JTAG connector to the PES24NT24G2 JTAG pins.

Software

There is no software or firmware executed on the board. However, useful software is provided along

with the Evaluation Board to facilitate configuration and evaluation of the PES24NT24G2 within host

systems running popular operating systems.

Installation programs

– Operating Systems Supported: WindowsServer200x, WindowsXP, Vista, Linux

GUI based application for Windows and Linux

– Allows users to view and modify registers in the PES24NT24G2

– Binary file generator for programming the serial EEPROMs attached to the SMBUS.

Other

SMBUS cable may be required for certain evaluation exercises.

SMA connectors are provided on the EB-LOGAN-19 board for clock outputs.

Revision History

April 13, 2010: Initial publication of evaluation board manual.

89EB-LOGAN-19 Evaluation Board 1 - 2 February 16, 2011

Page 11

IDT Description of the EB-LOGAN-19 Evaluation Board

Notes

April 23, 2010: Updated Schematics in Chapter 4.

February 16, 2011: Changed default settings from Off to On in Tables 2.3 and 2.4.

89EB-LOGAN-19 Evaluation Board 1 - 3 February 16, 2011

Page 12

IDT Description of the EB-LOGAN-19 Evaluation Board

Notes

89EB-LOGAN-19 Evaluation Board 1 - 4 February 16, 2011

Page 13

Chapter 2

Installation of the EB-LOGAN-19

Evaluation Board

®

Notes

EB-LOGAN-19 Installation

This chapter discusses the steps required to configure and install the EB-LOGAN-19 evaluation board.

All available DIP switches and jumper configurations are explained in detail.

The primary installation steps are:

1. Configure jumper/switch options suitable for the evaluation or application requirements.

2. Connect PCI Express endpoint cards to the downstream port PCIe slots on the evaluation board.

3. Make sure that the host system (motherboard with root complex chipset) is powered off.

4. Connect the evaluation board to the host system.

5. Apply power to the host system.

The EB-LOGAN-19 board is typically shipped with all jumpers and switches configured to their default

settings. In most cases, the board does not require further modification or setup however please visit IDT

website and fill out the Technical Support Request form at http://www.idt.com/?app=TechSupport for other

configurations.

PCI Express Mezzanine and Edge Adapters

The PCI Express lanes are broken out to four Mezzanine connectors on EB-LOGAN-19 Evaluation

Board. The adapter cards are used to convert Mezzanine connector into PCI Express slot connector(s) or

Internal mini SAS (iSAS) connectors or both. A Bifurcated Mezzanine Card has two mechanical x8 PCIe

Slots (x4 electrically) while a Merged Mezzanine Card has single x8 PCIe Slot. Pictured in

Figure 2.1.

Figure 2.1 Bifurcated and Merged Mezzanine Cards

89EB-LOGAN-19 Evaluation Board 2 - 1 February 16, 2011

Page 14

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Pictured in Figure 2.2 is the mini-SAS Mezzanine card which consists of two iSAS and two SATA

connectors. Each iSAS connector supports up to PCI Express x4 width and the SATA connectors are used

for clock and reset signals of each x4 or less stack/port. An iSAS-to-SATA breakout cable shown in

Figure

2.3 is used connect from iSAS to edge adapter and/or 12PACK.

Figure 2.2 MiniSAS Mezzanine Adapter

SA S (x 4) – f our

SA S (x 4) – f our

SATA (x 1 )

SATA (x 1 )

breakout c ab le

breakout c ab le

Figure 2.3 EB-LOGAN-19 iSAS-to-SATA Breakout Cable

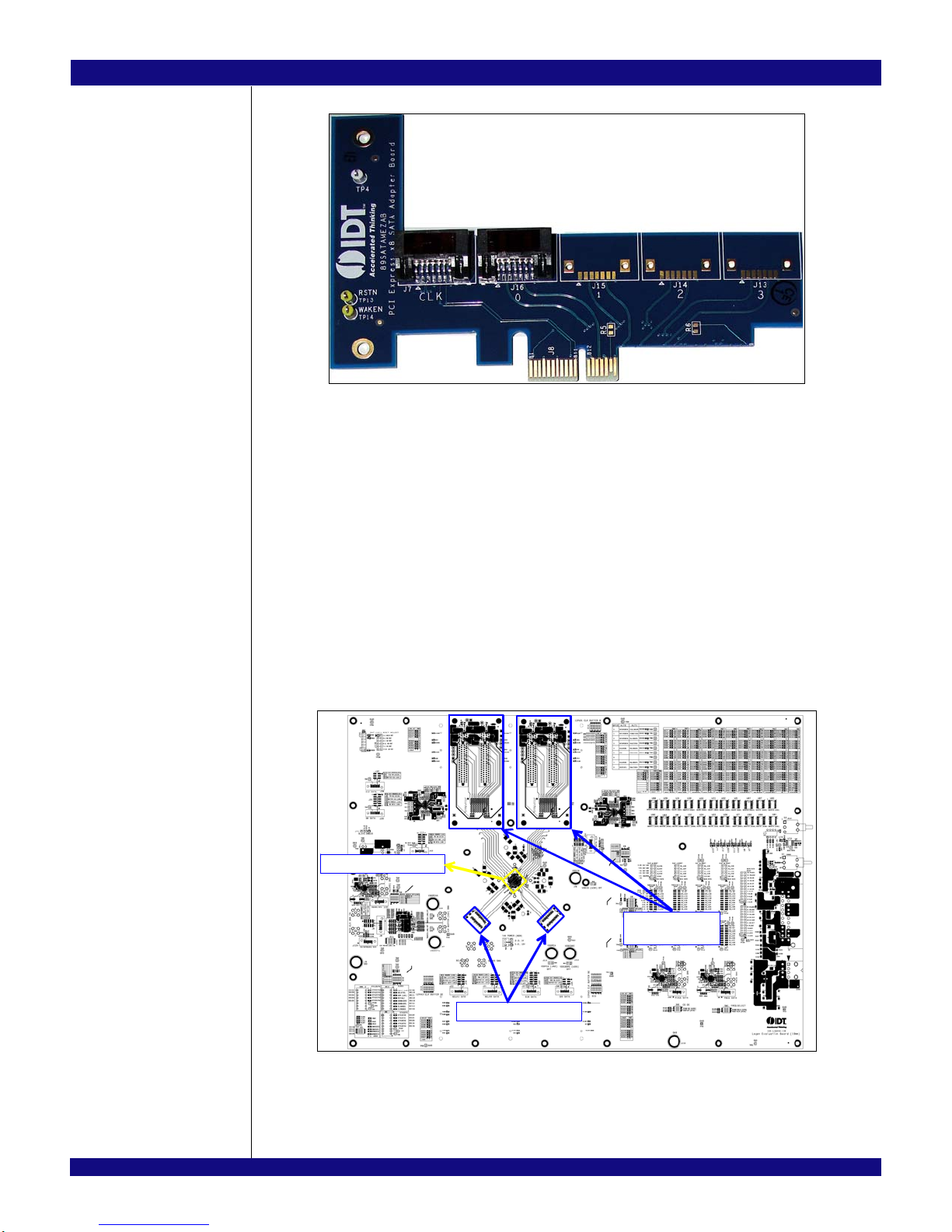

The PCI Express Edge to SATA Adapter, pictured in Figure 2.4, can be inserted into any physical PCIe

slot on a host system and in combination with mini-SAS Mezzanine Card, such as the one in Figure 2.2, to

form a link between evaluation main board and the host system. There are 5 SATA connectors which one

connector (J7) is for clock and reset, and the rest supports one PICe lane per SATA connector. The edge

adapters can be inserted into a mechanical x1 or greater slot.

89EB-LOGAN-19 Evaluation Board 2 - 2 February 16, 2011

Page 15

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Figure 2.4 PCIe x1 Edge-to-SATA Adapter

Hardware Description

The PES24NT24G2 is a 24-lane, 24-port PCI Express® switch. It is a peripheral chip that performs PCI

Express based switching with a feature set optimized for high performance applications such as servers

and storage. It provides fan-out and switching functions between a PCI Express upstream port and down

stream ports or peer-to-peer switching between downstream ports. Furthermore, up to eight ports can be

configured as NTB ports for multi-root application.

-

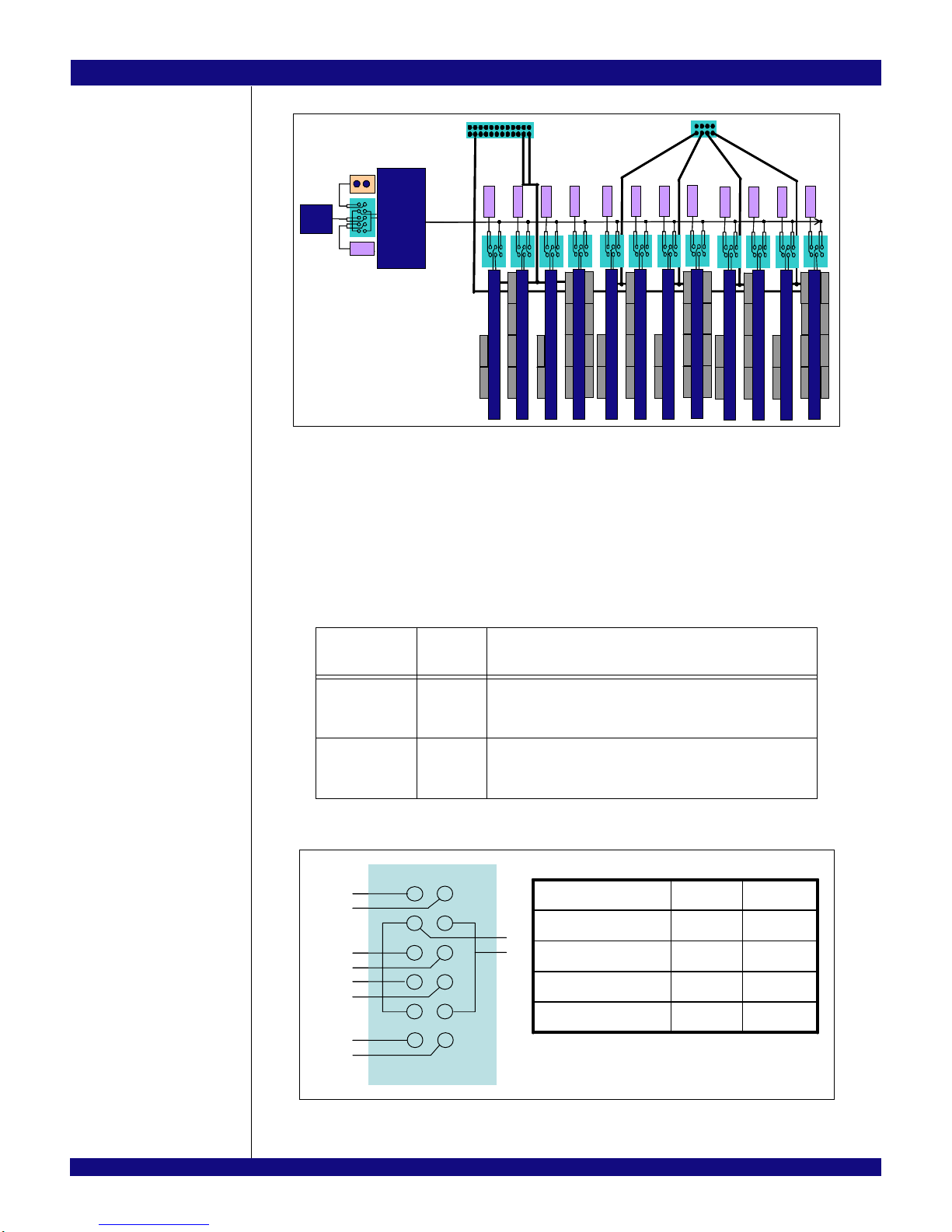

The EB-LOGAN-19 Main Board, shown in Figure 2.5, will support up to 4 PCI Express downstream

ports and up to 23 ports when using two 12PACK Daughter Boards.

Basic requirements for the board to run are:

– Host system with a PCI Express root complex supporting x1 configuration through a PCI Express

x1 slot.

– – x1, x2, x4, or x8 PCI Express Endpoint Cards.

DUT on bottom side

DUT on bottom side

Me zzto tw o x 4

Me zzto tw o x 4

slot connectors

slot connectors

x4 iSAS connectors

x4 iSAS connectors

89EB-LOGAN-19 Evaluation Board 2 - 3 February 16, 2011

Figure 2.5 EB-LOGAN-19 Evaluation Main Board

Page 16

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

8-PIN EPS 12V

8-PIN EPS 12V

+12

+12

SATA

SATA

SATA

SATA

SATA

CL K

CL K

S

S

A

A

T

T

A

A

S

S

A

A

T

T

S

S

S

S

A

A

L

L

L

L

O

O

O

O

S

S

S

S

A

A

A

A

T

T

T

T

T

T

T

T

A

A

A

A

7

6

7

6

S

S

S

S

A

A

A

A

T

T

T

T

A

A

A

A

x4

x4

Data

Data

SATA

SATA

SATA

CLK

CLK

S

S

L

L

O

O

S

S

A

A

T

T

T

T

A

A

5

5

S

S

A

A

T

T

A

A

x2

x2

Data

Data

SATA

SATA

SATA

SATA

SATA

CLK

CLK

CLK

CLK

S

S

A

A

T

T

A

A

S

S

A

A

T

T

A

A

S

S

A

A

T

T

A

A

S

S

A

A

T

T

A

A

x8

x8

Dat a

Dat a

CLK

CLK

S

S

S

S

A

A

A

A

T

T

T

T

A

A

A

A

S

S

S

S

A

A

A

A

T

T

T

S

S

L

L

O

O

T

T

4

4

T

S

S

S

A

A

S

S

A

A

T

T

A

A

S

S

A

A

T

T

A

A

S

A

A

L

L

L

L

O

O

O

O

S

S

S

S

A

A

A

A

T

T

T

T

T

T

T

T

A

A

A

A

3

2

3

2

S

S

S

S

A

A

A

A

T

T

T

T

A

A

A

A

x2

x2

x4

x4

Dat a

Dat a

Data

Data

SATA

SATA

SATA

CLK

CLK

CLK

S

S

A

A

T

T

A

A

S

S

A

A

T

T

A

A

x2

x2

Data

Data

CLK

CLK

CLK

S

S

S

S

A

A

A

A

T

T

T

T

A

A

A

A

S

S

S

S

A

A

A

A

T

T

T

T

S

S

S

S

A

A

A

A

L

L

L

L

O

O

O

O

S

S

S

S

A

A

A

A

T

T

T

T

T

T

T

T

A

A

A

A

1

1

0

0

S

S

S

S

A

A

A

A

T

T

T

T

A

A

A

A

x8

x8

Data

Data

On-Board

On-Board

Clock Gen

Clock Gen

SMA

SMASMA

SATA

SATA

1:12

1:12

Buffe r

Buffe r

24-PIN ATX

24-PIN ATX

clk[0:11]

clk[0:11]

+3.3

+3.3

SATA

SATA

S

S

A

A

T

T

A

A

S

S

A

A

T

T

A

A

x2

x2

Data

Data

+12

+12

SATA

SATA

SATA

CLK

CLK

S

S

A

A

T

T

A

A

S

S

A

A

T

T

S

S

S

S

A

A

L

L

L

L

O

O

O

O

S

S

A

A

T

T

T

T

T

T

A

A

1

1

1

1

S

S

1

0

1

0

A

A

T

T

A

A

x4

x4

Data

Data

SATA

SATA

SATA

CLK

CL K

CL K

S

S

A

A

T

T

A

A

S

S

A

A

T

T

A

A

x2

x2

Data

Data

CLK

CLK

CLK

S

S

S

S

A

A

A

A

T

T

T

T

A

A

A

A

S

S

S

S

A

A

A

A

T

T

T

T

S

S

S

S

A

A

A

A

L

L

L

L

O

O

O

O

S

S

S

S

A

A

A

A

T

T

T

T

T

T

T

T

A

A

A

A

8

8

9

9

S

S

S

S

A

A

A

A

T

T

T

T

A

A

A

A

x8

x2

x8

x2

Data

Data

Data

Data

Figure 2.6 12PACK PCIe Slots Breakout Daughter Board

Reference Clocks

Global Reference Input Clocks

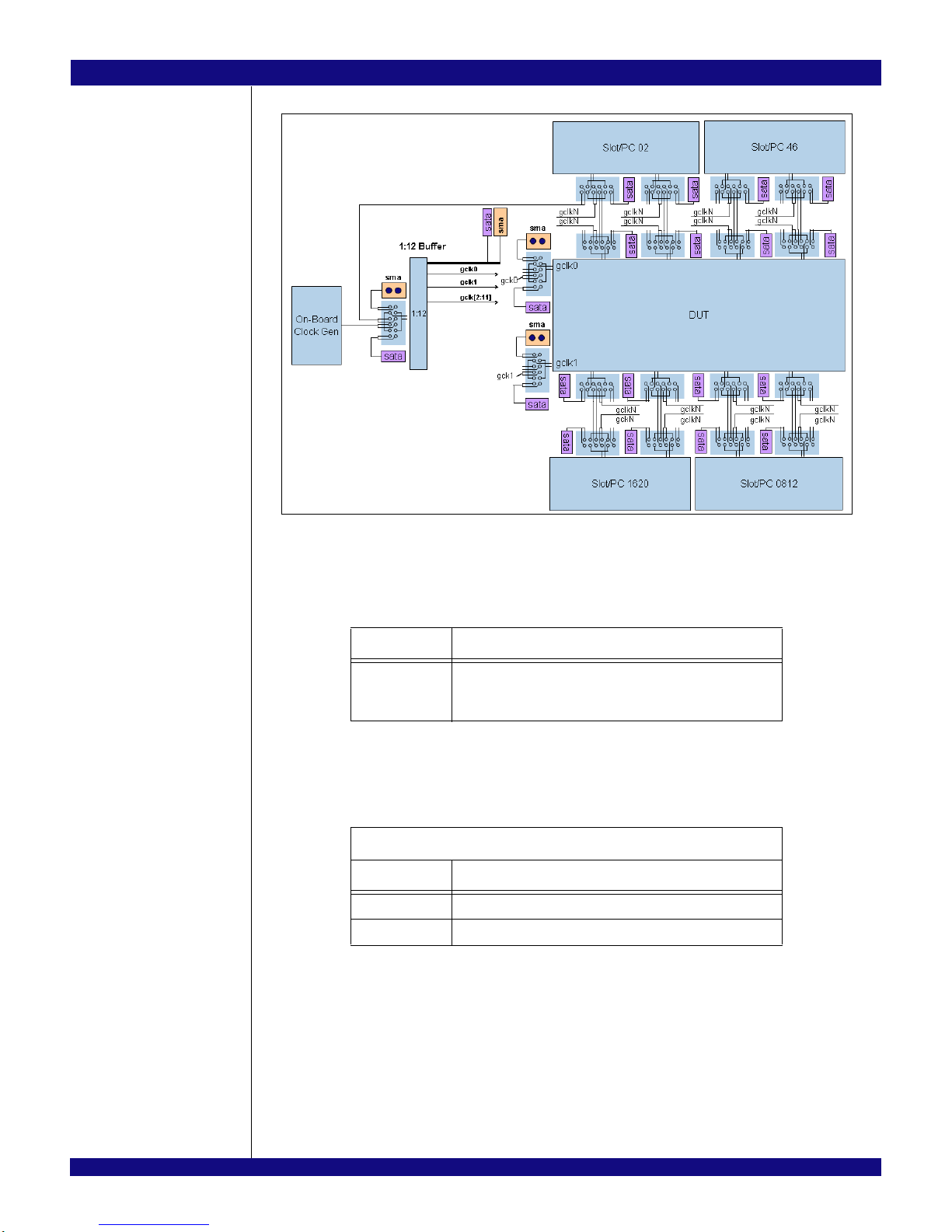

The PES24NT24G2 requires two differential reference clocks. The EB-LOGAN-19 derives these clocks

from SMA connectors (J17, J20, J66, J67), clock buffer (U50), or SATA connectors (J21, J22) as described

in

Table 2.1 and Figures 2.7 and 2.8.

IOA

IOA

IOB

IOB

IOC

IOC

IOD

IOD

Global

Clock#

Jumper Selection

0 J18 [1-3 / 2-4] SMA (J66/J67)

[5-7 /6-8] From Clock Buffer U51 (default)

[7-9 / 8-10] SATA, J21

1 J19 [1-3 / 2-4] SMA (J17/J20)

[5-7 /6-8] From Clock Buffer U51 (default)

[7-9 / 8-10] SATA, J22

Table 2.1 EB-LOGAN-19 Global Clock Select

1

1

3

3

5

5

7

7

9

9

11

11

2

2

4

4

6

6

8

8

10

10

12

12

JMP2JMP1CONNECTION

JMP2JMP1CONNECTION

2-41-3IOA <-> COM

2-41-3IOA <-> COM

4-63-5IOB <-> COM

4-63-5IOB <-> COM

8-107-9IOC <-> COM

8-107-9IOC <-> COM

10-129-11IOD <-> COM

10-129-11IOD <-> COM

89EB-LOGAN-19 Evaluation Board 2 - 4 February 16, 2011

Figure 2.7 Differential Jumper Arrangement

Page 17

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Figure 2.8 Reference Clock Configuration

By default the clock buffer derives its clock from a common source. The common source can be the host

system’s reference clock, the onboard clock generator, or SATA connector (J8). See

Table 2.2.

.

Jumper Selection

J6 [1-3 / 2-4] SMA (J5/J7)

[5-7 / 6-8] Onboard Clock Generator (U49)

[7-9 / 8-10] SATA (J8) (default)

Table 2.2 Clock Buffer Input Sources

The frequency of the global reference clock input may be selected by the Clock Frequency Select

(GCLKFEL) pin to be either 100 MHz or 125 MHz as described in

Global Clock Frequency Switch - SW10[2

SW10[2] Clock Frequency

ON 100 MHz (Default)

OFF 125 MHz

Table 2.3 Global Reference Input Clock Frequency Select

Table 2.3.

The source for the onboard clock is the ICS841484 clock generator device (U49) connected to a 25MHz

oscillator (X1). When using the onboard clock generator, the output frequency is fixed at 100MHz. There

fore, ICS_FS (S10, bit 1) is ON as the default setting. See Table 2.4.

89EB-LOGAN-19 Evaluation Board 2 - 5 February 16, 2011

-

Page 18

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Onboard Clock Frequency Switch - S10[1]

S10[1] Clock Frequency

ON 100 MHz (Default)

OFF 125 MHz

Table 2.4 Onboard Clock Generator Frequency Select

The output of the onboard clock generator is accessible through two yellow colored loop connectors

located on the Evaluation Board. See

capturing purposes and cannot be used to drive the clock from an external source.

Onboard Reference Clock Output (Differential)

J119 Positive Reference Clock

J120 Negative Reference Clock

J121 SATA Reference Clock

Table 2.5 Onboard Reference Clock Generator Access Points

Table 2.5. This can be used to connect a scope for probing or

Local Port Input Clocks

Associated with some ports is a port reference clock input (PxCLK). Depending on the port clocking

mode, a differential reference clock is driven into the device on the corresponding PxCLKP and PxCLKN

pins. The frequency of a port reference clock input is always 100 MHz.

Table 2.6 lists the possible sources

for the port reference clock input, and Table 2.7 lists the possible sources for the slot clock input.

Port # Header Selection

8 J13 [1-3 / 2-4] Onboard Clock Generator (U118)

[5-7 / 6-8] Slot Clock Header (J31)

[7-9 / 8-10] SATA (J62) (default)

16 J15 [1-3 / 2-4] Onboard Clock Generator (U120)

[5-7 / 6-8] Slot Clock Header (J33)

[7-9 / 8-10] SATA (J64) (default)

Table 2.6 EB24NT24G2 Port Clock Select

Slot/Port # Header Selection

8 J31 [1-3 / 2-4] Onboard Clock Generator (U118)

[3-5 / 4-6] From Clock Buffer (default)

[7-9 / 8-10] To P08CLK Clock Header (J13)

[9-11 / 8-10] SATA (J35)

89EB-LOGAN-19 Evaluation Board 2 - 6 February 16, 2011

Table 2.7 EB-LOGAN-19 Slot Clock Select (Part 1 of 2)

Page 19

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Slot/Port # Header Selection

12 J32 [1-3 / 2-4] From Clock Buffer (default)

[3-5 / 4-6] SATA (J36)

16 J33 [1-3 / 2-4] Onboard Clock Generator (U120)

[3-5 / 4-6] From Clock Buffer (default)

[7-9 / 8-10] To P16CLK Clock Header (J15)

[9-11 / 8-10] SATA (J37)

20 J34 [1-3 / 2-4] From Clock Buffer (default)

[3-5 / 4-6] SATA (J38)

Table 2.7 EB-LOGAN-19 Slot Clock Select (Part 2 of 2)

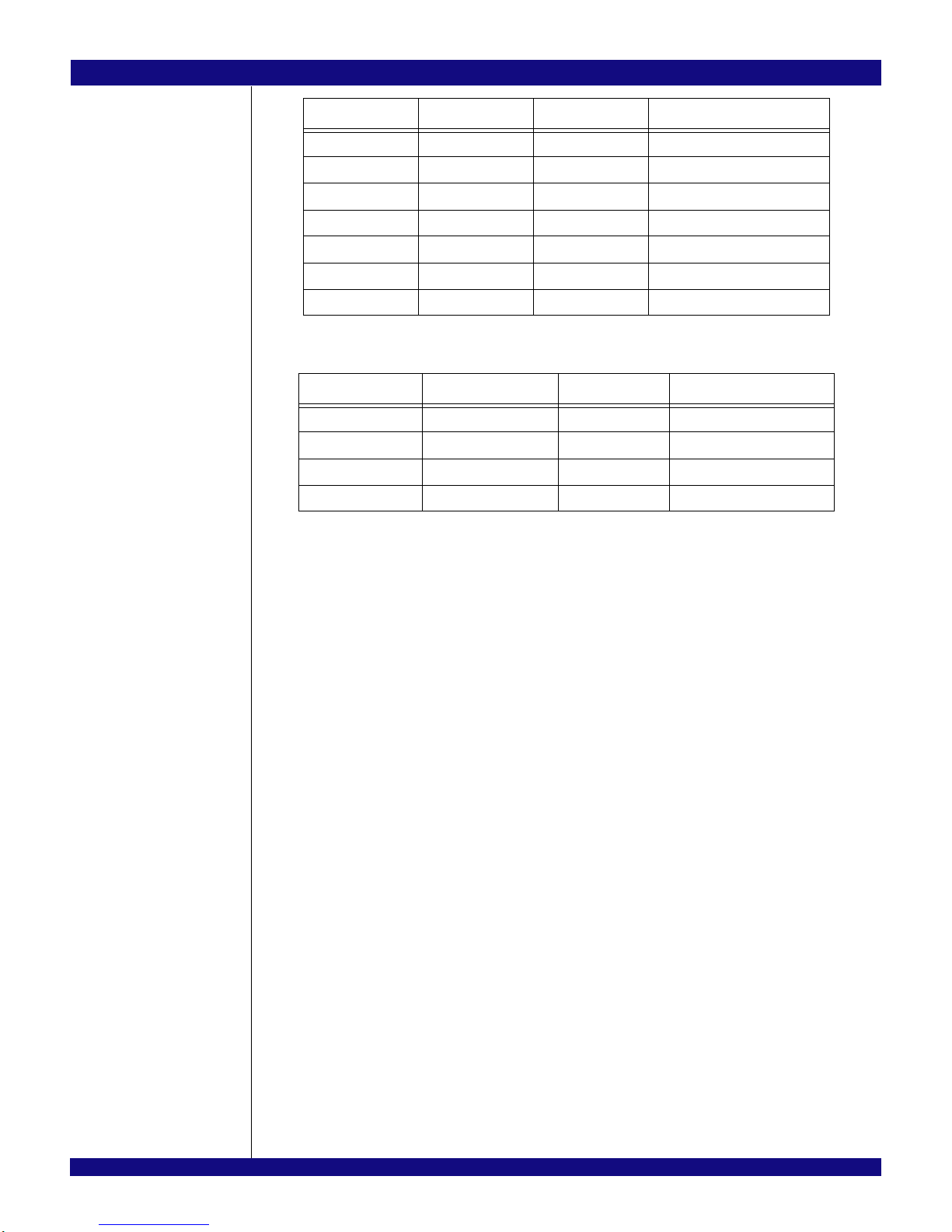

CLKMODE Selection

All ports in the PES24NT24G2 device (upstream and downstream) use global clocked mode. The port

clocking mode of a port is determined by the state of the CLKMODE[1:0] pins in the boot configuration

vector as shown in

Table 2.8. This field determines the initial value of the Slot Clock Configuration (SCLK)

field in each port’s PCI Express Link Status (PCIELSTS) register. The SCLK field controls the advertisement of whether or not the port uses the same reference clock source as the link partner. A one in the SCLK

field indicates that the port and its link partner use the same reference clock source. This is defined as

Common Clock Configuration by the PCI Express Base Specification. A zero in the SCLK field indicates

that the port and its link partner do not use the same reference clock source.

SW10[8]

CLKMODE[0]

SW10[7]

CLKMODE[1]

Port 0

SCLK

Port[23:1]

SCLK

ON ON 0 0

OFF ON 1 0

ON OFF 0 1

OFF OFF 1 1

Table 2.8 CLKMODE Selection PES24NT24G2

Power Sources

Power for the PES24NT24G2 and all downstream ports will be generated from the 12V from an external

power connector. See

Table 2.9. A 12V to 3.3V DC-DC converter will be used to provide power to five

switching regulators to generate VDDCORE, VDDPEA, VDDPETA, VDDPEHA, and VDDIO voltages. The

3.3V from the DC-DC converter will be used to power the clock buffers and circuitries.

The external power supply connectors are 24-pin (J69) and 8-pin (J68) molex connector as described in

Tables

2.9 and 2.10. The +12V3 is used to power PES32NT24AG2 and downstream slots 16 and 20. The

+12V2 is used to power downstream slots 8 and 12.

Pin Signal Pin Signal

1 +3.3V 13 +3.3V

2 +3.3V 14 -12V

3 GND 15 GND

4 +5V 16 PS_ON

5 GND 17 GND

89EB-LOGAN-19 Evaluation Board 2 - 7 February 16, 2011

Table 2.9 EPS12V 24-pin Power Connector - J6 (Part 1 of 2)

Page 20

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Pin Signal Pin Signal

6 +5V 18 GND

7 GND 19 GND

8 PWR_OK 20 NC

9 5VSB 21 +5V

10 +12V3 22 +5V

11 +12V3 23 +5V

12 +3.3V 24 GND

Table 2.9 EPS12V 24-pin Power Connector - J6 (Part 2 of 2)

Pin Signal Pin Signal

1 GND 5 +12V1

2 GND 6 +12V1

3 GND 7 +12V2

4 GND 8 +12V2

Table 2.10 EPS12V 8-Pin Connector - J5

The power on switch located at S1 can be used to control the supply power from the external power

supply connector. Add a shunt to W27 to enable power on switch.

PCI Express Analog Power Voltage Regulator

A voltage regulator (U65) provides a 2.5V PCI Express analog power voltage (shown as VDDPEHA) to

the PES24NT24G2.

PCI Express Digital Power Voltage Converter

A separate voltage regulator (U62) provides a 1.0V PCI Express analog power voltage (shown as

VDDPEA) to the PES24NT24G2.

PCI Express Transmitter Analog Voltage Converter

A separate voltage regulator (U68) provides a 1.0V PCI Express transmitter analog voltage (shown as

VDDPETA) to the PES24NT24G2.

Core Logic Voltage Converter

A separate voltage regulator (U59) provides the 1.0V core voltage (VDDCORE) to the PES24NT24G2.

3.3V I/O Voltage Regulator

A separate voltage regulator (U56) provides the 3.3V I/O voltage (VDDIO) to the PES24NT24G2.

Power-up Sequence f or PES24NT24G2

During power supply ramp-up, VDDCORE must remain at least 1.0V below VDDIO at all times. There

are no other power-up sequence requirements for the various operating supply voltages.

Heatsink Requirement

The EB-LOGAN-19 evaluation board utilizes a heatsink with integrated fan.

89EB-LOGAN-19 Evaluation Board 2 - 8 February 16, 2011

Page 21

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Reset

The PES24NT24G2 supports two types of reset mechanisms as described in the PCI Express specifica-

tion:

– Fundamental Reset: This is a system-generated reset that propagates along the PCI Express

tree through a single side-band signal PERST# which is connected to the Root Complex, the

PES24NT24G2, and the endpoints.

– Hot Reset: This is an In-band Reset, communicated downstream via a link from one device to

another. Hot Reset may be initiated by software. This is further discussed in the PES24NT24G2

User Manual. The EB-LOGAN-19 evaluation board provides seamless support for Hot Reset.

Fundamental Reset

There are two types of Fundamental Resets which may occur on the EB-LOGAN-19 evaluation board:

– Cold Reset: During initial power-on, the onboard voltage monitor (TLC7733D) will assert the PCI

Express Reset (PERSTN) input pin of the PES24NT24G2.

– Warm Reset: This is triggered by hardware while the device is powered on. Warm Reset can be

initiated by two methods:

• Pressing a push-button switch (S3) located on EB-LOGAN-19 board

• The host system board IO Controller Hub asserting PERST# signal, which propagates through

the PCIe upstream edge connector of the EB-LOGAN-19.

Both events cause the onboard voltage monitor (TLC7733D) to assert the PCI Express Reset

(PERSTN) input of the PES24NT24G2 while power is on.

Downstream Reset

Single Partition Mode without Hot Plug:

When the evaluation board initially powers on is assumes the following:

The switch is configured in single partition mode.

Slot 0 is the root port and controls the downstream port resets.

Ports 1-23 are downstream ports.

Hot Plug is disabled.

The following behavior should be observed:

The resets to slots 1-23 should initially be asserted and remain this way until after the fundamental

reset is initially de-asserted.

The assertion of slot 0 reset should propagate to slots 1-23.

Stack Configuration

The PES24NT24G2 contains four stack blocks labeled Stack 0, Stack 1, Stack 2, and Stack 3. Stacks 0

and 1 have four x1 ports each, and stacks 2 and 3 have eight x1 ports each. This provides a total of 24

ports in the device labeled port 0 through port 23.

Table 2.11 lists the ports associated with each stack.

Stacks 0 and 1 have non-mergeable x1 ports. Stacks 2 and 3 may be configured as eight x1 ports, four

x2 ports, two x4 ports, one x8 port, and any combinations in between. The configuration of each stack is

controlled by the Stack Configuration (STK[3:2]CFG) registers. For possible configurations please refer to

the device user manual.

89EB-LOGAN-19 Evaluation Board 2 - 9 February 16, 2011

Page 22

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Stack

Stack 0 0, 1, 2, 3

Stack 1 4, 5, 6, 7

Stack 2 8, 9, 10, 11, 12, 13, 14, 15

Stack 3 16, 17, 18, 19, 20, 21, 22, 23

Ports Associated with the

Stack

Table 2.11 Ports in Each Stack

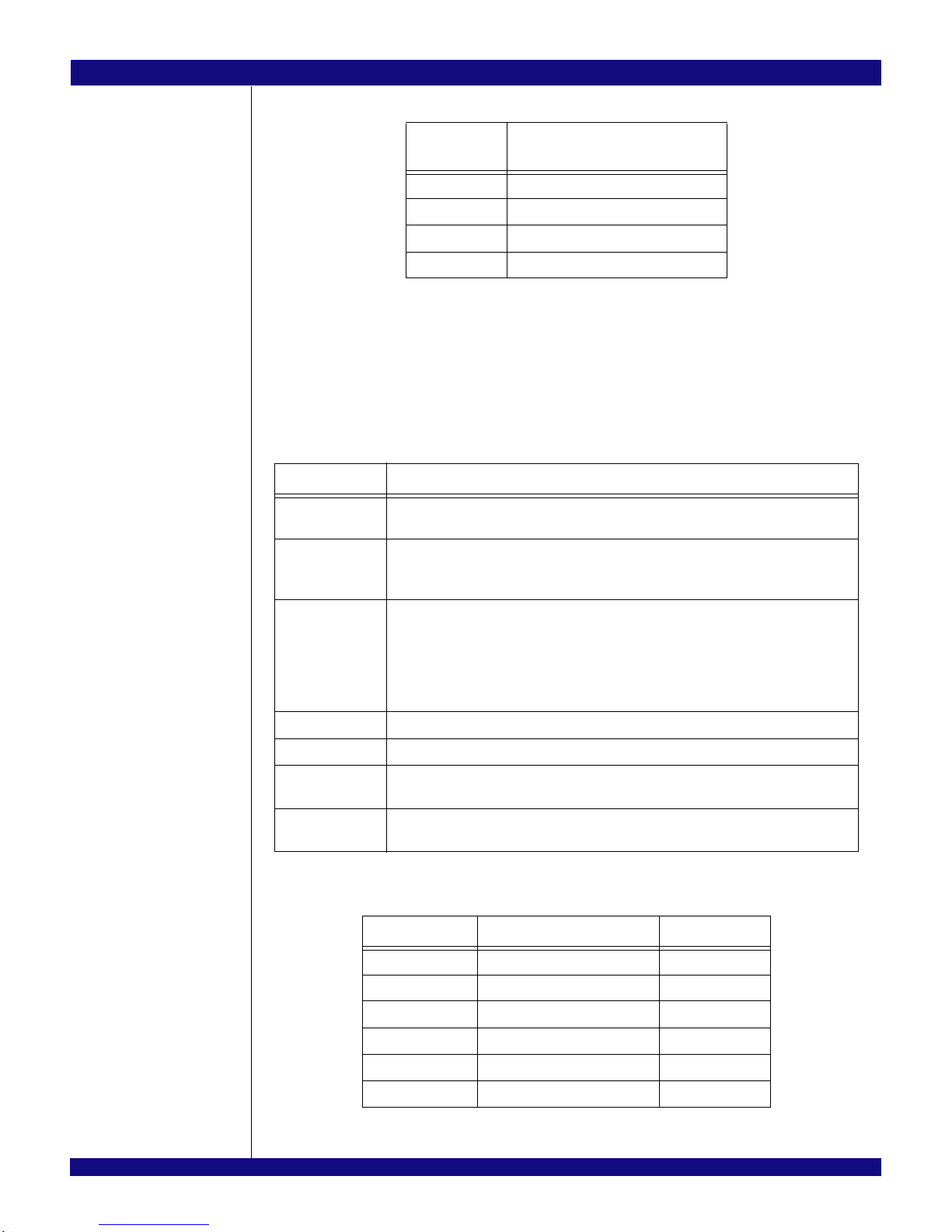

Boot Configuration Vector

A boot configuration vector consisting of the signals listed in Table 2.12 is sampled by the

PES24NT24G2 during a fundamental reset (while PERSTN is active). The boot configuration vector defines

the essential parameters for switch operation and is set using DIP switches S5, SW8, SW9 and SW10 as

defined in

Table 2.13.

Signal Description

GCLKFSEL Global Clock Frequency Select. This pin specifies the frequency of the GCLKP and

GCLKN signals.. Default: low

CLKMODE[1:0] Clock Mode. These pins specify the clocking mode used by switch ports. See Table 2.8 for

a definition of the encoding of these signals. The value of these signals may be overridden

by modifying the Port Clocking Mode (PCLKMODE) register.. Default: 0x3

RSTHALT Reset Halt. When this pin is asserted during a switch fundamental reset

sequence, the switch remains in a quasi-reset state with the Master and Slave SMBuses

active. This allows software to read and write registers internal to the device before normal

device operation begins. The device exits the quasi-reset state when the RSTHALT

bit is cleared in the SWCTL register by an SMBus master. Refer to section Switch Fundamental Reset on page 3-2 for further details. Default: low

SSMBADDR[2:1] Slave SMBus Address. SMBus address of the switch on the slave SMBus. Default: 0x3

SWMODE[3:0] Switch Mode. These pins specify the switch operating mode. Default: 0x0

STK2CFG[4:0] Stack 2 Configuration. These pins select the configuration of stack 2 during a switch fun-

STK3CFG[4:0] Stack 3 Configuration. These pins select the configuration of stack 3 during a switch fun-

89EB-LOGAN-19 Evaluation Board 2 - 10 February 16, 2011

damental reset. Default: 0x1

damental reset. Default: 0x1

Table 2.12 Boot Configuration Vector Signals

Location Signal Default

S5[1] SWMODE[0] ON

S5[2] SWMODE[1] ON

S5[3] SWMODE[2] ON

S5[4] SWMODE[3] ON

SW8[1] STK2CFG[0] OFF

SW8[2] STK2CFG[1] ON

Table 2.13 Boot Configuration Vector Switches S5, SW8 - SW10 (Part 1 of 2)

Page 23

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Location Signal Default

SW8[3] STK2CFG[2] ON

SW8[4] STK2CFG[3] ON

SW8[5] STK2CFG[4] ON

SW9[1] STK3CFG[0] OFF

SW9[2] STK3CFG[1] ON

SW9[3] STK3CFG[2] ON

SW9[4] STK3CFG[3] ON

SW9[5] STK3CFG[4] ON

SW10[2] GCLKFSEL ON

SW10[4] RSTHALT ON

SW10[5] SSMBADDR[2] OFF

SW10[6] SSMBADDR[1] OFF

SW10[7] CLKMODE[1] OFF

SW10[8] CLKMODE[0] OFF

Table 2.13 Boot Configuration Vector Switches S5, SW8 - SW10 (Part 2 of 2)

SMBus Interfaces

The System Management Bus (SMBus) is a two-wire interface through which various system compo-

nent chips can communicate. It is based on the principles of operation of I2C. Implementation of the SMBus

signals in the PCI Express connector is optional and may not be present on the host system. The SMBus

interface consists of an SMBus clock pin and an SMBus data pin.

The PES24NT24G2 contains two SMBus interfaces: a slave SMBus interface and a master SMBus

interface. The slave SMBus interface allows a SMBus Master device full access to all software-visible regis

ters. The Master SMBus interface provides a connection to the external serial EEPROM used for initialization and the I/O expanders used for hot-plug signals.

SMBus Slave Interface

On the PES24NT24G2 board, the slave SMBus interface is accessible through a 4-pin header as

described in

Table 2.14.

.

Slave SMBus Interface Connector J71

Pin Signal

1 SDA

2 GND

3 SCL

4 NC

-

For a fixed address, the SMBus address of the PES24NT24G2 slave interface is 0b1110111 by default

and is configurable using DIP Switches SW10[5] and SW10[6] as described in

89EB-LOGAN-19 Evaluation Board 2 - 11 February 16, 2011

Table 2.14 Slave SMBus Interface Connector

Table 2.15.

Page 24

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Slave Interface Address Configuration

Address Bit Signal

1 SSMBUSADDR[1]

2 SSMBUSADDR[2]

3 1

4 0

5 1

6 1

7 1

Table 2.15 SMBus Slave Interface Address Configuration

The slave SMBus interface responds to the following SMBus transactions initiated by an SMBus master.

Initiation of any SMBus transaction other than those listed above produces undefined results. See the

SMBus 2.0 specification for a detailed description of the following transactions:

– Byte and Word Write/Read

– Block Write/Read

SMBus Master Interface

Connected to the master SMBus interface are twenty-two 16-bit I/O Expanders (MAX7311AUG) and a

serial EEPROM, U77 (24LC512). The I/O Expanders are used as the interface for the onboard hot-plug

controllers (MIC2591B). The lower three bits of the bus address for the I/O Expander 0 through I/O

Expander 20 are fixed through the stuffing resistor as 0x20, 0x22, 0x24, 0x26, 0x28, 0x2A, 0x2C, 0x2E,

0x50, 0x52, x54, 0x56, 0x58, 0x5A, 0x5C, 0x5E, 0xB0, 0xA2, 0xA4, 0xA6, 0xA8, and 0xAA, respectively.

Note: Hot-plug is not implemented when the PES24NT24G2 is installed.

The seven bits address for the selected EEPROM device is fixed at 0b1010_000 by default.

JTAG Header

The EB-LOGAN-19 provides a JTAG connector J73 for access to the PES24NT24G2 JTAG interface.

The connector is a 2.54 x 2.54 mm pitch male 14-pin connector . Refer to

J73 pin out.

JTAG Connector J73

Pin Signal Direction Pin Signal Direction

1 /TRST - Test reset Input 2 GND —

3 TDI - Test data Input 4 GND —

5 TDO - Test data Output 6 GND —

7 TMS - Test mode select Input 8 GND —

9 TCK - Test clock Input 10 GND —

11 3.3V 12 N/C —

13 GND — 14 3.3V

T able 2.16 for the JTAG Connector

89EB-LOGAN-19 Evaluation Board 2 - 12 February 16, 2011

Table 2.16 JTAG Connector Pin Out

Page 25

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

PCI Express Connectors

Pin Side A Side B

1 +12V 12V power PRSNT1# Hot-Plug presence detect

2 +12V 12V power +12V 12V power

3 RSVD Reserved +12V 12V power

4 GND Ground GND Ground

5 SMCLK SMBus clock JTAG2 TCK (Test Clock) JTAG i/f clk i/p

6 SMDAT SMBus Data JTAG TDI (Test Data Input)

7 GND Ground JTAG TDO (Test Data Output)

8 +3.3V 3.3V power JTAG TMS (Test Mode Select)

9 JTAG1 TRST# (Test/Reset) resets

JTAG i/f

10 3.3Vaux 3.3V auxiliary power +3.3V 3.3V power

11 WAKE# Signal for Link reactivation PERST# Fundamental Reset

Mechanical Key

12 RSVD Reserved GND Ground

13 GND Ground REFCLK+ REFCLK Reference clock

14 PETp0 Transmitter differential REFCLK- (differential pair)

15 PETn0 pair, Lane 0 GND Ground

+3.3V 3.3V power

16 GND Ground PERp0 Receiver differential

17 PRSNT2# Hot-Plug presence detect PERn0 pair, Lane 0

18 GND Ground GND Ground

19 PETp1 Transmitter differential RSVD Reserved

20 PETn1 pair, Lane 1 GND Ground

21 GND Ground PERp1 Receiver differential

22 GND Ground PERn1 pair, Lane 1

23 PETp2 Transmitter differential GND Ground

24 PETn2 pair, Lane 2 GND Ground

25 GND Ground PERp2 Receiver differential

26 GND Ground PERn2 pair, Lane 2

27 PETp3 Transmitter differential GND Ground

28 PETn3 pair, Lane 3 GND Ground

29 GND Ground PERp3 Receiver differential

30 RSVD Reserved PERn3 pair, Lane 3

31 PRSNT2# Hot-Plug presence detect GND Ground

32 GND Ground RSVD Reserved

33 PETp4 Transmitter differential RSVD Reserved

89EB-LOGAN-19 Evaluation Board 2 - 13 February 16, 2011

Table 2.17 PCI Express x8 Connector Pinout (Part 1 of 2)

Page 26

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

Pin Side A Side B

34 PETn4 pair, Lane 4 GND Ground

35 GND Ground PERp4 Receiver differential

36 GND Ground PERn4 pair, Lane 4

37 PETp5 Transmitter differential GND Ground

38 PETn5 pair, Lane 5 GND Ground

39 GND Ground PERp5 Receiver differential

40 GND Ground PERn5 pair, Lane 5

41 PETp6 Transmitter differential GND Ground

42 PETn6 pair, Lane 6 GND Ground

43 GND Ground PERp6 Receiver differential

44 GND Ground PERn6 pair, Lane 6

45 PETp7 Transmitter differential GND Ground

46 PETn7 pair, Lane 7 GND Ground

47 GND Ground PERp7 Receiver differential

48 PRSNT2# Hot-Plug presence detect PERn7 pair, Lane 7

49 GND Ground GND Ground

Table 2.17 PCI Express x8 Connector Pinout (Part 2 of 2)

89EB-LOGAN-19 Evaluation Board 2 - 14 February 16, 2011

Page 27

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

EB-LOGAN-19 Board Figure

Figure 2.9 EB24NT24G2 Evaluation Board

89EB-LOGAN-19 Evaluation Board 2 - 15 February 16, 2011

Page 28

IDT Installation of the EB-LOGAN-19 Evaluation Board

Notes

89EB-LOGAN-19 Evaluation Board 2 - 16 February 16, 2011

Page 29

Chapter 3

Software for the EB-LOGAN-19

Eval Board

®

Notes

Introduction

This chapter discusses some of the main features of the available software to give users a better understanding of what can be achieved with the EB-LOGAN-19 evaluation board using the device management

software.

Device management software and related user documentation are available on a CD which is included

in the Evaluation Board Kit. This information is also available on IDT FTP site and also at my.idt.com. For

more information, please go to:

email IDT at ssdhelp@idt.com.

http://www.idt.com/?app=TechSupport&prodFamily=PCIe%20Switches or

Device Management Software

The primary use of the Device Management Software package is to enable users of the evaluation

board to access all the registers in the PES24NT24G2 device. This access can be achieved using the PCI

Express in-band configuration cycles through the upstream port on the PES24NT24G2 or through the

SMBUS salve interface available on the IDT PCIe switch.

This software also enables users to save a snapshot of the current register set into a dump file which

can be used for debugging purposes. An export/import facility is also available to create and use “Configu

ration” files which can be used to initialize the switch device with specific values in specific registers.

A conversion utility is also provided to translate a configuration file into an EEPROM programmable data

structure. This enables the user to program an appropriate serial EEPROM with desirable register settings

for the PES24NT24G2, and then to populate that EEPROM onto the Evaluation Board. It is also possible to

program the EEPROM directly on the Evaluation Board using a feature provided by the software package.

The front-end of the Device Management Software is a user-friendly Graphical User Interface which

allows the user to quickly read or write the registers of interest. The GUI also permits the user to run the

software in “simulation” mode with no real hardware attached, allowing the creation of configuration files for

the PES24NT24G2 in the absence of the actual device.

-

Much of the Device Management Software is written with device-independent and OS-independent

code. The software is expected to work on Linux (/sys interface) and MS Windows XP. It may function well

on various flavors of MS Windows, but may not be validated on all. The fact that the software is device-inde

pendent assures its scalability to future PCIe parts from IDT. Once users are familiar with the GUI, they will

be able to use the same GUI on all PCIe parts from IDT. This software is customized for each device

through an XML device description file which includes information on the number of ports, registers, types

of registers, information on bit-fields within each register, etc.

The actual program name of the Device Management Software is “PCIeBrowser” (an executable file

under Windows or Linux). Revision 5.0.1 or later is required for devices in the PES24NT24G2 product

family family.

Device Drivers

The PES24NT24G2 and other members of this switch family offer Non-Transparent Bridging and built-in

DMA capability inside the device. Device drivers are needed to take advantage of these features. Sample

code for these drivers is available from IDT for the Linux operating system. Additionally, there a few other

software packages available from IDT. These packages are not related to the evaluation board per se, and

therefore not listed here. However, several of these packages may prove to be useful for specific device or

system functionality. For more information, please go to

Family=PCIe%20Switches or email IDT at ssdhelp@idt.com.

89EB-LOGAN-19 Evaluation Board 3 - 1 February 16, 2011

http://www.idt.com/?app=TechSupport&prod-

-

Page 30

IDT Software for the EB-LOGAN-19 Eval Board

Notes

89EB-LOGAN-19 Evaluation Board 3 - 2 February 16, 2011

Page 31

Chapter 4

Schematics

®

Notes

Schematics

89EB-LOGAN-19 Evaluation Board 4 - 1 February 16, 2011

Page 32

TITLE PAGE / TABLE OF CONTENTS

1.

MEZZANINE CONNECTOR PORTS 16, 20

24NT24AG2 - CLK, CONFIG, GPIO

PORT 8 CLOCK GENERATOR

PORT 16 CLOCK GENERATOR

POWER REGULATOR - VDDIO

POWER REGULATOR - VDDCORE

POWER REGULATOR - VDDPEA

POWER REGULATOR - VDDPEHA

POWER REGULATOR - VDDPETA

MIN LOAD RESISTORS

LED - PORT STATUS (6 OF 7)

LED - PORT STATUS (5 OF 7)

LED - PORT STATUS (4 OF 7)

LED - PORT STATUS (3 OF 7)

LED - PORT STATUS (2 OF 7)

LED - PORT STATUS (1 OF 7)

DIP SWITCHES

RESET, SMBUS, EEPROM, JTAG

22.

23.

24.

25.

26.

27.

31.

32.

28.

29.

30.

33.

34.

36.

35.

SLOT RESET SELECT HEADERS

PARTITION RESET SELECT HEADERS

12PK RIBBON CONNECTORS

41.

40.

39.

38

37.

CLOCK SELECTOR - DUT PCLK 0-20, GCLK 1-2

SLOT RESETS AND WAKE PULL-UPS

HOT PLUG CONTROL PORTS 16-20

HOT PLUG CONTROL PORTS 8-12

24NT24AG2 - SERDES

24NT24AG2 - POWER, GND

IOEXPANDER 0-3

IOEXPANDER 4-7

IOEXPANDER 8-11

IOEXPANDER 12-13

IOEXPANDER 16-19

IOEXPANDER 20-21

3.

16.

15.

14.

13.

12.

11.

10.

9.

7.

4.

6.

8.

POWER CONNECTORS

CLOCK SELECTOR - SLOTS 0-20

CLOCK BUFFER - 1

CLOCK

21.

20.

19.

18.

17.

SAS CONNECTOR PORTS 0-7

2.

5.

MEZZANINE CONNECTOR PORTS 8, 12

LED - PORT STATUS (7 OF 7)

Tue Apr 20 12:37:19 2010

SHEET 1 OF 41

EB-LOGAN-19

Tony Tran

2010

SCH-PESEB-002

Derek Huang

1.1

18-692-000

B

1.0 INITIAL RELEASE 2009-12-05 T. TRAN

6

A

TITLE

CHECKED BY

DCN

DESCRIPTION

DATE

REV

8

8

65 4

4

2

2

D

D

CC

BB

A

1

1

REV.

SIZE

3

COPYRIGHT (C) IDT

AUTHOR

DRAWING NO.

REVISIONS

CHANGE BY

3

7

FAB P/N

57

6024 SILVER CREEK VALLEY RD. SAN JOSE, CA 95138

CONFIDENTIAL PROPERTY OF INTEGRATED DEVICE TECHNOLOGY, INC.

Page 33

Tue Apr 20 12:38:25 2010

SHEET 2 OF 41

1.1

18-692-000

Derek Huang

2010

Tony Tran

SCH-PESEB-002

EB-LOGAN-19

B

C81

C80

C76

C73

C71

C68

C67

C63

B16

B17

B13

B14

B5

B6

B2

B3

A8

B11A11

A10

A9

B10

B9

B8

A16

A17

A13

A14

A5

A6

A2

A3

MTG9

MTG8

MTG7

MTG6

MTG5

MTG4

MTG3

MTG2

MTG1

B7

B4

B1

A18

A15

A12

A7

A4

B18

B15

B12

A1

J40

B16

B17

B13

B14

B5

B6

B2

B3

A8

B11A11

A10

A9

B10

B9

B8

A16

A17

A13

A14

A5

A6

A2

A3

MTG9

MTG8

MTG7

MTG6

MTG5

MTG4

MTG3

MTG2

MTG1

B7

B4

B1

A18

A15

A12

A7

A4

B18

B15

B12

A1

J39

C32

C28

C36

C38

C56

C50

C58

C59

5

5

5

5

5

5

5

55

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

SAS CONNECTOR PORTS 0-7

0.1UF

PE07TN0

0.1UF

PE07TP0

0.1UF

PE06TN0

0.1UF

PE06TP0

0.1UF

PE05TN0

0.1UF

PE05TP0

0.1UF

PE04TN0

0.1UF

PE04TP0

0.1UF

PE00TP0

0.1UF

PE00TN0

0.1UF

PE01TP0

0.1UF

PE01TN0

0.1UF

PE02TP0

0.1UF

PE02TN0

0.1UF

PE03TP0

0.1UF

PE03TN0

VERT

PE00RP0

PE00RN0

PE01RP0

PE03RN0

PE03RP0

PE02RN0

PE02RP0

PE01RN0

SMT

PE07RN0

PE07RP0

PE06RN0

PE06RP0

PE05RN0

PE05RP0

PE04RN0

PE04RP0

SMT

VERT

IDT

TITLE

DRAWING NO.

AUTHOR

CHECKED BY

COPYRIGHT (C)

3

SIZE

REV.

FAB P/N

1

1

A A

B B

C C

D

D

2

2

4

45

6

67

7

8

38 5

6024 SILVER CREEK VALLEY ROAD. SAN JOSE, CA 95138

CONFIDENTIAL PROPERTY OF INTEGRATED DEVICE TECHNOLOGY, INC.

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

IN

IN

IN

IN

IN

IN

MOLEX_IPASS_36

MTG9

MTG8

MTG7

MTG6

MTG5

MTG4

MTG3

MTG2

MTG1

GND12

TX3N

TX3P

GND11

TX2N

TX2P

GND10

SB6

SB2

SB1

SB0

GND9

TX1N

TX1P

GND8

TX0N

TX0P

GND7

GND6

RX3N

RX3P

GND5

RX2N

RX2P

GND4

SB5

SB4

SB3

SB7

GND3

RX1N

RX1P

GND2

RX0N

RX0P

GND1

IN

IN

IN

IN

IN

IN

IN

IN

MOLEX_IPASS_36

MTG9

MTG8

MTG7

MTG6

MTG5

MTG4

MTG3

MTG2

MTG1

GND12

TX3N

TX3P

GND11

TX2N

TX2P

GND10

SB6

SB2

SB1

SB0

GND9

TX1N

TX1P

GND8

TX0N

TX0P

GND7

GND6

RX3N

RX3P

GND5

RX2N

RX2P

GND4

SB5

SB4

SB3

SB7

GND3

RX1N

RX1P

GND2

RX0N

RX0P

GND1

Page 34

X4 - STK2CFG1 = 0, STK2CFG0 = 1

X8 - STK2CFG1 = 0, STK2CFG0 = 0

STK2CFG1 & STK2CFG0 SET BY MEZZ CARDS

Tue Apr 20 12:38:31 2010

SHEET 3 OF 41

1.1

18-692-000

Derek Huang

2010

Tony Tran

SCH-PESEB-002

EB-LOGAN-19

B

R32

R31

J51

W19

W17

W15

W13

W11

V20

V18

V16

V14

V12

U19

U17

U15

U13

U11

T20

T18

T16

T14

T12

R19

R17

R15

R13

R11

P20

P18

P16

P14

P12

N19

N17

N15

N13

N11

M20

M18

M16

M14

M12

L19

L17

L15

L13

L11

K20

K18

K16

K14

K12

J19

J17

J15

J13

J11

H20

H18

H16

H14

H12

G19

G17

G15

G13

G11

F20

F18

F16

F14

F12

E19

E17

E15

E13

E11

D20

D18

D16

D14

D12

C19

C17

C15

C13

C11

B20

B18

B16

B14

B12

A19

A17

A15

A13

A11

J3

R27

R28

R30

R29

W9

W7

W5

W3

W1

V8

V6

V4

V2

V10

U9

U7

U5

U3

U1

T8

T6

T4

T2

T10

R9

R7

R5

R3

R1

P8

P6

P4

P2

P10

N9

N7

N5

N3

N1

M8

M6

M4

M2

M10

L9

L7

L5

L3

L1

K8

K6

K4

K2

K10

J9

J7

J5

J3

J1

H8

H6

H4

H2

H10

G9

G7

G5

G3

G1

F8

F6

F4

F2

F10

E9

E7

E5

E3

E1

D8

D6

D4

D2

D10

C9

C7

C5

C3

C1

B8

B6

B4

B2

B10

A9

A7

A5

A3

A1

J3

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

5

8

2937

5

5

5

8

2937

6

28

5

6

28

3

3

16

37

6

343839

20

20

6

343839

16

37

20

20

5

5

5

5

5

5

5

5

5

5

5

5

3

3

470-1075-600 (1 of 2)

PE13TN0

PE13RP0

PE11RN0

PE11TN0

PE11TP0

PE11RP0

PE12TP0

PE12TN0

PE12RN0

PE12RP0

PE13TP0

PE13RN0

PE14TP0

PE14TN0

PE14RP0

PE14RN0

M812_ID<2>

P8_PDN

PE15RN0

PE15TP0

PE15RP0

P12_PDN

STK2CFG1

PE15TN0

STK2CFG0

MEZZ_SMBDAT3

MEZZ_SMBCLK3

SLOT_WAKEN8

SLOT_HDR_RSTN8

S8_CLKP

S8_CLKN

M812_ID<1>

SLOT_HDR_RSTN12

SLOT_WAKEN12

S12_CLKP

S12_CLKN

PE08RP0

PE08RN0

PE08TP0

PE08TN0

PE09RP0

PE09RN0

PE09TP0

PE09TN0

PE10RP0

PE10RN0

PE10TP0

PE10TN0

S8_12V

S12_12V

100

100

100

100

S12_3VAUX

S8_3V

S8_3VAUX

S12_3V

470-1075-600 (2 of 2)

1K

1K

0603

MEZZ_SMBDAT3

MEZZ_SMBCLK3

5%

0603

5%

+3V3

MEZZANINE CONNECTOR PORTS 8/12

IDT

TITLE

DRAWING NO.

AUTHOR

CHECKED BY

COPYRIGHT (C)

3

SIZE

REV.

FAB P/N

1

1

A A

B B

C C

D

D

2

2

4

45

6

67

7

8

38 5

6024 SILVER CREEK VALLEY ROAD. SAN JOSE, CA 95138

CONFIDENTIAL PROPERTY OF INTEGRATED DEVICE TECHNOLOGY, INC.

IN

IN

BI

OUT

OUT

Common Power

Signal

Common Power

Signal

Common Power

Signal

Common Power

Signal

Common Power

Signal

Wafer 9

Wafer 8

Wafer 7

Wafer 6

Wafer 5

V18

T18

P18

M18

K18

H18

F18

D18

B18A17

C17

E17

G17

J17

L17

N17

R17

U17

W17

B16

D16

F16

H16

K16

M16

P16

T16

V16

W15

U15

R15

N15

L15

J15

G15

E15

C15

A15

V20

T20

P20

M20

K20

H20

F20

D20

B20A19

C19

E19

G19

J19

L19

N19

R19

U19

W19

B14

D14

F14

H14

K14

M14

P14

T14

V14

W13

U13

R13

N13

L13

J13

G13

E13

C13

A13

B12

D12

F12

H12

K12

M12

P12

T12

V12

W11

U11

R11

N11

L11

J11

G11

E11

C11

A11

OUT

IN

IN

OUT

OUT

IN

IN

OUT

OUT

IN

IN

IN

OUT

OUT

IN

IN

OUT

OUT

OUT

IN

OUT

IN

IN

OUT

OUT

OUT

OUT

IN

IN

OUT

OUT

OUT

IN

IN

IN

OUT

OUT

IN

OUT

IN

IN

OUT

BI

IN

OUT

Common Power

Signal

Common Power

Signal

Common Power

Signal

Common Power

Signal

Common Power

Signal

Wafer 4

Wafer 3

Wafer 2

Wafer 1

Wafer 0

V8

T8

P8

M8

K8

H8

F8

D8

B8A7

C7

E7

G7

J7

L7

N7

R7

U7

W7

B6

D6

F6

H6

K6

M6

P6

T6

V6

W5

U5

R5

N5

L5

J5

G5

E5

C5

A5

V10

T10

P10

M10

K10

H10

F10

D10

B10

A9

C9

E9

G9

J9

L9

N9

R9

U9

W9

B4

D4

F4

H4

K4

M4

P4

T4

V4

W3

U3

R3

N3

L3

J3

G3

E3

C3

A3

B2

D2

F2

H2

K2

M2

P2

T2

V2

W1

U1

R1

N1

L1

J1

G1

E1

C1

A1

Page 35

X4 - STK3CFG1 = 0, STK3CFG0 = 1

X8 - STK3CFG1 = 0, STK3CFG0 = 0

STK3CFG1 & STK3CFG0 SET BY MEZZ CARDS

Tue Apr 20 12:38:32 2010

SHEET 4 OF 41

1.1

18-692-000

Derek Huang

2010

Tony Tran

SCH-PESEB-002

EB-LOGAN-19

B

R43

R42

J52

W19

W17

W15

W13

W11

V20

V18

V16

V14

V12

U19

U17

U15

U13

U11

T20

T18

T16

T14

T12

R19

R17

R15

R13

R11

P20

P18

P16

P14

P12

N19

N17

N15

N13

N11

M20

M18

M16

M14

M12

L19

L17

L15

L13

L11

K20

K18

K16

K14

K12

J19

J17

J15

J13

J11

H20

H18

H16

H14

H12

G19

G17

G15

G13

G11

F20

F18

F16

F14

F12

E19

E17

E15

E13

E11

D20

D18

D16

D14

D12

C19

C17

C15

C13

C11

B20

B18

B16

B14

B12

A19

A17

A15

A13

A11

J4

R38

R39

R41

R40

W9

W7

W5

W3

W1

V8

V6

V4

V2

V10

U9

U7

U5

U3

U1

T8

T6

T4

T2

T10

R9

R7

R5

R3

R1

P8

P6

P4

P2

P10

N9

N7

N5

N3

N1

M8

M6

M4

M2

M10

L9

L7

L5

L3

L1

K8

K6

K4

K2

K10

J9

J7

J5

J3

J1

H8

H6

H4

H2

H10

G9

G7

G5

G3

G1

F8

F6

F4

F2

F10

E9

E7

E5

E3

E1

D8

D6

D4

D2

D10

C9

C7

C5

C3

C1

B8

B6

B4

B2

B10

A9

A7

A5

A3

A1

J4

5

5

5

5

5

5

5

5

5

5

5

5

8

2937

5

5

5

5

6

28

8

2937

5

5

5

5

6

28

4

4

16

37

6

343839

20

20

16

37

20

20

6

343839

5

5

5

5

5

5

5

5

5

5

5

5

4

4

PE20TN0

PE20TP0

PE20RN0

PE20RP0

PE21RP0

PE21RN0

PE21TP0

PE21TN0

PE19TN0

PE19TP0

PE19RN0

PE19RP0

M1620_ID<2>

P16_PDN

PE22RP0

PE22RN0

PE22TP0

PE22TN0

STK3CFG1

P20_PDN

PE23RP0

PE23RN0

PE23TP0

PE23TN0

470-1075-600 (1 of 2)

S20_12V

S16_12V

STK3CFG0

MEZZ_SMBDAT4

MEZZ_SMBCLK4

SLOT_WAKEN16

SLOT_HDR_RSTN16

S16_CLKP

S16_CLKN

M1620_ID<1>

SLOT_WAKEN20

S20_CLKN

S20_CLKP

SLOT_HDR_RSTN20

PE16RP0

PE16RN0

PE16TP0

PE16TN0

PE17RP0

PE17RN0

PE17TN0

PE17TP0

PE18RP0

PE18RN0

PE18TP0

PE18TN0

100

100

100

100

S20_3V

S16_3V

S20_3VAUX

470-1075-600 (2 of 2)

S16_3VAUX

MEZZ_SMBDAT4

MEZZ_SMBCLK4

5%

06031K0603

1K

5%

+3V3

MEZZANINE CONNECTOR PORTS 16/20

IDT

TITLE

DRAWING NO.

AUTHOR

CHECKED BY

COPYRIGHT (C)

3

SIZE

REV.

FAB P/N

1

1

A A

B B

C C

D

D

2

2

4

45

6

67

7

8

38 5

6024 SILVER CREEK VALLEY ROAD. SAN JOSE, CA 95138

CONFIDENTIAL PROPERTY OF INTEGRATED DEVICE TECHNOLOGY, INC.

OUT

IN

IN

OUT

BI

Common Power

Signal

Common Power

Signal

Common Power

Signal

Common Power

Signal

Common Power

Signal

Wafer 9

Wafer 8

Wafer 7

Wafer 6

Wafer 5

V18

T18

P18

M18

K18

H18

F18

D18

B18A17

C17

E17

G17

J17

L17

N17

R17

U17

W17

B16

D16

F16

H16

K16

M16

P16

T16

V16

W15

U15

R15

N15

L15

J15

G15

E15

C15

A15

V20

T20

P20

M20

K20

H20

F20

D20

B20A19

C19

E19

G19

J19

L19

N19

R19

U19

W19

B14

D14

F14

H14

K14

M14

P14

T14

V14

W13

U13

R13

N13

L13

J13

G13

E13

C13

A13

B12

D12

F12

H12

K12

M12

P12

T12

V12

W11

U11

R11

N11

L11

J11

G11

E11

C11

A11

OUT

IN

IN

OUT

OUT

OUT

OUT

IN

IN

OUT

IN

IN

OUT

OUT

IN

IN

IN

IN

OUT

OUT

IN

IN

IN

OUT

IN

OUT

BI

IN

IN

IN

OUT

OUT

OUT

OUT

IN

OUT

IN

OUT

OUT

OUT

OUT

IN

IN

Common Power

Signal

Common Power

Signal

Common Power

Signal

Common Power

Signal

Common Power

Signal

Wafer 4

Wafer 3

Wafer 2

Wafer 1

Wafer 0

V8

T8

P8

M8

K8

H8

F8

D8

B8A7

C7

E7

G7

J7

L7

N7

R7

U7

W7

B6

D6

F6

H6

K6

M6

P6

T6

V6

W5

U5

R5

N5

L5

J5

G5

E5

C5

A5

V10

T10

P10

M10

K10

H10

F10

D10

B10

A9

C9

E9

G9

J9

L9

N9

R9

U9

W9

B4

D4

F4

H4

K4

M4

P4

T4

V4

W3

U3

R3

N3

L3

J3

G3

E3

C3

A3

B2

D2

F2

H2

K2

M2

P2

T2

V2

W1

U1

R1

N1

L1

J1

G1

E1

C1

A1

OUT

OUT

Page 36

Tue Apr 20 12:38:33 2010

SHEET 5 OF 41

1.1

18-692-000

Derek Huang

2010

Tony Tran

SCH-PESEB-002

EB-LOGAN-19

B

U18

T18

N18

P18

V17

U17

P17

R17

V15

U15

R16

T16

V14

U14

R13

T13

V8

U8

R10

T10

V7

U7

R9

T9

V4

U4

R6

T6

V3

U3

R5

T5

U1

A9

B9

D7

C7

A10

B10

D8

C8

A15

B15

D13

C13

A16

B16

D14

C14

E18

E17

G15

G16

F18

F17

H15

H16

J18

J17

L15

L16

K18

K17

M15

M16

U1

T1

T2

P4

P3

R1

R2

N4

N3

M1

M2

K4

K3

L1

L2

J4

J3

H1

H2

F4

F3

G1

G2

E4

E3

B1

B2

C4

C3

A2

A3

B5

B4

U1

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

3

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

24NT24G2 - SERDES

PE15RN0

PE15RP0

PE14RN0

PE13RN0

PE13RP0

PE14RP0

PE11RN0

PE12RP0

PE12RN0

PE11RP0

PE10RP0

PE10RN0

PE09RN0

PE09RP0

PE08RN0

PE08RP0

PE15TN0

PE15TP0

PE14TN0

PE14TP0

PE13TP0

PE13TN0

PE12TN0

PE12TP0

PE11TN0

PE11TP0

PE10TN0

PE10TP0

PE09TN0

PE09TP0

PE08TN0

PE08TP0

PE16TP0

PE23RP0

PE23RN0

PE22RN0

PE22RP0

PE21RN0

PE21RP0

PE20RN0

PE20RP0

PE19RN0

PE19RP0

PE18RP0

PE18RN0

PE17RN0

PE17RP0

PE16RN0

PE16RP0

PE23TN0

PE23TP0

PE22TN0

PE22TP0

PE21TN0

PE21TP0

PE20TP0

PE20TN0

PE19TN0

PE19TP0

PE18TN0

PE18TP0

PE17TN0

PE17TP0

PE16TN0

PE00RP0

PE00RN0

PE07TP0

PE07TN0

PE06TN0

PE06TP0

PE05TP0

PE05TN0

PE04TP0

PE04TN0

PE07RP0

PE07RN0

PE06RN0

PE06RP0

PE05RP0

PE05RN0

PE04RP0

PE04RN0

PE03TP0

PE03TN0

PE02TN0

PE02TP0

PE01TP0

PE01TN0

PE00TP0

PE00TN0

PE03RP0

PE03RN0

PE02RN0

PE02RP0

PE01RP0

PE01RN0

IDT

TITLE

DRAWING NO.

AUTHOR

CHECKED BY

COPYRIGHT (C)

3

SIZE

REV.

FAB P/N

1

1

A A

B B

C C

D

D

2

2

4

45

6

67

7

8

38 5

6024 SILVER CREEK VALLEY ROAD. SAN JOSE, CA 95138

CONFIDENTIAL PROPERTY OF INTEGRATED DEVICE TECHNOLOGY, INC.

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

OUT

OUT

OUT

IN

OUT

OUT

OUT

89HPES24NT24G2 (3/8)

PE07TP0

PE07TN0

PE07RP0

PE07RN0

PE06TP0

PE06TN0

PE06RP0

PE06RN0

PE05TP0

PE05TN0

PE05RP0

PE05RN0

PE04TP0

PE04TN0

PE04RP0

PE04RN0