Page 1

®

CPS-1848™ User Manual

Titl

Central Packet Switch

Formal Status

June 2, 2014

Page 2

GENERAL DISCLAIMER

Integrated Device Technology, Inc. (“IDT”) reserves the right to make changes to its products or specifications at any time, without notice,

in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the

circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or

otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product

performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as

“reserved” or “undefined” are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising

from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not

warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury ,

or damage to tangible property . Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for

developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright ©2014 Integrated Device Technology, Inc.

The IDT logo is registered to Integrated Device Technology, Inc.

Page 3

Table of Contents

o

About this Document....................................................................................................................17

Content Summary....................................................................................................................................................................................17

Additional Resources...............................................................................................................................................................................17

Document Conventions and Definitions...................................................................................................................................................17

Device Revision Information....................................................................................................................................................................18

Revision History.......................................................................................................................................................................................18

1. Device Overview...................... .................................................................................................... 23

1.1 Device Description...................................................................................................................................................................................23

1.2 Key Features ...........................................................................................................................................................................................23

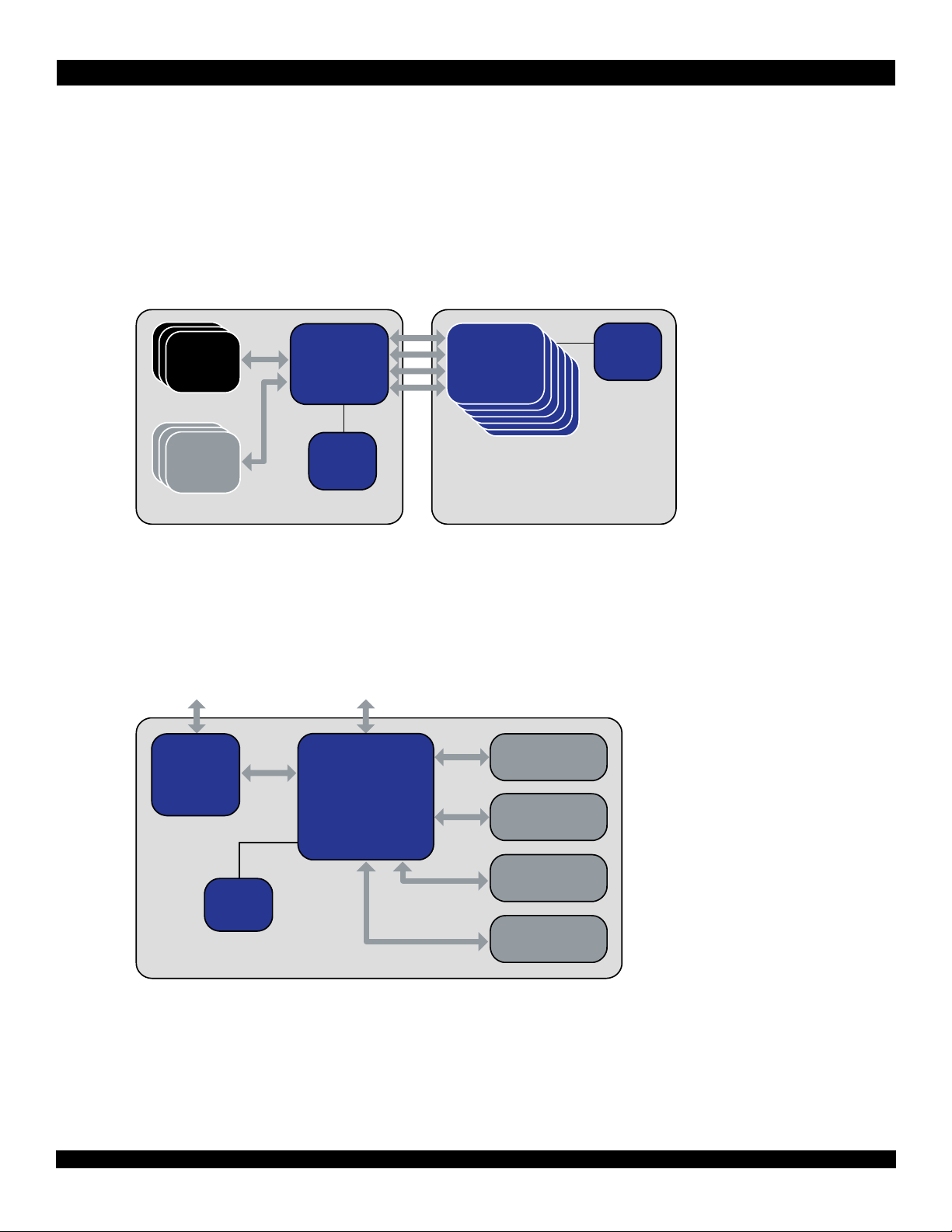

1.3 Block Diagrams........................................................................................................................................................................................25

1.4 Typical Applications................................................................................................................................................................................. 26

1.4.1 Wireless Application Benefits...................................................................................................................................................26

1.4.2 Defense and Aerospace Application Benefits.......................................................................................................................... 27

1.4.3 Video and Imaging Application Benefits...................................................................................................................................27

2. RapidIO Por t s .......................... ......................... .......................... .. ......................... .. .................... 28

2.1 Overview..................................................................................................................................................................................................28

2.2 Key Features ...........................................................................................................................................................................................29

2.3 Packet Routing ........................................................................................................................................................................................30

2.3.1 Packet Routing Overview.........................................................................................................................................................30

2.3.2 Unicast Programming Model....................................................................................................................................................31

2.3.3 Multicast Programming Model..................................................................................................................................................33

2.3.4 Programming Examples...........................................................................................................................................................34

2.4 Flow Control.............................................................................................................................................................................................38

2.4.1 Transmitter- and Receiver-Controlled Flow Control Programming Model................................................................................38

2.5 Multicast Event Control Symbols.............................................................................................................................................................39

2.6 Port Reconfiguration Operations..............................................................................................................................................................39

2.6.1 Disabling IDLE2 Operation.......................................................................................................................................................40

2.7 Reset Control Symbol Processing........................................................................................................................................................... 40

2.7.1 Per-Port Reset..........................................................................................................................................................................40

2.7.2 Port Disable/Enable..................................................................................................................................................................42

2.7.3 Generating a Reset Request....................................................................................................................................................42

2.8 Hot Extraction/Insertion............................................................................................................................................................................42

2.8.1 Hot Extraction...........................................................................................................................................................................43

2.8.2 Controlled Removal/Reset........................................................................................................................................................43

2.8.3 Link Partner Insertion............................................................................................................................................................... 48

2.9 Packet Trace and Filtering.......................................................................................................................................................................53

2.9.1 Packet Trace............................................................................................................................................................................53

2.9.2 Packet Filtering.........................................................................................................................................................................57

2.10 Packet Generation and Capture..............................................................................................................................................................57

2.10.1 Packet Generation and Capture Mode Overview.....................................................................................................................58

2.10.2 Packet Generation and Capture Mode Programming Model....................................................................................................59

C

CPS-1848 User Manual 3 June 2, 2014

Formal Status This document is confidential and is subject to an NDA.

Integrated Device Technology

Page 4

Table of Contents

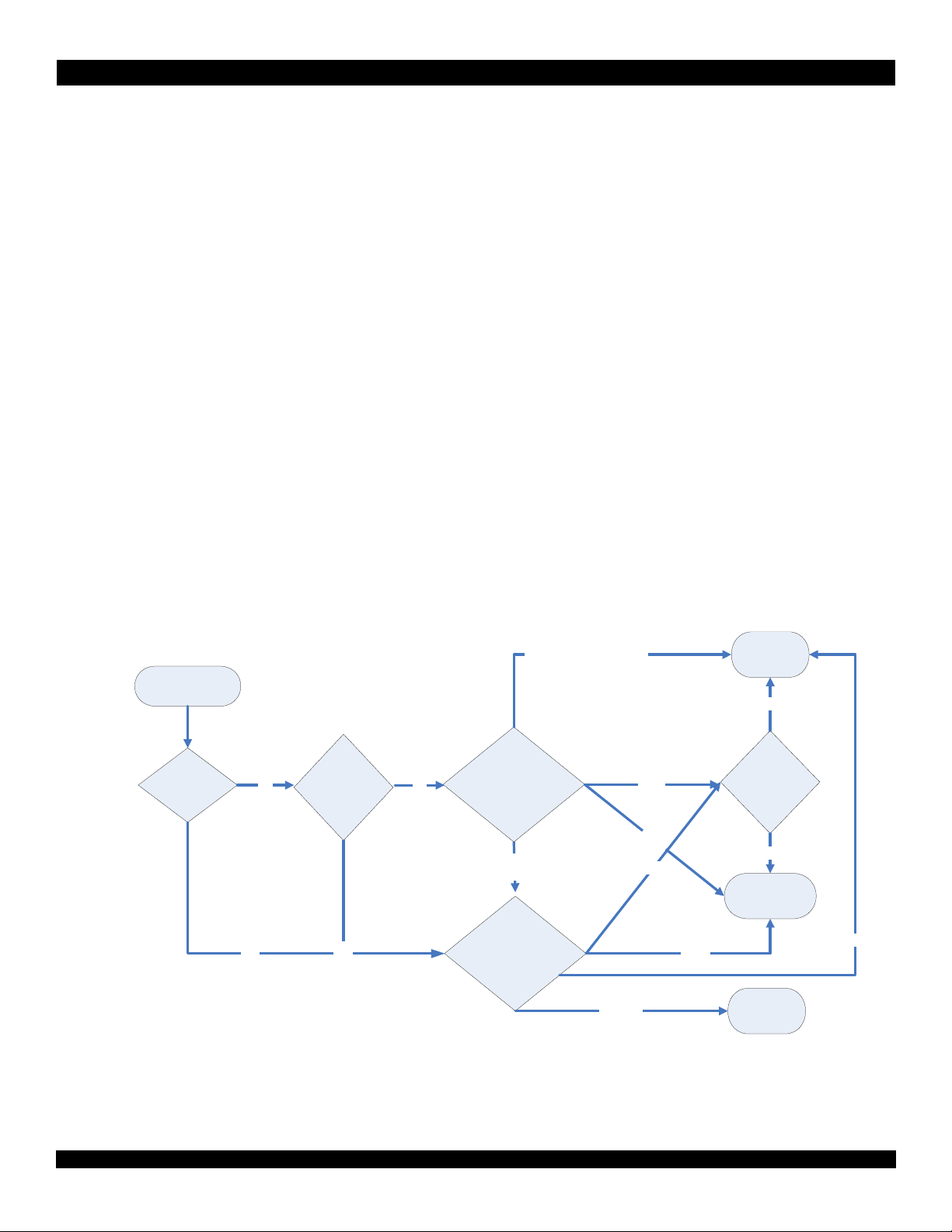

2.11 Packet Transfer Validation and Debug.....................................................................................................................................................62

2.11.1 Overview...................................................................................................................................................................................62

2.11.2 Successful Packet Transfer...................................................................................................................................................... 63

2.11.3 Switch Cannot Accept Packets.................................................................................................................................................63

2.11.4 Switch Is Not Routing Packets Correctly..................................................................................................................................65

2.11.5 Switch Cannot Transmit Packets..............................................................................................................................................66

2.11.6 Requesting Debug Assistance.................................................................................................................................................68

3. RapidIO Lanes ............................................................................................................................. 69

3.1 Lane to Port Mapping ..............................................................................................................................................................................70

3.2 Lane and Port Speeds.............................................................................................................................................................................73

3.2.1 Lane Speed Change Examples................................................................................................................................................73

3.3 Lane, PLL, and Port Power-Down...........................................................................................................................................................75

3.4 Port and Lane Initialization Sequence.....................................................................................................................................................75

3.4.1 Signal Quality Optimization......................................................................................................................................................76

3.5 Loopback Capabilities..............................................................................................................................................................................82

3.5.1 Lane Loopback Modes.............................................................................................................................................................83

3.5.2 Port Loopback Mode................................................................................................................................................................ 83

3.6 Bit Error Rate Testing...............................................................................................................................................................................84

3.6.1 PRBS Polynomials...................................................................................................................................................................84

3.6.2 User-Defined Patterns..............................................................................................................................................................84

3.6.3 PRBS Pattern Generator..........................................................................................................................................................85

3.6.4 PRBS Pattern Checker and Log (Revision C)..........................................................................................................................85

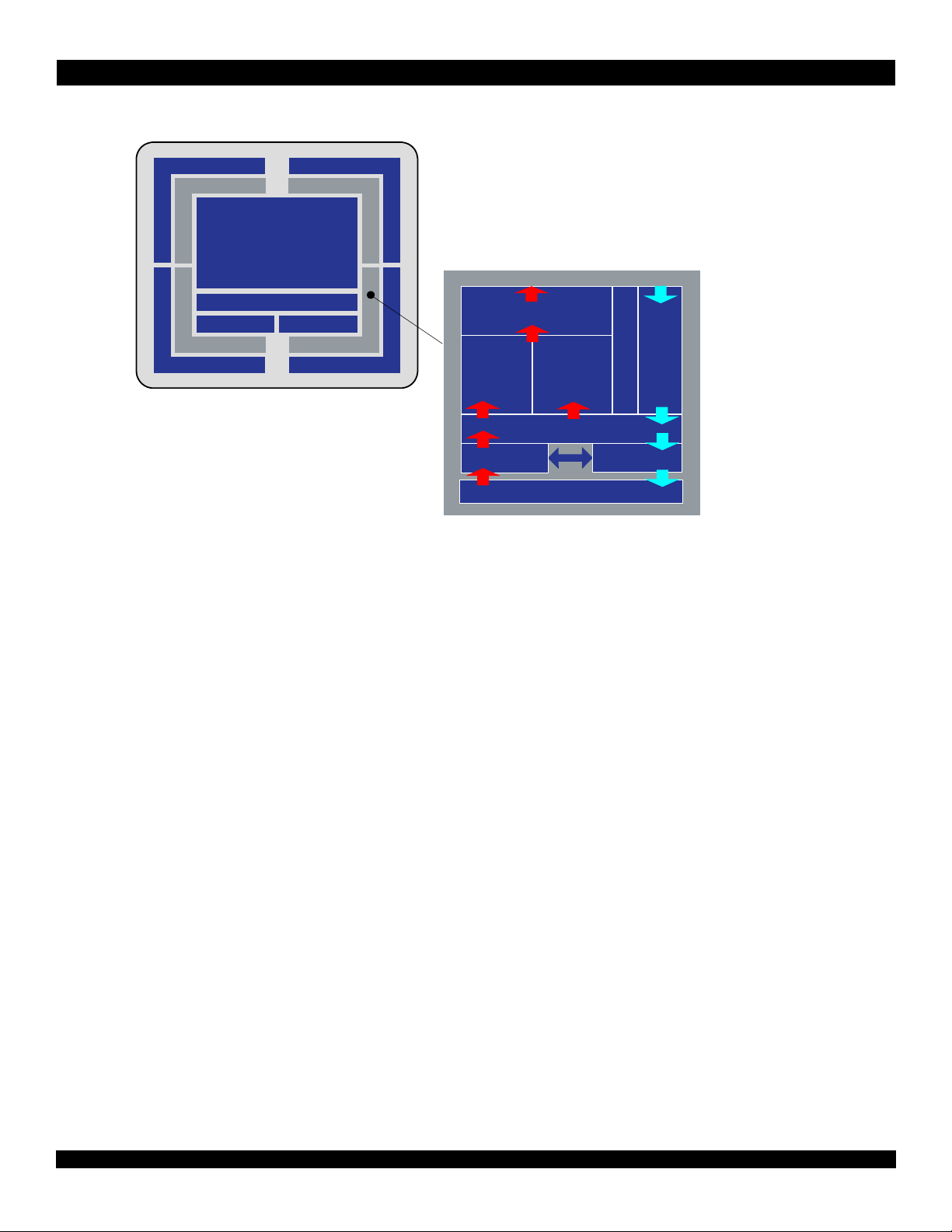

4. Switch Fabric............................................................................................................................... 87

4.1 Key Features ...........................................................................................................................................................................................87

4.2 Switch Fabric Architecture.......................................................................................................................................................................88

4.3 Input Buffer..............................................................................................................................................................................................89

4.4 Input Buffer to Crosspoint Buffer Transfers..............................................................................................................................................89

4.4.1 VoQ Fairness/Starvation Avoidance.........................................................................................................................................90

4.4.2 Multicast Packets......................................................................................................................................................................90

4.5 Crosspoint Buffers...................................................................................................................................................................................90

4.6 Crosspoint Buffer to Final Buffer Transfers..............................................................................................................................................91

4.7 Maintenance Transaction Support...........................................................................................................................................................91

4.8 Final Buffer...............................................................................................................................................................................................92

5. Performance ................................................................................................................................ 93

5.1 Overview..................................................................................................................................................................................................93

5.1.1 Throughput...............................................................................................................................................................................93

5.1.2 Latency.....................................................................................................................................................................................93

5.1.3 Latency Variation...................................................................................................................................................................... 94

5.2 Performance Monitoring...........................................................................................................................................................................94

5.2.1 Traffic Efficiency.......................................................................................................................................................................95

5.2.2 Congestion Detection...............................................................................................................................................................95

5.2.3 Resetting Performance Registers.............................................................................................................................................95

5.3 Performance Measurements....................................................................................................................................................................96

5.3.1 Buffer Management Settings....................................................................................................................................................96

5.3.2 Store-and-Forward or Cut-Through Mode................................................................................................................................98

5.3.3 Transmitter-Controlled or Receiver-Controlled Flow Control Mode..........................................................

................................98

5.4 Port-to-Port Performance Characteristics................................................................................................................................................99

5.4.1 Packet Latency Performance................................................................................................................................................... 99

CPS-1848 User Manual 4 June 2, 2014

Formal Status This document is confidential and is subject to an NDA.

Integrated Device Technology

Page 5

Table of Contents

5.4.2 Packet Throughput Performance............................................................................................................................................100

5.4.3 Multicast Latency Performance..............................................................................................................................................102

5.4.4 Multicast Throughput Performance........................................................................................................................................ 102

5.4.5 Multicast-Event Control Symbol (MECS) Latency..................................................................................................................103

6. Event Management. .. .. .. ............................ .. ........................... ... ........................... ...................... 104

6.1 Event Management Overview................................................................................................................................................................104

6.1.1 Logical/Transport Layer Events Overview..............................................................................................................................108

6.1.2 Physical Layer Error Management Overview.........................................................................................................................109

6.1.3 Lane Error Management Overview..........................................................................................................................................111

6.1.4 I2C Error Management Overview............................................................................................................................................112

6.1.5 Configuration Error Management Overview............................................................................................................................113

6.2 Event Detection ......................................................................................................................................................................................113

6.2.1 Logical and Transport Layer Events........................................................................................................................................113

6.2.2 Physical Layer Events.............................................................................................................................................................115

6.2.3 Lane Events............................................................................................................................................................................124

6.2.4 I2C Events..............................................................................................................................................................................126

6.2.5 JTAG Events (Revision A/B Only).......................................................................................................................................... 126

6.2.6 Configuration Block Events.................................................................................................................................................... 127

6.2.7 Trace and Filter Events..........................................................................................................................................................127

6.2.8 Packet Generation and Capture Mode Events.......................................................................................................................127

6.2.9 Error Log Events.....................................................................................................................................................................127

6.3 Event Notification...................................................................................................................................................................................137

6.3.1 Logical Layer Events Notification........................................................................................................................................... 137

6.3.2 Physical Layer Events Notification.........................................................................................................................................139

6.3.3 Lane Event Notification...........................................................................................................................................................146

6.3.4 I2C Event Notification.............................................................................................................................................................146

6.3.5 JTAG 1149.1 Event Notification (Revision A/B Only).............................................................................................................147

6.3.6 Configuration Block Event Notification...................................................................................................................................147

6.3.7 Trace and Filter Event Notification.........................................................................................................................................147

6.3.8 Packet Generation and Capture Mode Event Notification......................................................................................................147

6.3.9 Port-Write Formats, Programming Model, and Generation....................................................................................................148

6.3.10 Interrupt Notification...............................................................................................................................................................152

6.3.11 Error Log Event Notification Programming Model..................................................................................................................152

6.4 Event Isolation.......................................................................................................................................................................................154

6.4.1 Fatal Link Response Timeout Isolation..................................................................................................................................156

6.4.2 Received Retry Count Trigger Congestion Isolation ..............................................................................................................157

6.4.3 TTL Event Isolation.................................................................................................................................................................157

6.4.4 Transmit Packet Dropped via CRC Retransmit Limit Isolation...............................................................................................157

6.4.5 Packet Received With a CRC Error While CRC Error Suppression Enabled Isolation..........................................................157

6.4.6 Software Controlled Isolation Functions.................................................................................................................................158

6.5 Event Clearing and Recovery................................................................................................................................................................ 158

6.5.1 Logical Layer Event Clearing and Handling........................................................................................................................... 158

6.5.2 Physical Layer Events Clearing and Handling........................................................................................................................159

6.5.3 Lane Event Clearing and Handling......................................................................................................................................... 167

6.5.4 I2C Event Clearing and Handling...........................................................................................................................................167

6.5.5 JTAG 1149.1 Events (Revision A/B Only)..............................................................................................................................168

6.5.6 Configuration Block Events....................................................................................................................................................168

6.5.7 Trace, Filter, and PGC Events................................................................................................................................................169

CPS-1848 User Manual 5 June 2, 2014

Formal Status This document is confidential and is subject to an NDA.

Integrated Device Technology

Page 6

Table of Contents

7. I2C Interface.............................................................................................................................. 170

7.1 Overview................................................................................................................................................................................................170

7.2 Master/Slave Configuration....................................................................................................................................................................170

7.3 Temporary Master Mode........................................................................................................................................................................ 170

7.3.1 Obtaining Configuration in Master Mode................................................................................................................................171

7.3.2 Commanded Master Mode.....................................................................................................................................................171

7.3.3 Master Clock Frequency.........................................................................................................................................................171

7.3.4 EEPROM Format....................................................................................................................................................................171

7.3.5 CRC Calculation.....................................................................................................................................................................173

7.3.6 Register Map Example...........................................................................................................................................................175

7.3.7 EEPROM Format Example.....................................................................................................................................................175

7.3.8 I2C Master Mode Validation Debug........................................................................................................................................176

7.4 Slave Mode............................................................................................................................................................................................177

7.4.1 Signaling in Slave Mode.........................................................................................................................................................177

7.4.2 Connecting to Standard-, Fast-, and Hs-Mode Devices as a Slave.......................................................................................180

7.4.3 CPS-1848 Memory Access through I2C as a Slave...............................................................................................................180

8. JTAG and Boundary Scan.......................................................................................................... 183

8.1 Overview................................................................................................................................................................................................183

8.2 JTAG and AC Extest Compliance..........................................................................................................................................................183

8.3 Test Instructions.....................................................................................................................................................................................184

8.4 Device ID Register.................................................................................................................................................................................184

8.5 Initialization and Reset...........................................................................................................................................................................185

8.6 Configuration Register Access (Revision A/B).......................................................................................................................................185

8.6.1 Configuration Register Access – Writes.................................................................................................................................186

8.6.2 Configuration Register Access – Reads................................................................................................................................. 186

8.7 Configuration Register Access (Revision C).......................................................................................................................................... 187

8.7.1 Inter-Command Delay............................................................................................................................................................188

8.7.2 Configuration Register Access – Writes.................................................................................................................................190

8.7.3 Configuration Register Access – Reads................................................................................................................................. 190

8.8 JTAG Clock Constraints.........................................................................................................................................................................191

8.9 Boundary Scan......................................................................................................................................................................................191

9. Reset and Initialization ............................................................................................................. 192

9.1 Hardware Reset.....................................................................................................................................................................................192

9.1.1 Power-Up Reset.....................................................................................................................................................................192

9.1.2 Resets after Power-Up...........................................................................................................................................................192

9.2 Initialization............................................................................................................................................................................................ 193

9.2.1 I2C Initialization......................................................................................................................................................................193

9.2.2 Link Initialization.....................................................................................................................................................................193

9.2.3 Register Initialization..............................................................................................................................................................194

9.2.4 Computing Timeout Values....................................................................................................................................................195

10. Registers ................................................................................................................................... 197

10.1 Overview................................................................................................................................................................................................197

10.1.1 RapidIO Compliance..............................................................................................................................................................197

10.1.2 Interpretation of Reserved Register Bits.................................................................................................................................198

10.1.3 Backward Compatibility..........................................................................................................................................................198

10.1.4 Register Type Field Definitions...............................................................................................................................................198

10.2 Address Map..........................................................................................................................................................................................198

CPS-1848 User Manual 6 June 2, 2014

Formal Status This document is confidential and is subject to an NDA.

Integrated Device Technology

Page 7

Table of Contents

10.3 RapidIO Capability Registers (CARs)....................................................................................................................................................212

10.3.1 Device Identity CAR...............................................................................................................................................................212

10.3.2 Device Information CAR.........................................................................................................................................................213

10.3.3 Assembly Identity CAR........................................................................................................................................................... 214

10.3.4 Assembly Information CAR....................................................................................................................................................214

10.3.5 Processing Element Features CAR........................................................................................................................................ 215

10.3.6 Switch Port Information CAR.................................................................................................................................................. 217

10.3.7 Source Operations CAR.........................................................................................................................................................218

10.3.8 Switch Multicast Support CAR................................................................................................................................................219

10.3.9 Switch Route Table Entries Table Limit CAR..........................................................................................................................220

10.3.10 Switch Multicast Information CAR..........................................................................................................................................221

10.4 RapidIO Control and Status Registers (CSRs)......................................................................................................................................222

10.4.1 Host Base deviceID Lock CSR............................................................................................................................................... 222

10.4.2 Component Tag CSR..............................................................................................................................................................222

10.4.3 Standard Route Table Entries Configuration destID Select CSR...........................................................................................223

10.4.4 Standard Route Table Entry Configuration Port Select CSR..................................................................................................224

10.4.5 Standard Route Table Entry Default Port CSR....................................................................................................................... 225

10.4.6 Multicast Mask Port CSR........................................................................................................................................................226

10.4.7 Multicast Association Selection CSR......................................................................................................................................227

10.4.8 Multicast Association Operations CSR................................................................................................................................... 228

10.5 LP-Serial Extended Features Registers with Software Assisted Error Recovery..................................................................................229

10.5.1 Port Maintenance Block Header Register..............................................................................................................................229

10.5.2 Port Link Timeout Control CSR..............................................................................................................................................230

10.5.3 Port General Control CSR......................................................................................................................................................230

10.5.4 Port {0..17} S-RIO Extended Features Base Addresses........................................................................................................231

10.5.5 Port {0..17} Link Maintenance Request CSR.........................................................................................................................232

10.5.6 Port {0..17} Link Maintenance Response CSR.......................................................................................................................233

10.5.7 Port {0..17} Local ackID CSR.................................................................................................................................................234

10.5.8 Port {0..17} Error and Status CSR.......................................................................................................................................... 235

10.5.9 Port {0..17} Control 1 CSR.....................................................................................................................................................238

10.5.10 Port {0..17} Control 2 CSR.....................................................................................................................................................242

10.6 Virtual Channel Extended Features Block Registers.............................................................................................................................244

10.6.1 VC Register Block Header Register.......................................................................................................................................244

10.7 Error Management Extensions Block Registers....................................................................................................................................245

10.7.1 Error Management Extensions Block Header Register..........................................................................................................245

10.7.2 Logical/Transport Layer Error Detect CSR............................................................................................................................. 246

10.7.3 Logical/Transport Layer Error Enable CSR............................................................................................................................247

10.7.4 Logical/Transport Layer deviceID Capture CSR....................................................................................................................248

10.7.5 Logical/Transport Layer Control Capture CSR....................................................................................................................... 249

10.7.6 Port-Write Target deviceID CSR.............................................................................................................................................251

10.7.7 Packet Time to Live CSR.......................................................................................................................................................252

10.7.8 Port Error Management Register Base Addresses................................................................................................................253

10.7.9 Port {0..17} Error Detect CSR.................................................................................................................................................254

10.7.10 Port {0..17} Error Rate Enable CSR.......................................................................................................................................256

10.7.11 Port {0..17} Attributes Capture CSR.......................................................................................................................................258

10.7.12 Port {0..17} Capture 0 CSR....................................................................................................................................................259

10.7.13 Port {0..17} Capture 1 CSR....................................................................................................................................................260

10.7.14 Port {0..17} Capture 2 CSR....................................................................................................................................................260

10.7.15 Port {0..17} Capture 3 CSR....................................................................................................................................................261

10.7.16 Port {0..17} Error Rate CSR...................................................................................................................................................262

CPS-1848 User Manual 7 June 2, 2014

Formal Status This document is confidential and is subject to an NDA.

Integrated Device Technology

Page 8

Table of Contents

10.7.17 Port {0..17} Error Rate Threshold CSR..................................................................................................................................264

10.8 Lane Status Registers ........................................................................................................................................................................... 265

10.8.1 Lane {0..47} Status Base Addresses...................................................................................................................................... 265

10.8.2 Lane Status Block Header Register.......................................................................................................................................267

10.8.3 Lane {0..47} Status 0 CSR.....................................................................................................................................................268

10.8.4 Lane {0..47} Status 1 CSR.....................................................................................................................................................270

10.8.5 Lane {0..47} Status 2 CSR.....................................................................................................................................................272

10.8.6 Lane {0..47} Status 3 CSR.....................................................................................................................................................273

10.8.7 Lane {0..47} Status 4 CSR.....................................................................................................................................................275

10.9 IDT Specific Miscellaneous Registers....................................................................................................................................................276

10.9.1 Route Port Select Register.....................................................................................................................................................276

10.9.2 Multicast Route Select Register.............................................................................................................................................277

10.9.3 Port n Watermarks Base Addresses......................................................................................................................................278

10.9.4 Port {0..17} Watermarks Register........................................................................................................................................... 279

10.9.5 Broadcast Watermarks Register.............................................................................................................................................280

10.10 IDT Specific Event Notification Control Registers..................................................................................................................................281

10.10.1 Aux Port Error Capture Enable Register................................................................................................................................281

10.10.2 Aux Port Error Detect Register...............................................................................................................................................282

10.10.3 Configuration Block Error Capture Enable Register...............................................................................................................283

10.10.4 Configuration Block Error Detect Register..............................................................................................................................284

10.10.5 Impl. Specific Logical/Transport Layer Address Capture Register......................................................................................... 286

10.10.6 Logical/Transport Layer Error Report Enable Register...........................................................................................................287

10.10.7 Port {0..17} Error Report Enable Base Addresses.................................................................................................................288

10.10.8 Port {0..17} Error Report Enable Register..............................................................................................................................289

10.10.9 Port {0..17} Implementation Specific Error Report Enable Register.......................................................................................291

10.10.10 Broadcast Port Error Report Enable Register........................................................................................................................ 294

10.10.11 Broadcast Port Implementation Specific Error Report Enable Register.................................................................................296

10.10.12 Lane n Error Report Enable Base Addresses........................................................................................................................ 298

10.10.13 Lane {0..47} Error Report Enable Register.............................................................................................................................300

10.10.14 Broadcast Lane Error Report Enable Register.......................................................................................................................301

10.11 Packet Generation and Capture Registers............................................................................................................................................302

10.11.1 Packet Generation and Capture Base Addresses.................................................................................................................. 302

10.11.2 Port {0..17} Packet Generation and Capture Mode Configuration Register...........................................................................303

10.11.3 Port {0..17} Packet Generation and Capture Mode Data Register......................................................................................... 304

10.12 IDT Specific Routing Table Registers....................................................................................................................................................305

10.12.1 Base Addresses for IDT Specific Routing Table Registers.....................................................................................................305

10.12.2 Broadcast Device Route Table Register {0..255}...................................................................................................................306

10.12.3 Broadcast Domain Route Table Register {0..255}..................................................................................................................307

10.12.4 Port {0..17} Device Route Table Register {0..255}..................................................................................................................308

10.12.5 Port {0..17} Domain Routing Table Register {0..255}.............................................................................................................309

10.13 Trace Comparison Values and Masks Registers...................................................................................................................................310

10.13.1 Base Addresses for Trace Comparison Values and Masks Registers...................................................................................310

10.13.2 Port {0..17} Trace 0 Value 0 Register......................................................................................................................................311

10.13.3 Port {0..17} Trace 0 Value 1 Register......................................................................................................................................311

10.13.4 Port {0..17} Trace 0 Value 2 Register..................................................................................................................................... 312

10.13.5 Port {0..17} Trace 0 Value 3 Register..................................................................................................................................... 312

10.13.6 Port {0..17} Trace 0 Value 4 Register..................................................................................................................................... 313

10.13.7 Port {0..17} Trace 0 Mask 0 Register.....................................................................................................................................313

10.13.8 Port {0..17} Trace 0 Mask 1 Register.....................................................................................................................................314

10.13.9 Port {0..17} Trace 0 Mask 2 Register.....................................................................................................................................314

CPS-1848 User Manual 8 June 2, 2014

Formal Status This document is confidential and is subject to an NDA.

Integrated Device Technology

Page 9

Table of Contents

10.13.10 Port {0..17} Trace 0 Mask 3 Register.....................................................................................................................................315

10.13.11 Port {0..17} Trace 0 Mask 4 Register.....................................................................................................................................315

10.13.12 Port {0..17} Trace 1 Value 0 Register.....................................................................................................................................316

10.13.13 Port {0..17} Trace 1 Value 1 Register.....................................................................................................................................316

10.13.14 Port {0..17} Trace 1 Value 2 Register.....................................................................................................................................317

10.13.15 Port {0..17} Trace 1 Value 3 Register.....................................................................................................................................317

10.13.16 Port {0..17} Trace 1 Value 4 Register.....................................................................................................................................318

10.13.17 Port {0..17} Trace 1 Mask 0 Register.....................................................................................................................................318

10.13.18 Port {0..17} Trace 1 Mask 1 Register.....................................................................................................................................319

10.13.19 Port {0..17} Trace 1 Mask 2 Register.....................................................................................................................................319

10.13.20 Port {0..17} Trace 1 Mask 3 Register.....................................................................................................................................320

10.13.21 Port {0..17} Trace 1 Mask 4 Register.....................................................................................................................................320

10.13.22 Port {0..17} Trace 2 Value 0 Register.....................................................................................................................................321

10.13.23 Port {0..17} Trace 2 Value 1 Register.....................................................................................................................................321

10.13.24 Port {0..17} Trace 2 Value 2 Register.....................................................................................................................................322

10.13.25 Port {0..17} Trace 2 Value 3 Register.....................................................................................................................................322

10.13.26 Port {0..17} Trace 2 Value 4 Register.....................................................................................................................................323

10.13.27 Port {0..17} Trace 2 Mask 0 Register.....................................................................................................................................323

10.13.28 Port {0..17} Trace 2 Mask 1 Register.....................................................................................................................................324

10.13.29 Port {0..17} Trace 2 Mask 2 Register.....................................................................................................................................324

10.13.30 Port {0..17} Trace 2 Mask 3 Register.....................................................................................................................................325

10.13.31 Port {0..17} Trace 2 Mask 4 Register.....................................................................................................................................325

10.13.32 Port {0..17} Trace 3 Value 0 Register.....................................................................................................................................326

10.13.33 Port {0..17} Trace 3 Value 1 Register.....................................................................................................................................326

10.13.34 Port {0..17} Trace 3 Value 2 Register.....................................................................................................................................327

10.13.35 Port {0..17} Trace 3 Value 3 Register.....................................................................................................................................327

10.13.36 Port {0..17} Trace 3 Value 4 Register.....................................................................................................................................328

10.13.37 Port {0..17} Trace 3 Mask 0 Register.....................................................................................................................................328

10.13.38 Port {0..17} Trace 3 Mask 1 Register.....................................................................................................................................329

10.13.39 Port {0..17} Trace 3 Mask 2 Register.....................................................................................................................................329

10.13.40 Port {0..17} Trace 3 Mask 3 Register.....................................................................................................................................330

10.13.41 Port {0..17} Trace 3 Mask 4 Register.....................................................................................................................................330

10.13.42 Broadcast Trace 0 Value 0 Register.......................................................................................................................................331

10.13.43 Broadcast Trace 0 Value 1 Register.......................................................................................................................................331

10.13.44 Broadcast Trace 0 Value 2 Register.......................................................................................................................................332

10.13.45 Broadcast Trace 0 Value 3 Register.......................................................................................................................................332

10.13.46 Broadcast Trace 0 Value 4 Register.......................................................................................................................................333

10.13.47 Broadcast Trace 0 Mask 0 Register.......................................................................................................................................333

10.13.48 Broadcast Trace 0 Mask 1 Register.......................................................................................................................................334

10.13.49 Broadcast Trace 0 Mask 2 Register.......................................................................................................................................334

10.13.50 Broadcast Trace 0 Mask 3 Register.......................................................................................................................................335

10.13.51 Broadcast Trace 0 Mask 4 Register.......................................................................................................................................335

10.13.52 Broadcast Trace 1 Value 0 Register.......................................................................................................................................336

10.13.53 Broadcast Trace 1 Value 1 Register.......................................................................................................................................336

10.13.54 Broadcast Trace 1 Value 2 Register.......................................................................................................................................337

10.13.55 Broadcast Trace 1 Value 3 Register.......................................................................................................................................337

10.13.56 Broadcast Trace 1 Value 4 Register.......................................................................................................................................338

10.13.57 Broadcast Trace 1 Mask 0 Register.......................................................................................................................................338

10.13.58 Broadcast Trace 1 Mask 1 Register.......................................................................................................................................339

10.13.59 Broadcast Trace 1 Mask 2 Register.....................................................................................

..................................................339

CPS-1848 User Manual 9 June 2, 2014

Formal Status This document is confidential and is subject to an NDA.

Integrated Device Technology

Page 10

Table of Contents

10.13.60 Broadcast Trace 1 Mask 3 Register.......................................................................................................................................340

10.13.61 Broadcast Trace 1 Mask 4 Register.......................................................................................................................................340

10.13.62 Broadcast Trace 2 Value 0 Register.......................................................................................................................................341

10.13.63 Broadcast Trace 2 Value 1 Register.......................................................................................................................................341

10.13.64 Broadcast Trace 2 Value 2 Register.......................................................................................................................................342

10.13.65 Broadcast Trace 2 Value 3 Register.......................................................................................................................................342

10.13.66 Broadcast Trace 2 Value 4 Register.......................................................................................................................................343

10.13.67 Broadcast Trace 2 Mask 0 Register.......................................................................................................................................343

10.13.68 Broadcast Trace 2 Mask 1 Register.......................................................................................................................................344

10.13.69 Broadcast Trace 2 Mask 2 Register.......................................................................................................................................344

10.13.70 Broadcast Trace 2 Mask 3 Register.......................................................................................................................................345

10.13.71 Broadcast Trace 2 Mask 4 Register.......................................................................................................................................345

10.13.72 Broadcast Trace 3 Value 0 Register.......................................................................................................................................346

10.13.73 Broadcast Trace 3 Value 1 Register.......................................................................................................................................346

10.13.74 Broadcast Trace 3 Value 2 Register.......................................................................................................................................347

10.13.75 Broadcast Trace 3 Value 3 Register.......................................................................................................................................347

10.13.76 Broadcast Trace 3 Value 4 Register.......................................................................................................................................348

10.13.77 Broadcast Trace 3 Mask 0 Register.......................................................................................................................................348

10.13.78 Broadcast Trace 3 Mask 1 Register.......................................................................................................................................349

10.13.79 Broadcast Trace 3 Mask 2 Register.......................................................................................................................................349

10.13.80 Broadcast Trace 3 Mask 3 Register.......................................................................................................................................350

10.13.81 Broadcast Trace 3 Mask 4 Register.......................................................................................................................................350

10.14 Global Device Configuration Registers..................................................................................................................................................351

10.14.1 Device Control 1 Register.......................................................................................................................................................351

10.14.2 Configuration Block Error Report Register.............................................................................................................................353

10.14.3 Aux Port Error Report Enable Register..................................................................................................................................354

10.14.4 RapidIO Domain Register.......................................................................................................................................................355

10.14.5 Port-Write Control Register....................................................................................................................................................356

10.14.6 RapidIO Assembly Identification CAR Override.....................................................................................................................357

10.14.7 RapidIO Assembly Information CAR Override....................................................................................................................... 357

10.14.8 Device Soft Reset Register....................................................................................................................................................358

10.14.9 I2C Master Control Register...................................................................................................................................................358

10.14.10 I2C Master Status and Control Register ................................................................................................................................. 360

10.14.11 JTAG Control Register (Revision A/B)....................................................................................................................................361

10.14.12 External MCES Trigger Counter Register..............................................................................................................................362

10.14.13 Maintenance Dropped Packet Counter Register....................................................................................................................362

10.14.14 Switch Parameters 1 Register................................................................................................................................................363

10.14.15 Switch Parameters 2 Register................................................................................................................................................365

10.14.16 Quadrant Configuration Register............................................................................................................................................ 366

10.14.17 Device Reset and Control Register........................................................................................................................................368

10.15 Implementation Specific Multicast Mask Registers................................................................................................................................369

10.15.1 Implementation Specific Multicast Mask Base Addresses.....................................................................................................369

10.15.2 Broadcast Multicast Mask Register {0..39}............................................................................................................................. 370

10.15.3 Port {0..17} Multicast Mask Register {0..39}...........................................................................................................................371

10.16 Port Function Registers.........................................................................................................................................................................372

10.16.1 Port {0..17} Function Registers Base Addresses...................................................................................................................372

10.16.2 Port {0..17} Operations Register.............................................................................................................................................373

10.16.3 Port {0..17} Implementation Specific Error Detect Register....................................................................................................376

10.16.4 Port {0..17} Implementation Specific Error Rate Enable Register........................................................

..................................379

10.16.5 Port {0..17} VC0 Acknowledgements Transmitted Counter Register.....................................................................................382

CPS-1848 User Manual 10 June 2, 2014

Formal Status This document is confidential and is subject to an NDA.

Integrated Device Technology

Page 11

Table of Contents

10.16.6 Port {0..17} Not Acknowledgements Transmitted Counter Register.......................................................................................382

10.16.7 Port {0..17} VC0 Retry Symbols Transmitted Counter Register............................................................................................. 383

10.16.8 Port {0..17} VC0 Packets Transmitted Counter Register........................................................................................................383

10.16.9 Port {0..17} Trace Match Counter Value 0 Register................................................................................................................384

10.16.10 Port {0..17} Trace Match Counter Value 1 Register................................................................................................................384

10.16.11 Port {0..17} Trace Match Counter Value 2 Register................................................................................................................385

10.16.12 Port {0..17} Trace Match Counter Value 3 Register................................................................................................................385

10.16.13 Port {0..17} Filter Match Counter Value 0 Register.................................................................................................................386

10.16.14 Port {0..17} Filter Match Counter Value 1 Register.................................................................................................................386

10.16.15 Port {0..17} Filter Match Counter Value 2 Register.................................................................................................................387

10.16.16 Port {0..17} Filter Match Counter Value 3 Register.................................................................................................................387

10.16.17 Port {0..17} VC0 Acknowledgements Received Counter Register.........................................................................................388

10.16.18 Port {0..17} Not Acknowledgements Received Counter Register...........................................................................................388

10.16.19 Port {0..17} VC0 Retry Symbols Received Counter Register................................................................................................. 389

10.16.20 Port {0..17} VC0 Switch Crosspoint Buffer Output Packet Counter Register.........................................................................389

10.16.21 Port {0..17} VC0 Packets Received Counter Register............................................................................................................390

10.16.22 Port {0..17} Trace Port-Write Reset Register..........................................................................................................................391

10.16.23 Port {0..17} Lane Synchronization Register............................................................................................................................392

10.16.24 Port {0..17} VC0 Received Packets Dropped Counter Register.............................................................................................393

10.16.25 Port {0..17} VC0 Transmitted Packets Dropped Counter Register.........................................................................................394

10.16.26 Port {0..17} VC0 TTL Packets Dropped Counter Register..................................................................................................... 395

10.16.27 Port {0..17} VC0 CRC Limit Packets Dropped Counter Register........................................................................................... 395

10.16.28 Port {0..17} Congestion Retry Counter Register.....................................................................................................................396

10.16.29 Port {0..17} Status and Control Register................................................................................................................................397