Integrated Device Technology Inc 7429FCT53BTQ, 7429FCT53BTPYB, 7429FCT53BTPY, 7429FCT53BTPB, 7429FCT53BTP Datasheet

...

Integrated Device Technology, Inc.

FAST CMOS

OCTAL REGISTERED

TRANSCEIVERS

IDT29FCT52AT/BT/CT/DT

IDT29FCT2052AT/BT/CT

IDT29FCT53AT/BT/CT

FEATURES:

• Common features:

– Low input and output leakage ≤1µA (max.)

– CMOS power levels

– True TTL input and output compatibility

– VOH = 3.3V (typ.)

– V

OL = 0.3V (typ.)

– Meets or exceeds JEDEC standard 18 specifications

– Product available in Radiation Tolerant and Radiation

Enhanced versions

– Military product compliant to MIL-STD-883, Class B

and DESC listed (dual marked)

– Available in DIP, SOIC, SSOP, QSOP, CERPACK

and LCC packages

• Features for 29FCT52/29FCT53T:

– A, B, C and D speed grades

– High drive outputs (-15mA IOH, 64mA IOL)

– Power off disable outputs permit “live insertion”

• Features for 29FCT2052T:

– A, B and C speed grades

– Resistor outputs (-15mA IOH, 12mA IOL Com.)

(-12mA IOH, 12mA IOL Mil.)

– Reduced system switching noise

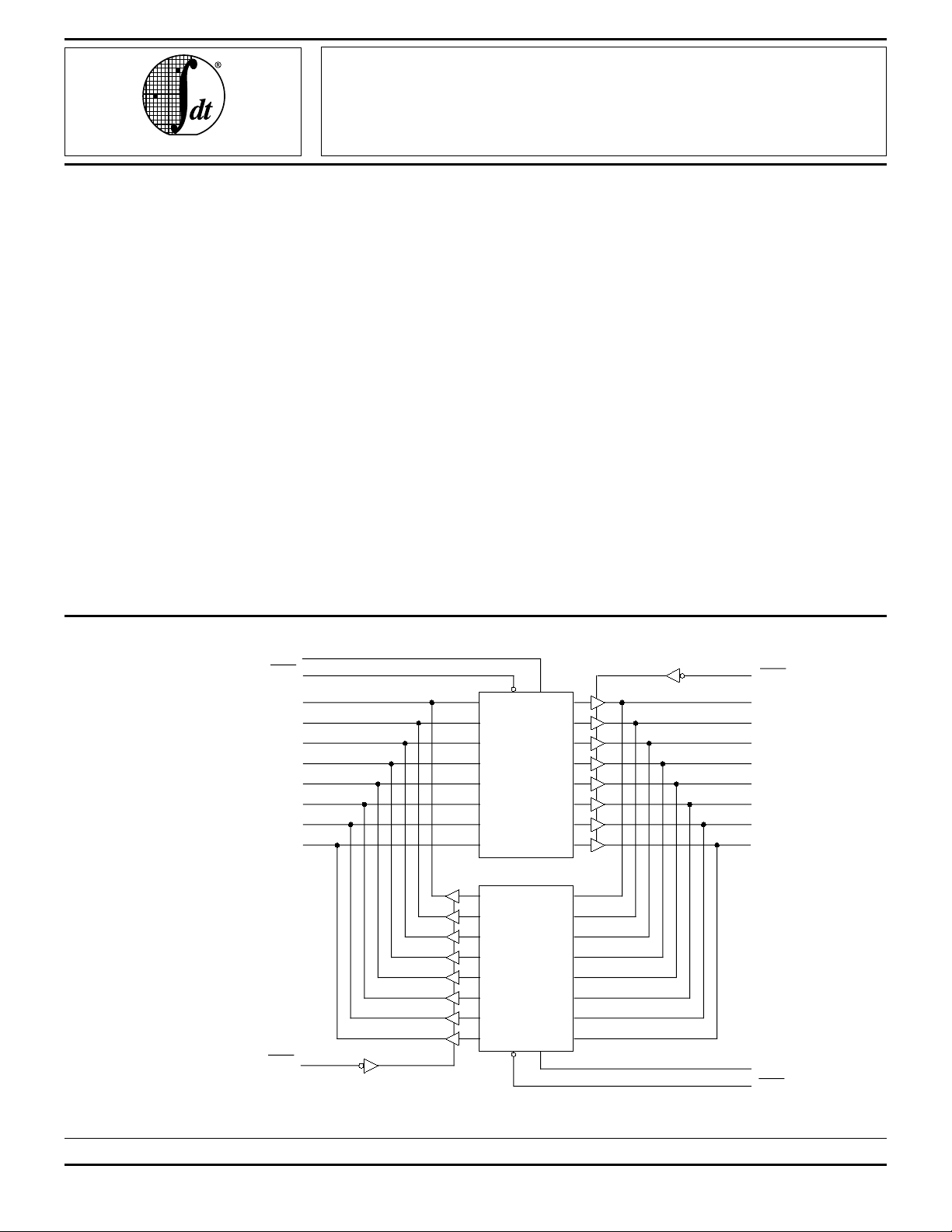

FUNCTIONAL BLOCK DIAGRAM

CPA

CEA

A

0

1

A

A

2

A

3

A

4

A

5

A

6

A

7

(1)

DESCRIPTION:

The IDT29FCT52AT/BT/CT/DT and IDT29FCT53AT/BT/

CT are 8-bit registered transceivers built using an advanced

dual metal CMOS technology. Two 8-bit back-to-back registers store data flowing in both directions between two bidirectional buses. Separate clock, clock enable and 3-state output

enable signals are provided for each register. Both A outputs

and B outputs are guaranteed to sink 64mA.

The IDT29FCT52AT/BT/CT/DT and IDT29FCT2052AT/BT/

CT are non-inverting options of the IDT29FCT53AT/BT/CT.

The IDT29FCT2052AT/BT/CT has balanced drive outputs

with current limiting resistors. This offers low ground bounce,

minimal undershoot and controlled output fall times-reducing

the need for external series terminating resistors. The

IDT29FCT2052T part is a plug-in replacement for

IDT29FCT52T part.

OEB

D

D

D

D

D

D

D

D

CE CP

0

1

2

3

4

5

6

7

A

Reg.

Q

0

Q

1

Q

2

Q

3

Q

4

Q

5

Q

6

Q

7

B

0

B

1

B

2

B

3

B

4

B

5

B

6

B

7

D

0

D

1

D

2

D

3

B

D

4

D

5

D

6

D

7

CPB

CEB

2629 drw 01

NOTE:

1. IDT29FCT52T/IDT29FCT2052T function is shown. IDT29FCT53T is

the inverting option.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

OEA

Q

Q

Q

Q

Q

Q

Q

Q

0

1

2

3

4

5

6

7

CE CP

Reg.

MILITARY AND COMMERCIAL TEMPERATURE RANGES JUNE 1995

1995 Integrated Device Technology, Inc. 6.1 DSC-4224/5

1

IDT29FCT52AT/BT/CT/DT, IDT29FCT/2052AT/BT/CT, IDT29FCT53AT/BT/CT

FAST CMOS OCTAL REGISTERED TRANSCEIVERS MILITARY AND COMMERCIAL TEMPERATURE RANGES

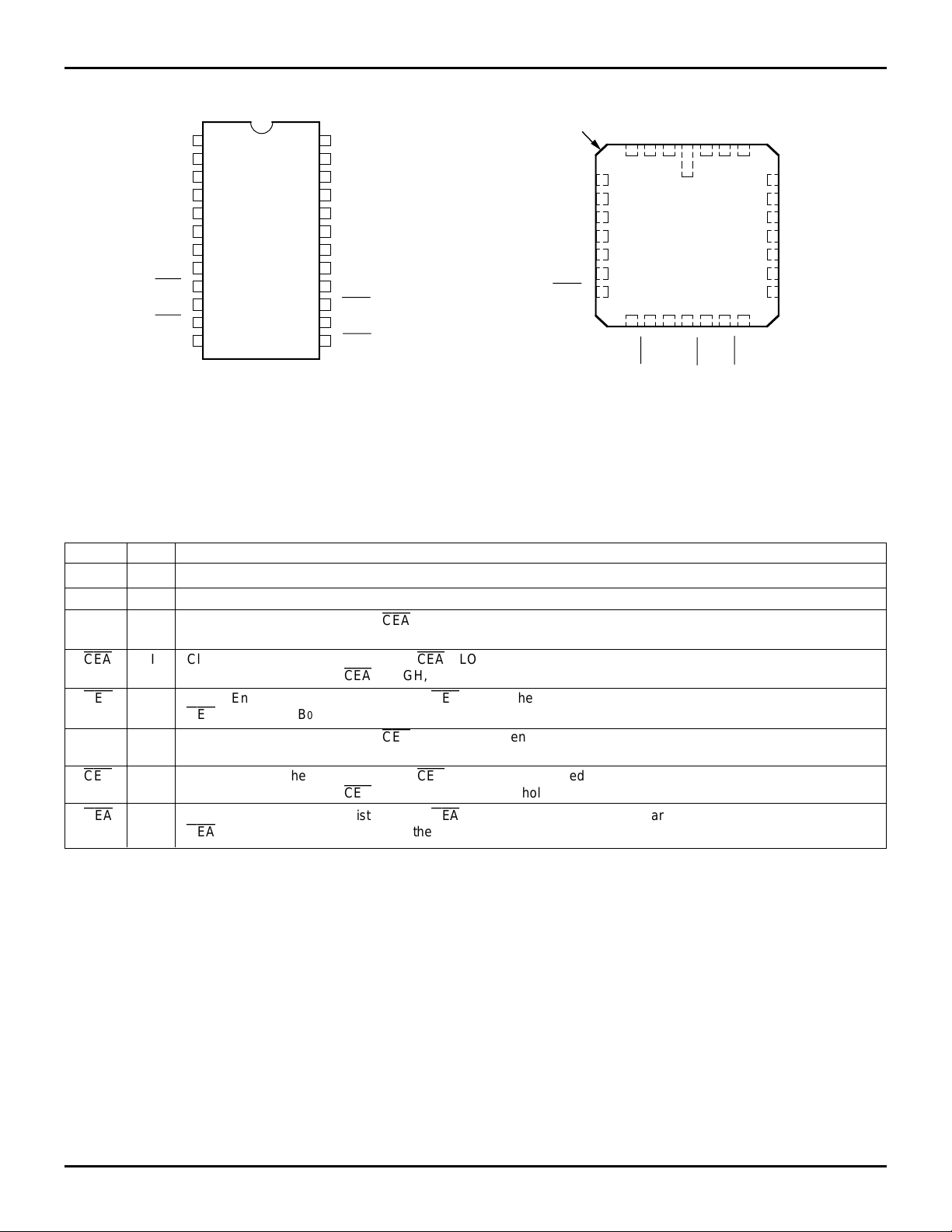

PIN CONFIGURATIONS

B

B

B5

B4

B

B

B1

B

OEB

CPA

CEA CPB

GND

1

7

2

6

3

P24-1

4

D24-1

5

3

2

0

6

7

8

9

10

11

12

SO24-2

SO24-7*

SO24-8*

E24-1

24

Vcc

23

A

22

21

20

19

18

17

&

16

15

14

13

7

A

6

A5

A4

A

3

A

2

A1

A0

OEA

CEB

2629 drw 02

5

6

INDEX

B

B

B2

NC NC

B1

B

5

4

6

3

7

8

9

10

0

11

12 13 14 15 16 17 18

7

B

432128 27 26

NC

B

B

L28-1

NC

CEA

CPA

GND

Vcc

CEB

6

A

A 7

CPB

OEA

25

24

23

22

21

20

19

A

5

A

4

A3

A

2

A

1

A0OEB

2629 drw 03

DIP/SOIC/SSOP/QSOP/CERPACK

TOP VIEW

* For 29FCT52/29FCT2052AT/BT/CT only

PIN DESCRIPTION

Name I/O Description

0-7 I/O Eight bidirectional lines carrying the A Register inputs or B Register outputs.

A

0-7 I/O Eight bidirectional lines carrying the B Register inputs or A Register outputs.

B

CPA I Clock for the A Register. When

the CPA signal.

CEA

I Clock Enable for the A Register. When

of the CPA signal. When

OEB

I Output Enable for the A Register. When

OEB

is HIGH, the B

0-7 outputs are in the high-impedance state.

CPB I Clock for the B Register. When

the CPB signal.

CEB

I Clock Enable for the B Register. When

of the CPB signal. When

OEA

I Output Enable for the B Register. When

OEA

is HIGH, the A

0-7 outputs are in the high-impedance state.

CEA

is LOW, data is entered into the A Register on the LOW-to-HIGH transition of

CEA

is LOW, data is entered into the A Register on the LOW-to-HIGH transition

CEA

is HIGH, the A Register holds its contents, regardless of CPA signal transitions.

OEB

is LOW, the A Register outputs are enabled onto the B

CEB

is LOW, data is entered into the B Register on the LOW-to-HIGH transition of

CEB

is LOW, data is entered into the B Register on the LOW-to-HIGH transition

CEB

is HIGH, the B Register holds its contents, regardless of CPB signal transitions.

OEA

is LOW, the B Register outputs are enabled onto the A

LCC

TOP VIEW

0-7 lines. When

0-7 lines. When

2629 tbl 01

6.1 2

IDT29FCT52AT/BT/CT/DT, IDT29FCT/2052AT/BT/CT, IDT29FCT53AT/BT/CT

FAST CMOS OCTAL REGISTERED TRANSCEIVERS MILITARY AND COMMERCIAL TEMPERATURE RANGES

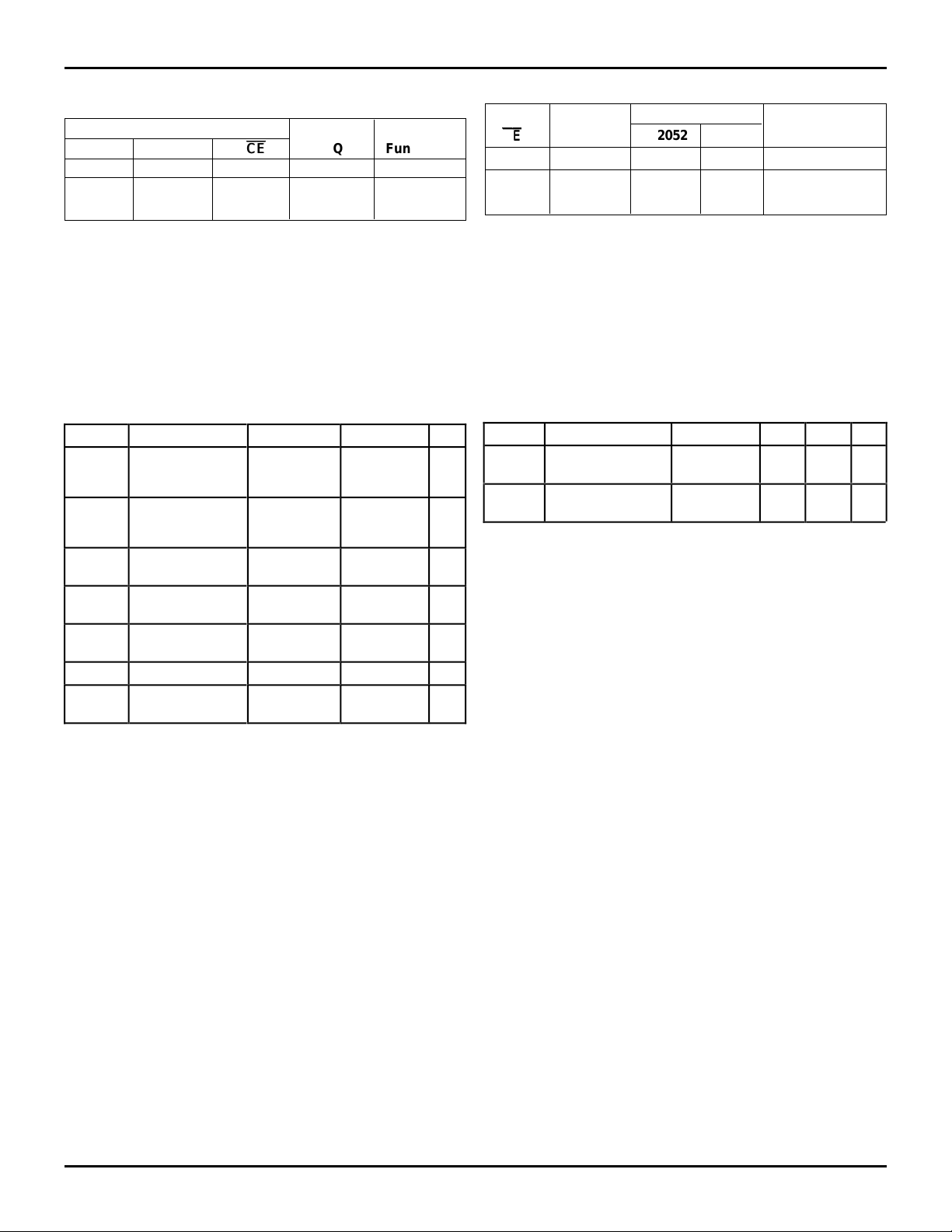

REGISTER FUNCTION TABLE

(1)

(Applies to A or B Register)

Inputs Internal

DCP

X X H NC Hold Data

L ↑ L L Load Data

H ↑ LH

NOTE:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

NC = No Change

↑ = LOW-to-HIGH Transition

Symbol Rating Commercial Military Unit

(2)

VTERM

Terminal Voltage

with Respect to

GND

(3)

VTERM

Terminal Voltage

with Respect to

GND

TA Operating

Temperature

TBIAS Temperature

Under Bias

TSTG Storage

Temperature

PT Power Dissipation 0.5 0.5 W

IOUT DC Output

Current

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating

only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not

extended periods may affect reliability. No terminal voltage may exceed

V

2. Input and V

3. Outputs and I/O terminals only.

implied. Exposure to absolute maximum rating conditions for

CC by +0.5V unless otherwise noted.

CC terminals only.

CE

CE

Q Function

2629 tbl 02

(1)

–0.5 to +7.0 –0.5 to +7.0 V

–0.5 to

CC +0.5

V

–0.5 to

VCC +0.5

0 to +70 –55 to +125 °C

–55 to +125 –65 to +135 °C

–55 to +125 –65 to +150 °C

–60 to +120 –60 to +120 mA

2529 lnk 04

V

OUTPUT CONTROL

(1)

Internal Y-Outputs

OE

OE

Q 52/2052 53 Function

H X Z Z Disable Outputs

L L L H Enable Outputs

LHHL

NOTE: 2629 tbl 03

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

Z = High Impedance

CAPACITANCE (TA = +25°C, f = 1.0MHz)ABSOLUTE MAXIMUM RATINGS

Symbol Parameter

CIN Input

Capacitance

COUT Output

Capacitance

NOTE:

1. This parameter is measured at characterization but not tested.

(1)

Conditions Typ. Max. Unit

VIN = 0V 6 10 pF

VOUT = 0V 8 12 pF

2640 lnk 05

6.1 3

Loading...

Loading...