ICT PEEL22LV10AZJ-25, PEEL22LV10AZJI-35, PEEL22LV10AZP-25, PEEL22LV10AZPI-35, PEEL22LV10AZS-25 Datasheet

...

PEEL™ 22LV10AZ-25 / I-35

CMOS Programmable Electrically Erasable Logic Device

Features

• Low Voltage, Ultra Low Power Operation

- Vcc = 2.7 to 3.6 V

- Icc = 5 µA (typical) at standby

- Icc = 1.5 mA (typical) at 1 MHz

- Meets JEDEC LV Interface Spec (JESD8-B)

- 5 Volt tolerant inputs and I/O’s

• CMOS Electrically Erasable Technology

- Superior factory testing

- Reprogrammable in plastic package

- Reduces retrofit and development costs

• Application Versatility

- Replaces random logic

- Super set of standard PLDs

- Pin and JEDEC compatible with 22V10

- Ideal for battery powered systems

- Replaces expensive oscillators

General Description

The PEEL22LV10AZ is a Programmable Electrically

Erasable Logic (PEEL) SPLD (Simple Programmable

Logic Device) that operates over the supply voltage

range of 2.7V-3.6V and features ultra-low, automatic

"zero" power-down operation. The PEEL22LV10AZ is

logically and functionally similar to ICT's 5V

PEEL22CV10A and PEEL 2 2CV10AZ. T he "zero p o wer"

(25 µA max. I

PEEL22LV10AZ ideal for a broad range of batterypowered portable equipment applications, from handheld meters to PCMCIA modems. EEreprogrammability provides both the convenience of

product fast reprogramming for product development

and quick personalization in manufacturing, including

Engineering Change Orders.

) power-down mode makes the

CC

Commercial/Industrial

• Architectural Flexibility

- Enhanced architecture fits in more logic

- 133 product terms x 44 input AND array

- 12 inputs and 10 I/O pins

- 12 possible macrocell configurations

- Asynchronous clear, synchronous preset

- Independent output enables

- Programmable clock; pin 1 or p-term

- Programmable clock polarity

- 24-Pin DIP/SOIC/TSSOP and 28 Pi n PLCC

- Schmitt triggers on clock and data inputs

• Schmitt Trigger Inputs

- Eliminates external Schmitt trigger devices

- Ideal for encoder designs

The differences between the PEEL22LV10AZ and

PEEL22CV10A include the addition of programmable

clock polarity, p-term clock, and Schmitt trigger input

buffers on all inputs, inc luding the clock . Schmitt trigger

inputs allow direct input of slow signals such as

biomedical and sine waves or clocks. Like the

PEEL22CV10A, the PEEL22LV10AZ is a pin and

JEDEC compatible, logical superset of the industry

standard PAL22V10 SPLD Figure 1. The

PEEL22LV10AZ provides additional architectural

features that allow more logic to be incorporated into

the design. The PEEL22LV10AZ architecture allows it

to replace over twenty standard 24-pin DIP, SOIC,

TSSOP and PLCC packages.

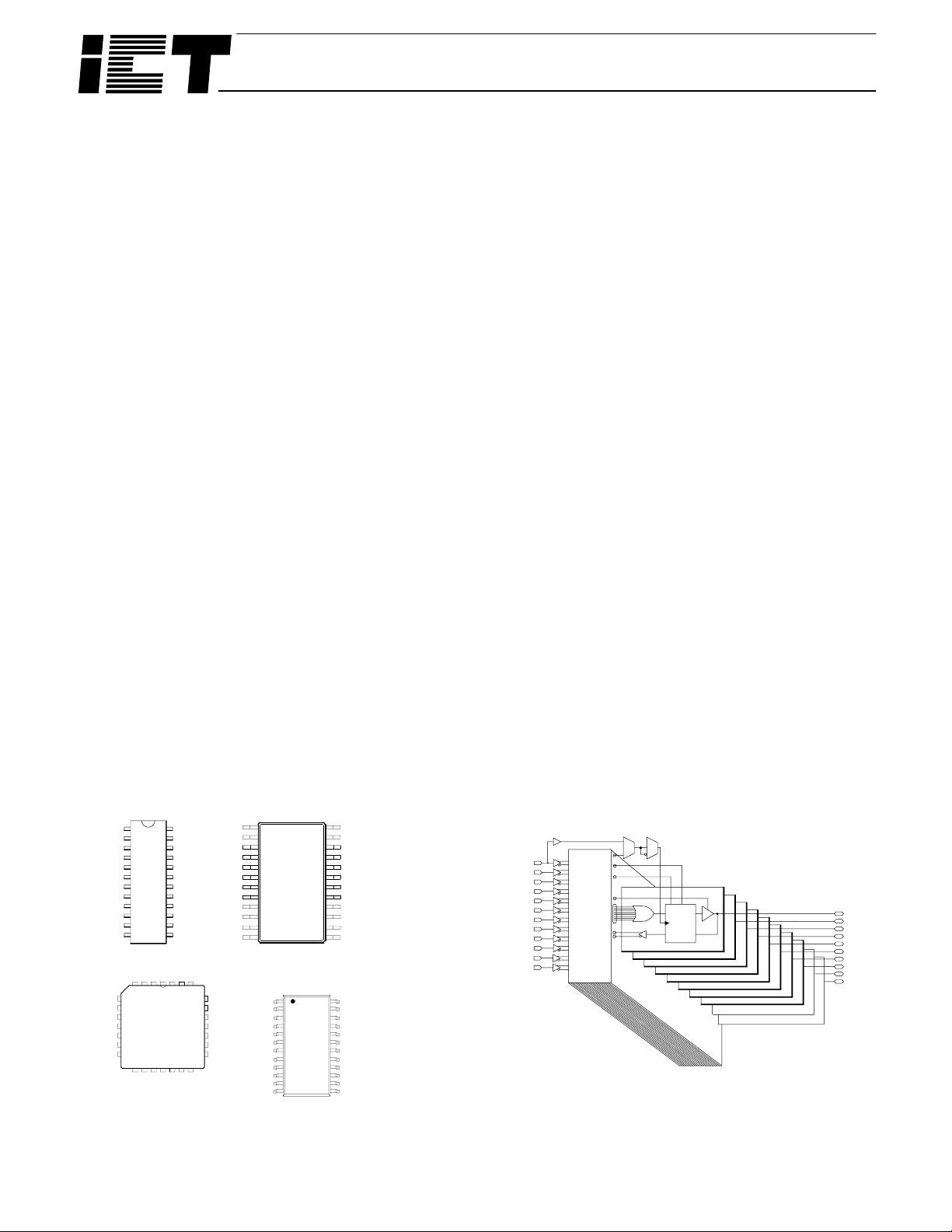

Figure 1 - Pin Configuration

I/CLK

GND

DIP

I

I

I

NC

I

I

I

PLCC

1

24

I

2

23

3

I

22

I

4

21

I

5

20

I

19

6

I

18

7

8

I

17

9

I

16

10

I

15

11

14

I

12

13

I/CLKII

NC

2

4

5

6

7

8

9

10

11

NC

GND

VCC

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

VCC

III

I/CLK

GND

I/O

I/O

2628 2713

I/O

25

I/O

24

I/O

23

NC

22

I/O

21

I/O

20

I/O

19

181716141312 15

I/O

I/O

1

I

2

I

3

I

4

I

5

I

6

I

7

8

I

9

I

10

I

11

I

12

I/CLK

I

I

I

I

I

I

I

I

I

I

GND

Figure 2 - Block Diagram

VCC

24

I/O

23

I/O

22

I/O

21

I/O

20

19

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I/O

13

I

TSSOP

1

24

23

22

21

20

19

18

17

16

15

14

13

VCC

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

SOIC

2

3

4

5

6

7

8

9

10

11

12

I/CLK

I

I

I

I

I

I

I

I

I

I

I

PEEL

ARRAY

133 Terms

44 Inp u ts

1

"AND"

X

CLK MUX (Optional)

TM

SP

AC

OE

MACRO

CELL

SP = SYNCHRONOUS PRESET

AC = ASYNCHRONOUS CLEAR

OE = OUTPUT ENABLE

04-02-037D

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

(

I/CLK*

)

)

PEELTM 22LV10AZ

132

0

2

9

10

(2)

ASYNC H R O NOUS C L EAR

(TO ALL MACR OCELLS

MACRO

CELL

N

I/O*

(27)

MACRO

20

I*

21

(3)

33

I*

34

(4)

48

I*

49

(5)

65

I*

66

(6)

82

I*

83

(7)

CELL

MACRO

CELL

MACRO

CELL

MACRO

CELL

MACRO

CELL

I/O*

(26)

I/O*

(25)

I/O*

(24)

I/O*

(23)

I/O*

(21)

MACRO

97

CELL

I/O*

(20)

I*

98

(9)

MACRO

110

I*

111

(10 )

121

I*

124

(11 )

130

I*

(12 )

131

CELL

MACRO

CELL

MACRO

CELL

SYNCHRONOUS PRESET

(TO ALL MACR OCELLS

I*

(13 )

* Schmitt Trigger Inputs

I/O*

(19)

I/O*

(18)

I/O*

(17)

I*

(16)

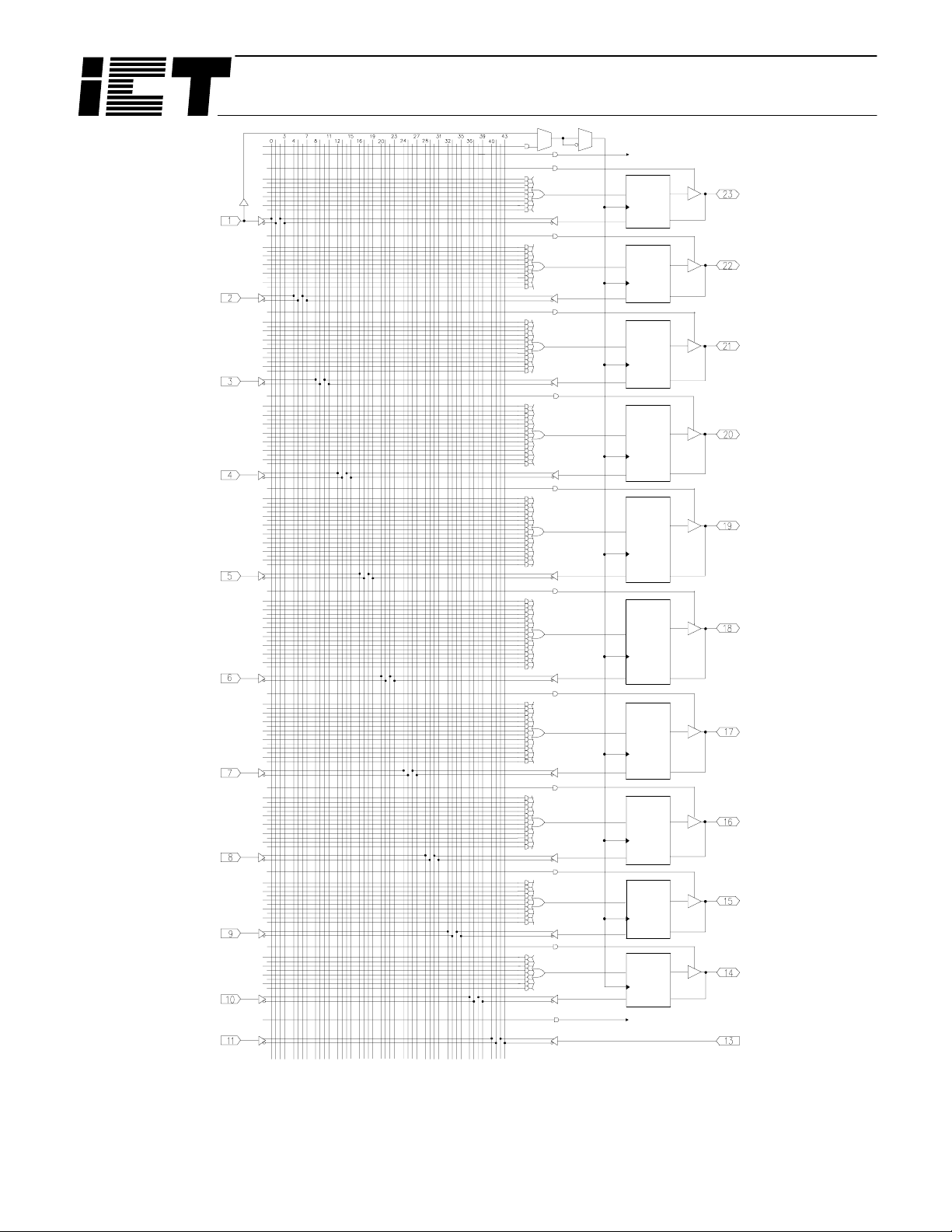

Figure 3 - PEEL22LV10AZ Logic Array Diagram

2

04-02-037D

PEELTM 22LV10AZ

Function Description

The PEEL22LV10AZ implements logic f unctions as s u m -of- pr oducts ex pres s ions in a pr ogr am mable-AND/fixed-OR

logic array. User-defined functions are created by programming the connections of input signals into the array.

User-configurable output structures in the form of I/O macrocells further increase logic flexibility.

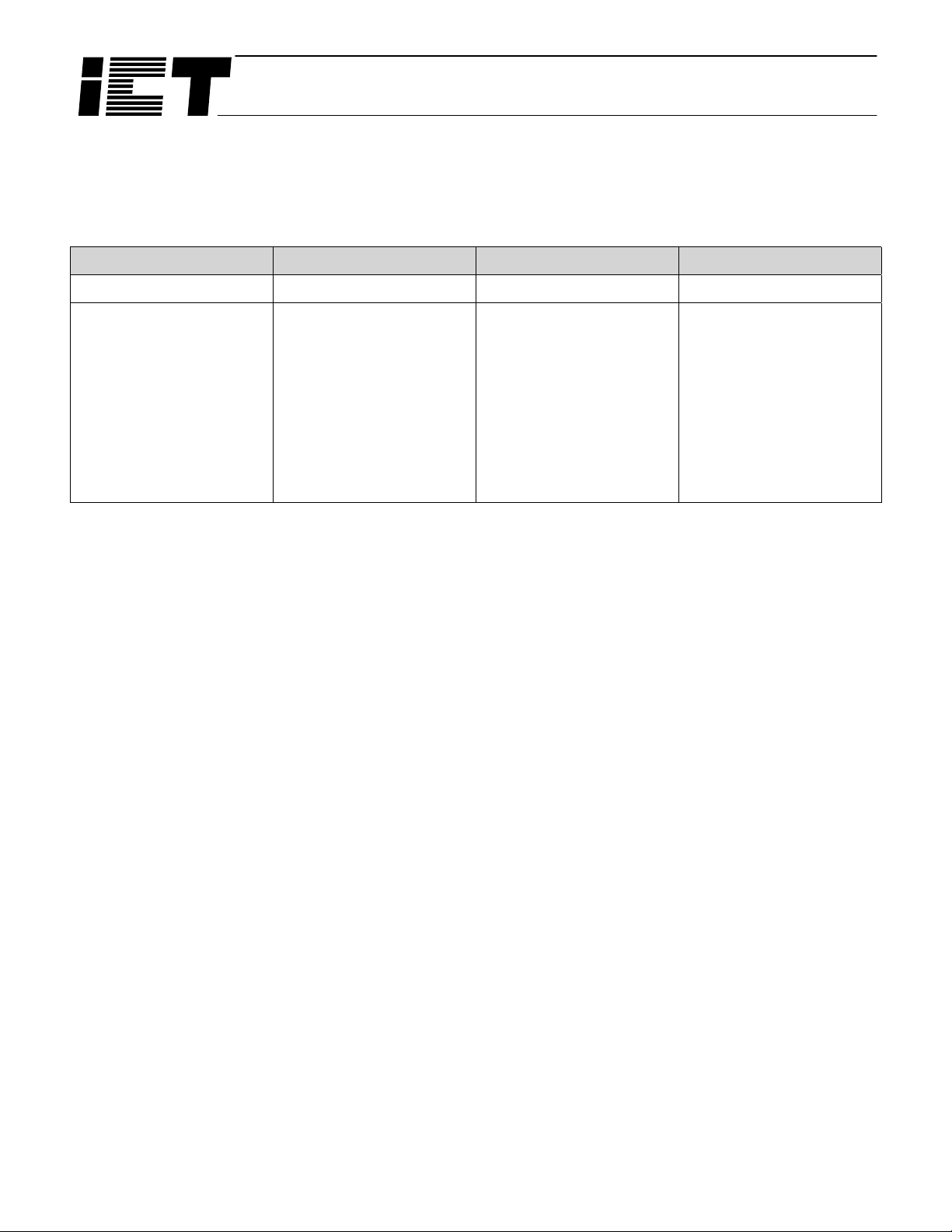

ICT has added opti onal enhanc ed cap abil ities to the PEEL2 2CV10 A fam il y of pr oducts with addit iona l featur es and

added fuses to support them. Please view the comparison chart found below for the best algorithm

Algorithms PEEL V10A Algorithm PEEL V10A+ Algorit hm PEEL V10A++ Algorithm

Number of Fuses 5828 5873 5958

Supported Features Standard 22V10 JEDEC

Compatible

4 macrocell options 12 macrocell options 12 macrocell options

3 byte signature word 8 byte signature word

Security bit Security bit

Clock source selection

Clock polarity selection

Table 1 - Programming Algorithm Comparison

Architecture Overview

The PEEL22LV10AZ architecture is illustrated in the

block diagram of F igure 2. Twelve dedicat ed inputs and

10 I/Os provide up to 22 inputs and 10 outputs for

creation of logic f unctions. At th e core of the devic e is a

programmable electrically erasable AND array that

drives a fixed OR array. With this structure, the

PEEL22LV10AZ can implement up to 10 sum-ofproducts logic expressions.

Associated with eac h of the ten OR functions is a n I/O

macrocell that can be independently programmed to

one of 12 different configurations, including the four

standard 22V10 m odes. The programm able macrocells

allow each I/O to be used to create sequential or

combinatorial logic f unctio ns of ac tive- high or act ive-lo w

polarity, while providing three different feedback paths

into the AND array.

AND/OR Logic Array

The programmable AND array of the PEEL22LV10AZ

(shown in Figure 3) is form ed by input lines inter secting

product terms. The input lines and product terms are

used as follows:

• 44 Input Lines:

- 24 input lines car ry the true and com plement

of the signals applied to the 12 input pins

- 20 additional lines carry the true and

complement values of feedback or input

signals from the 10 I/Os

Superset of standard

22V10

• 133 Product Terms:

- 120 product terms (arrange d in 2 gr oups of 8,

10, 12, 14, and 16) are used to form sum of

product functions

- 10 outputs enable terms (one for each I/O)

- 1 global synchronous preset term

- 1 global asynchronous clear term

- 1 programmable clock term

At each input-line/prod uct-term intersection, there is an

EEPROM memor y cell that determ ines whether or not

there is a logical connection at that intersection. Each

product term is essentially a 44-input AND gate. A

product term that is connected to both the true and

complement of an input signal will always be FALSE

and thus will not affect the OR function that it drives.

When all the connections on a product term are

opened, a "don't care" state exists and that term will

always be TRUE.

When programming the PEEL22LV10AZ, the device

programmer first performs a bulk erase to remove the

previous pattern. The erase cycle opens every logical

connection in the array. The device is configured to

perform the user-defined function by programming

selected connections in t he AND ar ra y. (Not e that PE E L

device programmers automatically program all of the

connections on unused pr oduct terms so that they will

have no effect on the output function).

Superset of standard

22V10 (recommended for

new designs)

3

04-02-037D

Loading...

Loading...