ICT PEEL18LV8ZJ-25, PEEL18LV8ZJI-35, PEEL18LV8ZP-25, PEEL18LV8ZPI-35, PEEL18LV8ZS-25 Datasheet

...

Features

Commercial/Industrial

PEEL™ 18LV8Z-25 / I-35

CMOS Programmable Electrically Erasable Logic Device

• Low Voltage, Ultra Low Power Operation

- Vcc = 2.7 to 3.6 V

- Icc = 5 µA (typical) at standby

- Icc = 1.5 mA (typical) at 1 MHz

- Meets JEDEC LV Interface Spec (JEDSD8-A)

- 5 Volts tolerant inputs and I/O’s

• CMOS Electrically Erasable Technology

- Superior factory testing

- Reprogrammable in plastic package

- Reduces retrofit and development costs

• Application Versatility

- Replaces random logic

- Super set of standard PLDs

- Pin-to-pin compatible with 16V8

- Ideal for battery powered systems

- Replaces expensive oscillators

General Description

The PEEL18LV8Z is a Programm able Electric ally Era sable

Logic (PEEL) S PLD (Simple Programm able Logic Device)

that operates over the supply voltage range of 2.7V-3.6V

and features ultra-low, automatic "zero" power-down

operation. The PEEL18LV8Z is logically and functionally

similar to ICT's 5V PEEL18CV8 and PEEL18CV8Z. The

"zero power" (25 µA max. Icc) power-down mode makes

the PEEL18LV8Z ideal for a broad range of batterypowered portable equipment applications, from hand-held

meters to PCMCIA modems. EE-reprogrammability

provides both the convenience of fast reprogramming for

product development and quick product personalization in

manufacturing, including Engineering Change Orders.

1

I/CLK1

GND

DIP

PLCC-J

1

I

2

I

3

I

4

I

5

6

I

7

I

8

I

9

I

10

I/O 2I/O

3

I

4

I

5

I

6

I

7

I

8

9I10

GND

1

11I12

V

20

19

18

17

16

15

14

13

12

11

VCC19I/O

I/CLK1

20

I/O13I/O

I/CLK1

CC

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

I

I/O

GND

I

I/CLK1

I

I

I/O

18

17

16

15

14

I

I/O

I

I/O

I

I/O

I

I/O

I

I

GND

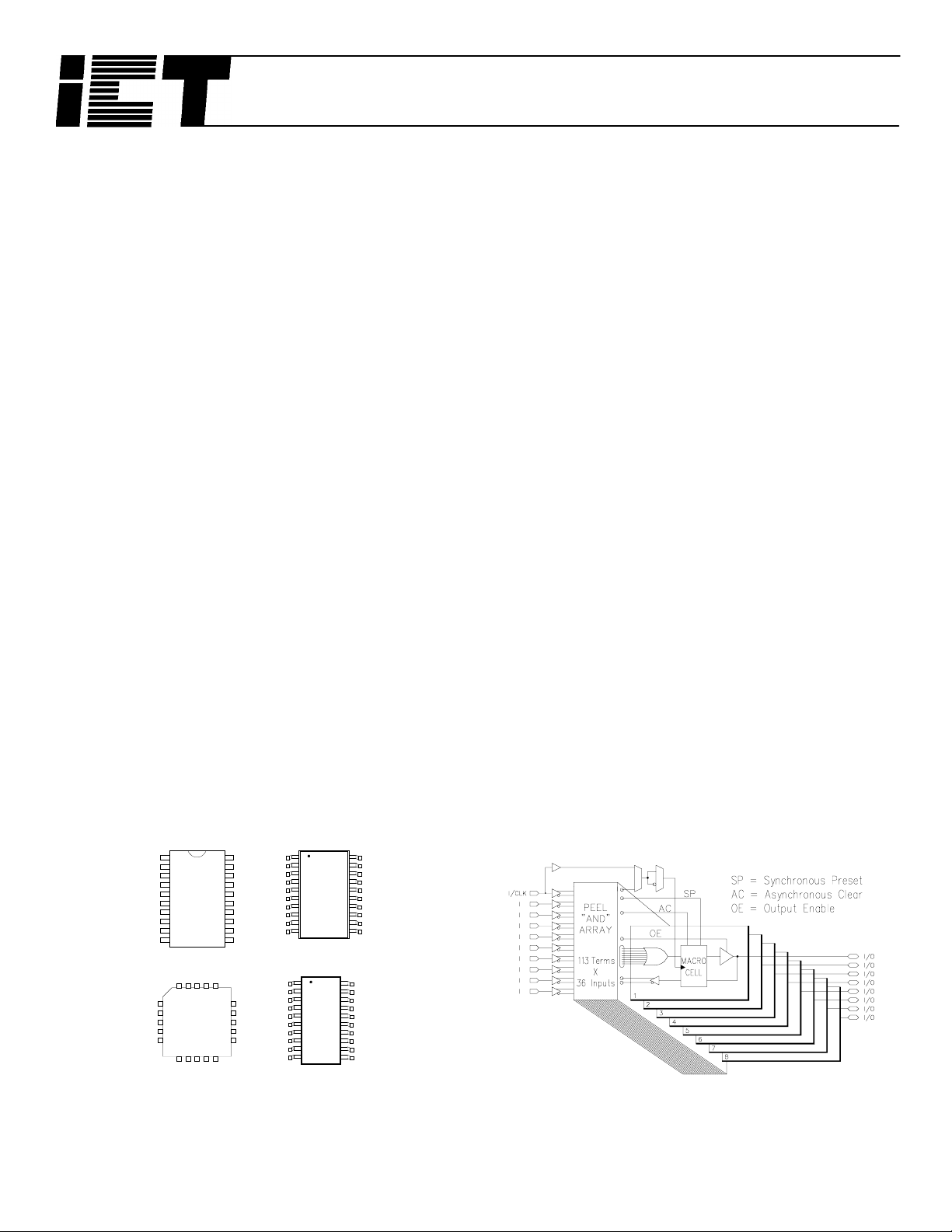

Figure 1 - Pin Configuration

20

V

2

3

4

5

6

7

8

9

10

1

2

3

4

5

6

7

8

9

10

CC

19

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I/O

13

I/O

12

I/O

11

I

TSSOP

20

V

CC

19

I/O

18

I/O

17

I/O

16

I/O

15

I/O

14

I/O

13

I/O

12

I/O

11

I

SOIC

• Architectural Flexibility

- Enhanced architecture fits in more logic

- 113 product terms x 36 input AND array

- 10 inputs and 8 I/O pins

- 12 possible macrocell configurations

- Asynchronous clear, Synchronous preset

- Independent output enables

- Programmable clock; pin 1 or p-term

- Programmable clock polarity

- 20 Pin DIP/SOIC/TSSOP and PLCC

- Schmitt triggers on clock and data inputs

• Schmitt Trigger Inputs

- Eliminates external Schmitt trigger devices

- Ideal for encoder designs

The differences between the PEEL18LV8Z and

PEEL18CV8 include the addition of programmable clock

polarity, p-term c lock, and Schmitt trigger input buffer s on

all inputs, including the clock. Schmitt trigger inputs allow

direct input of slow or noisy signals.

Like the PEEL18CV8, the PEEL18LV8Z is a logical

superset of the industry standard PAL16V8 SPLD. The

PEEL18LV8Z provides ad d iti ona l arc hit ec tur a l f eatur es that

allow more logic to be inc orporated into the design. ICT's

JEDEC file translator allo ws eas y conversion of ex isting 20

pin PLD designs to t he PEEL18LV8Z architecture w ithout

the need for redesign. The PEEL18LV8Z architecture

allows it to replace over t went y standar d 20- pin DI P, SOIC,

TSSOP and PLCC packages Pin Configuration.

C LK M U X (Opt io n al)

ª

Figure 2 - Block Diagram

1 of 10 04-02-042D

I/CLK

PEEL 18LV8Z

(OPTIONAL)

03478111215161920232427283132

112

0

1

2

9

1

10

11

20

2

I

21

22

33

3

I

I

34

35

48

4

49

50

35

ASYNCHRONOUS CLEAR

(TO ALL MACROCELLS)

19

MACRO

I/O

CELL

18

MACRO

CELL

MACRO

I/O

I/O

17

CELL

I/O

MACRO

CELL

16

I 5

I

I

I

I

I/O

MACRO

65

66

67

82

CELL

MACRO

CELL

15

I/O

14

6

83

84

I/O

MACRO

97

CELL

13

7

98

99

12

MACRO

110

8

111

CELL

SYNCHRONOUS PRESET

(TO ALL MACROCELLS)

9

I/O

11

I

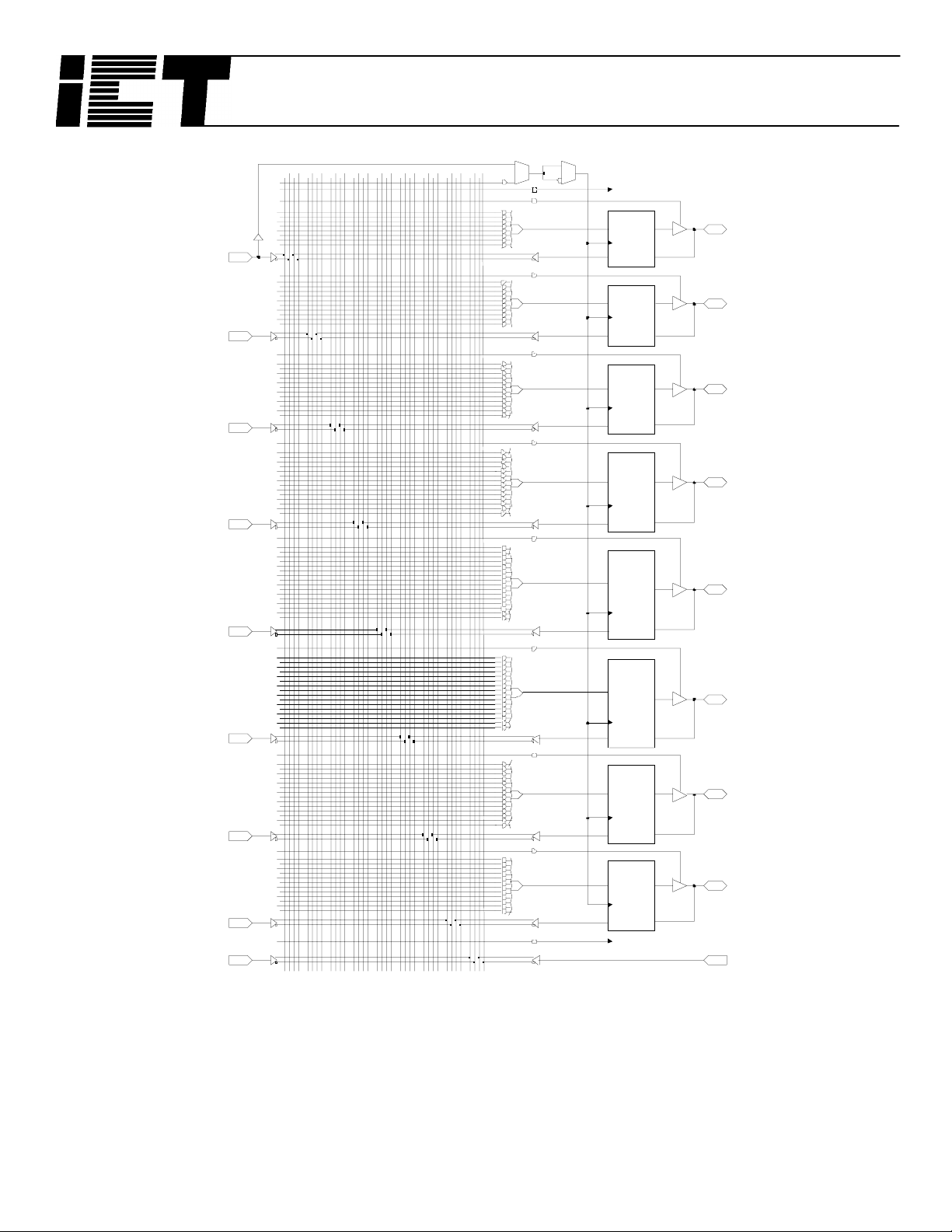

Figure 3 - PEEL18LV8Z Logic Array Diagram

Function Description

The PEEL18LV8Z implements logic functions as sum-ofproducts expressions in a programmable-AND/fixed-OR

logic array. Program ming the connections of input signals

into the array creates user-defined functions. Userconfigurable output st ructures in the f orm of I/O m acrocells

further increase logic flexibility.

2 of 10

04-02-042D

Architecture Overview

The PEEL18LV8Z architecture is illustrated in the block

diagram of Figure 14. Ten dedicated inputs and 8 I/Os

provide up to 18 inputs and 8 outputs f or creation of logic

functions. At the core of the device is a programmable

electrically erasable AND array that drives a fixed OR

array. With this str ucture, the PEEL18LV8Z can implem ent

up to 8 sum-of-products logic expressions.

Associated with each of the 8 OR functions is an I/O

macrocell that can be inde pendent ly progr amm ed to one of

12 different configurations. The programmable macrocells

allow each I/O to be used to create sequential or

combinatorial logic functions of active-high or active-low

polarity, while pro viding three diff erent feedback paths into

the AND array.

AND/OR Logic Array

The programm able AND arr ay of the PEEL18L V8Z (s hown

in Figure 15) is form ed by input lines intersecting product

terms. The input lines and product terms are used as

follows:

• 36 Input Lines:

- 20 input lines carry the true and complem ent of

the signals applied to the 10 input pins

- 16 additional l ines carr y the tru e and com plem ent

values of feedback or input signals from the 8

I/Os

• 113 product terms:

- 102 product terms are used to form sum of

product functions

- 8 output enable terms (one for each I/O)

- 1 global synchronous preset term

- 1 global asynchronous clear term

- 1 programmable clock term

PEEL 18LV8Z

on unused product t erm s so th at th ey will have no effec t on

the output function).

Variable Product Term Distribution

The PEEL18LV8Z provides 113 produc t terms to driv e the

8 OR functions. These product terms are distributed

among the outputs in groups of 8, 10, 12, 14, and 16 to

form logical sum s (see Figure 15). This distributio n allows

optimum use of the device resources.

Programmable I/O Macrocell

The unique twelve- configuration output m acrocell provides

complete control ov er the architecture of each out put. The

ability to configure each output independently lets you to

tailor the configuratio n of the PEEL18LV8Z to the precise

requirements of your design.

Macrocell Architecture

Each I/O macrocell, as shown in Figure 4, cons ists of a Dtype flip-flop and two signal-select multiplexers. The four

EEPROM bits controll ing these multiplexers determ ine the

configuration of each macrocell. These bits determine

output polarity, output type (registered or non-registered)

and input-feedback path (bidirectional I/O, combinatorial

feedback). Refer to Table 1 for details.

Equivalent circuits for the twelve macrocell configurations

are illustrated in F igure 5. In addition to emulating the f our

PAL-type output s tructures (conf igurations 3 , 4, 9, and 10),

the macrocell provides eight additional configurations.

When creating a PEEL device design, the desired

macrocell configuration is generally specified explicitly in

the design file. W hen the des ign is as sem bled or c ompil ed,

the macrocell conf iguration bits are defined in the last lin es

of the JEDEC programming file.

At each input-line/product-term intersection, there is an

EEPROM memory cell that determines whether or not

there is a logical connection at that intersection. Each

product term is es sentially a 36-inp ut AND gate. A product

term that is connected to both the tru e and complement of

an input signal will always be FALSE and thus will not

affect the OR function that it drives. When all the

connections on a product t erm are opened, a "don't care"

state exists and that term will always be TRUE.

When programming the PEEL18LV8Z, the device

programmer first performs a bulk erase to remove the

previous pattern. The erase cycle opens every logical

connection in the array. The device is configured to

perform the user-def ined f unc tion b y progr am ming selected

connections in the AND array. (Note that PEEL device

programmers autom atically program all of the c onnections

Output Type

The signal from the OR array can be fed directly to the

output pin (com binatorial function) or latched in the D-type

flip-flop (registered function). The D-type flip-flop latches

data on the rising edge of the c lock and is contr olled by the

global preset and clear terms. When the synchronous

preset term is satis fied, the Q output of the reg ister is set

HIGH at the next risi ng edge of the clock input. Satisfying

the asynchronous clear sets Q LOW, regardless of the

clock state. If both term s are satisfied simultaneously, the

clear will override the preset.

Output Polarity

Each macrocell c a n b e c on figured to implement active-high

or active-low logic. Programmable polarity eliminates the

need for external inverters.

3 of 10

04-02-042D

Loading...

Loading...