ICST MK74ZD133FT, MK74ZD133Y, MK74ZD133YT, MK74ZD133F Datasheet

PRELIMINARY

PRELIMINARY

INFORMATION

INFORMATION

MK74ZD133

PLL and 32-Output Clock Driver

Description

The MK74ZD133 is a monolithic CMOS high

speed clock driver that includes an on-chip PLL

(Phase Locked Loop). Ideal for communications

and other systems that require a large number of

high-speed clocks, the unique combination of PLL

and 32 outputs can eliminate oscillators and

multiple low skew buffers. With 32 outputs

included in one device, there is also no need to

worry about chip-to-chip skew. The zero delay

modes cause the input clock rising edge to be

synchronized with all of the outputs’ rising edges.

The MK74ZD133 has a large selection of built-in

multipliers, making it possible to run from a clock

input as low as 10 MHz and generate high

frequency outputs up to 80 MHz in the SSOP. For

speeds up to 133.33 MHz, use the LQFP package.

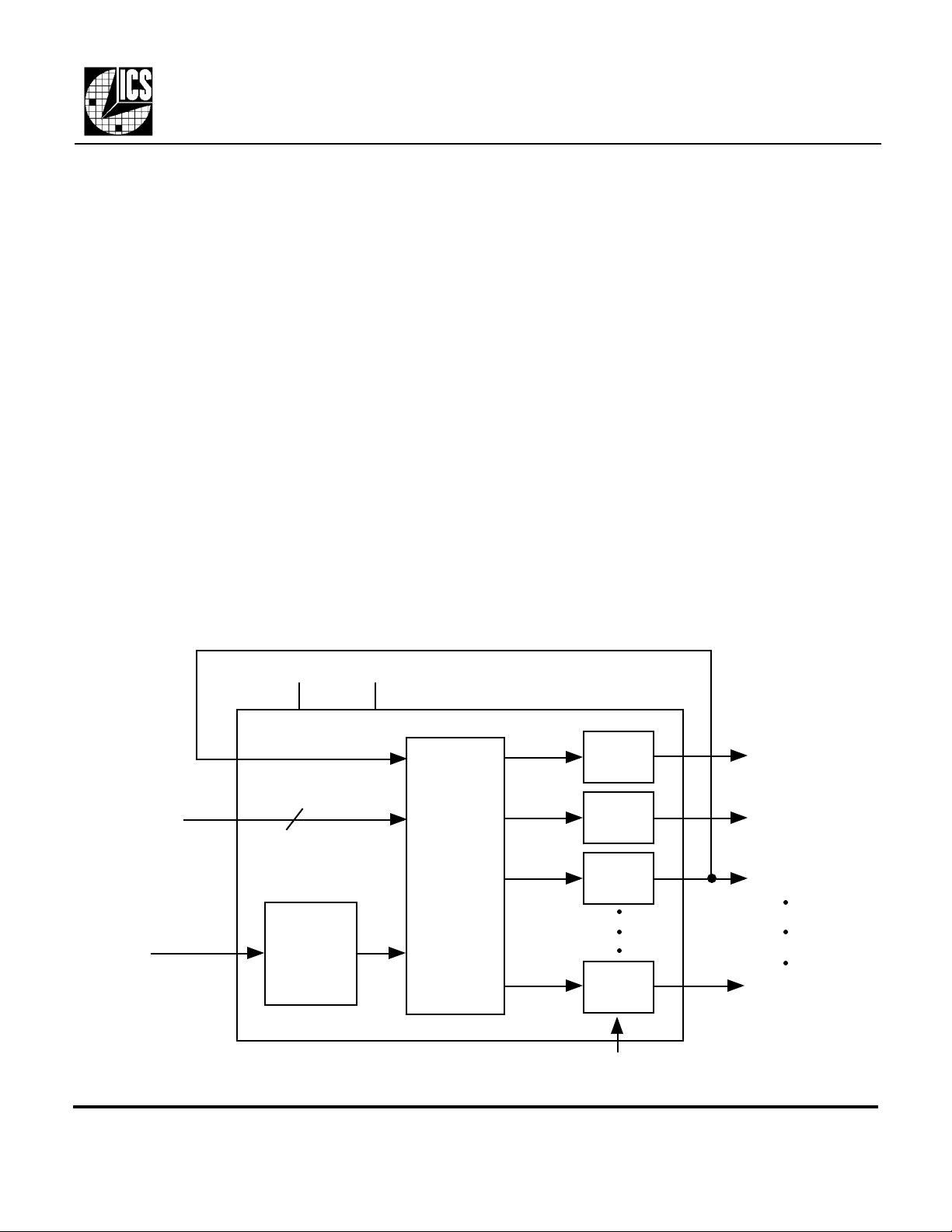

Block Diagram

Optional External Connection to Output 3 (for Zero Delay Mode)

Features

• 56 pin SSOP or 64 pin LQFP package

• On-chip PLL generates output clocks up to

80 MHz (SSOP) or 133.33 MHz (LQFP)

• Zero delay plus multiplier function

• 32 low-skew outputs can eliminate chip-to-chip

skew concerns in systems with less than 33 clocks

• Output to output skew of 200 ps (with stagger)

• Device to device skew of 700ps

• Staggered, fixed skew helps reduce EMI

• Tri-state (Output Enable) pin

• Output blocks can be independently powered off

• 250 ps typical fixed delay between input and

output in “Multiplier” mode

• Ideal for Fast Ethernet and Gigabit Ethernet

designs

• Good for video servers

• 3.3V±5% supply voltage

VDD

FBIN

S4:0

Clock input

MDS 74ZD133 C 1 Revision 010899 Printed 11/17/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•www.icst.com

5

Input

Buffer

GND

Clock

Synthesis

Circuitry

Output

Buffer

Output

Buffer

Output

Buffer

Output

Buffer

OE (all outputs)

Output 1

Output 2

Output 3

Output 32

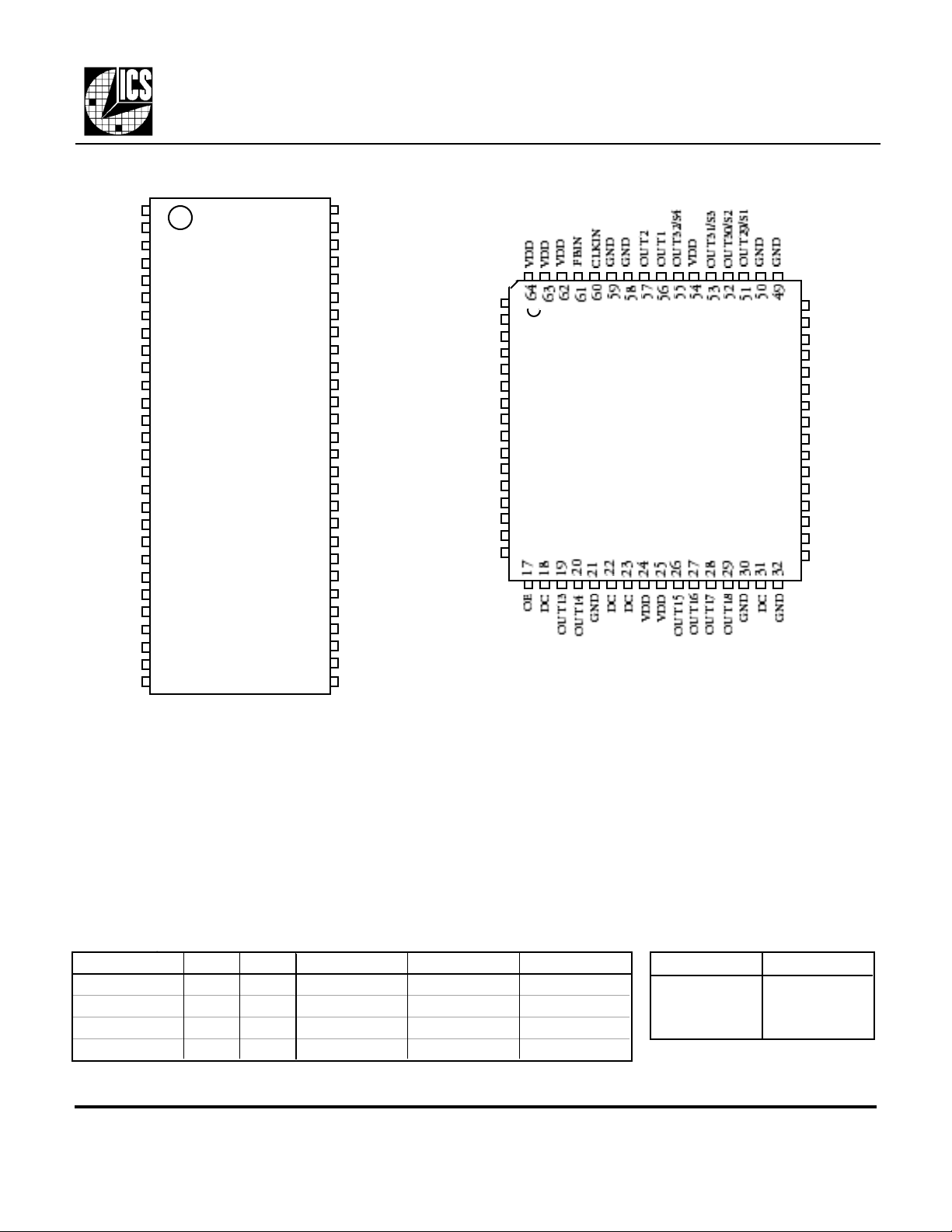

Pin Assignments

PRELIMINARY

PRELIMINARY

INFORMATION

INFORMATION

MK74ZD133

PLL and 32-Output Clock Driver

OUT1

OUT2

GND

CLKIN

FBIN

VDD

VDD

FBOUT3

OUT4

GND

OUT5

OUT6

VDD5:8

OUT7

OUT8

GND

OUT9

OUT10

VDD9:12

OUT11

OUT12

GND

VDD13:14

OE

OUT13

OUT14

GND

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

SSOP

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

OUT32/S4

VDD

OUT31/S3

OUT30/S2

OUT29/S1

GND

VDD

OUT28/S0

OUT27

OUT26

OUT25

GND

OUT24

OUT23

VDD21:24

OUT22

OUT21

GND

OUT20

OUT19

VDD

VDD

GND

OUT18

OUT17

OUT16

OUT15

VDD

FBOUT3

OUT4

GND

OUT5

OUT6

VDD5:8

OUT7

OUT8

GND

OUT9

OUT10

VDD9:12

OUT11

OUT12

GND

VDD13:14

1

2

3

4

5

6

7

8

LQFP

9

10

11

12

13

14

15

16

Y Package 10mm x 10mm x 1.4mm

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

VDD

OUT28/S0

OUT27

OUT26

OUT25

GND

OUT24

OUT23

VDD21:24

OUT22

OUT21

GND

OUT20

OUT19

VDD

VDD

F Package 300 mil wide

Controlling the Output Blocks

The MK74ZD133 offers a unique power supply structure that effectively creates five separate blocks of

outputs. The main supply (VDD) goes to all internal circuitry and to 18 outputs, as shown in the Pin

Descriptions table. The other 14 outputs are split into 4 blocks that are powered independently of the main

VDD supply. Each block has its own supply which can be the same as VDD, less than VDD, or left

unpowered to shut off the corresponding outputs. For example, with VDD = 3.3 V, VDD5:8 can be

unconnected and the OUT5:8 levels will be floating. The table below summarizes the power supply control

of the MK74ZD133.

VDD Name F Pin # Y Pin # Output Name F Pin Numbers Y Pin Numbers

VDD5:8 13 6 OUT5:8 11, 12, 14, 15 4, 5, 7, 8

VDD9:12 19 12 OUT9:12 17, 18, 20, 21 10, 11, 13, 14

VDD13:14 23 16 OUT13:14 25, 26 19, 20

VDD21:24 42 40 OUT21:24 40, 41, 43, 44 38, 39, 41, 42

MDS 74ZD133 C 2 Revision 010899 Printed 11/17/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•www.icst.com

F Main Supply Y Main Supply

6, 7, 28, 29 24, 25, 33, 34

35, 36, 50, 55 48, 54, 62, 63

and 64

PRELIMINARY

PRELIMINARY

INFORMATION

INFORMATION

MK74ZD133

PLL and 32-Output Clock Driver

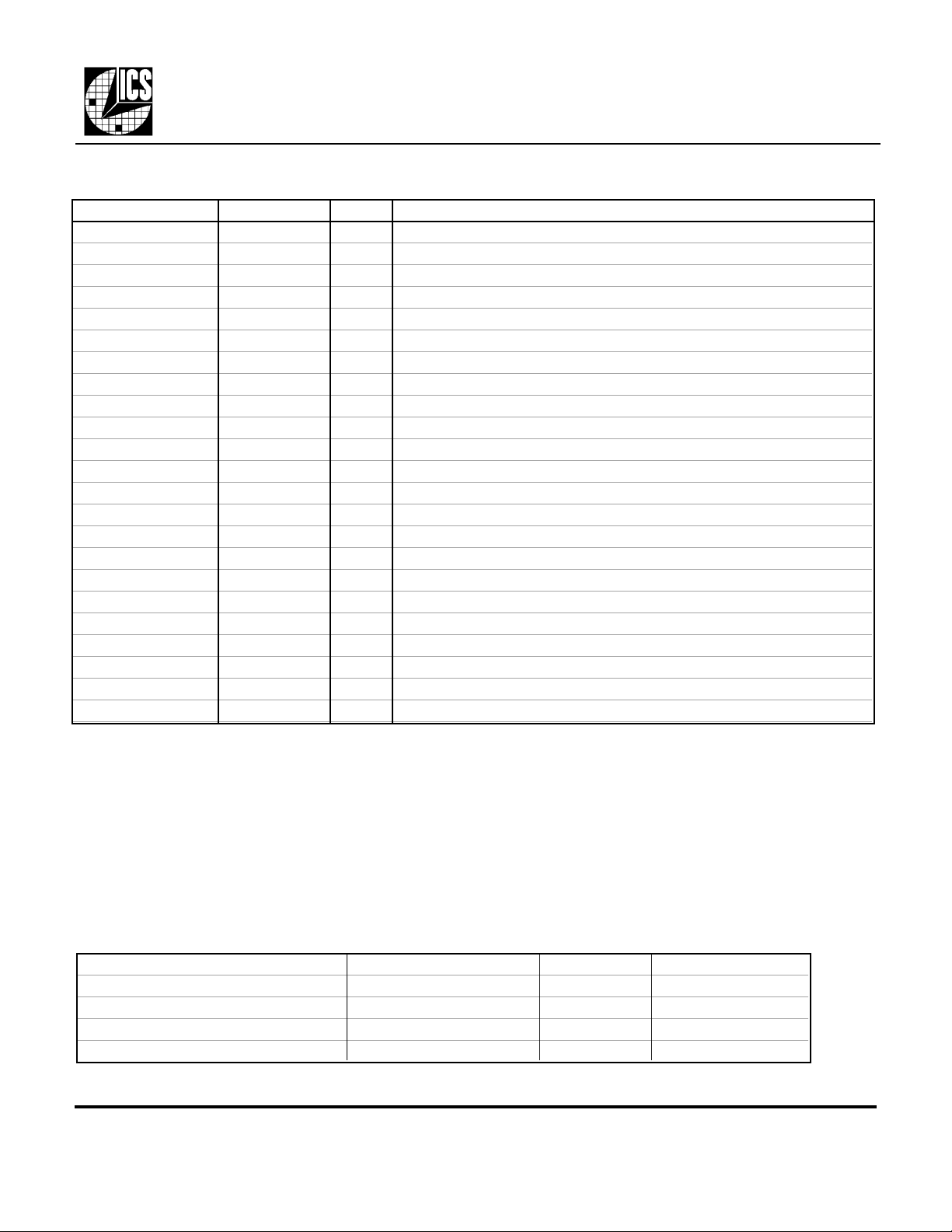

Pin Descriptions for 56 pin SSOP (F package)

Number Name Type Description

1, 2, 9 OUT1, 2, and 4 O Clock outputs 1, 2 and 4.

3, 10, 16, 22, 27 GND P Connect to ground.

4 CLKIN I Clock input for reference.

5 FBIN I Feedback input for "zero delay" in Multiplier Mode.

6, 7,28,29,35,36,50,55 VDD P Power supply for internal circuits and OUT1:4, OUT15:20, and OUT25:32.

8 FBOUT3 O Clock output 3. Connect to pin 5 for Zero Delay Mode.

11, 12, 14, 15 OUT5-OUT8 O Clock outputs 5 through 8; level set by VDD5:8 on pin 13.

13 VDD5:8 P Power supply for outputs 5 through 8. Cannot exceed VDD.

17, 18, 20, 21 OUT9-OUT12 O Clock outputs 9 through 12; level set by VDD9:12 on pin 19.

19 VDD9:12 P Power supply for outputs 9 through 12. Cannot exceed VDD.

23 VDD13:14 P Power supply for outputs 13 and 14. Cannot exceed VDD.

24 OE (see note) I Output Enable. Tri-states all clock outputs when low. Internal pull-up.

25, 26 OUT13-OUT14 O Clock outputs 13 and 14; level set by VDD13:14 on pin 23.

30, 31, 32, 33, 37, 38 OUT15-OUT20 O Clock outputs 15 through 20.

34, 39, 45, 51 GND P Connect to ground.

40, 41, 43, 44 OUT21-OUT24 O Clock outputs 21 through 24; level set by VDD21:24 on pin 42.

42 VDD21:24 O Power supply for outputs 21 through 24. Cannot exceed VDD.

46, 47, 48 OUT25-OUT27 O Clock outputs 25 through 27.

49 OUT28/S0 I/O Clock output 28 and output frequency select 0 per table on page 5.

52 OUT29/S1 I/O Clock output 29 and output frequency select 1 per table on page 5.

53 OUT30/S2 I/O Clock output 30 and output frequency select 2 per table on page 5.

54 OUT31/S3 I/O Clock output 31 and output frequency select 3 per table on page 5.

56 OUT32/S4 I/O Clock output 32 and output frequency select 4 per table on page 5.

Type: I = Input, O = output, P = power supply connection, I/O=input upon power up, becoming an output

clock within 10 ms later.

Important Note for OE functionality: To use the output enable function, once the OE has been taken

low, and the outputs have been tri-stated, the VDD must be removed and reapplied for the clocks to run

again.

Staggered output skews for 56 pin SSOP (F) To aid in the reduction of EMI, and to allow the board

designer the flexibility of running different length traces whose clock edges will still line up at their

destinations, the MK74ZD133F comes with different fixed skews for different outputs. All skews are with

respect to OUT1 (pin 1), and are measured into 33Ω termination resistors with 15 pF capacitive loads.

Output Name Pin Numbers Typical Skew Maximum variation

OUT2, OUT25:32 2, 46:49, 52:54, 56 0 200 ps

OUT4, OUT18:24 9, 33, 37, 38, 40, 41, 43, 44 - 350 ps 200 ps

OUT3, OUT5:8, OUT13:17 8, 11, 12, 14, 15, 25, 26, 30:32 -225 ps 200 ps

OUT9:12 17, 18, 20, 21 -150 ps 200 ps

MDS 74ZD133 C 3 Revision 010899 Printed 11/17/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•www.icst.com

Loading...

Loading...