ICST MK3230-01STR, MK3230-02S, MK3230-02STR, MK3230-01S Datasheet

MK3230

ICRO

C

LOCK

Description

The MK3230 is the smallest size, lowest power system

clock synthesizer available. It is the ideal way to

generate clocks for portable computers, PDAs, and

other devices where low power is required. Using

analog Phase-Locked Loop (PLL) techniques, the

device operates from a single 32.768 kHz crystal to

produce the 32.768kHz, CPU, system, keyboard

controller, and floppy (or super I/O) controller output

clocks.

The device has two power down modes. From the CPU

decoding table (when FS0, FS1, and FS2 all are low),

the CPU and 14.3 MHz system clocks can be turned

off. Also, the keyboard and 24 MHz peripheral clocks

can be shut off from PD24+KBD (pin 10). The part has

a separate VDD32 pin for the 32 kHz clock, allowing

it to run at a different voltage (down to 2.0V) from the

rest of the chip, allowing it to run from a back-up

battery.

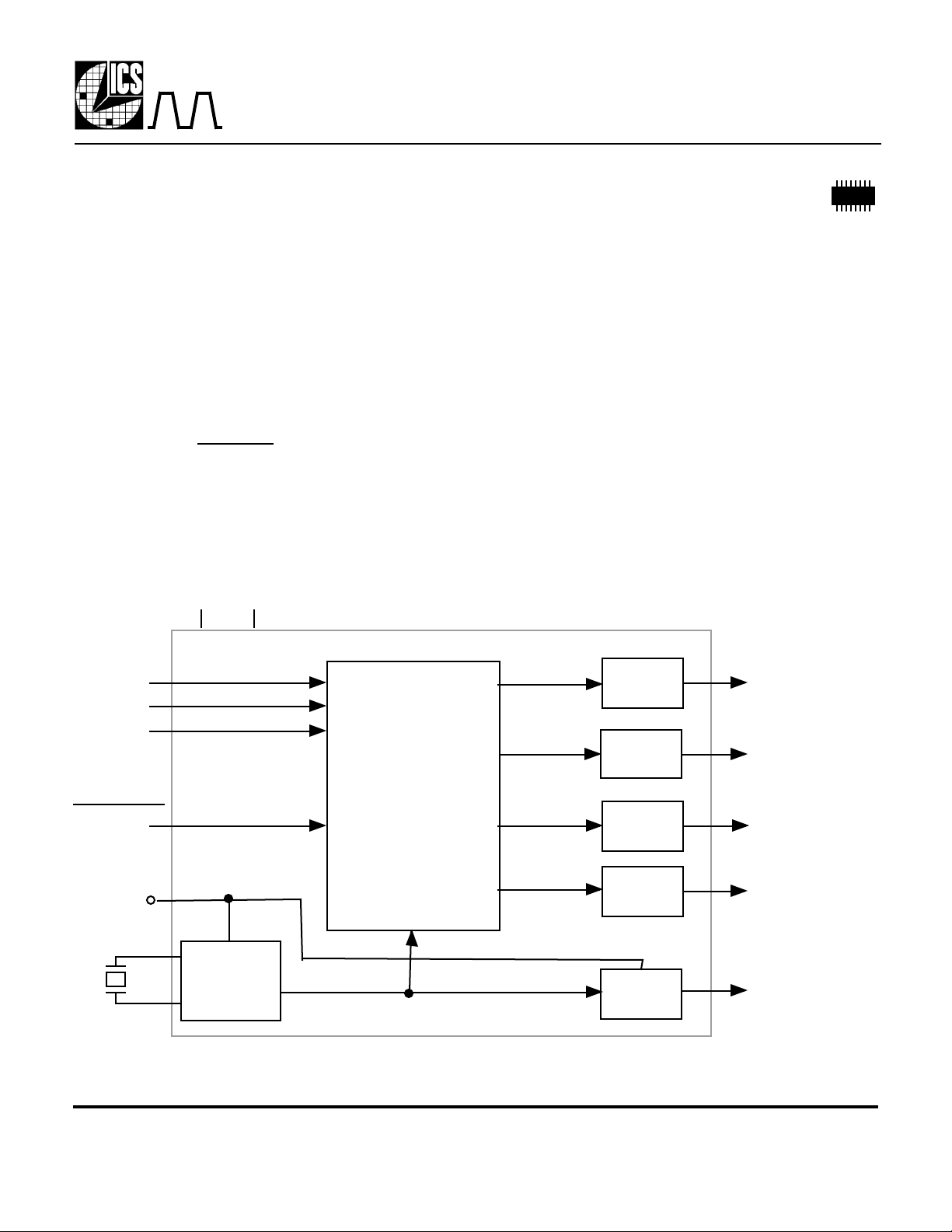

Block Diagram

Portable System Clock Synthesizer

Features

• Packaged in 16 pin narrow (0.150”) SOIC

• Input crystal frequency of 32.768 kHz

• Lowest power solution available

• Lowest profile clock solution where height is critical

• Output clock frequencies up to 80 MHz

• Five output clocks

• 3.3V or 5.0V operation

• Duty cycle of 45/55

• Seven selectable CPU frequencies

• CPU and peripheral clock power downs

• Separate battery supply pin for 32 kHz

• IDD less than 5µA when 32 kHz running

• Available with either 12MHz (-01) or 16MHz (-02)

keyboard clock output

• 14.3MHz output is not suitable for driving PLL for

CRT. Will drive all other functions

• 32kHz crystals require long startup (>500ms)

CPUS0

CPUS1

CPUS2

PD24+KBD

VDD32

X1

X2

VDD

GND

Crystal

Oscillator

Clock Synthesis

and Control

Circuitry

Output

Buffer

Output

Buffer

Output

Buffer

Output

Buffer

Output

Buffer

CPUCLK

12 or 16 MHz

24.00 MHz

14.32 MHz

32.768 kHz

32.768 kHz

crystal

MDS 3230 F 1 Revision 022798 Printed 11/16/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•www.icst.com

MK3230

Portable System Clock Synthesizer

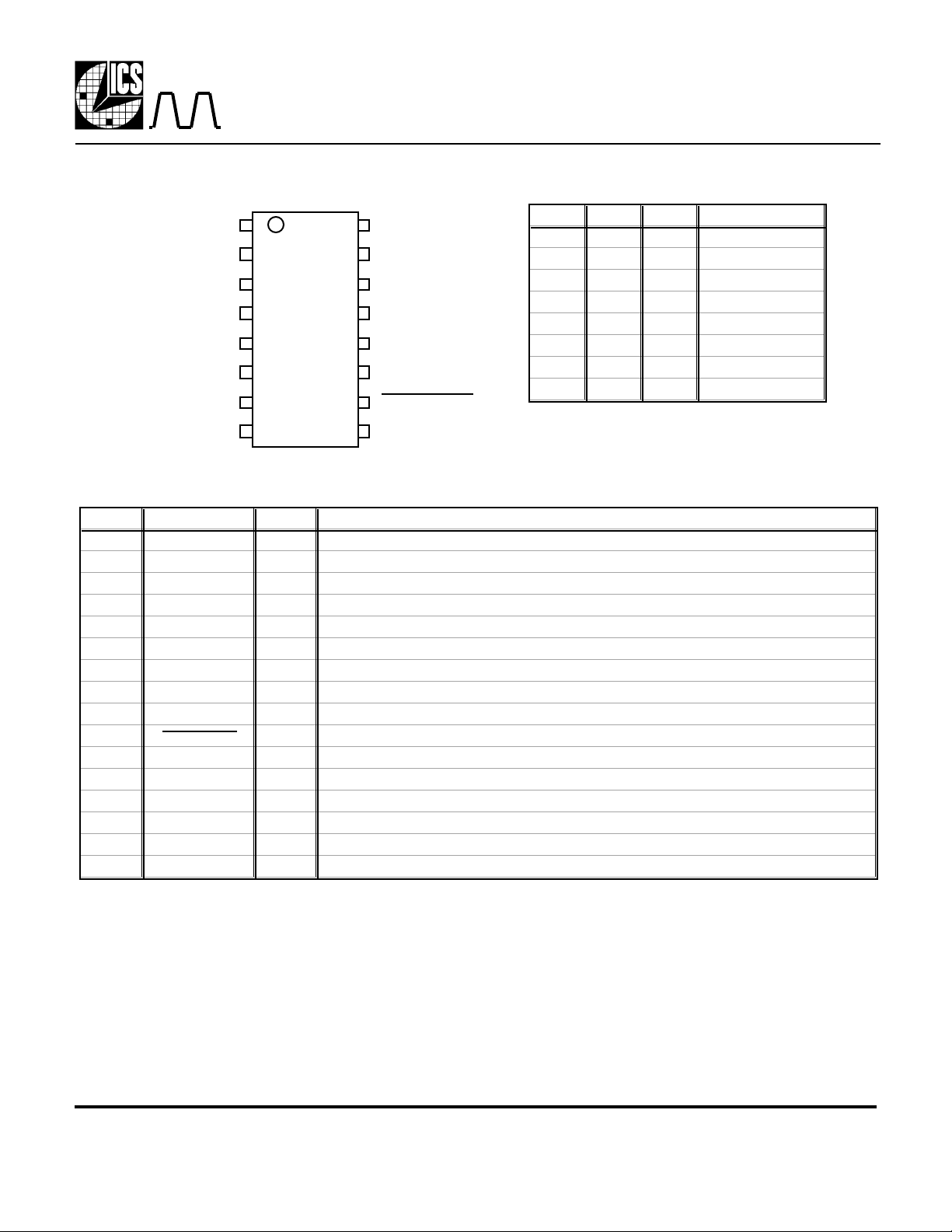

CPU Clock Decoding

CPUS2 CPUS1 CPUS0 CPUCLK (MHz)

0 0 0 Off+14M off

0 0 1 80.00

0 1 0 25.00

0 1 1 66.66

1 0 0 20.00

1 0 1 50.00

1 1 0 33.33

1 1 1 4.00

Pin Assignment

CPUS2

VDD32

VDD

GND

24M

ICRO

X2

X1

C

LOCK

1

2

3

4

5

6

16

15

14

13

12

11

7 10

CPUS1

CPUS0

CPUCLK

VDD

GND

14.3M

PD24+KBD

Frequency transitions (except going to/from

32K

8 9

KBOUT

off) will occur smoothly, and are compatible

with all 486 processors.

Pin Descriptions

Number Name Type Description

1 CPUS2 I Select 2 for CPUCLK frequencies. See Table above.

2 X2 O Crystal connection. Connect to 32.768 kHz crystal.

3 X1 I Crystal connection. Connect to 32.768 kHz crystal.

4 VDD32 P Separate power supply connection for 32.768kHz clock. Will operate to 2.0V.

5 VDD P Connect to +3.3V or +5V. Must be the same voltage as pin 13.

6 GND P Connect to ground.

7 24M O 24 MHz floppy (or super I/O) clock output.

8 32K O 32.768 kHz square wave clock output.

9 KBOUT O Keyboard clock output. Either 12MHz (-01) or 16MHz (-02)

10 PD24+KBD I Power Down 24M+keyboard. Shuts off both clock outputs (pins 7,9) when low.

11 14.3M O 14.318 MHz system clock output. Do not drive a CRT PLL device with this output.

12 GND P Connect to ground.

13 VDD P Connect to +3.3V or +5V. Must be the same voltage as pin 5.

14 CPUCLK O CPUCLK output. See Table above.

15 CPUS0 I Select 0 for CPUCLK frequencies. See Table above.

16 CPUS1 I Select 1 for CPUCLK frequencies. See Table above.

Type: I = Input, O = output, P = power supply connection

Power Down status: Output clocks will stop in a low state when powered down

External Components

The MK3230 requires a minimum number of external components for proper operation. Decoupling

capacitors of 0.1µF should be connected between VDD and GND, and VDD32 and GND, as close to the

MK3230 as possible. A 10kΩ series resistor should be used to filter the VDD32 pin. A series termination

resistor of 33Ω may be used for each clock output. The device does not require (nor do we recommend)

capacitors connected to the crystal pins. The 32.768 kHz crystal must be connected as close to the chip as

possible. See Application Brief MAB02 for a discussion on tuning for use on a real time clock (RTC).

MDS 3230 F 2 Revision 022798 Printed 11/16/00

Integrated Circuit Systems, Inc.•525 Race Street•San Jose•CA•95126•(408)295-9800tel•www.icst.com

Loading...

Loading...