ICST MK2771-12S, MK2771-12STR Datasheet

MK2771-12

ICRO

C

LOCK

Description

The MK2771-12 is a low cost, low jitter, high

performance VCXO and clock synthesizer

designed for set-top boxes. The on-chip Voltage

Controlled Crystal Oscillator accepts a 0 to 3V

input voltage to cause the output clocks to vary by

±100 ppm. Using MicroClock’s patented VCXO

and analog Phase-Locked Loop (PLL) techniques,

the device uses an inexpensive 13.5 MHz crystal

input to produce multiple output clocks including

a selectable processor clock, selectable UART and

audio clocks, a fixed 11.0592 MHz, and two low

skew copies of the 27 MHz. All clocks are

frequency locked to the 27.00 MHz output (and

to each other) with zero ppm error, so any output

can be used as the VCXO output.

This chip directly replaces the MK2771-02 when a

13.5 MHz input crystal is substituted for the

14.31818 MHz used on the -02. Additionally, the

-12 adds 24.576 MHz to the ACLK.

VCXO and Set-Top Clock Source

Features

• Packaged in 20 pin SOIC

• Pin for pin and functional upgrade to MK2771-02

• Uses an inexpensive 13.5 MHz crystal

• On-chip patented VCXO with pull range

of 200 ppm

• VCXO tuning voltage of 0 to 3 V

• Processor frequency of 16.67 MHz, 20 MHz,

32 MHz, 40 MHz, or 50 MHz

• Zero ppm synthesis error in all clocks (all exactly

track 27MHz VCXO) - patented

• 25 mA output drive capability at TTL levels

• Advanced, low power, sub-micron CMOS process

• 5 V operating voltage

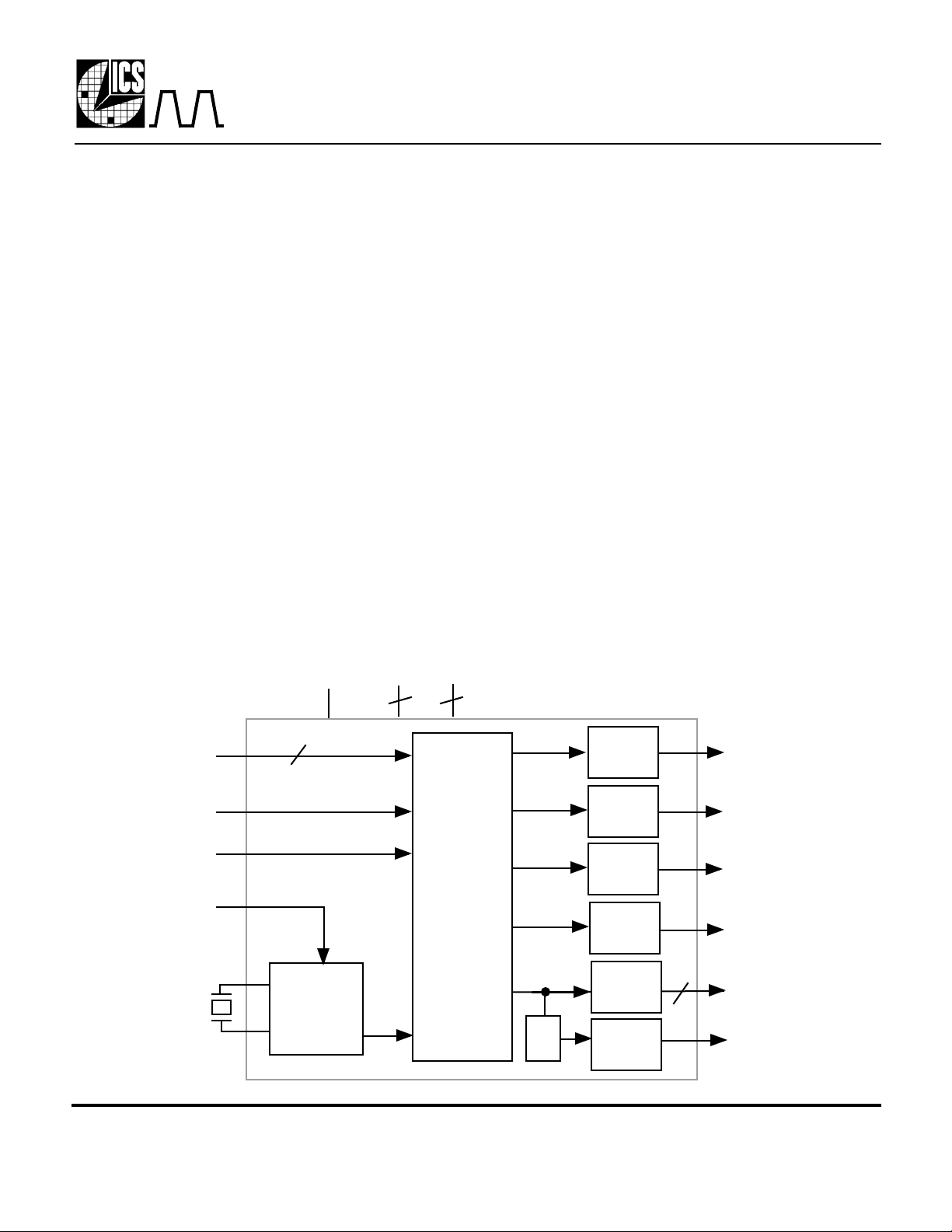

Block Diagram

PCS1:0

UCS

ACS

VIN

13.5 MHz

pullable

crystal

MDS 2771-12 A 1 Revision 061699 Printed 11/16/00

MicroClock Division of ICS • 525 Race Street • San Jose • CA • 95126•(408)295-9800tel•(408)295-9818fax

X1

X2

AVDD

2

Voltage

Controlled

Crystal

Oscillator

VDD GND

32

Clock

Synthesis

Circuitry

÷ 2

Output

Buffer

Output

Buffer

Output

Buffer

Output

Buffer

Output

Buffers

Output

Buffer

Processor Clock

11.0592 MHz

3.6864 MHz

or 18.432 MHz

49.152 MHz

or 24.576 MHz

2

27.000 MHz

13.500 MHz

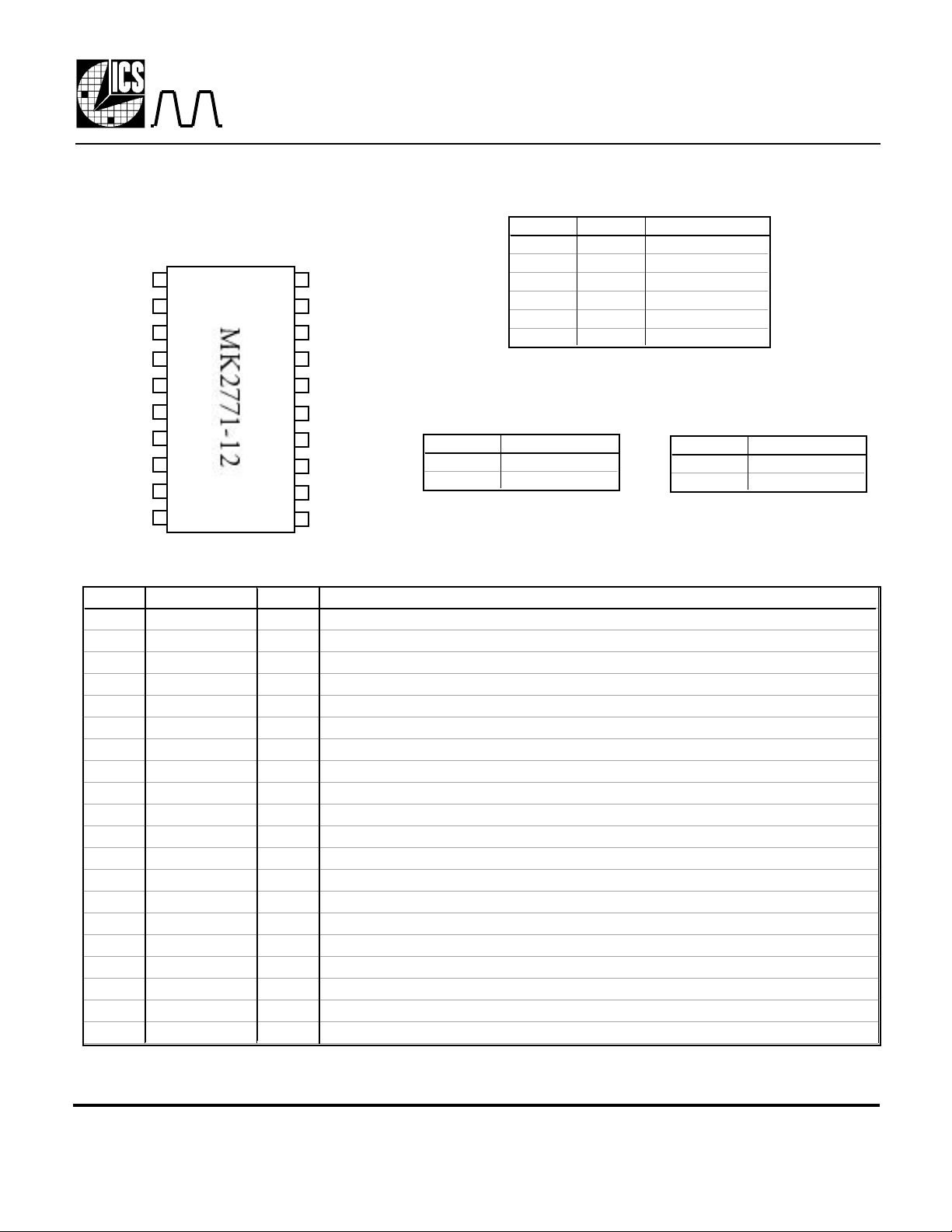

MK2771-12

VCXO and Set-Top Clock Source

Processor Clock Select Table

PCS1 PCS0 PCLK (MHz)

0 0 50.000

0 1 16.667

M 0 test

M 1 32.000

1 0 40.000

1 1 20.000

0 = connect directly to ground, 1 = connect directly

to VDD, M = leave floating or unconnected

ACLK Select Table

UCS UCLK (MHz)

0 18.432

1 3.6864

ACS ACLK (MHz)

0 49.152

1 24.576

Pin Assignment

PCS0

X2

X1

AVDD

VIN

VDD

GND

PCLK

UCLK

ACLK

1

2

3

4

5

6

7

8

9

10

ICRO

20

19

18

17

16

15

14

13

12

11

C

LOCK

ACS

UCS

27M

GND

27M

VDD

GND

11.06M

PCS1

13.5M

UART Clock Table

Pin Descriptions

Number Name Type Description

1 PCS0 I Processor Clock Select 0. Selects PCLK on pin 8. See table above.

2 X2 O Crystal connection. Connect to a pullable 13.5 MHz crystal.

3 X1 I Crystal connection. Connect to a pullable 13.5 MHz crystal.

4 AVDD P Analog VDD. Connect to +5V.

5 VIN I Voltage Input to VCXO. Zero to 3V signal which controls the frequency of the VCXO.

6 VDD P Connect to +5V.

7 GND P Connect to ground.

8 PCLK O Processor clock output determined by status of PCS1,0. See table above.

9 UCLK O UART clock output determined by status of UCS. See table above.

10 ACLK O 49.152 MHz or 24.576 MHz clock output determined by ACS. See table above

11 13.5M O 13.5 MHz clock output. Divide by two of the 27MHz VCXO output.

12 PCS1 TI Processor Clock Select 1. Selects PCLK on pin 8. See table above.

13 11.06M O 11.0592 MHz clock output.

14 GND P Connect to ground.

15 VDD P Connect to +5V.

16 27M O 27.00 MHz VCXO clock output.

17 GND P Connect to ground.

18 27M O 27.00 MHz VCXO clock output.

19 UCS I UART Clock Select. Selects UCLK on pin 9. See table above.

20 ACS I ACLK Select. Selects ACLK on pin 10. See table above.

Key: I = Input, TI = Tri-level input, O = output, P = power supply connection

MDS 2771-12 A 2 Revision 061699 Printed 11/16/00

MicroClock Division of ICS • 525 Race Street • San Jose • CA • 95126•(408)295-9800tel•(408)295-9818fax

Loading...

Loading...