ICST MK2712S, MK2712STR Datasheet

MK2712

NTSC/PAL Clock Source

Description

The MK2712 is the ideal way to generate clocks for

NTSC/PAL video encoders and decoders. Stored in

the device are two sets of popular frequencies for

NTSC and PAL. In an 8 pin SOIC, the chip can save

component count, board space, and cost over surface

mount crystals and oscillators, and increase reliability

by eliminating one or two mechanical devices from the

board. The power down pin turns off the device,

drawing less than 20µA.

ICS/MicroClock offers many other clocks for computers

and computer peripherals. Consult us when you need

to remove crystals and oscillators from your board.

Features

• Packaged in 8 pin SOIC

• Ideal for chips such as Analog Devices AD722

and Brooktree BT819

• Input clock frequency of 27.0000 MHz

• Power down turns off chip

• Output enable tri-states output for system testing

• Frequencies are within 1 ppm with accurate

input clock

• Low jitter

• Output clock frequencies of 14.31818MHz,

17.7345MHz, 28.6364MHz, or 35.46896MHz

• 25mA drive capability at TTL levels

• 3.3V or 5V supply voltage

• Advanced, low power CMOS process

• Insensitive to input clock duty cycle

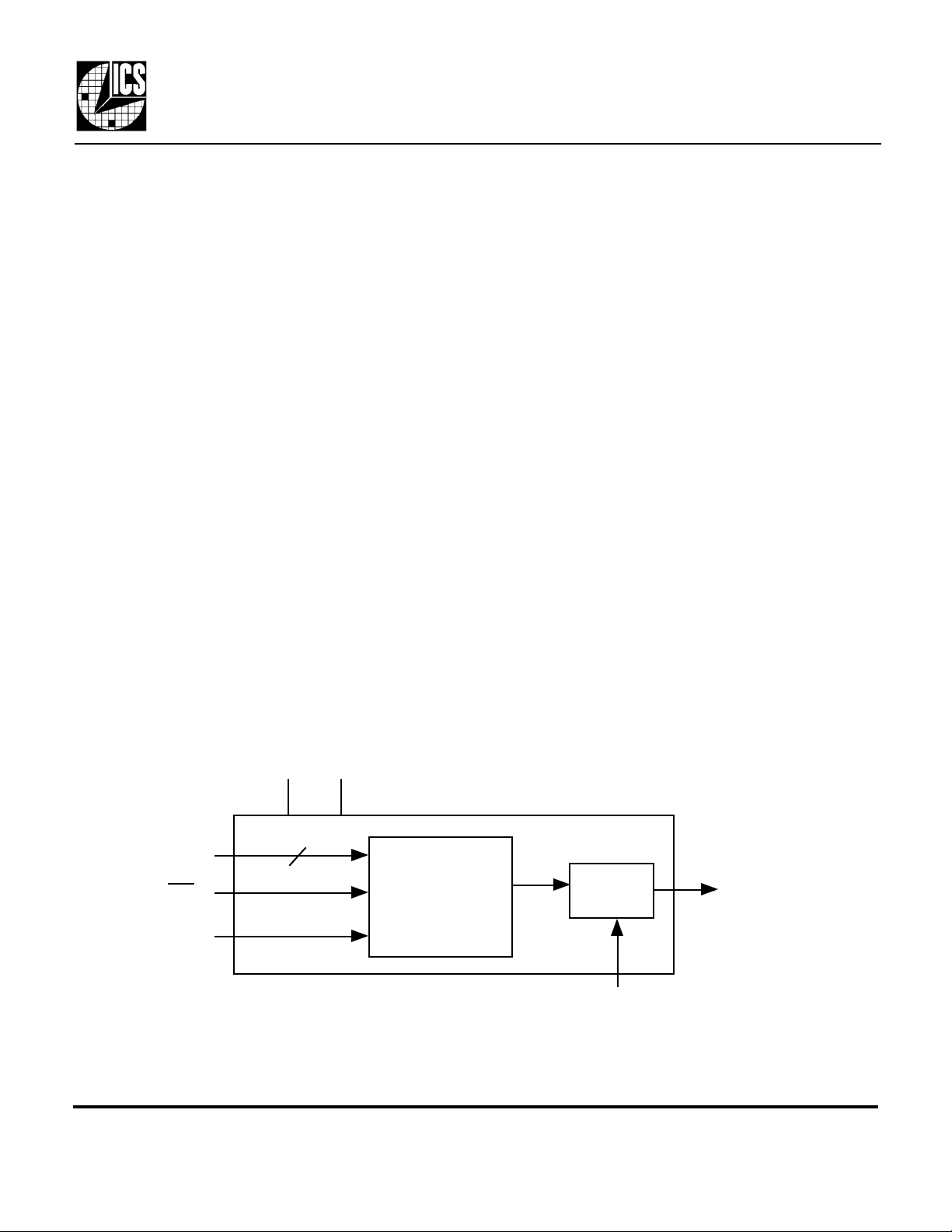

Block Diagram

VDD GND

FS0, 1

PD

27.00 MHz

clock input

MDS 2712 C 1 Revision 061401

Integrated Circuit Systems • 525 Race Street • San Jose • CA • 95126 • (408)295-9800tel • www.icst.com

2

PLL

Clock Synthesis

Circuitry

Output

Buffer

OE

NTSC/PALCL

OCK

MK2712

Description

Input Clock. Connect to a 27.0000 MHz clock.

Connect to +3.3V or +5V.

Connect to ground.

NTSC or PAL output clock. Selected by FS1, FS0 per tables above.

Frequency Select pin #1. Selects NTSC or PAL frequency per table above.

Output Enable. Tri-states clock output when this input is low. Internal pull-up.

Power Down. Active low. Clocks stop low.

Frequency Select pin #0. Selects NTSC or PAL frequency per table above.

NTSC/PAL Clock Source

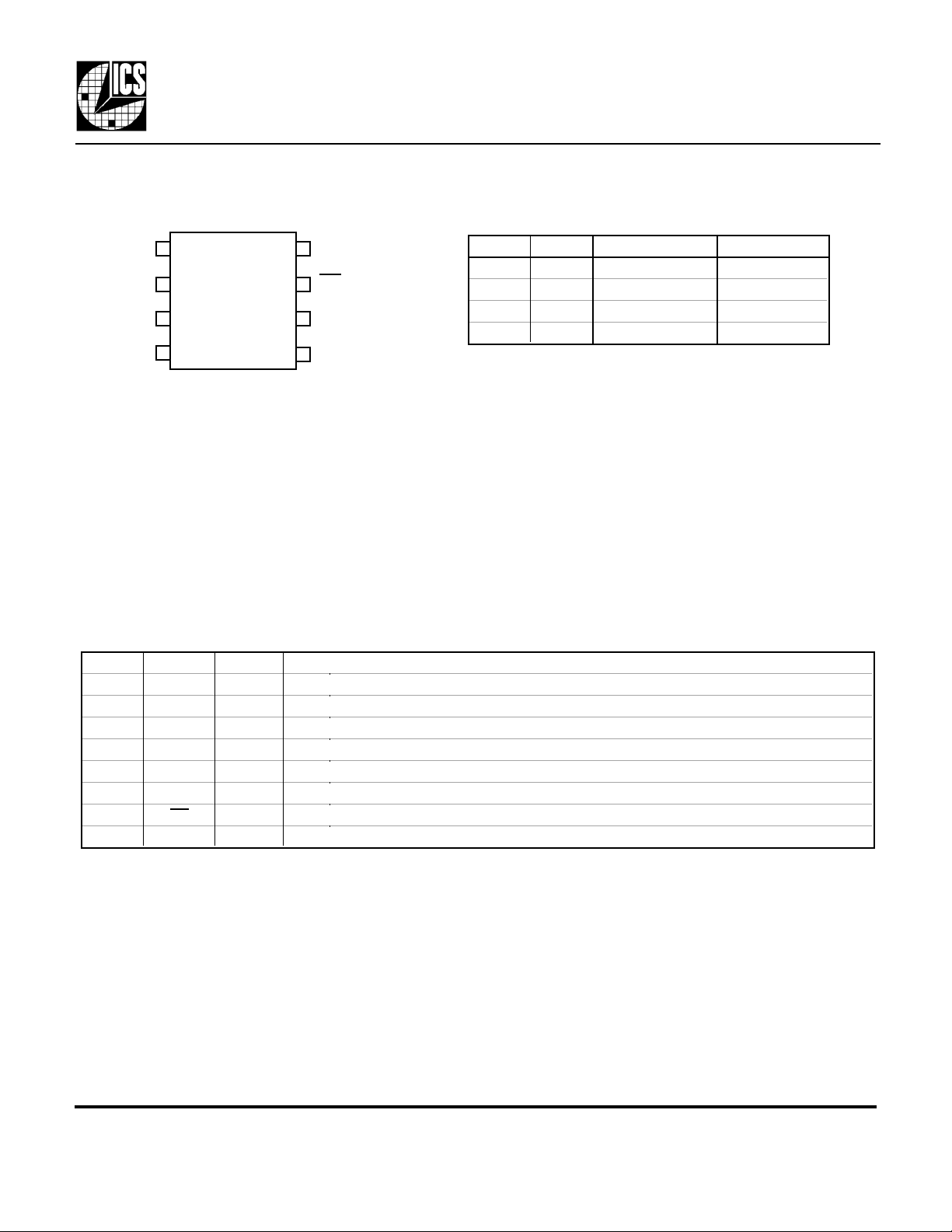

Pin Assignment

ICLK

GND

NPCLK

1 8

2

3

4

8 pin SOIC

Pin Descriptions

Decoding Table

FS0

7

PDVDD

6

OE

5

FS1

FS1 FS0 NPCLK (MHz) Error (ppm)

0 0 14.31818 0.3 ppm

0 1 17.73447 0.3 ppm

1 0 28.63636 0.3 ppm

1 1 35.46894 0.3 ppm

Number Name Type

1 ICLK I

2 VDD P

3 GND P

4 NPCLK O

5 FS1 I

6 OE I

7 PD I

8 FS0 I

Key: I = Input, O = output, P = power supply connection

External Components/Crystal Selection

A minimum number of external components are required for proper oscillation. Connect a 27.000 MHz clock to

ICLK. A decoupling capacitor of 0.1µF should be connected between VDD and GND on pins 2 and 3, and a 33Ω

terminating resistor should be used on the clock output if the trace is longer than 1 inch.

Description

Input Clock. Connect to a 27.0000 MHz clock.

Connect to +3.3V or +5V.

Connect to ground.

NTSC or PAL output clock. Selected by FS1, FS0 per tables above.

Frequency Select pin #1. Selects NTSC or PAL frequency per table above.

Output Enable. Tri-states clock output when this input is low. Internal pull-up.

Power Down. Active low. Clocks stop low.

Frequency Select pin #0. Selects NTSC or PAL frequency per table above.

MDS 2712 C 2 Revision 061401

Integrated Circuit Systems • 525 Race Street • San Jose • CA • 95126 • (408)295-9800tel • www.icst.com

Loading...

Loading...