MK2703

ICRO

C

LOCK

Description

The MK2703 is a low cost, low jitter, high

performance PLL clock synthesizer designed to

replace oscillators and PLL circuits in set-top box

and multimedia systems. Using our patented

analog Phase-Locked Loop (PLL) techniques, the

device uses a 27 MHz crystal or clock input to

produce a buffered reference clock and a selectable

audio clock.

MicroClock manufactures the largest variety of

Set-Top Box and multimedia clock synthesizers

for all applications. Consult MicroClock to

eliminate VCXOs, crystals and oscillators from

your board.

PLL Audio Clock Synthesizer

Features

• Packaged in 8 pin SOIC

• Uses an inexpensive fundamental crystal, or clock

• Supports MPEG sampling rates of 32 kHz,

44.1 kHz, 48 kHz and 96 kHz

• Patented zero ppm synthesis error in all clocks

• All frequencies are frequency locked

• 25 mA output drive capability at TTL levels

• Advanced, low power, sub-micron CMOS process

• 3.3 V or 5 V operating voltage

• For audio clocks that require lower jitter, use the

MK2731-03C

• Industrial temperature version available

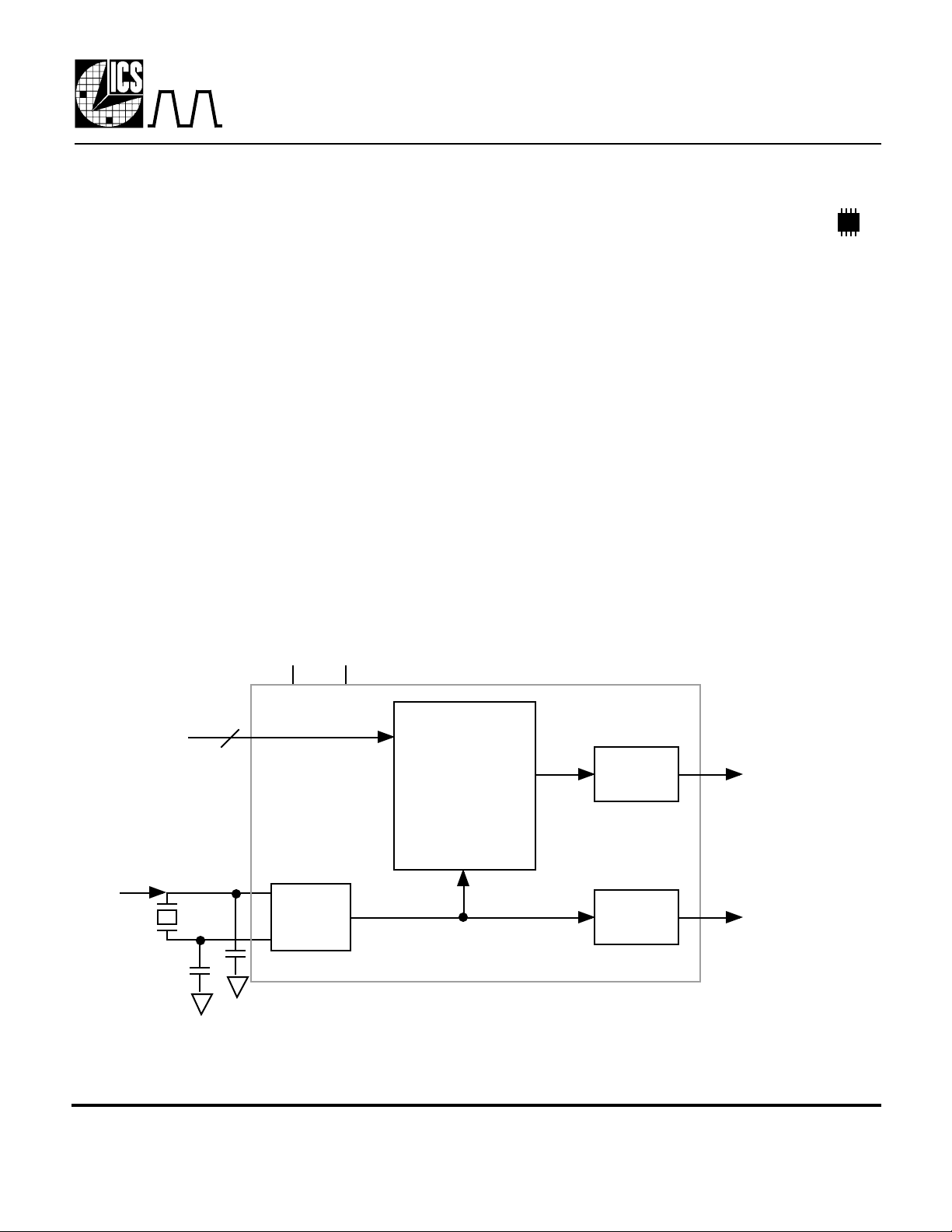

Block Diagram

S1:0

27 MHz crystal or

clock

(Capacitors are required

X1

X2

for crystal tuning)

VDD GND

2

PLL

Clock Synthesis

and Control

Circuitry

Crystal

Oscillator

Output

Buffer

Output

Buffer

Audio Clock

27.000 MHz

MDS 2703 C 1 Revision 062700 Printed 11/16/00

Integrated Circuit Systems, Inc. • 525 Race Street • San Jose •CA•95126• (408) 295-9800tel • www.icst.com

MK2703

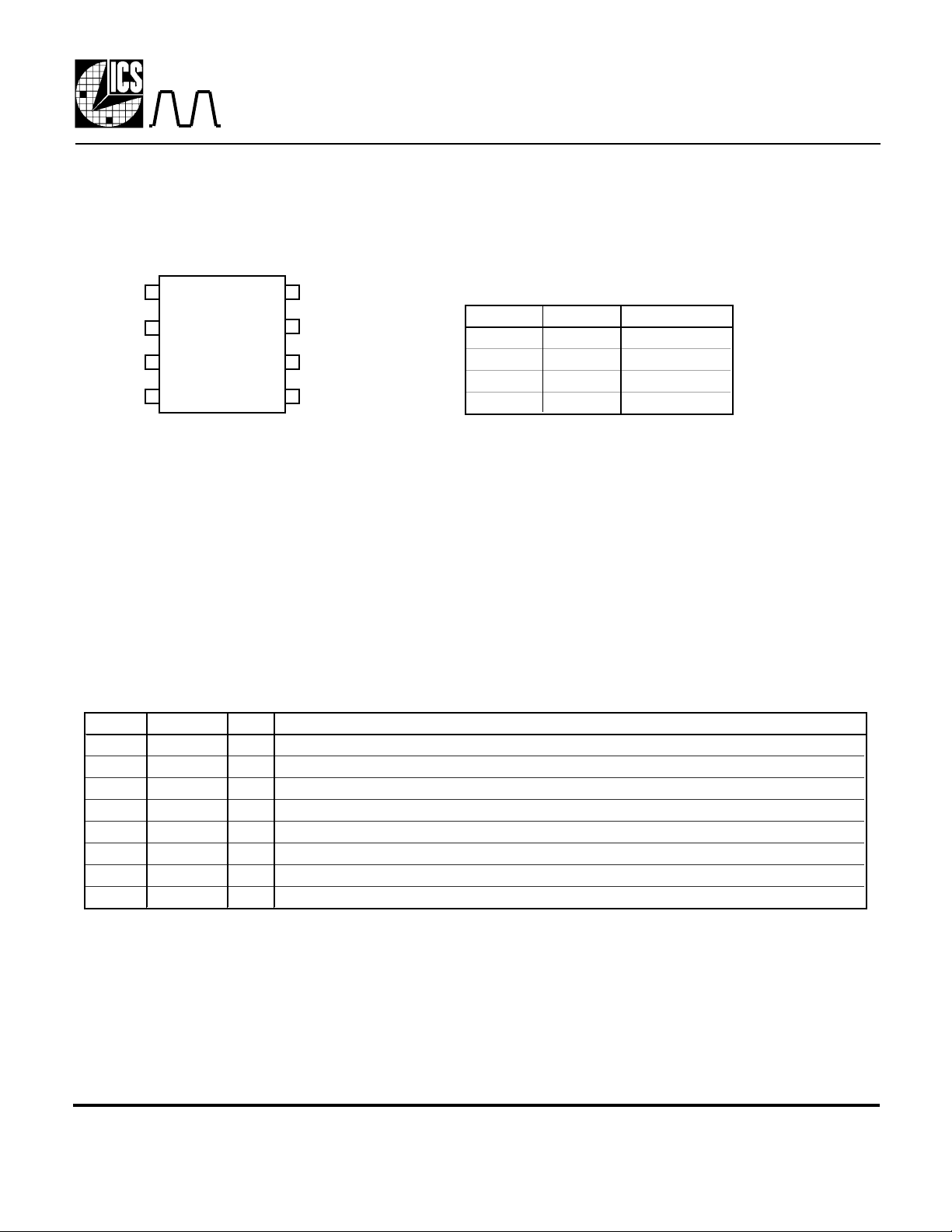

Pin Assignment

MK2703

X1

VDD

GND

27M

1 8

2

3

4

8 pin SOIC

ICRO

7

6

5

C

LOCK

X2

S0

S1

CLK

PLL Audio Clock Synthesizer

Audio Clock Output Select Table (MHz)

S1 S0 CLK

0 0 8.192

0 1 11.2896

1 0 12.288

1 1 24.576

Key: 0 = connect pin directly to ground

1 = connect pin directly to VDD

Pin Descriptions

Number Name Type Description

1 X1 XI Crystal Connection. Connect to a 27.0 MHz fundamental crystal or clock.

2 VDD P Connect to +3.3V or +5V.

3 GND P Connect to ground.

4 27M O 27.00 MHz buffered reference clock output.

5 CLK O Audio Clock Output per table above.

6 S1 I(PU) Audio Clock Frequency Select Input #1. Determines CLK output per table above.

7 S0 I(PU) Audio Clock Frequency Select Input #0. Determines CLK output per table above.

8 X2 XO Crystal Connection to a 27.0 MHz crystal, or leave unconnected for clock input.

Key: XI, XO = Crystal connections; I(PU)= Input with internal pull-up resistor; O = output;

P = power supply connection

MDS 2703 C 2 Revision 062700 Printed 11/16/00

Integrated Circuit Systems, Inc. • 525 Race Street • San Jose •CA•95126• (408) 295-9800tel • www.icst.com

Loading...

Loading...