ICST ICS9248F-78 Datasheet

Integrated

Circuit

Systems, Inc.

General Description Features

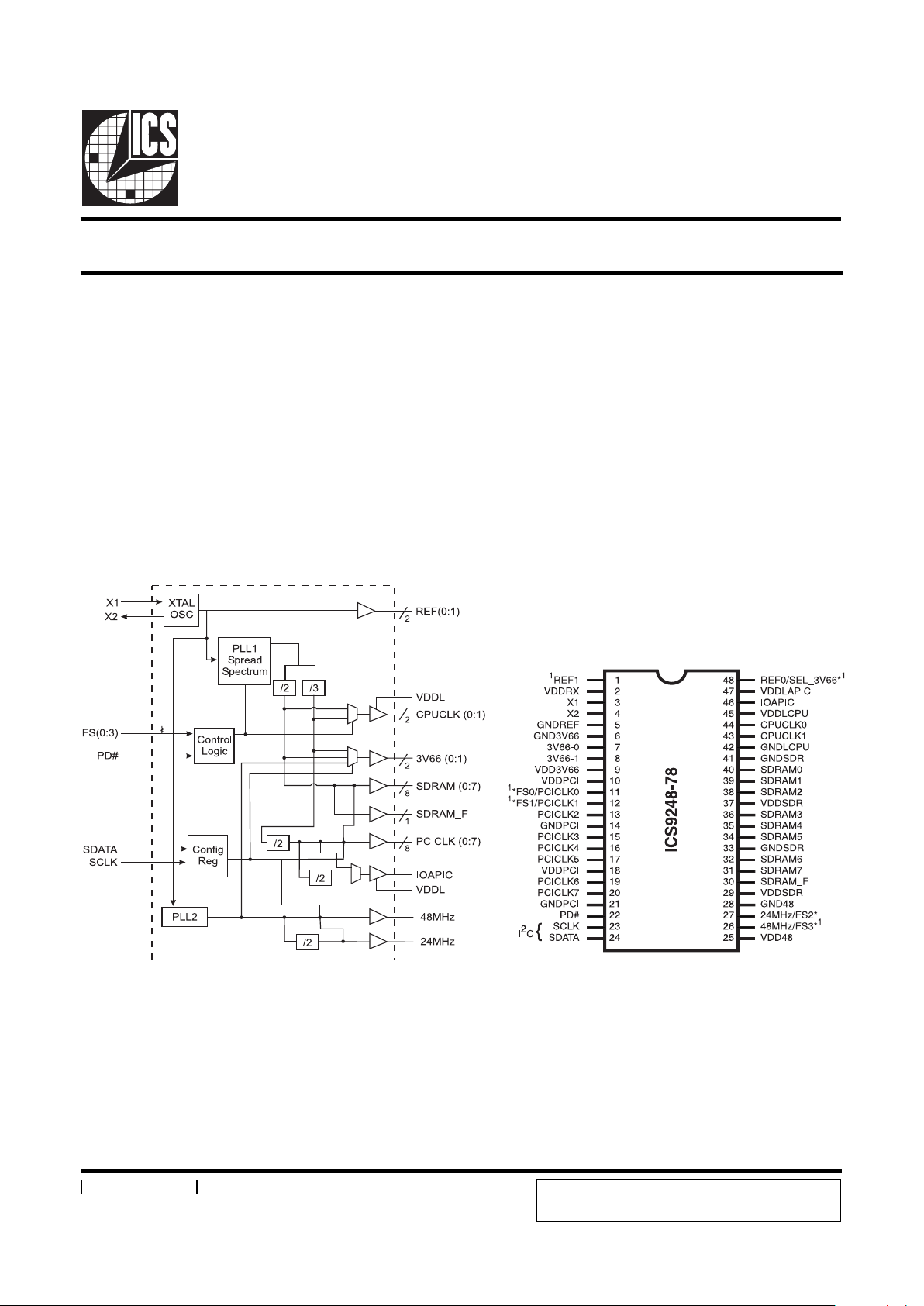

ICS9248-78

Block Diagram

Pentium II is a trademark of Intel Corporation

I2C is a trademark of Philips Corporation

Frequency Timing Generator for Pentium II Systems

9248-78 Rev A 7/21/99

Pin Configuration

Generates the following system clocks:

- 2 - CPUs @ 2.5V, up to 150MHz.

- 1 - IOAPIC @ 2.5V, PCI/2MHz.

- 9 SDRAMs (3.3V), up to150MHz.

-2 - 3V66 @ 3.3V, 2x PCIMHz.

- 8 - PCIs @ 3.3V.

- 1 - 48MHz, @ 3.3V fixed.

- 2 - REF @ 3.3V, 14.318Hz.

- 1 - 24MHz, @ 3.3V fixed.

Supports spread spectrum modulation ,

down spread 0 to -0.5%, ±0.25% center spread.

I2C support for power management.

Efficient power management scheme through PD#.

Uses external 14.138 MHz crystal.

48-Pin 300 mil SSOP

The ICS9248-78 is a single chip clock for Intel Pentium II.

It provides all necessary clock signals for such a system.

Spread spectrum may be enabled through I2C programming.

Spread spectrum typically reduces EMI by 8dB to 10 dB.

This simplifies EMI qualification without resorting to board

design iterations or costly shielding. The ICS9248-78

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

Power Groups

GNDREF, VDDREF = REF, Crystal

GND3V66, VDD3V66 = 3V66

GNDPCI, VDDPCI = PCICLKs

GNDCOR, VDDCOR = PLLCORE

GND48, VDD48 = 48

GNDSDR, VDDSDR = SDRAM

GNDLCPU, VDDLCPU = CPUCLK

GNDLPCI, VDDLAPIC = IOAPIC

1. These pins will have 2X drive strength.

* 120K ohm pull-up to VDD on indicated inputs.

Preliminary Product Preview

PRODUCT PREVIEW documents contain information on new

products in the sampling or preproduction phase of development.

Characteristic data and other specifications are subject to change

without notice.

2

ICS9248-78

Preliminary Product Preview

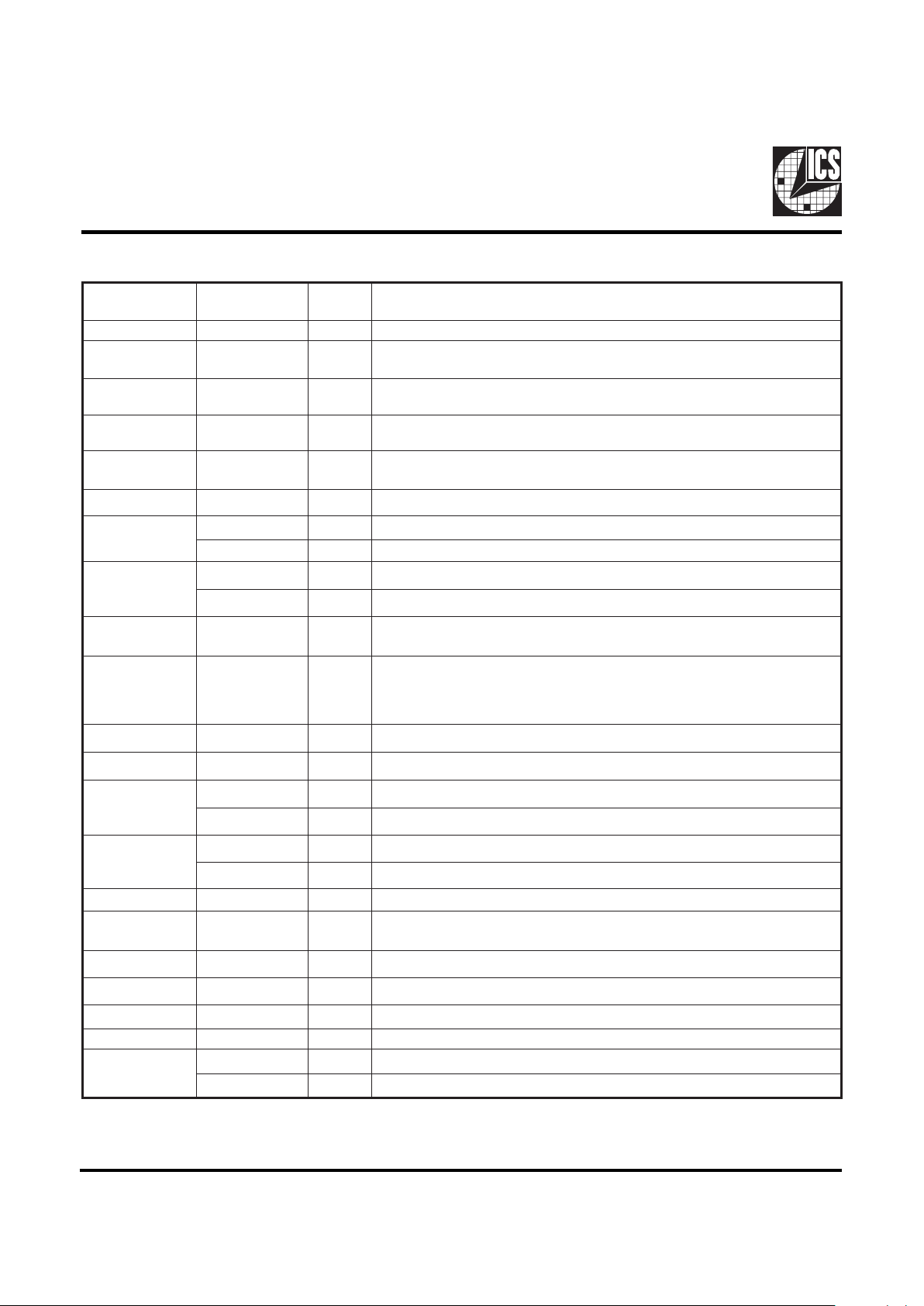

Pin Descriptions

NIP

REBMUN

EMANNIPEPYTNOITPIRCSED

11FERTUO.tuptuokcolcecnereferzHM813.41,V3.3

,81,01,9,2

73,92,52

DDVRWPylppusrewopV3.3

31XNI

kcabdeefdna)Fp33(pacdaollanretnisah,tupnilatsyrC

2Xmorfrotsiser

42XTUO

daollanretnisaH.zHM813.41yllanimon,tuptuolatsyrC

)Fp33(pac

,82,12,41,6,5

14,33

DNGRWPylppusV3.3rofsnipdnuorG

8,7)0:1(66V3TUOzHMICPX2tagninnurBUHrofstuptuokcolcV3.3

11

0KLCICP

1

TUOSKLCUPCsuonorhcnyShtiw,stuptuokcolcICPV3.3

0SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

21

1KLCICP

1

TUOSKLCUPCsuonorhcnyShtiw,stuptuokcolcICPV3.3

1SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

,61,51,31

02,91,71

)7:2(KLCICPTUOSKLCUPCsuonorhcnyShtiw,stuptuokcolcICPV3.3

22#DPNI

otniecivedehtnwodrewopotdesuniptupniwolevitcasuonorhcnysA

dnaOCVehtdnadelbasideraskcolclanretniehT.etatsrewopwola

ebtonlliwnwodrewopehtfoycnetalehT.deppotseralatsyrceht

.sm3nahtretaerg

32KLCSNIIfotupnikcolC

2

tupniC

42ATADSNIIroftupniataD

2

.tupnilairesC

62

zHM84TUOBSUroftuptuokcolczHM84dexiFV3.3

3SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

72

2SFNI.norewoptadehctaltupnI.tibtcelesycneuqerftupnicigoL

zHM42TUOtuptuozHM42dexifV3.3

03F_MARDSTUOIybdetceffatonMARDSgninnureerfV3.3

2

C

,63,83,93,04

13,23,43,53

)0:7(MARDSTUOstuptuoV3.3

24LDNGRWPCIPA&UPCrofylppusrewopV5.2rofdnuorG

44,34)0:1(KLCUPCTUO.tuptuokcolcsubtsoHV5.2

74,54LDDVRWPCIPAOI,UPCrofylppyusrewopV5.2

64CIPAOITUOzHM2/ICPtagninnurstuptuokcolcV5.2

84

66V3_LESNI.ycneuqerftuptuo66V3ehtstcelesnipsihT

0FER

1

TUO.tuptuokcolcecnereferzHM813.41,V3.3

Note:

1. These pins will have 2X drive strength.

3

ICS9248-78

Preliminary Product Preview

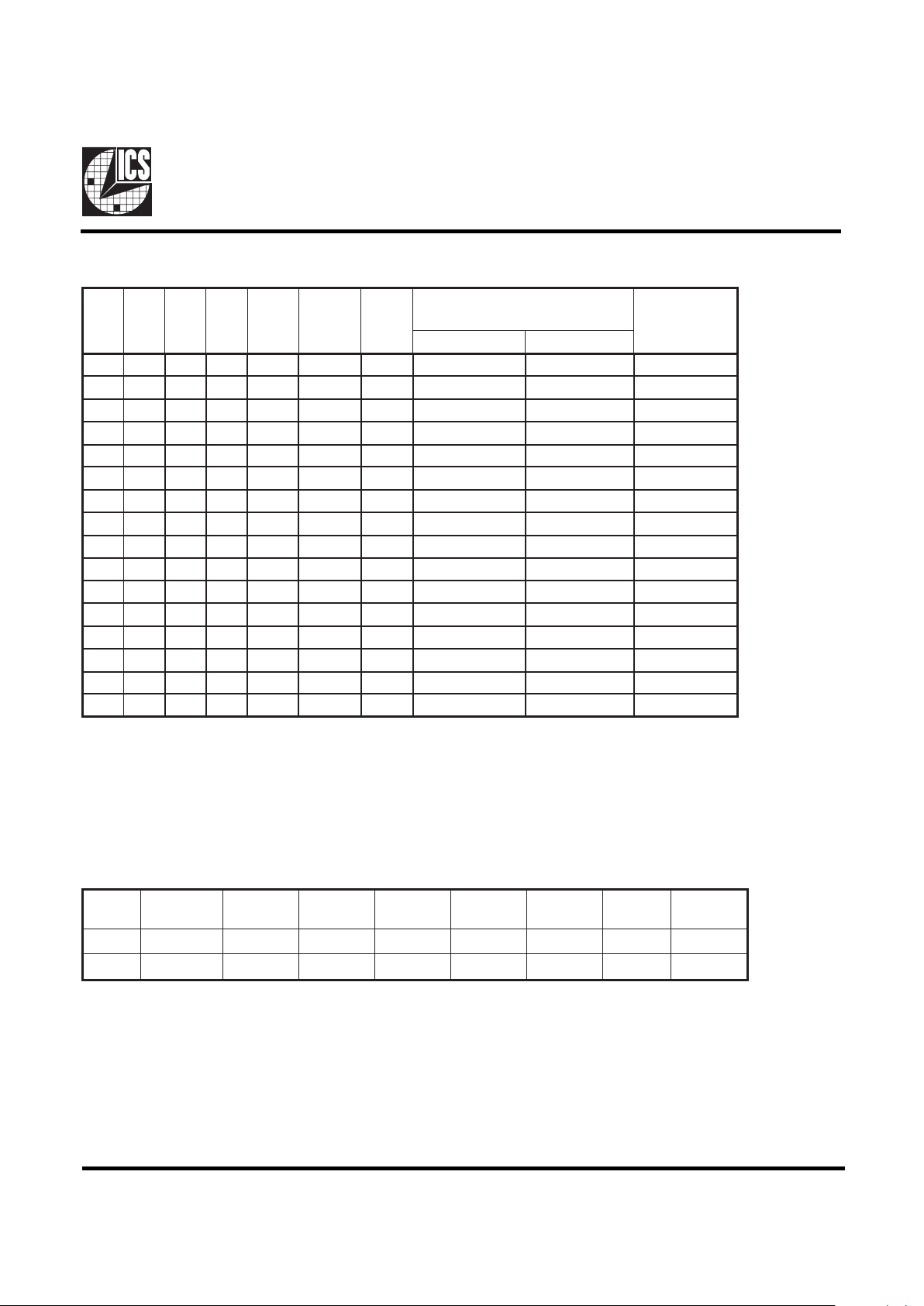

Frequency Selection

Clock Enable Configuration

#DPKLCUPCMARDSCIPAOIzHM66KLCICP

,FER

zHM84

csOsOCV

0WOLWOLWOLWOLWOLWOLFFOFFO

1NONONONONONONONO

Note:

* These output frequencies are not synchronous to CPUCLK and do not have spread spectrum modulation.

3SF2SF1SF0SF

UPC

zHM

MARDS

zHM

ICP

zHM

zHM66V3

zHMCIPAOI

0=66V3_LES1=66V3_LES

0000 32.00132.00114.3328.6628.6607.61

0001 09.00109.00136.3362.7662.7618.61

0010 00.50100.50100.5300.0700.0705.71

0011 98.6633.00144.3398.6698.6627.61

0100 00.02100.02100.04*00.4600.0800.02

0101 00.42100.42133.14*00.4666.2876.02

0110 03.33103.33134.44*00.4668.8812.22

0111 03.33103.33123.3356.6656.6666.61

1000 00.04100.04100.5300.0700.0705.71

100 1 00.05100.05105.73*00.4600.5757.81

1010 99.41199.41133.83*00.4666.6761.91

1011 00.0700.50100.5300.0700.0705.71

1100 00.5705.21105.73*00.4600.5757.81

1101 13.3869.42156.14*00.4613.3838.02

1110 00.0900.0900.0300.0600.0600.51

1111 00.5900.5976.1333.3633.3638.51

4

ICS9248-78

Preliminary Product Preview

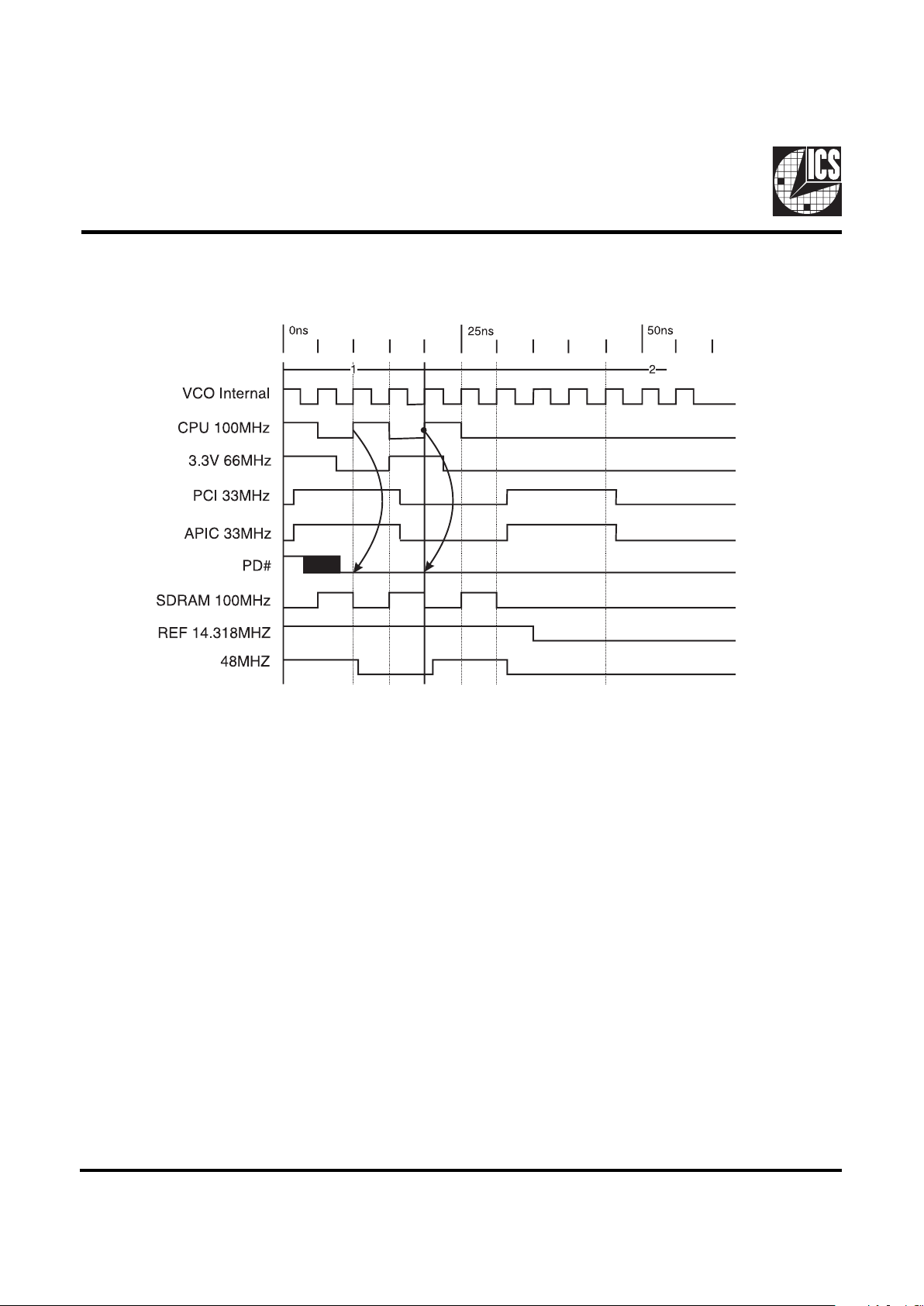

Power Down Waveform

Note

1. After PD# is sampled active (Low) for 2 consective rising edges of CPUCLKs, all

the output clocks are driven Low on their next High to Low tranistiion.

2. Power-up latency <3ms.

3. Waveform shown for 100MHz

Loading...

Loading...