Integrated

Circuit

Systems, Inc.

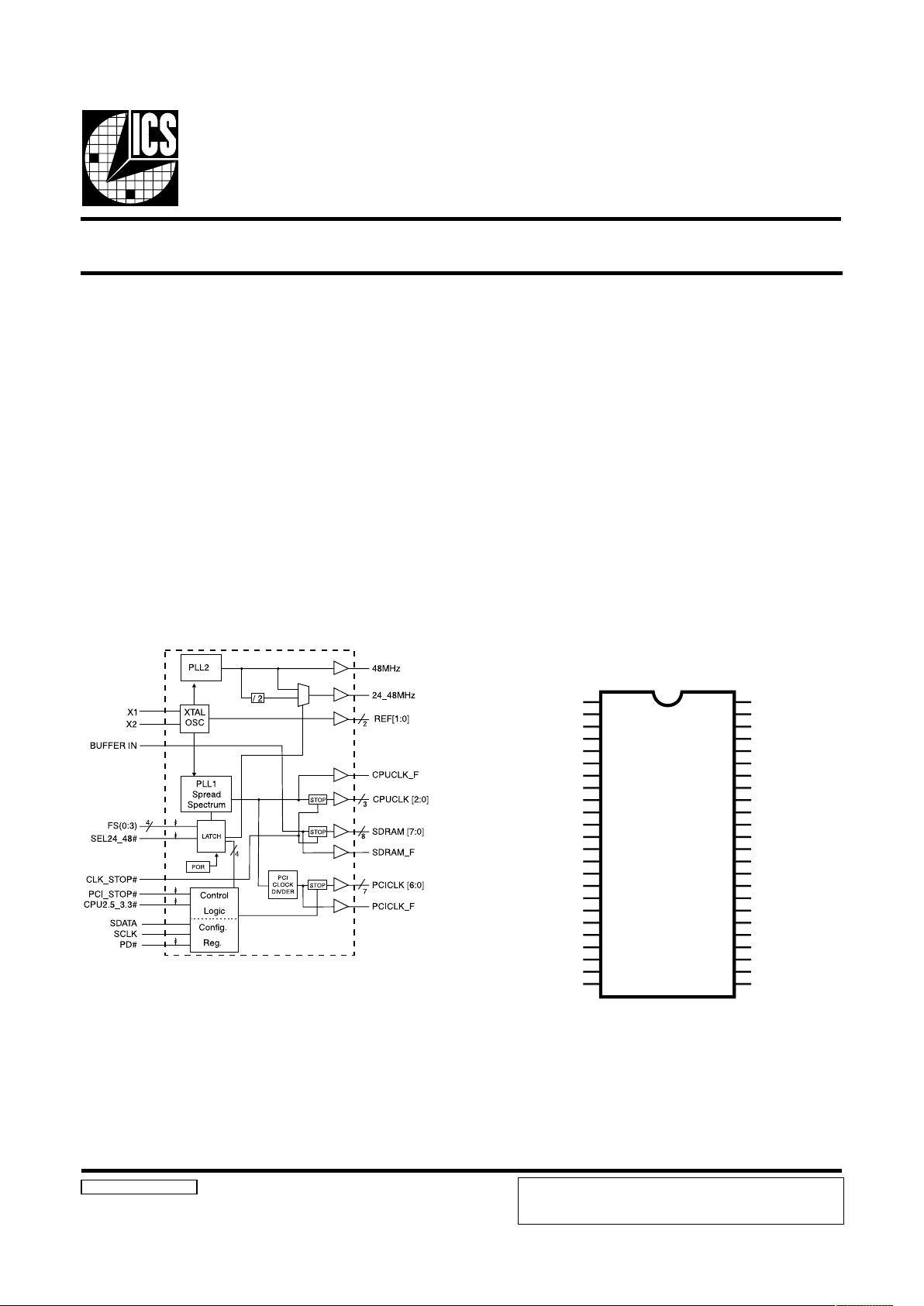

General Description Features

ICS9248-101

Block Diagram

Pentium is a trademark of Intel Corporation

I2C is a trademark of Philips Corporation

Frequency Generator & Integrated Buffers for PENTIUM/Pro

TM

& K6

9248-101 Rev C 2/29/00

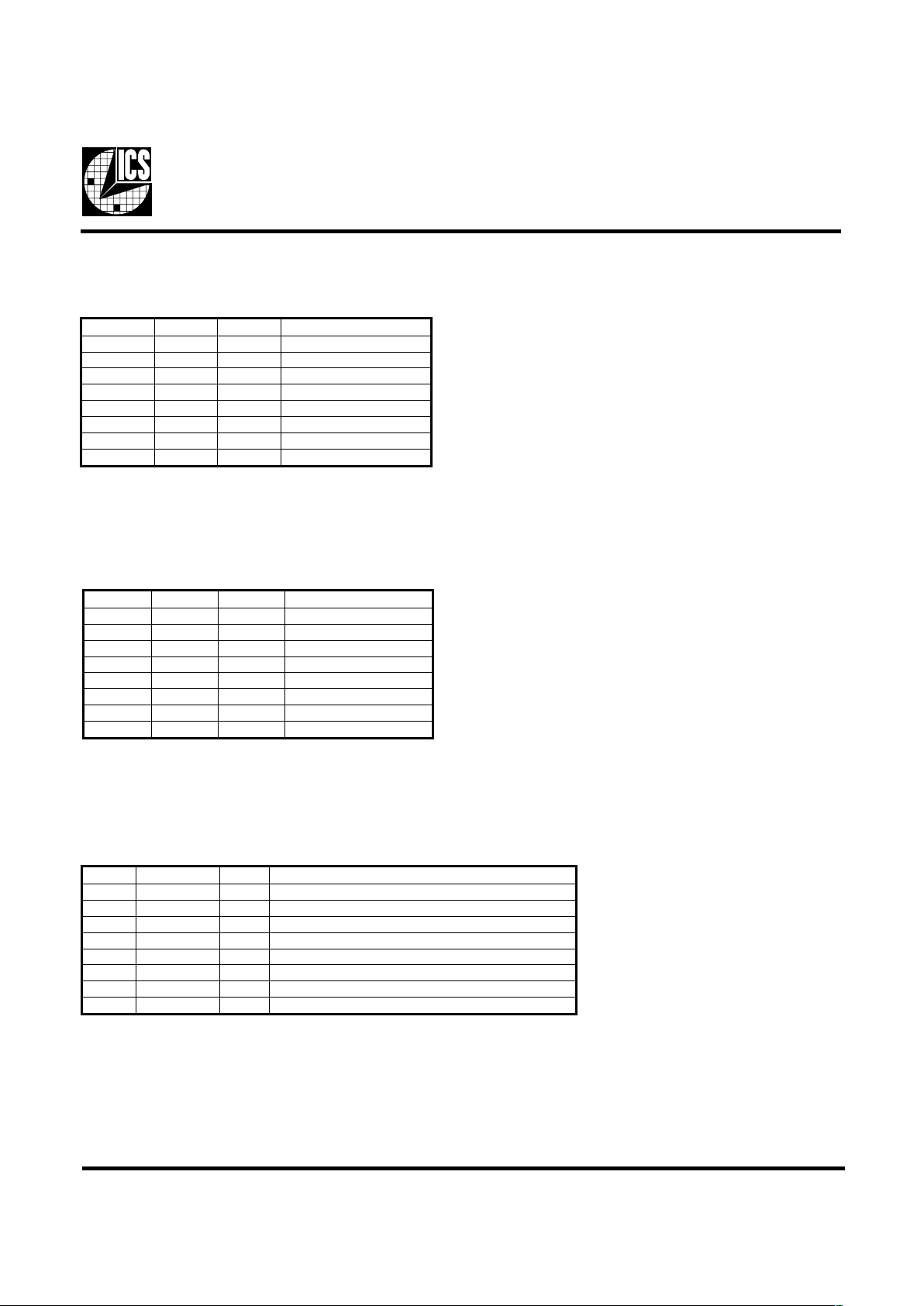

Pin Configuration

Up to 137MHz frequency support

Spread Spectrum for EMI control

Serial I

2

C interface for Power Management,

Frequency Select, Spread Spectrum.

Provides the following system clocks

- 4-CPUs @ 2.5/3.3V, up to 137MHz.

(including CPUCLK_F)

- 9-SDRAMs @3.3V, up to 137MHz

(including SDRAM_F)

- 8-PCI @3.3V, CPU/2 or CPU/3

(including 1 free running PCICLK_F)

- 1-24/48MHz @3.3V

- 1-48MHz @3.3V fixed

- 2-REF @3.3V, 14.318MHz.

Efficient Power management scheme through PCI

and STOP CLOCKS

Spread Spectrum ± .25%, & 0 to -0.5% down spread

48-Pin SSOP and TSSOP

Power Groups

VDDLCPU, GNDLCPU = CPUCLK [2:0], CPUCLK_F

VDDSDR, GNDSDR = SDRAMCLKS [7:0], SDRAM_F

VDDPCI, GNDPCI = PCICLKS [6:0], PCICLK_F

VDD48, GND48 = 48MHz, 24MHz

VDDREF, GNDREF = REF, X1, X2

VDDCOR = PLL CORE

* Internal Pull-up Resistor of 120K to VDD

The ICS9248-101 is the single chip clock solution for

Notebook designs using the 440BX or the VIA Apollo Pro 133

style chipset. It provides all necessary clock signals for such a

system.

Spread spectrum may be enabled through I2C programming.

Spread spectrum typically reduces system EMI by 8dB to

10dB. This simplifies EMI qualification without resorting to

board design iterations or costly shielding. The ICS9248-101

employs a proprietary closed loop design, which tightly

controls the percentage of spreading over process and

temperature variations.

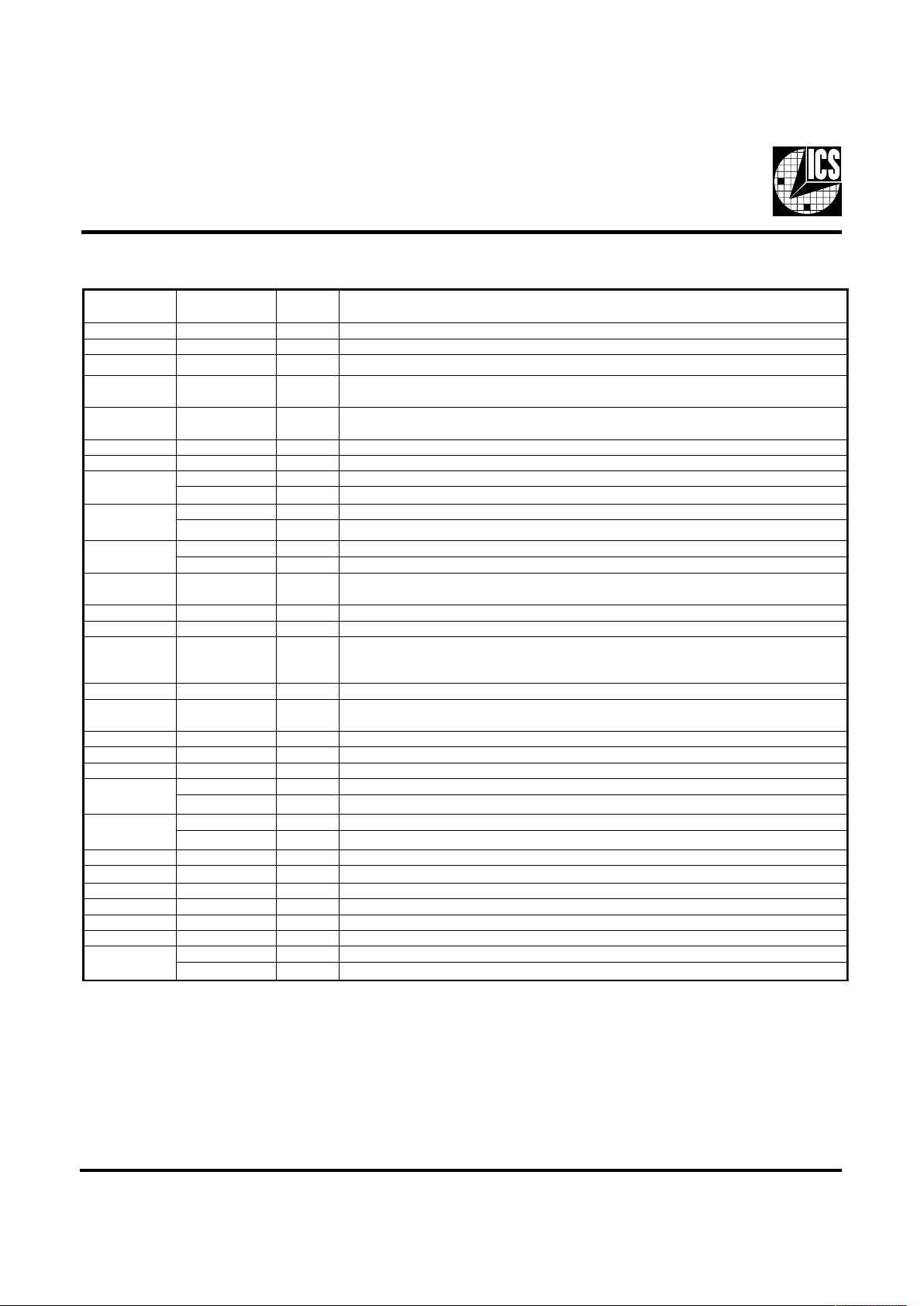

VDDREF

REF0

GNDREF

X1

X2

VDDPCI

*CPU2.5_3.3#/PCICLK_F

*FS3/PCICLK0

GNDPCI

*SEL24_48#/PCICLK1

PCICLK2

PCICLK3

PCICLK4

VDDPCI

BUFFER IN

GNDPCI

PCICLK5

PCICLK6

VDDCOR

PCI_STOP#

*PD#

GND48

SDATA

SCLK

REF1/FS2*

VDDLCPU

CPUCLK_F

CPUCLK0

GNDLCPU

CPUCLK1

CPUCLK2

CLK_STOP#

GNDSDR

SDRAM_F

SDRAM0

SDRAM1

VDDSDR

SDRAM2

SDRAM3

GNDSDR

SDRAM4

SDRAM5

VDDSDR

SDRAM6

SDRAM7

VDD48

48MHz/FS0*

24_48MHz/FS1*

ICS9248-101

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

{

I

C

2

ICS reserves the right to make changes in the device data identified in

this publication without further notice. ICS advises its customers to

obtain the latest version of all device data to verify that any

information being relied upon by the customer is current and accurate.

2

ICS9248-101

Pin Descriptions

Notes:

1: Internal Pull-up Resistor of 120K to 3.3V on indicated inputs

2: Bidirectional input/output pins, input logic levels are latched at internal power-on-reset. Use 10Kohm resistor

to program logic Hi to VDD or GND for logic low.

NIP

REBMUN

EMANNIPEPYTNOITPIRCSED

1FERDDVRWPV3.3lanimon,ylppusrewopLATX,feR

20FERTUO sdaolSUBASIrofreffubREGNORTSehtsituptuoFERsihT.kcolcecnereferzhM813.41

02#POTS_ICPNI )0=EDOM,edomelibomnI(woltupninehw,level0cigoltaskcolc]0:6[KLCICPstlaH

,61,9,3

44,04,33

DNGRWPdnuorG

41XNI

kcabdeefdna)Fp63(pacdaollanretnisah,tupnilatsyrC

2Xmorfrotsiser

52XTUO.zHM813.41yllanimon,tuptuolatsyrC

41,6ICPDDVRWPV3.3lanimon,]0:6[KLCICPdnaF_KLCICProfylppuS

7

#3.3_5.2UPC

2,1

NI .tupnIdehctaL.UPCV3.3=WOL,UPCV5.2=hgiH.V3.3ro5.2siUPCLDDVrehtehwsetacidnI

F_KLCICPTUO .tnemeganamrewoprof#POTS_ICPybdetceffatonkcolcICPgninnureerF

8

3SF

2,1

NI.tupnIdehctaL.niptcelesycneuqerF

0KLCICPTUO )ylraeUPC(wekssn4-1htiwskcolcUPCotsuonorhcnyS.tuptuokcolcICP

01

#84_42LES

2,1

NIzHM84=woLnehwzHM84ro42rehtiestceleS

1KLCICPTUO )ylraeUPC(wekssn4-1htiwskcolcUPCotsuonorhcnyS.tuptuokcolcICP

,31,71,81

,11,21

]2:6[KLCICPTUO )ylraeUPC(wekssn4-1htiwskcolcUPCotsuonorhcnyS.stuptuokcolcICP

51NIREFFUBNI.stuptuoMARDSrofsreffuBtuonaFottupnI

91ROCDDVRWPV3.3.erocLLPehtrofniprewoP

12#DP

1

NI

ehT.etatsrewopwolaotniecivedehtnwodrewopotdesuniptupniwolevitcasuonorhcnysA

rewopehtfoycnetalehT.deppotseralatsyrcehtdnaOCVehtdnadelbasideraskcolclanretni

.sm4nahtretaergebtonlliwnwod

2284DNGRWP.erocLLPdexif&sreffubtuptuozHM84&42ehtrofnipdnuorG

,23,13,92,82

83,73,53,43

]0:7[MARDSTUO .)tespihcybdellortnoc(nipNIREFFUBmorfstuptuoreffuBtuonaF,stuptuokcolcMARDS

63,03RDSDDVRWP.V3.3lanimon,eroCLLPUPCdna]0:7[MARDSrofylppuS

32ATADSNIIroftupniataD

2

tupnitnarelotV5,tupnilairesC

42KLCSNIIfotupnikcolC

2

tupnitnarelotV5,tupniC

52

zHM84_42TUO01nipybelbatceleskcolctuptuozHM84rozHM42

1SF

2,1

NI.tupnIdehctaL.niptcelesycneuqerF

62

zHM84TUOkcolctuptuozHM84

0SF

2,1

NItupnIdehctaL.niptcelesycneuqerF

7284DDVRWP.erocLLPdexifdnasreffubtuptuozHM84&42rofrewoP

93F_MARDSTUO#POTS_UPCybdetceffatoN.tuptuokcolcMARDSgninnureerF

14#POTS_KLCNI .wolnevirdnehwlevel"0"cigolta)7:0(MARDS&,)2:0(KLCUPCstlahtupnisuonorhcnysasihT

54,34,24]0:2[KLCUPCTUOUPCLDDVybderewop,stuptuokcolcUPC

64F_KLCUPCTUO#POTS_UPCehtybdetceffatoN.kcolcUPCgninnureerF

74UPCLDDVRWPV5.2skcolcUPCrofylppuS

84

1FERTUO.kcolcecnereferzHM813.41

2SF

2,1

NItupnIdehctaL.niptcelesycneuqerF

3

ICS9248-101

1. The ICS clock generator is a slave/receiver, I2C component. It can read back the data stored in the latches for verification.

Read-Back will support Intel PIIX4 "Block-Read" protocol.

2. The data transfer rate supported by this clock generator is 100K bits/sec or less (standard mode)

3. The input is operating at 3.3V logic levels.

4. The data byte format is 8 bit bytes.

5. To simplify the clock generator I2C interface, the protocol is set to use only "Block-Writes" from the controller. The

bytes must be accessed in sequential order from lowest to highest byte with the ability to stop after any complete byte

has been transferred. The Command code and Byte count shown above must be sent, but the data is ignored for those

two bytes. The data is loaded until a Stop sequence is issued.

6. At power-on, all registers are set to a default condition, as shown.

General I2C serial interface information

The information in this section assumes familiarity with I2C programming.

For more information, contact ICS for an I2C programming application note.

How to Write:

Controller (host) sends a start bit.

Controller (host) sends the write address D2

(H)

ICS clock will acknowledge

Controller (host) sends a dummy command code

ICS clock will acknowledge

Controller (host) sends a dummy byte count

ICS clock will acknowledge

Controller (host) starts sending first byte (Byte 0)

through byte 5

ICS clock will acknowledge each byte one at a time.

Controller (host) sends a Stop bit

How to Read:

Controller (host) will send start bit.

Controller (host) sends the read address D3

(H)

ICS clock will acknowledge

ICS clock will send the byte count

Controller (host) acknowledges

ICS clock sends first byte (Byte 0) through byte 5

Controller (host) will need to acknowledge each byte

Controller (host) will send a stop bit

Notes:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D3

(H)

AC

K

Byte Count

ACK

Byte

0

ACK

Byte 1

ACK

Byte

2

ACK

Byte

3

ACK

Byte 4

ACK

Byte

5

ACK

Stop Bit

How to Read:

Controller (Host) ICS (Slave/Receiver)

Start Bit

Address

D2

(H)

AC

K

Dummy Command Code

AC

K

Dummy Byte Count

AC

K

Byte 0

AC

K

Byte 1

ACK

Byte 2

AC

K

Byte 3

AC

K

Byte 4

AC

K

Byte 5

AC

K

Stop Bit

How to Write:

4

ICS9248-101

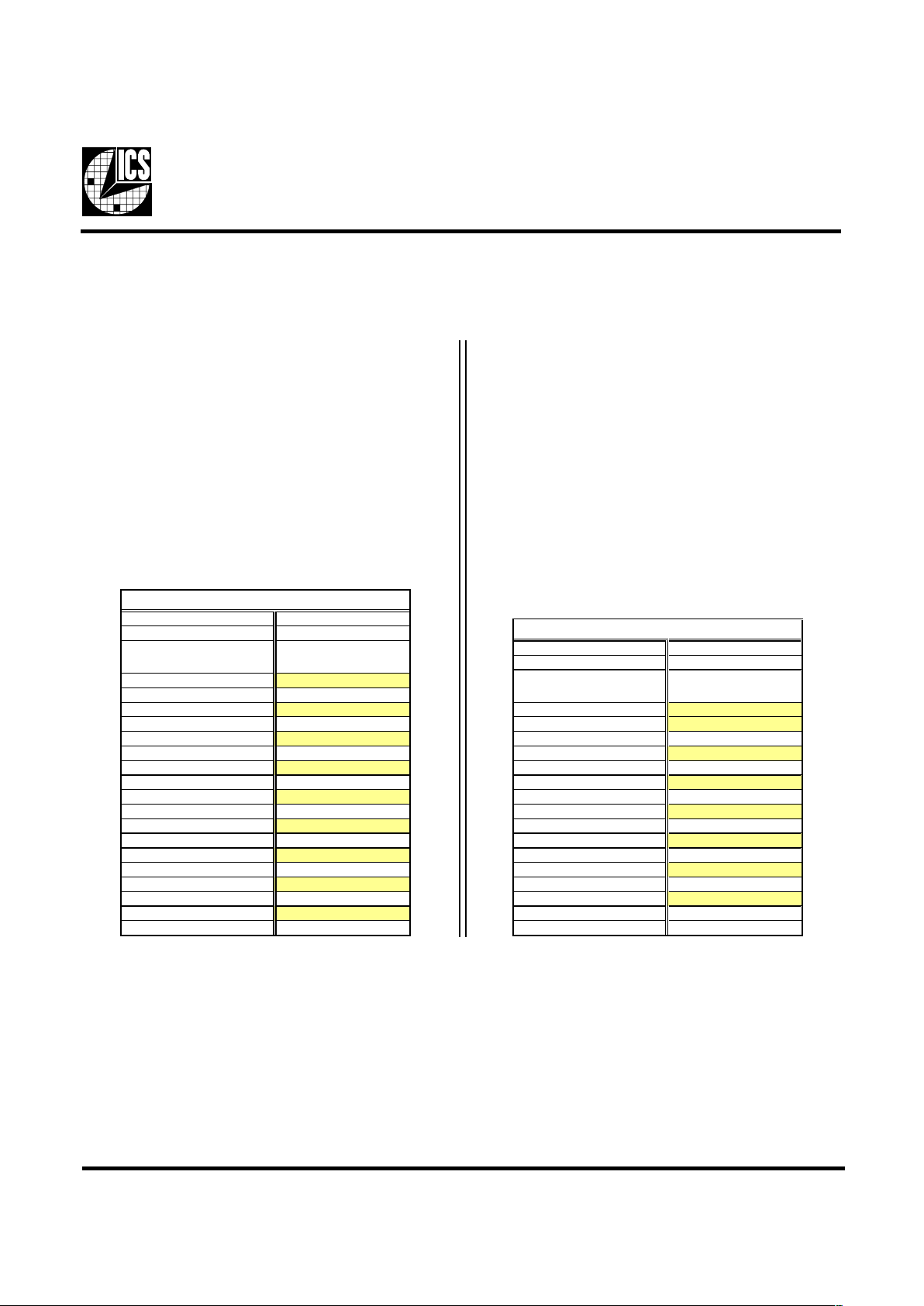

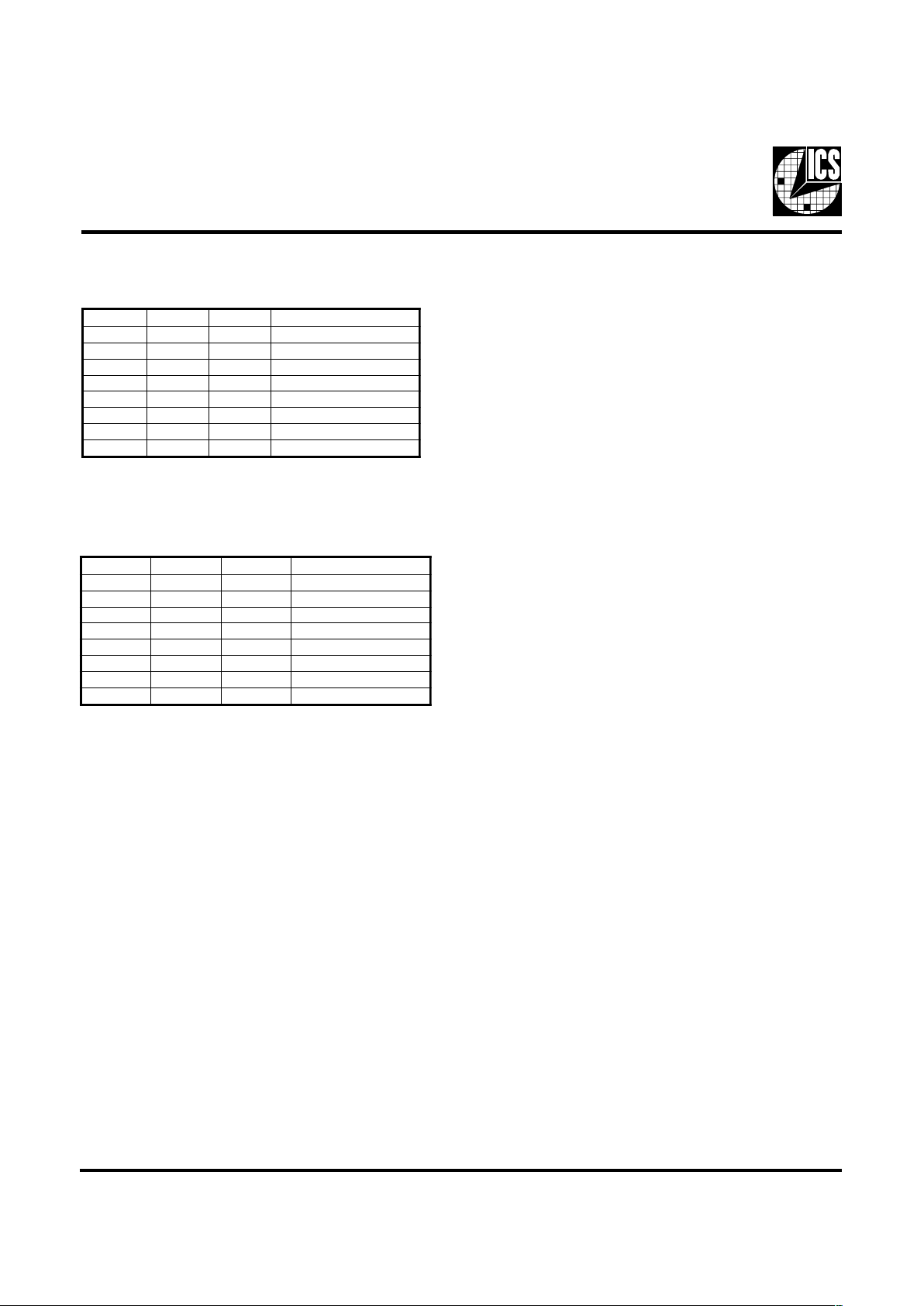

Functionality

VDD = 3.3V±5%, V

DDL

= 2.5V±5% or 3.3±5%, TA=0 to 70°C

Crystal (X1, X2) = 14.31818MHz

3SF2SF1SF0SF

UPC

)zHM(

ICP

)zHM(

0000 00.42133.14

0001 00.02100.04

0010 99.41133.83

0011 99.90166.63

0100 00.50100.53

0101 13.3856.14

0110 00.73152.43

0111 00.5705.73

1000 00.00133.33

1001 00.5976.13

1010 13.3877.72

1011 33.33133.33

1100 00.0900.03

1101 22.6970.23

1110 28.6614.33

1111 5.195.03

Byte0: Functionality and Frequency Select Register (default = 0)

Serial Configuration Command Bitmap

tiBnoitpircseDDWP

7tiB

daerpSretneC,noitaludoMmurtcepSdaerpS%52.0±-0

daerpSnwoD%5.0-ot0-1

1

tiB

]4:6,2[

]4:6,2[tiB

KLCUPC

)zHM(

KLCICP

)zHM(

1etoN

000000.42133.14

100000.02100.04

010099.41133.83

110099.90166.63

001000.50100.53

101013.3856.14

011000.73152.43

111000.5705.73

000100.00133.33

100100.5976.13

010113.3877.72

110133.33133.33

001100.0900.03

101122.6970.23

011128.6614.33

11115.195.03

3tiB

stupnidehctal,tceleserawdrahybdetcelessiycneuqerF-0

]4:6,2[tiBybdetcelessiycneuqerF-1

0

1tiB

lamroN-0

delbanEmurtcepSdaerpS-1

1

0tiB

gninnuR-0

stuptuollaetatsirT-1

0

Notes:

1, Default at Power-up will be for latched

logic inputs to define frequency. Bit [2,

6:4] are default to 0010.

2, PWD = Power-Up Default

3, When disabling spread spectrum bit7

needs to be set to 0 to maintain nominal

frequency.

5

ICS9248-101

Notes:

1. Inactive means outputs are held LOW and are disabled from switching.

2. Latched Frequency Selects (FS#) will be inverted logic load of the input frequency select pin conditions.

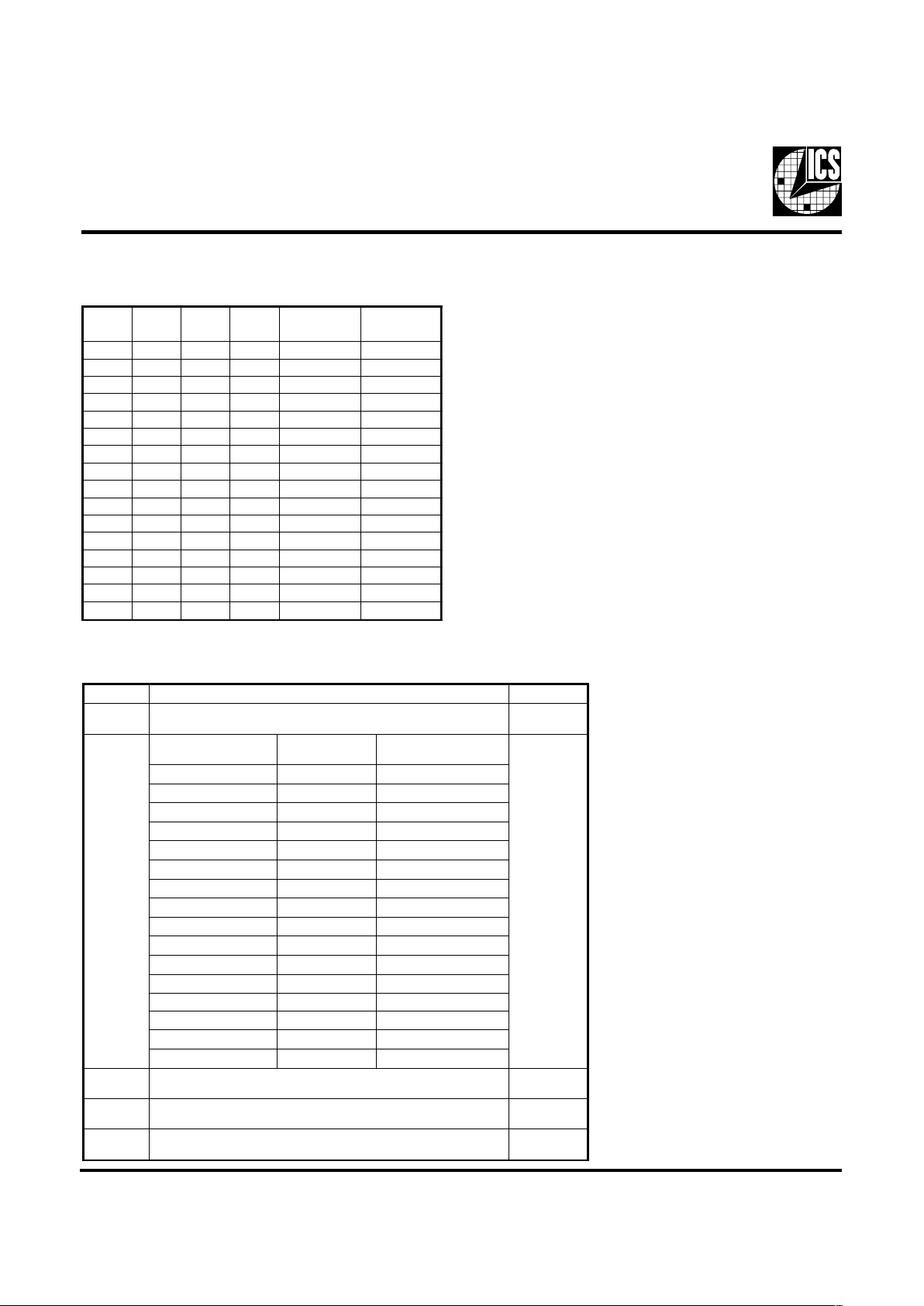

Byte 2: PCI Active/Inactive Register (1 = enable, 0 = disable)

tiB#niPDWPnoitpircseD

7tiB71 )tcanI/tcA(F_KLCICP

6tiB811 )tcanI/tcA(6KLCICP

5tiB711 )tcanI/tcA(5KLCICP

4tiB311 )tcanI/tcA(4KLCICP

3tiB211 )tcanI/tcA(3KLCICP

2tiB111 )tcanI/tcA(2KLCICP

1tiB011 )tcanI/tcA(1KLCICP

0tiB81 )tcanI/tcA(0KLCICP

Byte 1: CPU, Active/Inactive Register (1 = enable, 0 = disable)

tiB#niPDWPnoitpircseD

7tiB-1 )devreseR(

6tiB641 )tcanI/tcA(F_KLCUPC

5tiB-1 )devreseR(

4tiB-1 )devreseR(

3tiB931 )tcanI/tcA(F_MARDS

2tiB241 )tcanI/tcA(2KLCUPC

1tiB341 )tcanI/tcA(1KLCUPC

0tiB541 )tcanI/tcA(0KLCUPC

Byte 3: SDRAM Active/Inactive Register (1 = enable, 0 = disable)

tiB#niPDWPnoitpircseD

7tiB-1 )devreseR(

6tiB-1 )devreseR(

5tiB-1 )devreseR(

4tiB-1 )devreseR(

3tiB821 )evitcanI/evitcA(7MARDS

2tiB921 )evitcanI/evitcA(6MARDS

1tiB131 )evitcanI/evitcA(5MARDS

0tiB231 )evitcanI/evitcA(4MARDS

6

ICS9248-101

Byte 4: Reserved Active/Inactive Register (1 = enable, 0 = disable)

Byte 5: Peripheral Active/Inactive Register (1 = enable, 0 = disable)

Notes:

1. Inactive means outputs are held LOW and are disabled from switching.

2. Latched Frequency Selects (FS#) will be inverted logic load of the input frequency select pin conditions.

tiB#niPDWPnoitpircseD

7tiB-1 )devreseR(

6tiB-1 )devreseR(

5tiB-1 #)84_42LES(

4tiB-1 )devreseR(

3tiB-X #1SFdehctaL

2tiB-1 )devreseR(

1tiB-X #3SFdehctaL

0tiB-1 )devreseR(

tiB#niPDWPnoitpircseD

7tiB431 )tcanI/tcA(3MARDS

6tiB531 )tcanI/tcA(2MARDS

5tiB731 )tcanI/tcA(1MARDS

4tiB831 )tcanI/tcA(0MARDS

3tiB621 )tcanI/tcA(zHM84

2tiB521 )tcanI/tcA(zHM42

1tiB841 )tcanI/tcA(1FER

0tiB21 )tcanI/tcA(0FER

Loading...

Loading...