Integrated

Circuit

ICS9159-12

Systems, Inc.

Frequency Generator and Buffers for Mobile Pentium Systems

General Description

The ICS9159-12 generates all clocks required for mobile

microprocessor systems based on Pentium/Mobile Triton

chip sets. Three different reference frequency multiplying

factors are externally selectable with smooth frequency

transitions. These multiplying factors can be customized

for specific plications. A test mode is provided to drive all

clocks directly.

High drive BCLK outputs provide greater than 1V/ns slew

rate into 30pF loads. PCLK outputs provide better than 1V/

ns slew rate into 20pF loads while maintaining ±5% duty

cycle.

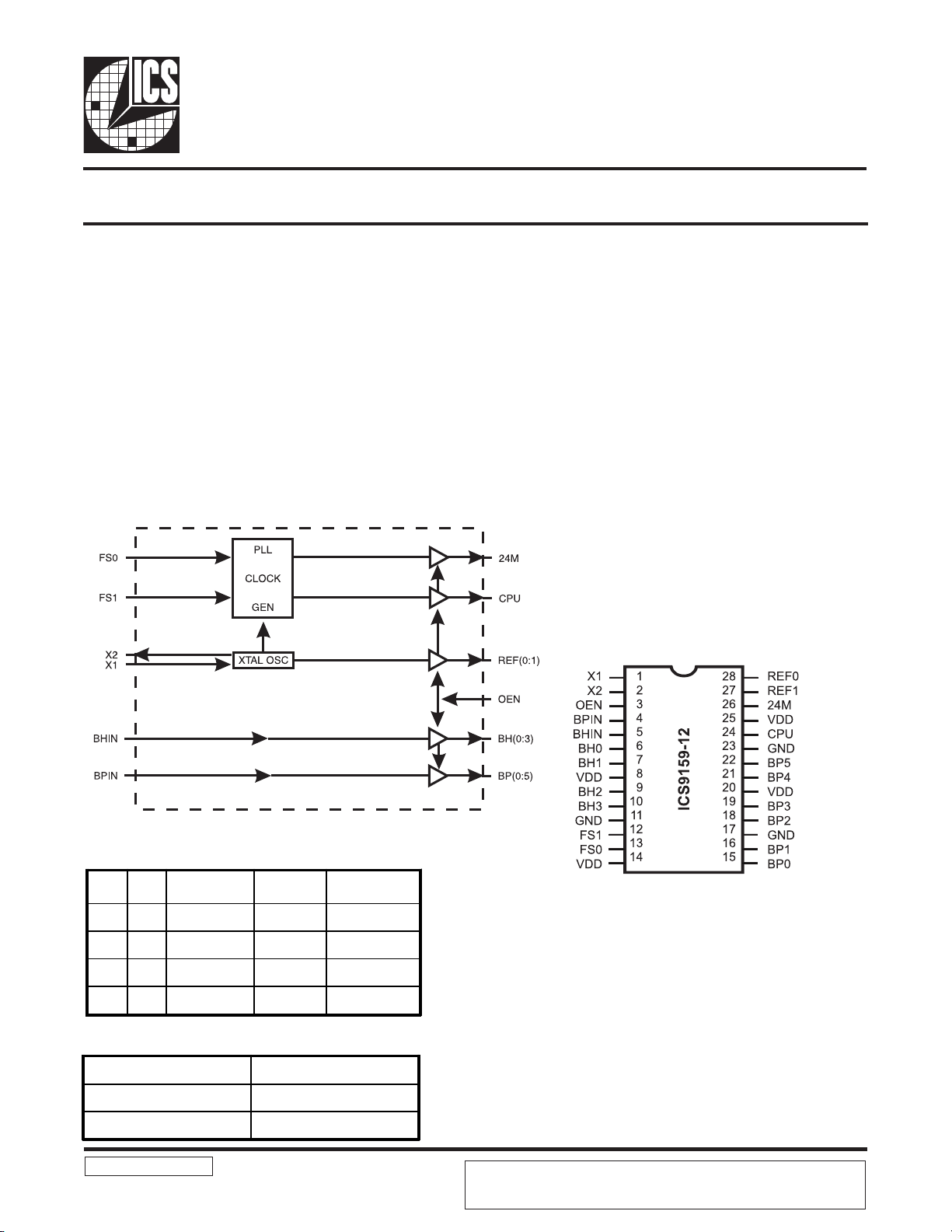

Block Diagram

Features

Generates 14 clocks including processor, disk

and reference

Meets all Pentium/Mobile Triton 82430MX

requirments

Independent buffers provide 4 and 6 clock copies

Buffered clocks skew matched to ±250ps

Buffer inputs are 5V tolerant

Test clock mode eases system design

Selectable multiplying and processor/bus ratios

Custom configurations available

3.0V- 5.5V supply range

28pin, .209" SSOP package

Pin Configuration

Functionality

FS1 FS0 *VCO

0 0 118/17*X1 14.318 50 (49.69)

0 1 65/7*X1 14.318 66. 6 (66.47)

1 0 92/11*X1 14.318 60 (59.87)

1 1 Test mode TCLK TCLK/2

*VCO range is limited form 60 - 200 MHz.

CPU 24M

VCO/2 24 MHz

TCLK/2 TCLK/4

9159-12 Rev B 071797

X1, REF

(MHz)

CPU (MHz)

28-Pin SSOP

Pentium is a trademark of Intel Corporation.

ICS reserves the right to make changes in the device data identified in this publication

without further notice. ICS advises its customers to obtain the latest version of all

device data to verify that any information being relied upon by the customer is current

and accurate.

ICS9159-12

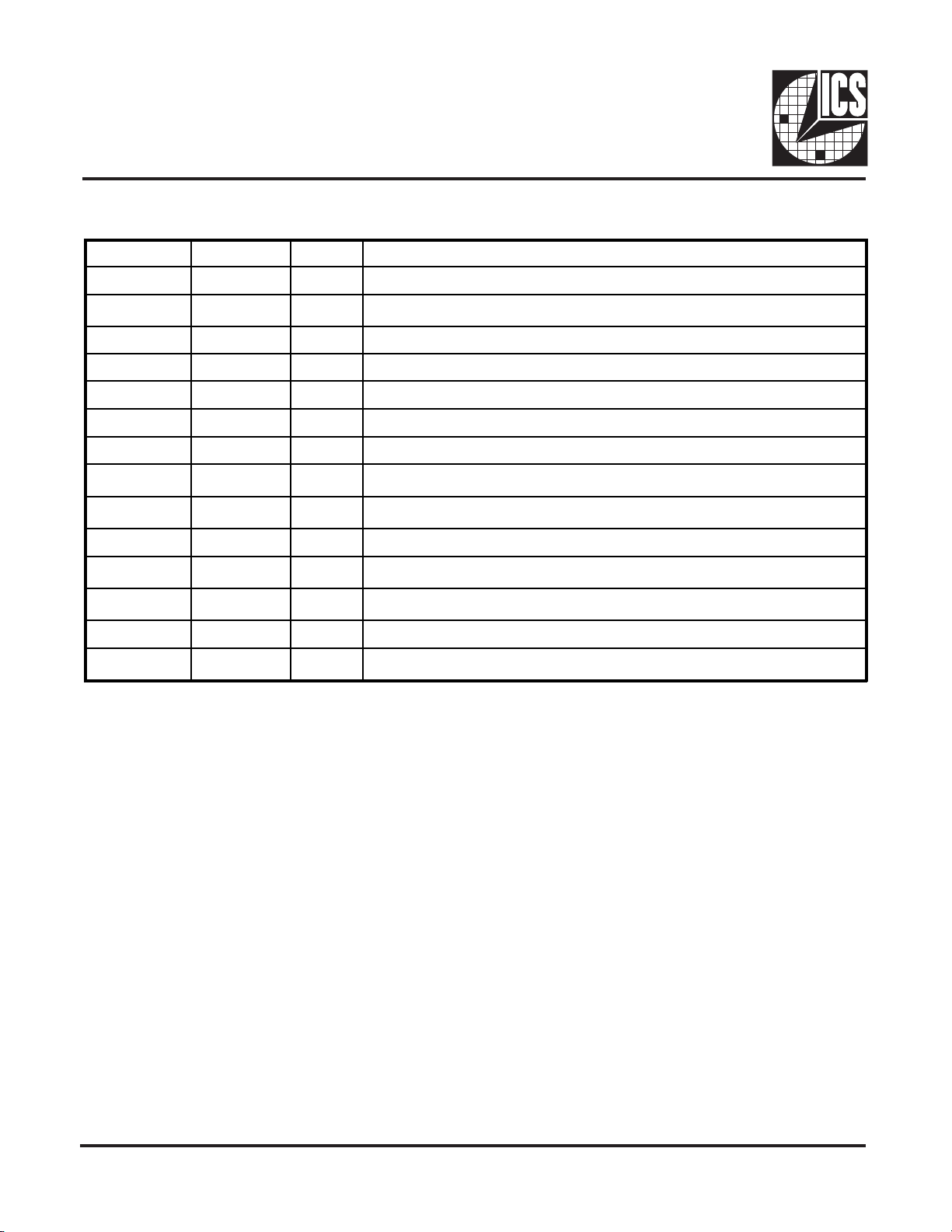

Pin Descriptions

PIN NUMBER PIN NAME TYPE DESCRIPTION

8, 25 VDD PWR Power for logic , CPU and fixed frequ ency output buffers.

1X1 IN

2 X2 OUT XTAL output which includes XTAL load capacitance.

3 OEN IN OEN tristates all outputs when low. This input has an internal pull-up device.

4 BPIN IN Input to BPIN(0:5) buffers.

5 BHIN IN Input to BHIN(0:3) buffers.

11, 23 GND PWR Ground for logic, CPU and fixed frequency output buffers.

6, 7, 9, 10 BH(0:3) OUT

13, 12 FS(0:1) IN

14, 20 VDD PWR Power for B CLK output buffers.

15, 16, 18 19,

21, 22

24 CPU OUT

26 24M OUT The 24M clock is fixed at 24 MHz.

28, 27 REF(0:1) OUT

BP(0:5) OUT

XTAL or external reference frequency input. This input includes XTAL load

capacitance and feedback bias for a 10 - 30 MHz XTAL.

Buffered copies of the BHIN input, typically used to drive the PCI device clock

inputs at one half the CPU frequency.

Frequency multiplier select pins. See table below. These inputs have internal pull-up

devices.

Buffered copies of the BPIN input , typically used to drive the host device clock

inputs at the CPU fr equency. 17 VSS PWR Ground f or BCLK output buffers.

The CPU output, which is a multiple of the input reference frequency as shown in

the table above. Duty cy cle is 50/50±5% with a maximum freq uency of 100 MHz.

REF is a buffered copy of the crystal oscillator or reference input clock,

nominally 14.3 1818 MHz.

Note: BCLK buffers cannot be supplied with 5 volts (Pins 14 and 20) if CPU

and fixed frequencies (Pins 1, 8 and 26) are being supplied with 3 volts.

2

Loading...

Loading...