Integrated

Circuit

Systems, Inc.

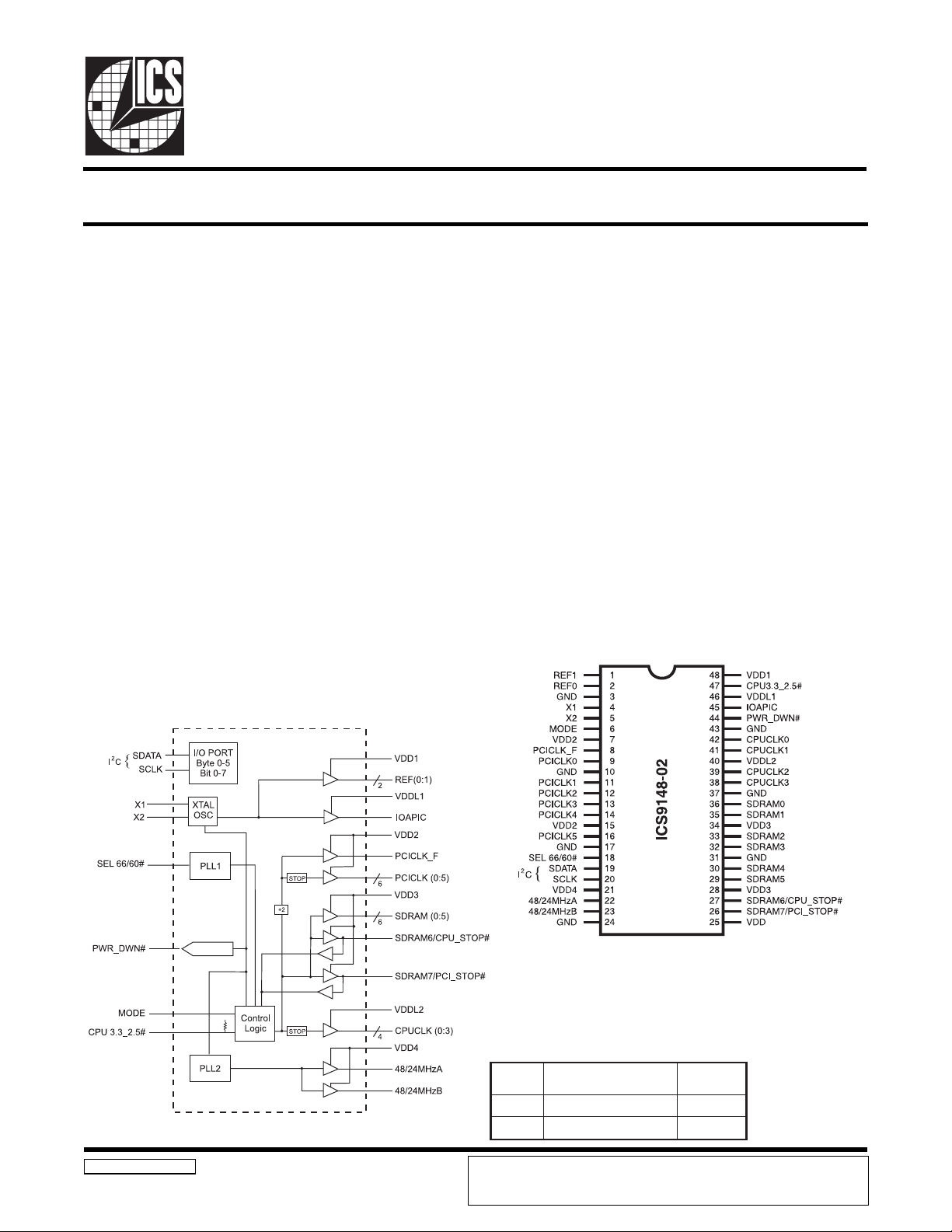

Pentium/ProTM System Clock Chip

General Description Features

The ICS9148-02 is a Clock Synthesizer chip for Pentium and

PentiumPro CPU based Desktop/Notebook systems that will

provide all necessary clock timing.

Features include four CPU, seven PCI and eight SDRAM

clocks. Two reference outputs are available equal to the

crystal frequency. Additionally, the device meets the Pentium

power-up stabilization, which requires that CPU and PCI

clocks be stable within 2ms after power-up.

PWR_DWN# pin allows low power mode by stopping crystal

OSC and PLL stages. For optional power management,

CPU_STOP# can stop CPU (0:3) clocks and PCI_STOP#

will stop PCICLK (0:5) clocks. CPU and IOAPIC output

buffer strength controlled by CPU 3.3_2.5# pin to match

VDDL voltage.

High drive CPUCLK outputs typically provide greater than 1

V/ns slew rate into 20pF loads. PCICLK outputs typically

provide better than 1V/ns slew rate into 30pF loads while

maintaining 50±5% duty cycle. The REF clock outputs typically

provide better than 0.5V/ns slew rates.

Generates system clocks for CPU, IOAPIC, SDRAM,

PCI, plus 14.314 MHz REF(0:1), USB, Plus Super I/O

Supports single or dual processor systems

I2C serial configuration interface provides output clock

disabling and other functions

MODE input pin selects optional power management

input control pins

Two fixed outputs separately selectable as

24 or 48MHz

Separate 2.5V and 3.3V supply pins

2.5V or 3.3V outputs: CPU, IOAPIC

3.3V outputs: SDRAM, PCI, REF, 48/24 MHz

CPU 3.3_2.5# logic pin to adjust output strength

No power supply sequence requirements

Uses external 14.318MHz crystal

48 pin 300 mil SSOP

Output enable register

for serial port control: 1 = enable

ICS9148-02

0 = disable

The ICS9148-02 accepts a 14.318MHz reference crystal or

clock as its input and runs on a 3.3V core supply.

Block Diagram

Pentium is a trademark on Intel Corporation.

Pin Configuration

48-Pin SSOP

Functionality

VDD (1:4) 3.3V±10%, VDDL1, 2 2.5±5% or 3.3±10% 0-70°C

Crystal (X1, X2) = 14.31818 MHz

LES

00603

16.663.33

MARDS,KLCUPC

)zHM(

KLCICP

)zHM(

9148-02 Rev C 1/26/99

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

ICS9148-02

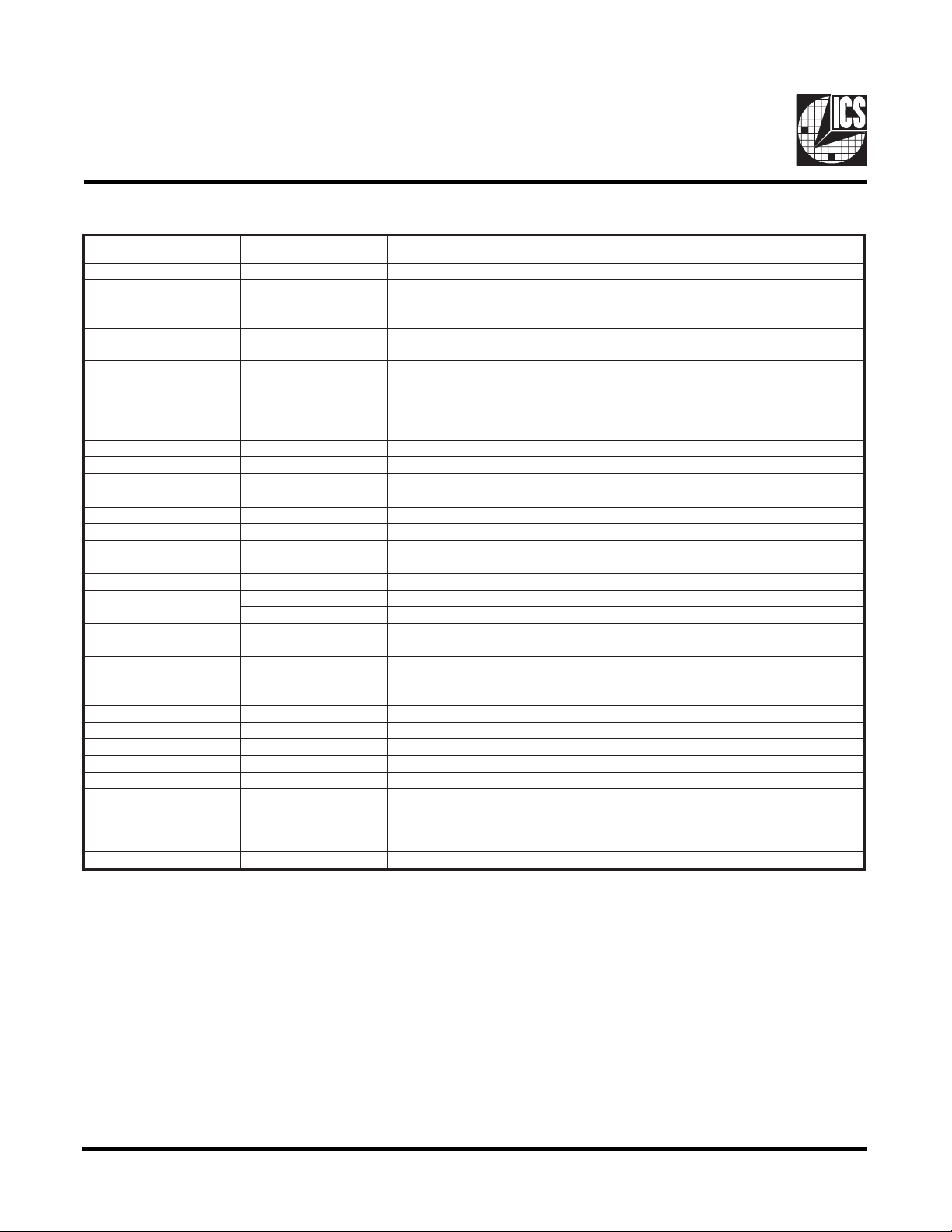

Pin Descriptions

REBMUNNIPEMANNIPEPYTNOITPIRCSED

1,2)1:0(FERTUOtuptuOkcolcecnerefeR

,42,71,01,3

34,73,13

41XNIpacdaollatsyrclanretnisah,tupniecnereferrolatsyrC

52XTUO

6EDOMNI

51,72DDVRWPV3.3lanimon,)5:0(KLCICP,F_KLCICProfylppuS

8F_KLCICPTUO#POTS_ICPybdetceffaton,kcolcICPgninnureerF

61,41,31,21,11,9)5:0(KLCICPTUOskcolcICP

81#06/66LESNIUPCdnaMARDSrofzHM6.66rozHM06stceleS

91ATADSNII

02KLCSNII

124DDVRWPV3.3lanimon,BzHM42/84,AzHM42/84rofylppuS

22AzHM42/84TUOO/IrepuSroBSUroftuptuorevirdzHM42/84

32BzHM42/84TUOO/IrepuSroBSUroftuptuorevirdzHM42/84

52DDVRWPV3.3lanimon,erocLLProfylppuS

62

72

43,823DDVRWP

042LDDVRWPlanimonV3.3ro5.2rehtie,)3:0(KLCUPCrofylppuS

83,93,14,24)3:0(KLCUPCTUO2LDDVybderewop,tuptuokcolcKLCUPC

92,03,23,33,53,63)5:0(MARDSTUO)detceles(zHM6.66ro06takcolcsMARDS

44#NWD_RWPNIwolevitca,pihcnwodsrewoP

54CIPAOITUO1LDDVybderewop)zHM813.41(,tuptuokcolcCIPAOI

641LDDVRWPlanimonV3.3ro5.2rehtie,CIPAOIrofylppuS

74#5.2-3.3UPCNI

841DDVRWPV3.3lanimon,2X,1X,)1:0(FERrofylppuS

DNGRWP)nommoc(dnuorG

7MARDSTUO)detceles(zHM6.66/06kcolcMARDS

#POTS_ICPNIwolnehwlevel"0"cigolta)5:0(suBICPstlaH

6MARDSTUO)detceles(zHM6.66/06kcolcMARDS

#POTS_UPCNIwolnehwlevel"0"cigoltaskcolcUPCstlaH

1Xotrotsiser

.)#POTS_UPCdna#POTS_ICP(

2

2

tupniatadC

tupnikcolcC

V3.3lanimon,#POTS_ICP/7MARDS

.detcelessihtgnerts

kcabdeefdnapacdaollanretnisah,tuptuolatsyrC

72&62snipneht,HGIHsiedoMfI.noitcelesnoitcnuftupnI

edoMfI.)6MARDSdna7MARDS(stuptuosaderugifnocera

stupnisaderugifnocera72&62snip,neht,WOLsi

,#POTS_UPC/6MARDS,)5:0(MARDSrofylppuS

,DDVotpullupsah,noitceleshtgnertsreffubDDV5.2ro3.3

reffuBV3.3,DDVotdetcennocnehW.rotsiserK03lanimon

reffuBV5.2,DNGotdetcennocnehW.detcelessihtgnerts

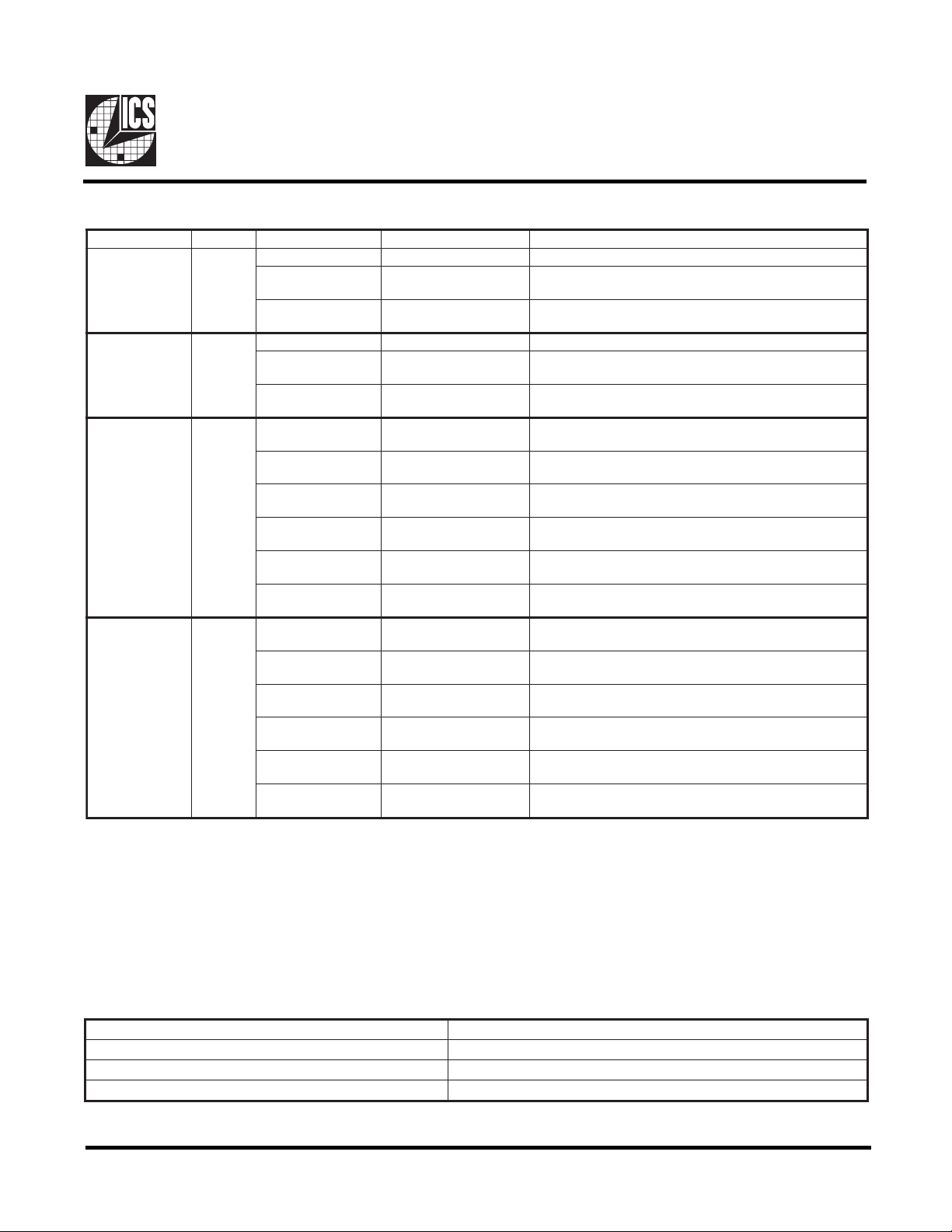

Power Groups

VDD = Supply for PLL core

VDD1 = REF (0:1), X1, X2

VDD2 = PCICLK_F, PCICLK (0:5)

VDD3 = SDRAM (0:5), SDRAM6/CPU_STOP#, SDRAM7/PCI_STOP#

VDD4 = 48/24MHzA, 48/24MHzB

VDDL1 = IOAPIC

VDDL2 = CPUCLK (0:3)

2

Power-On Conditions

#06/66LESEDOM#NIPNOITPIRCSEDNOITCNUF

11

01

10

00

24,14,93,83sKLCUPCelbasid/elbanegifnoclaires/w-zHM6.66

,23,33,53,63

62,72,92,03

,21,31,41,61

8,9,11

24,14,93,83sKLCUPCelbasid/elbanegifnoclaires/w-zHM06

,23,33,53,63

62,72,92,03

,21,31,41,61

8,9,11

62#POTS_ICP

72#POTS_UPC

8F_KLCICP

24,14,93,83sKLCUPC

,23,33,53,63

92,03

,21,31,41,61

9,11

62#POTS_ICP

72#POTS_UPC

8F_KLCICP

24,14,93,83sKLCUPC

,23,33,53,63

92,03

,21,31,41,61

9,11

MARDSstuptuoMARDSllA-zHM6.66

sKLCICPelbasid/elbanegifnoclaires/w-zHM3.33

MARDSelbasid/elbanegifnoclaires/w-zHM06

sKLCICPelbasid/elbanegifnoclaires/w-zHM03

MARDS

sKLCICP

MARDS

sKLCICP

ICS9148-02

skcolC)5:0(ICP,tnemeganaMrewoP

wolnehwdeppotS

skcolC)5:0(UPC,tnemeganaMrewoP

wolnehwdeppotS

rofgninnureerFkcolCICP-zHM3.33-zHM3.33

tnemeganaMrewoP

dnalortnoCpotSlanretxe/wskcolCUPC-zHM6.66

.elbasid/elbanelaudividnigifnoclaires

laudividnigifnoclaires/wskcolCMARDS-zHM6.66

.elbasid/elbane

dnalortnocpotSlanretxe/wskcolCICP-zHM3.33

.elbasid/elbanelaudividnigifnoclaires

skcolC)5:0(ICP,tnemeganaMrewoP

wolnehwdeppotS

skcolC)5:0(UPC,tnemeganaMrewoP

wolnehwdeppotS

rewoProfgninnureerFkcolCICP-zHM03

tnemeganaM

dnalortnocpotSlanretxe/wskcolCUPC-zHM06

.elbasid/elbanelaudividnigifnoclaires

laudividnigifnoclaires/wskcolCMARDS-zHM06

.elbasid/elbane

dnalortnocpotSlanretxe/wskcolCICP-zHM03

.elbasid/elbanelaudividnigifnoclaires

Example:

a) if MODE = 1, pins 26 and 27 are configured as SDRAM7 and SDRAM6 respectively.

b) if MODE = 0, pins 26 and 27 are configured as PCI_STOP# and CPU_STOP# respectively.

Power-On Default Conditions

At power-up and before device programming, all clocks will default to an enabled and on condition. The frequencies that are then produced

are on the MODE pin as shown in the table below.

KCOLC PU-REWOPTANOITIDNOCTLUAFED

)1:0(FER zHM81813.41

0CIPAOI zHM81813.41

zHM42/84zHM84

3

ICS9148-02

T echnical Pin Function Descriptions

VDD(1,2,3,4)

This is the power supply to the internal core logic of the

device as well as the clock output buffers for REF(0:1),

PCICLK, 48/24MHzA/B and SDRAM(0:7).

This pin operates at 3.3V volts. Clocks from the listed

buffers that it supplies will have a voltage swing from Ground

to this level. For the actual guaranteed high and low voltage

levels for the Clocks, please consult the DC parameter table

in this data sheet.

VDDL1,2

This is the power supplies for the CPUCLK and IOAPCI

output buffers. The voltage level for these outputs may be

2.5 or 3.3volts. Clocks from the buffers that each supplies

will have a voltage swing from Ground to this level. For the

actual Guaranteed high and low voltage levels of these

Clocks, please consult the DC parameter table in this Data

Sheet.

GND

This is the power supply ground (common or negative) return

pin for the internal core logic and all the output buffers.

X1

This input pin serves one of two functions. When the device

is used with a Crystal, X1 acts as the input pin for the

reference signal that comes from the discrete crystal. When

the device is driven by an external clock signal, X1 is the

device input pin for that reference clock. This pin also

implements an internal Crystal loading capacitor that is

connected to ground. See the data tables for the value of this

capacitor.

X2

This Output pin is used only when the device uses a Crystal

as the reference frequency source. In this mode of operation,

X2 is an output signal that drives (or excites) the discrete

Crystal. The X2 pin will also implement an internal Crystal

loading capacitor that is connected to ground. See the Data

Sheet for the value of this capacitor.

CPUCLK (0:3)

These Output pins are the Clock Outputs that drive processor

and other CPU related circuitry that requires clocks which

are in tight skew tolerance with the CPU clock. The voltage

swing of these Clocks are controlled by the Voltage level

applied to the VDDL2 pin of the device. See the Functionality

Table for a list of the specific frequencies that are available

for these Clocks and the selection codes to produce them.

SDRAM(0:7)

These Output Clocks are use to drive Dynamic RAMs and

are low skew copies of the CPU Clocks. The voltage swing

of the SDRAMs output is controlled by the supply voltage

that is applied to VDD3 of the device, operates at 3.3 volts.

48/24MHzA, B

This is a fixed frequency Clock output that is typically used

to drive Super I/O devices. Outputs A and B are defined as

24 or 48MHz by I2C register (see table).

IOAPIC

This Output is a fixed frequency Output Clock that runs at the

Reference Input (typically 14.31818MHz) . Its voltage level

swing is controlled by VDDL1 and may operate at 2.5 or

3.3volts.

REF(0:1)

The REF Outputs are fixed frequency Clocks that run at the

same frequency as the Input Reference Clock X1 or the

Crystal (typically 14.31818MHz) attached across X1 and

X2.

PCICLK_F

This Output is equal to PCICLK(0:5) and is FREE RUNNING,

and will not be stopped by PCI_STP#.

PCICLK (0:5)

These Output Clocks generate all the PCI timing requirements

for a Pentium/Pro based system. They conform to the

current PCI specification. They run at 1/2 CPU frequency.

SELECT 66.6/60MHz#

This Input pin controls the frequency of the Clocks at the

CPU, PCICLK and SDRAM output pins. If a logic 1 value

is present on this pin, the 66.6 MHz Clock will be selected.

If a logic 0 is used, the 60MHz frequency will be selected.

MODE

This Input pin is used to select the Input function of the I/

O pins. An active Low will place the I/O pins in the Input

mode and enable those stop clock functions.

4

T echnical Pin Function Descriptions

CPU 3.3_2.5#

This Input pin controls the CPU and IOAPIC output buffer

strength for skew matching CPU and SDRAM outputs to

compensate for the external VDDL supply condition. It is

important to use this function when selecting power supply

requirements for VDDL1,2. A logic 0 (ground) will indicate

2.5V operation and a logic 1 will indicate 3.3V operation.

This pin has an internal pullup resistor to VDD.

PWR_DWN#

This is an asynchronous active Low Input pin used to Power

Down the device into a Low Power state by not removing the

power supply. The internal Clocks are disabled and the VCO

and Crystal are stopped. Powered Down will also place all

the Outputs in a low state at the end of their current cycle.

The latency of Power Down will not be greater than 3ms. The

I2C inputs will be Tri-Stated and the device will retain all

programming information. This input pin only valid when

MODE=0 (Power Management Mode)

CPU_STOP#

This is a synchronous active Low Input pin used to stop the

CPUCLK clocks in an active low state. All other Clocks

including SDRAM clocks will continue to run while this

function is enabled. The CPUCLKs will have a turn ON

latency of at least 3 CPU clocks. This input pin only valid

when MODE=0 (Power Management Mode)

ICS9148-02

PCI_STOP#

This is a synchronous active Low Input pin used to stop the

PCICLK clocks in an active low state. It will not effect

PCICLK_F nor any other outputs. This input pin only valid

when MODE=0 (Power Management Mode)

I2C

The SDATA and SCLOCK Inputs are use to program the

device. The clock generator is a slave-receiver device in the

I2C protocol. It will allow read-back of the registers. See

configuration map for register functions. The I2C

specification in Philips I2C Peripherals Data Handbook

(1996) should be followed.

5

Loading...

Loading...